## 摘要

光电分选就是利用光电技术把次品分类检出并剔除，其关键的一个环节是物料数据的精确采集。CCD(电荷耦合器件)是一种集光电转换、电荷存储、电荷转移为一体的传感器件，因其具有自扫描、高分辨率、高灵敏度、结构紧凑、像素位置准确等特性，近年来在摄像、工业检测等科技领域得到了广泛的应用。

本课题主要研究光电分选机的数据采集系统。系统以 Xilinx 公司的 FPGA 芯片 XC3S50 作为主控制器和处理器，用线阵 CCD 传感器对颗粒状物料进行动态扫描，得到图像数据，由图像数字器进行信号调理、A/D 转换，经外部存储器缓存后送数据处理模块进行处理。该系统可实时在 PC 机上显示采集数据波形。

本文详细的介绍了 CCD 的工作原理，分模块介绍了线阵 CCD 驱动电路；图像信号的调理、采样和存储电路；通信电路；电源电路以及 EPP 接口电路等的设计与实现。系统采用 FPGA 技术实现了 CCD 时序逻辑控制，CCD 图像信号的采样和存储控制；自定通信总线协议，建立三线制同步串行通信系统；完成对一帧 CCD 样本图像数据的采集和传输等。上位机用 VC++ 编写了数据采集应用程序，完成了数据波形的实时显示。印制电路板采用多层设计方法，所用硬件基本使用高速大规模集成电路，故电路板面积小、可靠性高并且和镜头的体积相适应。

本文采用 Verilog 语言进行硬件电路描述，利用 Xilinx ISE 软件进行仿真、综合、实现和配置下载。最后经过大量实验，实现了 CCD 信号的稳定输出和数据采集系统的工作，并给出了实验波形，总结了系统的各方面性能和下一步的研究方向，为进一步的研究积累了经验。

**关键词：**光电分选机；线阵 CCD；FPGA；数据采集；EPP

## The Study of Photoelectric Sorter Data Acquisition System

### Abstract

Sorting is a way to sort and remove infested objects by using photoelectrical technology. The most important part of sorting is accurate data acquisition of the materials. CCD (Charge Coupled Devices) is a sensor integrated the optics to electronics conversion, charge storage and charge transition, which is applied widely in some fields such as camera and industry measurement and so on recently as its feathers of self-scanning, high aspect ratio, high sensitivity, compact structure and accurate pitch position etc.

The thesis mainly studies the data acquisition system of photoelectric sorter. The system uses XC3S50 FPGA by Xilinx as the core controller and processor, and uses linear CCD sensor to scan the grainy materials and acquire the image data. The image data through the image digitizer which included the image signal conditioning, A/D converter is cached by the external memory and processed by the data process module. The system can realize the display of data acquisition waveform real-time on PC.

At the beginning, the thesis detailed introduces the CCD working principle. Then the designs and implementations of the drive circuit of CCD camera; the image signal conditioning, sample and store circuit; communication circuit for data transmit; power supply circuit for the voltages and EPP interface circuit are introduced in modules. Based on FPGA technology, the system realizes CCD time sequence logical control, CCD image data sample and store. Besides, the design completes synchronous serial communication system based on self-defining protocol; furthermore, the design completes the sample image data acquisition and transmission. Upper computer writes the data acquisition application programs with VC++ and realizes the waveforms of data real-time display. The hardware circuit is mainly designed based on high-speed LSI (Large Scale Integrated) circuits and multi-layer circuits. Because of this, the design has high reliability and the size of the PCB (Printed-Circuit Board) is small and matches the camera lenses and volume.

In this paper, the hardware description is realized in Verilog language. Using Xilinx ISE software has completed the simulation, synthesis, implementation and configuration. The experimental results prove the stable output of CCD and operation of data acquisition system are achieved, test waves are given out. The system's performance and next study directions are summarized which can provide some experience for further research.

**Key Words:** Electro-optical Sorter; Linear CCD; FPGA; Data Acquisition; EPP

## 独创性说明

作者郑重声明：本硕士学位论文是我个人在导师指导下进行的研究工作及取得研究成果。尽我所知，除了文中特别加以标注和致谢的地方外，论文中不包含其他人已经发表或撰写的研究成果，也不包含为获得大连理工大学或者其他单位的学位或证书所使用过的材料。与我一同工作的同志对本研究所做的贡献均已在论文中做了明确的说明并表示了谢意。

作者签名: 宋献波 日期: 2006.12.29

## 大连理工大学学位论文版权使用授权书

本学位论文作者及指导教师完全了解“大连理工大学硕士、博士学位论文版权使用规定”，同意大连理工大学保留并向国家有关部门或机构送交学位论文的复印件和电子版，允许论文被查阅和借阅。本人授权大连理工大学可以将本学位论文的全部或部分内容编入有关数据库进行检索，也可采用影印、缩印或扫描等复制手段保存和汇编学位论文。

作者签名: 宋献波

导师签名: 李明伟

2006 年 12 月 29 日

## 1 绪论

### 1.1 光电分选机研究的意义

分选，是物料精加工的一道工序。光电分选机是综合利用了现代光学、电子学和生物学等新技术，从大量散装产品中将颜色不正常的或感受病虫害的个体(球、块或颗粒)以及外来夹杂物检测出并自动分选剔除，是典型的光、机、电一体化的高新技术设备。在合格品与疵品因粒度或密度十分接近，无法用传统的筛选或比重分选设备分离的场合，其提高产品品质、适应日益发展的商品市场需要的独特作用将十分明显<sup>[1-2]</sup>。它的应用不但可以提高生产效率，增加其附加值，带来巨大的经济及社会效益，而且还可以保障食用、使用时的安全性。

在分选机研究方面，国外公司起步较早。美国 ESM 公司及 Sortex 公司分别于 20 世纪 30 年代及 40 年代研制了这种设备，并根据市场需要不断推陈出新。日本佐竹公司于 1979 年首次推出这种产品，且目前生产的 GS 系列大米色选机性能优越，技术指标稳定，得到了广泛的应用<sup>[3]</sup>。日本安西制作所于 1966 年 6 月成立后，至今一直着力于光电分选技术的研究，2002 年 4 月成功开发出世界首创的用于分选低粘度小麦的专用分选机 AU，2004 年开发并生产搭载高速 CCD(Charge Coupled Device)的大型号色选机 DC<sup>[4]</sup>。另外从事分选机研究的公司还有美国布勒集团及英国和瑞士的一些粮食加工设备生产企业。

相对国外而言，国内分选机的研究还处于起步阶段，用于成品的还很少，目前主要是引进或者改造国外的分选机。主要有：中美合资合肥安科光电有限公司引进美国技术生产的分选机系列；由浙江齐鲤机械有限公司和韩国韩亚自动化(株式会社)联合开发制作的 DIGINICS 系列大米分选机；合肥美亚光电技术有限责任公司 2003 年 8 月推出的最新 V8 软件系统 SS-B 系列数字化分选机，其首次将高速浮点 DSP 数字信号处理技术及雷达中的抗干扰技术用于数字化分选机的开发；另外，核工业理化工程研究院自主研究生产的分选机 1996 年 11 月通过了国家鉴定，但在结构设计上还有许多值得改进的地方，各项技术指标与国外产品相比还有一定的差距<sup>[5]</sup>。

近 30 年来，光电分选机在发达国家的农业、食品业、工业和矿业等行业中得到了广泛应用。在我国，分选机已在碾米加工业中占据主导地位，农副产品分选、金属分选和矿石分选等其它加工业也正在积极推广应用。

上述说明，我国在光电分选机的研发方面还处于起步阶段，为了尽可能瞄准国际先进水平，实现高起点开发，有必要对国产分选机进行技术革新和产品升级。

## 1.2 FPGA/CPLD 技术及其开发环境

FPGA(Field Programmable Gate Array, 现场可编程门阵列)和 CPLD(Complex Programmable Logic Device, 复杂可编程逻辑器件), 是作为专用集成电路 ASIC(Application Specific Integrated Circuit)领域中的一种半定制电路而出现的, 既继承了 ASIC 的大规模、高集成度、高可靠性的优点, 又克服了普通 ASIC 设计周期长、投资大、灵活性差的缺点, 逐步成为复杂数字硬件电路的首选<sup>[6]</sup>。

FPGA 主要由以下几个部分组成: (1)可编程逻辑块 CLB; (2)可编程输入/输出模块 IOB; (3)可编程内部连线 PI。I/O 模块分布在芯片四周, 它是内部逻辑和芯片封装脚之间的接口。逻辑单元通过程序定义内部联接关系, 完成用户所需的逻辑功能, 逻辑单元与逻辑单元、逻辑单元与外界的连接关系以及矩阵开关的状态都通过程序定义。FPGA 借助于可编程内部连线 PI 把功能比较简单的逻辑块连接在一起, 从而实现复杂功能电路的设计。CPLD 的结构相对比较简单, 它主要有可编程 I/O 单元、基本逻辑单元、布线池和其他辅助功能模块组成。CPLD 在工艺和结构上与 FPGA 有一定的区别, FPGA 一般都是 SRAM 工艺的, 而 CPLD 一般都是基于乘积项结构的。

### 1.2.1 FPGA/CPLD 设计流程

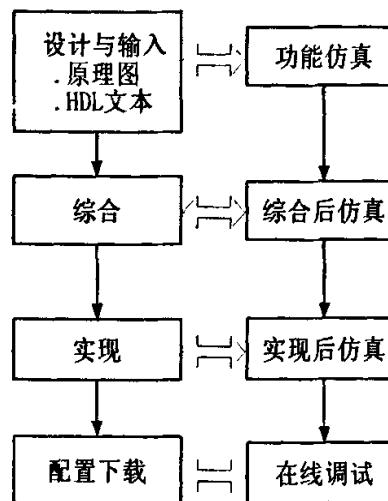

一般来说, 完整的 FPGA/CPLD 设计流程主要包括设计与输入、设计仿真、设计综合、实现和配置下载等主要步骤, 其流程图如图 1.1 所示。

图 1.1 FPGA/CPLD 设计流程图

Fig. 1.1 Flow chart of FPGA/CPLD design

设计与输入是根据设计者的设计方法将所设计的功能描述给 EDA 软件。常用的设计方法有硬件描述语言(HDL)和原理图设计输入方法。原理图设计输入法的优点是直观、便于理解、元件库资源丰富，缺点是可维护性较差，不利于模块建设与重用，而且当选用的芯片升级换代后，所有的原理图都要作相应的改动。目前进行大型工程设计时，最常用的方法是 HDL 设计输入法，其中最为广泛的 HDL 语言是 VHDL 和 Verilog HDL。波形输入法和状态机输入法是两种常用的辅助设计方法，但是这两种方法只有在特定的情况下才能缓解设计者的工作量，并不适合所有的设计。

电路设计完成后，要用专用的仿真工具对设计进行功能仿真，验证电路功能是否符合设计要求。功能仿真有时也称前仿真。通过仿真能及时发现设计中的错误，加快设计进度，提高设计的可靠性。

综合优化(Synthesize)是指将 HDL 语言、原理图等设计输入翻译成由与、或、非门，RAM，寄存器等基本逻辑单元组成的逻辑连接(网表)，并根据目标与约束条件优化所生成的逻辑连接，输出 edf 和 edn 等文件，供 FPGA/CPLD 厂家的布局布线器进行实现。

综合完成后需要检查结果是否与原设计一致，就需要做综合后仿真。在仿真时，把综合生成的延时文件反标到综合仿真模型中去，可估计门延时带来的影响，综合后仿真虽然比功能仿真精确一些，但是只能估计门延时，而不能估计线延时，仿真结果与布线后的实际情况还有一定的差距，并不十分精确。这种仿真的主要目的在于检查综合器的综合结果是否与设计输入一致。

根据所选芯片的型号，将综合输出的逻辑网表适配到具体的 FPGA/CPLD 器件上，这一过程称为实现(Implementation)过程。因为只有器件开发商最了解器件的内部结构，所以实现步骤必须选用器件开发商提供的工具软件。

布局布线之后做时序仿真，时序仿真中应该将布局布线的时延文件反标到设计中，使仿真既包含门延时，又包含线延时信息。与前面的各种仿真相比，这种后仿真包含的延时信息最为全面、准确，能较好地反映芯片实际的工作情况。

设计开发的最后步骤是在线调试或者将生成的配置文件写入芯片中进行测试。

### 1.2.2 FPGA/CPLD 设计工具 Xilinx ISE 介绍

Xilinx 作为当今世界上最大的 FPGA/CPLD 生产商之一，长期以来一直推动着 FPGA/CPLD 技术的发展。其开发的软件也不断升级换代，由早期的 Foundation 系列逐步发展到目前的 ISE 8.X 系列。ISE 是集成综合环境的简称，它是 Xilinx FPGA/CPLD 的综合性集成设计平台，该平台集成了从设计输入，仿真，逻辑综合，布局布线与实现、时序分析、芯片下载和配置、功率分析等几乎所有设计流程所需工具。限于篇幅只对

FPGA 设计流程涉及的常用工具加以介绍。根据设计流程与功能划分, ISE 的集成工具主要分为设计输入工具、综合工具、仿真工具、实现工具和辅助设计工具等 5 类<sup>[6]</sup>。

设计输入是工程设计的第一步, 设计输入工具主要包括 HDL 编辑器(HDL Editor)、状态机编辑器(StateCAD)、原理图编辑器(ECS)、IP 核生成器(Core Generator)和测试激励编辑器(HDL Bencher)等。HDL 语言方式由于其设计重用和代码移植性好受到广泛应用。

ISE 集成的综合工具主要有 Synplicity 公司的 Synplify/Synplify Pro, Synopsys 公司的 FPGA Compiler II/Express 和 Xilinx ISE 中的 XST 等。

ISE 集成的仿真工具主要有 Model Tech 公司的仿真工具 ModelSim 和测试激励发生器 HDL Bencher 等。ModelSim 是一个独立的仿真工具, 并且在工作的时候并不需要其他软件的协助, 在 ISE 集成开发环境中给 ModelSim 仿真软件预留了接口, 通过这个接口可以从 ISE 集成环境中直接启动 ModelSim 工具进行仿真。

ISE 集成的实现工具主要有约束编辑器(Constraints Editor)、引脚与区域约束编辑器(PACE)、时序分析器(Timing Analyzer)、FPGA 底层规划器(FPGA Editor)、芯片观察窗(Chip Viewer)和布局规划器(Floorplanner)等。

ISE 还集成了很多辅助设计工具, 主要工具包括以下几种: PROM 配置文件分割器(PROM File Formatter)可以完成配置文件的分割。iMPACT 配置器可以实现将配置文件下载到 FPGA/CPLD 或相应的存储器等功能。它的主要功能是下载、回读与校验配置数据, 生成 SVF 和 STAPL 文件。功能损耗器(XPOWER)是估计设计功耗的工具。

本文中 FPGA 设计采用 ISE 7.1 集成工具, 设计输入工具利用 Verilog HDL 的输入设计方式, 采用 Synplicity 公司的 Synplify Pro 7.3 作为 ISE 集成的综合工具完成综合过程, 仿真工具采用的是 ModelSim 5.5 和 ISE 自带的测试激励生成器 HDL Bencher 完成全部仿真, 从而完成了从设计输入到综合、布线、仿真、下载的工程。

### 1.2.3 FPGA/CPLD 的配置模式

由于 FPGA 器件采用的是 SRAM 工艺, 在断电的情况下 FPGA 内的配置数据就会丢失, 所以, 在采用 FPGA 器件的电子系统中通常将 FPGA 的配置数据存放于其兼容的 SPROM 中, 上电时由控制电路将 SPROM 中的配置数据装入 FPGA 器件中, 但是通常的 SPROM 价格昂贵, SPROM 芯片多为一次可编程芯片(OTP, One-time-programmable), 有的虽然可以多次擦写, 但调试阶段 FPGA 程序更新较快, 所以有必要在系统试验、调试阶段采用可重复使用的方式配置 FPGA。

Xilinx FPGA 的配置共有三种模式, 分别为并行(SelectMap)模式、串行(Serial)模式和边界扫描(Boundary Scan)模式<sup>[7]</sup>。本设计采用的是边界扫描配置方法, 它是 JTAG 标

准<sup>[8-9]</sup>，因此，有时也称 JTAG 配置模式，该模式只有四个专用的配置信号线，分别为 TCK(时钟)、TDI(数据输入)、TDO(数据输出)和 TMS(状态的控制)。JTAG 下载电缆通过标准并口与 PC 机相连，实现在线系统配置，它的构成为：与 PC 机并口相连的 25 针插座，与目标 PCB 板插座相连的 6 针插座和 25 针到 6 针的变换电路。下载时，将下载电缆连到 PCB 板上，就可以非常方便的实现在线系统配置，大大方便了电路的调试。

Xilinx 公司的所有 CPLD 产品均支持 JTAG 方式的下载，其由于为 ROM 型，所以其配置文件掉电不丢失，而且其扩展的 JTAG 指令集允许对编程模式和在系统调试进行控制，最少 10000 次的编程/擦除周期可实现系统区的重新配置和升级。

#### 1.2.4 Verilog HDL 与 VHDL 的比较

随着 EDA 技术的发展，使用硬件描述语言设计 CPLD/FPGA 成为一种趋势。目前最主要的硬件描述语言是 VHDL 和 Verilog HDL<sup>[10]</sup>。VHDL 发展的较早，语法严格，是一种全方位的语言，包括从系统到电路的所有层次设计，在描述风格上支持结构，数据流和行为三种形式的描述方式。而 Verilog HDL 是在 C 语言的基础上发展起来的一种硬件描述语言，语法较自由，用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。它们的共同特点是利于由顶向下设计，利于模块的划分与复用，可移植性好，通用性好，设计不因芯片的工艺与结构的变化而变化，更利于向 ASIC 的移植。

Verilog HDL 语言已经有 20 多年的历史了，因此 Verilog HDL 拥有广泛的设计群体，成熟的资源比 VHDL 丰富。同时 Verilog HDL 是从 C 语言发展而来的，相比 VHDL 更容易上手，其编程风格也更加简洁明了，是一种非常容易掌握的硬件设计语言<sup>[11]</sup>。作为专用集成电路(ASIC)设计人员，则必须首先掌握 Verilog HDL，因为在 IC 设计领域，90% 以上的公司都是采用 Verilog HDL 进行 IC 设计。在本文中选用 Verilog HDL 进行 FPGA/CPLD 的应用开发。

### 1.3 本文研究的主要内容和结构安排

本文主要对光电分选机的数据采集系统进行了研究，它以高分辨率、低噪声的线阵 CCD 器件为核心，以 Xilinx 公司的 FPGA 芯片 XC3S50 作为主控制器和处理器，通过 EPP 协议与计算机并口进行通信。本文是按照数据采集系统的各个模块的设计与实现过程来安排的。

论文的结构安排如下：

第 1 章在对光电分选机及其研究意义做了简要的介绍以后，详细的介绍了 FPGA/CPLD 技术及其开发环境。

第 2 章详细地阐述了 CCD 的工作原理，并对 CCD 器件的噪声进行了分析与抑制，然后论讨了本课题应用线阵 CCD 的原因。

第 3 章在详细介绍了光电分选机系统工作原理及其系统组成后，介绍了数据采集系统的结构设计。

第 4 章介绍了数据采集系统中各个模块的具体设计与实现过程。分析了 CCD 驱动电路设计与实现、CCD 输出信号处理电路的设计与实现、CCD 存储系统设计与实现、通信电路的硬件设计以及系统电源电路的实现。

第 5 章对系统的数据的传输与显示进行了详细的介绍。简单介绍了相机板与主控制器之间的通信的实现。重点介绍了基于 EPP 模式的数据采集系统显示的实现过程：给出了 EPP 并口的工作模式与 EPP 接口实现的软硬件设计与实现方法；并采用 FPGA 技术实现了一帧数据的传送。

第 6 章在简单介绍了系统的抗干扰设计以后，详细的介绍了系统的各个模块的调试与分析过程，并给出了示波器波形和上位机数据采集显示波形。

论文最后对全文进行了的总结，并提出了下一步的研究方向。

## 2 CCD 的特点及应用

CCD(Charge Coupled Device), 电荷耦合器件, 是 20 世纪 70 年代初发展起来的新型半导体集成光电器件。它是由美国贝尔实验室的 W.S.Boyer 与 G.E.Smith 于 1970 年提出的, 是在大规模硅集成电路工艺的基础上研制而成的模拟集成电路芯片<sup>[12]</sup>。

美国是最早开展 CCD 技术研究的国家, 也是目前投入人力、物力和财力最多的国家, 在此应用研究领域一直保持领先地位<sup>[13]</sup>。日本是目前世界上 CCD 的生产大国, 其产量居世界之首。日本政府非常重视 CCD 技术的开发和研究, 法国也是开展 CCD 技术研究较早的国家之一, 加拿大 DALSA 公司、英国通用电气公司(GEC)和荷兰的飞利浦(Philips)公司在 CCD 技术的研究与开发方面也很著名。我国研制 CCD 的单位也较多, 其中以机电部 44 所和 13 所水平较高, 但与国外相比差距较大。

CCD 技术是一项具有广泛应用前景的新技术, 三十多年来, 由于 CCD 具有自扫描、高分辨率、高灵敏度、重量轻、体积小、像素位置准确、耗电少、寿命长、可靠性好、信号处理方便、易于与计算机配合等优点, CCD 器件的研究及其应用取得了惊人的进展<sup>[14]</sup>。人们对它在摄像、信号处理和存储三大领域的应用十分重视, 特别是在图像传感器应用方面发展迅速, 已成为现代光电子学与现代测试技术中最活跃、最富有成果的新兴领域之一。

### 2.1 CCD 工作原理

CCD 的突出特点是以电荷作为信号, 而不同于其他大多数器件是以电流或者电压为信号。CCD 的基本功能是电荷的存储和电荷的转移, 因此 CCD 在工作过程中的主要问题是信号电荷的产生、存储、传输和检测。一个完整的 CCD 器件由光敏单元、转移栅、移位寄存器及一些辅助输入、输出电路组成。CCD 工作时, 在设定的积分时间内由光敏单元对光信号进行取样, 将光的强弱转换为各光敏单元的电荷多少, 取样结束后各光敏元电荷由转移栅转移到移位寄存器的相应单元中。移位寄存器在驱动时钟的作用下, 将信号电荷顺次转移到输出端<sup>[12]</sup>。

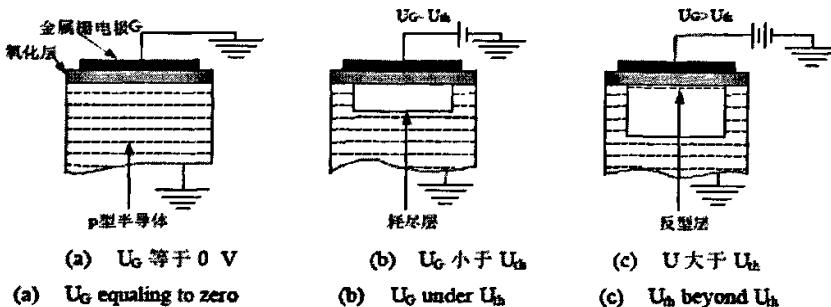

#### (1) 电荷的产生与存储

构成 CCD 的基本单元是半导体 MOS 结构(金属—氧化物—半导体)。如图 2.1 所示。在一定的偏压下, MOS 结构成为可存储电荷的分立势阱。当在栅极上加正偏压  $U_G$  后, 半导体的空穴被排空, 产生耗尽区(此时  $U_G$  小于半导体的阈值电压  $U_{th}$ )。当  $U_G > U_{th}$  时, 半导体与绝缘体表面上的电势很高, 以至于将半导体体内的电子吸引到表面, 形成一层

极薄但电荷浓度很高的反型层,如图 2.1(c)所示,反型层的存在表明了 MOS 结构存储电荷的基本功能。

图 2.1 单个 CCD 内部结构示意图

Fig.2.1 Single CCD inner structure

光照射到 CCD 硅片上时,在栅极附近的半导体体内产生电子空穴对,其多数载流子被栅极电压排开,少数载流子则被收集在势阱中形成信号电荷。信号电荷产生数量的多少,直接与入射光的强度及硅片曝光时间成正比。

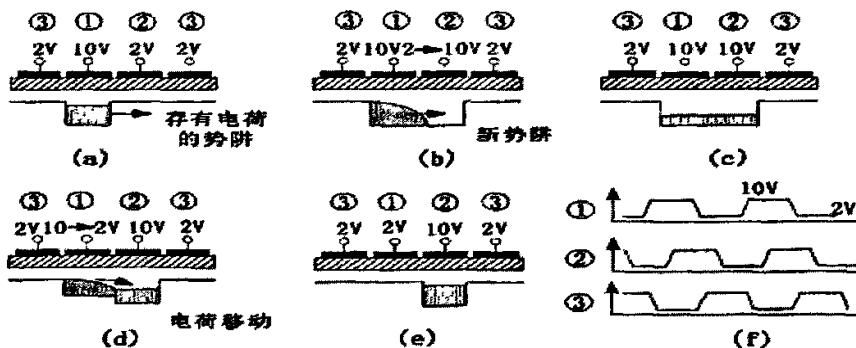

## (2) 电荷的转移

所谓电荷转移,就是指 MOS 结构势阱中的电荷从一个电极移向另一个电极的过程,如图 2.2 所示。取四个彼此靠得很近的电极来观察。开始时有一些电荷存储在偏压为 10V 的第二个电极下的势阱中,其他电极上均加有大于阈值的较低电压(例如 2V)。(a)为零时刻, (b)为  $t_1$  时刻,第二个电极仍保持为 10V,第三个电极上的电压由 2V 变到 10V,由于电极之间距离很小(只有几个微米),它们对应的势阱将合并在一起,原来的第二个电极下的势阱中的电荷将为两个势阱所共有,如图(c)。此后电极上的电压变为(d)所示。第二个电极电压由 10V 变成 2V,第三个电极电压仍为 10V,则共有的电荷转移到第三个电极下面的势阱中,如图(e)。此时深势阱及电荷包向右移动了一个位置。

将一定规则变化的电压加到 CCD 的各电极上,电极下的电荷包就能沿半导体表面按一定方向移动。通常把 CCD 电极分为几组,每一组为一相,并施加同样的时钟脉冲,这样就实现了电荷在势阱中的转移。用三相时钟驱动的 CCD 称为三相 CCD,如图(f)为三相 CCD 所需施加的时钟脉冲。在这里需要提及转移效率的问题,CCD 像元多,所需的转移次数也多。由于界面态及 Si 表面缺陷等因素的影响,电荷包都会残留一些电荷,为了取得高转移率,在结构上可以采取体内沟道 CCD 技术。在本文中采用了 P 沟道的 CCD,提高了器件的工作频率,降低了器件的噪声。

图 2.2 三相 CCD 电荷的转移过程

Fig.2.2 Charge transfer process of triple phase CCD

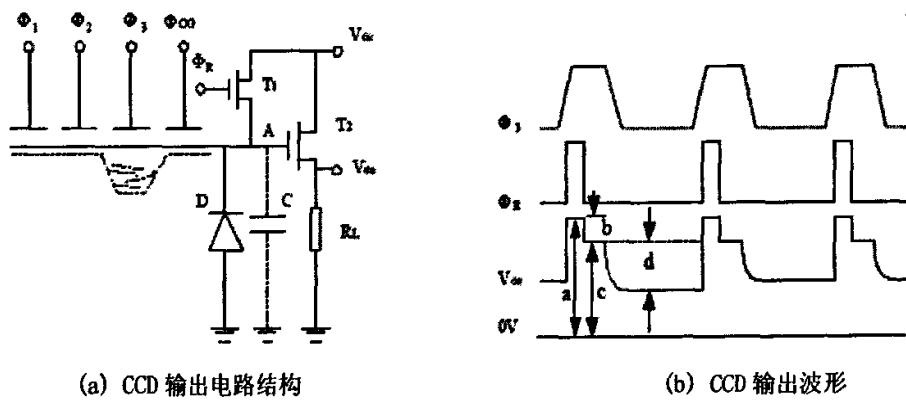

### (3) 电荷的输出

CCD 的最后一个栅极、输出栅、输出二极管分别相当于 MOS 管的源、栅、漏。CCD 最后一个栅极中的电荷包通过输出栅形成的“沟道”进入到输出二极管，然后通过一个输出耦合电路将调制在电荷包上的信息检测出来。CCD 电荷的读出多采用选通电荷积分器结构，以三相 CCD 为例说明电荷读出波形，如图 2.3 所示。图 2.3(a)为 CCD 输出电路结构；图 2.3(b)为 CCD 输出波形；图中 a 表示复位电压，b 表示读出电压，c 表示参考电压，d 表示信号电压。

(a) CCD 输出电路结构

(b) CCD 输出波形

图 2.3 CCD 输出电路结构与输出信号波形

Fig.2.3 The output circuit structure and output signal waveform of CCD

$T_2$  的输出电平  $V_{os}$  被复位到一个固定的略低于  $V_{cc}$  的正电平上，此电平称为复位电平。当  $\Phi_R$  正脉冲结束后， $T_1$  截止，由于  $T_1$  存在一定的漏电流，这漏电流在  $T_1$  上产生一

个的管压降，使输出点有一个下跳，其下跳值称为馈通电压。当  $\Phi_R$  为正时， $\Phi_3$  也处于高电位，信号电荷被转移到  $\Phi_3$  下的势阱中，由于输出栅压  $V_{os}$  是一个比  $\Phi_3$  低的正电压，因此信号电荷仍被保持在  $\Phi_3$  势阱中，但随着  $\Phi_R$  正脉冲结束，并变得低于  $V_{os}$  电平时，这时信号电荷进入电容 C 后，立即使 A 点电位下降一个与信号电荷量成正比的电压，即信号电荷越多，A 点电位下降越多。与此相应， $T_2$  输出电平  $V_{os}$  也随之下降，其下降幅度才是真正的信号电压，CCD 输出信号波形如图 2.3(b)所示。

## 2.2 CCD 器件的噪声及其抑制方法

CCD 图像传感器的输出信号是空间采样的离散模拟信号，其中夹杂着各种噪声和干扰。CCD 输出信号处理的目的是在不损失图像细节并保证在 CCD 动态范围内，图像信号随目标亮度线性变化时尽可能消除这些噪声和干扰。为了提高信噪比，必须对 CCD 输出噪声种类、特性有所了解，然后才能有针对性地对噪声进行抑制。CCD 器件在光注入引入的噪声主要是光子散粒噪声，在电荷转移时引入的噪声主要是界面态的俘获噪声，CCD 的输出噪声主要是指复位噪声，此外 CCD 还存在暗电流噪声、低频噪声( $1/f$  噪声  $1/f^2$  噪声)和高频噪声。以下是 CCD 输出的主要噪声和抑制方法<sup>[15-16]</sup>：

### (1) 散粒噪声

光注入光敏区产生信号电荷的过程可看作独立、均匀连续发生的随机过程，单位时间产生的光产生电荷数目并非绝对不变，而是在一个平均值上作微小波动，这一微小的起伏便形成散粒噪声。散粒噪声与频率无关，在很宽的频率范围内都有均匀的功率分布，所以散粒噪声通常又称为白噪声。应用传统的基于傅氏变换的信号去噪方法，在处理信号和噪声的频带重叠部分尽可能小时，可以使信号在频域内通过而噪声不通过的方法起到滤波的作用，但当信号和噪声的频带重叠部分很大时，这种方法就无能为力了。一种更好的方法是利用小波理论，构造一种既能降低图像噪声又能保持图像细节信息的算法。这种方法需要使用 DSP(Digital Signal Processing)芯片或计算机进行处理。

### (2) 暗电流噪声

图像传感器体内和表面不可避免地含有杂质，由于热激发使它们产生的电子被势阱单元捕获，这些热激发电子噪声被描述成暗电流噪声，在应用中对器件采取制冷措施，当温度降到-30℃～-50℃时，暗电流噪声就小到无足轻重的程度。也可以事先对一白背景成像，获得的图像分布即为暗电流噪声，在以后获取的图像中减去这一图像分布，基本上就可以消除暗电流噪声。

### (3) 复位噪声

复位噪声的产生于 CCD 输出结构有关，通常产生于浮置扩散输出结构的 CCD 中，如

图2.3(a)。一次信号的读取都以单个电荷包的形式出现在放大器的栅节点上。每个信号电荷包产生的电压变化被读出后，输出MOSFET的栅节点需加以复位。当复位脉冲到来时，复位管MOSFET导通，导通沟道电阻 $R_{on}$ 产生的电阻热噪声加在电容C两端。复位过程等效于漏电压通过电阻 $R_{on}$ 对电容C充电。由于电阻热噪声的影响，每一次复位操作都将产生复位噪声。

在 CCD 数据采集的设计中，要尽可能地采集到精确的 CCD 信号，并降低 CCD 的噪声。复位噪声是 CCD 输出的主要噪声，采用相关双采样 CDS(Correlated Double Sampling)技术进行抑制，它不仅可以较好的滤除复位噪声，而且对 CCD 的 $1/f$  噪声也有一定的滤除作用，因此被广泛地用于 CCD 图像传感器输出视频信号电路中。下面将从理论分析角度介绍相关双采样技术如何抑制复位噪声<sup>[17]</sup>。

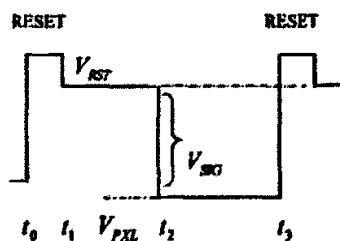

CCD的信号输出波形如图2.4所示。收集电容根据信号电荷的数目形成视频电压信号，FET消除在 $t_0$ 到 $t_1$ 复位脉冲期间因收集电容直接连到参考电压而形成的信号。从 $t_3$ 时刻又周期性的开始进行同样的操作。脉冲反馈到输出，但是在复位脉冲结束时迅速建立到复位电平 $V_{RST}$ 。在此之后的 $t_2$ 时刻，信号到达输出节点，输出电平建立为 $V_{PXL}$ ，这是从复位电平减去 $V_{SIG}$ 的值， $V_{RST}$ 和 $V_{PXL}$ 之间的差值就表现了视频信号自身的幅值。 $t_1 \sim t_2$ 期间采样信号为 $V_{SAMPLE1}$ ， $t_2 \sim t_3$ 期间采样信号为 $V_{SAMPLE2}$ 。设

$$V_{SAMPLE1} = V_{RST} \quad (2.1)$$

$$V_{SAMPLE2} = V_{PXL} = V_{RST} - V_{SIG} \quad (2.2)$$

则由式(2.1)与(2.2)可以得到：

$$V_{OUT} = V_{SAMPLE1} - V_{SAMPLE2} = V_{SIG} \quad (2.3)$$

图 2.4 CCD 输出波形图

Fig. 2.4 CCD output waveform

CDS 对复位噪声、 $1/f$  噪声、 $1/f^2$  噪声进行抑制。对于复位噪声，只要在同一像素周期内的暗电平参考区间和信号电平区间进行两次采样，那么这两次采样的复位噪声是

相关的, 将两次采样值模拟相减后, 复位噪声从输出信号中抑制了, 从而得到了如式(2.3)表示的真实视频信号  $V_{\text{SIG}}$ , 这就是著名的相关双采样法。

### 2.3 CCD 种类及器件选择

CCD 器件按其感光单元的排列方式分为线阵 CCD 和面阵 CCD 两类。线阵 CCD 结构简单, 成本较低。由于其单排感光单元的数目可以做的很多, 在同等测量精度的前提下, 其测量范围可以做的较大, 并且由于线阵 CCD 实时传输光电变换信号和自扫描速度快、频率响应高, 能够实现动态测量, 并能在低照度下工作, 所以线阵 CCD 广泛地应用在产品尺寸测量、分类和产品表面质量评定中<sup>[18]</sup>。

面阵CCD结构比线阵CCD复杂、成本较高, 其广泛地应用在平面曲线轮廓的检测中, 且检测的直观性好。但是在同等测量精度和检测范围的情况下, 面阵CCD感光单元的数目比线阵CCD多得多, 而且面阵CCD器件的驱动电路及相应处理电路复杂, 对其信号的采集需要较大的外部数据存储器, 且采集速度慢, 限制了整个系统的检测频响。

根据光电分选机的工作原理, 我们在线阵 CCD 传感器的选择上着重考虑了以下几个性能参数: 工作速率、分辨率、灵敏度和动态范围。因为记录的是快速运动目标, 故对所用 CCD 的扫描速度有很高的要求。分辨率的高低则直接影响着扫描图像的细节再现程度。由于器件工作频率高, 故光积分时间较短, 只有选用灵敏度高、动态范围大的 CCD 才能保证输出视频信号不被淹没于暗电流噪声中, 确保扫描图像的质量。

### 3 光电分选机系统

#### 3.1 光电分选机简介

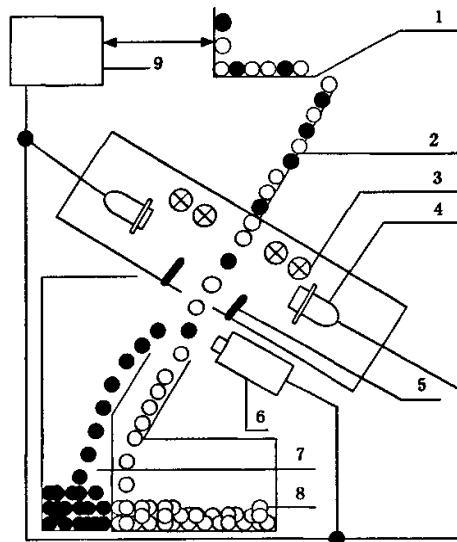

##### (1) 分选过程

光电分选机在工作前, 被选物料的各种参数由用户通过人机交互界面设定。在分选过程中, 被选物料首先由进料斗通过电磁振动给料器配送到各个分选通道中, 然后通过溜槽的加速使物种以恒定的速度下落进入光电系统。光电系统在灯光的照射下, 从前后两面由CCD摄像头对物种进行扫描, 并将CCD输出的视频信号经高速模数转换后, 进行数据的处理和分析, 给出次品的位置信号。由判别次品位置信号所产生的延时时间差正好等于被选物料从视镜下落至喷射器之间的时间差, 当次品到达喷射器位置时, 随即驱动气枪喷射高速气流, 将次品吹出, 使其落入次品槽, 而合格品则继续下落进入出料斗, 从而完成物种的一次分选。为了提高分选精度, 落入次品槽的物料还可进行二次分选。同时在分选过程中, 还可通过触摸屏对分选参数进行反复调节, 以使分选效果达到最佳。

图3.1为分选过程示意图。

1) 电磁振动给料器; 2) 分选通道; 3) 光源; 4) CCD 摄像头; 5) 背景板; 6) 喷射气枪; 7) 次品槽;

8) 合格品槽; 9) 电控系统

图 3.1 分选过程示意图

Fig. 3.1 Sketch map of the sorting process

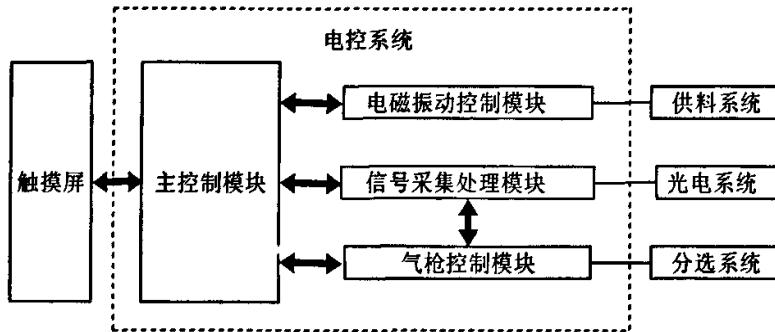

## (2) 系统结构

光电分选机形式多样, 结构各异, 但归纳起来, 可将它分为供料系统、光电系统、分选系统和整机的电控系统四个组成部分<sup>[19]</sup>。其整机结构框图如图 3.2 所示。

图 3.2 整机结构框图

Fig. 3.2 Structure of the whole system

### ① 供料系统

供料系统的作用是为光学系统的观察检测和分选系统的分选工作提供保障。它将待物料调节整理, 保证其在观察区内能被逐个地观察检测, 在分选区能被方便地分选剔除。一般由料斗、振动喂料器和溜槽等组成。待分选物料由进料斗进入振动喂料器, 通过振动和导向机构使物料自动排列成一行行连续的线状细束, 再通过溜槽加速后以恒定的速度抛飞进入光电系统的探测区内。

### ② 光电系统

光电系统是光电分选机的关键部位, 其作用主要是对待选物料进行光学检测分析, 为分选系统提供准确无误的分选信息。它一般由光源、背景板、接收器和镜头组成。目前常用的光源有荧光灯、氙灯和钠灯等。背景板选用的颜色应接近于合格品颜色, 并且通过调节其角度, 使背景板产生的反射信号与合格品产生的反射信号近乎等效, 以达到较好的分选效果。接收器即光电传感器, 可将接收面上的光信号转换成电信号, 目前应用于分选机上的主要有硅光电池及电荷耦合器件(CCD), 硅光电池虽成本低廉, 但分辨率低, 对有小病斑的颗粒及浅色杂质识别能力较差, 而 CCD 与硅光电池相比, 具有较高的分辨率, 得到了广泛应用。

### ③ 分选系统

分选系统主要是将光学系统检测发现的次品分选剔除。对于颗粒状物料的分选, 常用的方法主要是用压缩空气喷吹。当物料进入分选系统后, 合格品沿正常轨道排出, 次

品则被气枪喷嘴发出的脉冲式压缩空气吹离正常运动轨道，而落入次品槽。所以要获得准确无误的分选，就要求分选系统从接收光学系统的分选信号到分选机构动作这一延时时间要与物料从检测点到分选点的运动时间相匹配。

#### ④ 电控系统

电控系统包括主控制系统、检测系统、电磁振动给料系统和气枪控制系统。它控制着整机各机构的工作，主要是对分选流量进行调节，检测和识别次品物料和合格品物料，启动分选机构完成分类操作，对分选参数进行存储，而且还可进行故障的自诊断及处理，从而降低对操作人员的依赖性，提高系统的自动化程度。

### 3.2 总体电路结构设计

通过对光电分选机工作过程和系统结构的分析，光电分选机的控制系统是由主控制系统、信号采集处理系统、电磁振动给料系统和气枪控制系统协同工作的系统。主控制系统控制和管理其它三个系统，及温度、电源电压、开关信号、指示灯等外围电路等<sup>[20]</sup>；信号采集处理系统采用双面光学传感器检出技术对  $n$  个分选滑道的物料进行检测和识别处理，信号采集处理系统包括  $2n$  个 CCD 摄像机，每板控制 1 个 CCD 摄像机进行扫描工作并对接收到的扫描信号进行识别处理给出异物位置信息；电磁振动给料系统按照主控制系统设定的工作参数进行工作，将物料调节整理，保证物料在观察区内能被逐个地观察检测；气枪控制系统接收检测系统所发送的异物位置信息，收到后，气枪控制板控制电动气阀将高压气流喷出，把物料中的次品分选剔除，系统每组滑道有 45 个溜槽，每个溜槽对应 2 个气动喷嘴，所以 1 滑道对应 90 个气动喷嘴和 6 个气枪控制板，1 个气枪控制板控制 15 个气动喷嘴。

对于整个系统的通信连接设计如下：触摸屏通过 RS485 接口与主控制系统连接；主控制系统通过 RS485 发送数据线与电磁振动给料控制系统连接；主控制系统在与信号采集处理系统连接时，发送数据线和接收数据线经每组滑道的通信板分别与 12 块信号板连接，使 12 块信号板共用接收和发送数据线组；信号采集处理系统连接气枪控制系统，每块信号板分别与 8 块气枪控制板连接。这样，通过建立主控制系统与触摸屏间的异步串行通信，以及其与各子系统间的同步串行通信就可以将整个控制系统有机的结合在一起。

### 3.3 数据采集系统结构设计

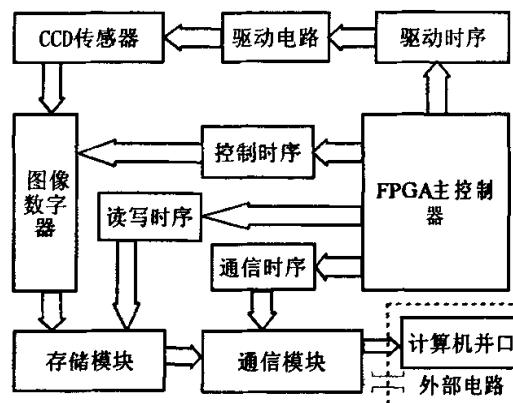

本课题实现了一种基于 FPGA 的，以高分辨率、低噪声线阵 CCD 器件为核心的数据采集系统。系统的实现包括线阵 CCD 驱动电路模块，图像信号的调理、高速采集和存储电路模块，数据传输中通信电路模块，提供系统所需电压的电源电路模块以及与计

计算机并口通信的电路模块。图 3.3 是数据采集系统整体框图, 数据采集系统流程如下: CCD 图像传感器通过一组时序驱动脉冲控制实现对目标图像的实时光电转换与信号的读出, 输出的视频信号经过图像数字器进行调理、高速 A/D 转换, 将模拟信号实时地转换成数字信号, 数字图像信号经外部存储器缓存通过同步串行通信接口发出, 通过通信板将采集到的信号传送给计算机并口, 由计算机将采集到的信号显示出来。数据采集系统同时也以串口通信的方式与主控制系统和分选系统进行通信。

图 3.3 数据采集系统整体结构框图

Fig. 3.3 The configuration of data acquisition system

光电分选机数据采集系统主要由相机控制板实现。相机控制板由相机主板和相机电源板构成。CCD及其驱动电路、图像数字器、外部存储器、FPGA芯片、SPROM和系统晶振都分布在相机主板中; SPROM用于存放FPGA的配置数据, 在系统试验、调试阶段, 采用可重复使用的边界扫描方式在线配置FPGA, 等调试成功、系统稳定后, 再把SPROM插在插槽中存放配置数据。CCD传感器插在相机主板的插槽中, 通过相机镜头对图像进行扫描。FPGA配置下载接口和通过下在线与计算机相连FPGA的在线配置。接口A是相机控制板与主控制器的通信接口, 在实验阶段还可以作为与计算机并口通信接口, 将采集到的数据在计算机中显示; 接口B是相机板与气枪控制器的通信接口, 同时也是电源的接口; 拨码开关可对FPGA芯片I/O管脚进行短脉冲控制, 当开关闭合后与地相连, 可以在系统调试阶段作为系统的复位和请求引脚; 电源电路用于提供数据采集系统所需三种电压值; MC1488和MC1489分别是发送驱动器和接收驱动器, 负责相机控制板与主控制器、气枪控制器的通信。可以通过一个50针插槽把相机主板和电源板连接在一起, 构成一个完整的相机控制器, 便于系统的调试与升级。数据采集系统可以通过接口电路与计算机相连实现采集数据的显示。

相机控制板选用FPGA芯片XC3S50作为主控制器和处理器，对数据进行高速并行处理。XC3S50是Xilinx公司推出的一款Spartan 3系列的FPGA，支持3.3V电压。它的封装选择表贴的PQ208，共有208个管脚。XC3S50芯片内部系统总门数达到5万门，共有1728个逻辑单元，192个CLB，带有片上可编程分布式RAM，可编程RAM为72K。其内部有专用的乘法器4个，能够进行高性能的算术处理功能；有两个专用的时钟管理器，具有灵活、完善的频率合成、相移、时钟偏移消除等功能<sup>[21]</sup>。芯片最高工作频率可达326MHz，因此具有很强的数据处理潜力。由于其性能与内部逻辑资源丰富，满足系统的设计需求，而且价格相对比较便宜，所以是一款低价格、高性能的FPGA芯片，因此十分适用于本系统的设计与应用。

## 4 CCD 数据采集系统设计与实现

### 4.1 CCD 驱动电路设计与实现

从固体图像传感器的工作原理可知,为了保证 CCD 工作稳定可靠,必须由外部提供适当的驱动信号和工作电压。这些驱动信号的质量将直接影响输出信号的质量,因此 CCD 驱动电路的设计是极其重要的。本节将对高速单沟道线阵 CCD 图像传感器 TP1024P 芯片的驱动电路进行介绍。

#### 4.1.1 CCD 的特点、结构和工作原理

TP1024P 芯片是具有 1024 个光敏像元的、具有低噪声、高速度和高灵敏度等优点二相图像传感器。像元尺寸为  $14\mu\text{m} \times 14\mu\text{m}$ ; 像素读出率 40MHz; 动态范围为 2500:1; 光谱范围为 250-1000nm; 行读出率 70KHz。除了上述特点以外,它还具有超低的图像延迟、电子曝光门和抗曝光控制等功能<sup>[22]</sup>。

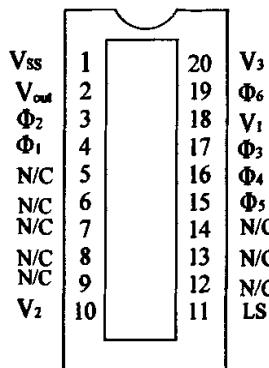

TP1024P 芯片具有双列直插式的封装形式,它需要 6 路驱动信号,即复位信号  $\Phi_6$ 、转移信号  $\Phi_3$ 、两相时钟信号  $\Phi_1$  和  $\Phi_2$ 、光电信号  $\Phi_4$ 、电子曝光控制信号  $\Phi_5$ 。其驱动电压列表如表 4.1, 管脚配置图如图 4.1。

表 4.1 CCD 的驱动电压列表

Tab. 4.1 Drive voltages of CCD

| 信号       | 功能      | 状态 | 电压(V) | 耐压偏差范围     |

|----------|---------|----|-------|------------|

| $\Phi_1$ | 水平移位时钟  | 高  | 5     | $\pm 5\%$  |

|          |         | 低  | 0     |            |

| $\Phi_3$ | 传输门     | 高  | 8     | $\pm 10\%$ |

|          |         | 低  | 0     |            |

| $\Phi_4$ | 光电信号门   | 高  | 8     | $\pm 5\%$  |

|          |         | 低  | -4    |            |

| $\Phi_5$ | 曝光控制门   | 高  | 4     | $\pm 5\%$  |

|          |         | 低  | -4    |            |

| $\Phi_6$ | 复位门     | 高  | 8     | $\pm 10\%$ |

|          |         | 低  | 0     |            |

| $V_1$    | 输出门     | -  | 3     | $\pm 5\%$  |

| $V_2$    | 内部放大器电压 | -  | 12    | $\pm 5\%$  |

| $V_3$    | 放大器复位电压 | -  | 9.5   | $\pm 5\%$  |

图 4.1 CCD 管脚配置图

Fig. 4.1 The pin configuration chart of CCD

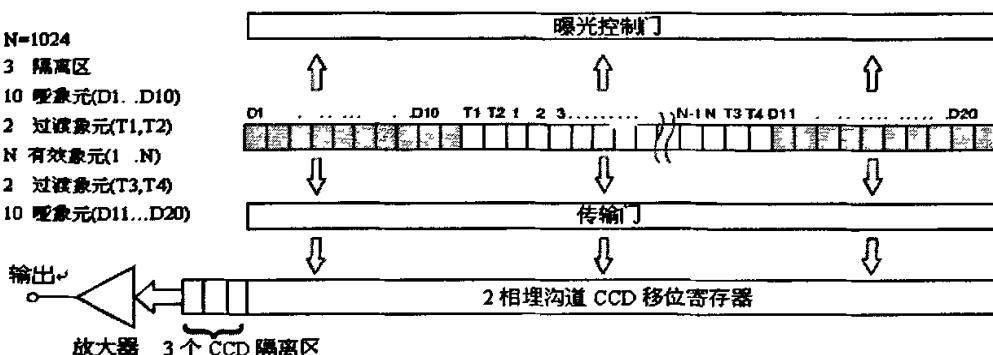

图 4.2 为 CCD 的内部结构图。它由 1048 个光电二极管构成光敏元阵列，其中前 12 个和后 12 个光敏元是作为暗电流检测被遮蔽的，中间的 1024 个光电二极管是曝光光敏单元，光敏元阵列总长为 14.336mm。光敏元阵列与转移区-移位寄存器是分开的，曝光控制门和传输门在光敏阵列两侧。曝光控制门控制 CCD 的曝光时间，传输门控制电荷从光电二极管到移位寄存器的运动，当传输门置高，电荷在光电信号的驱动下从光电二极管进入移位寄存器中，移位寄存器在转移脉冲的驱动下使电荷向左转移经放大器输出，形成视频脉冲信号。

图 4.2 CCD 内部结构图

Fig. 4.2 The inner structure of CCD

CCD 需要 6 路驱动信号，各个驱动信号的时序关系如波形图 4.3 所示。从图中可以看到在两个  $\Phi_4$  和  $\Phi_6$  信号之间是一帧图像数据；  $\Phi_6$  脉宽大于  $\Phi_4$  脉宽，一个  $\Phi_6$  信号对应一个  $\Phi_1$  信号，但其脉宽小于  $\Phi_1$ ；  $\Phi_1$  与  $\Phi_2$  反相。

图 4.3 CCD 时序波形图

Fig. 4.3 CCD's time sequence waveform chart

#### 4.1.2 CCD 时序分析

CCD 正常工作时, 有 27 个虚假像素输出(如图 4.3 所示), 由于该器件有 1024 个曝光光敏元, 所以在一个周期内至少要有 1051 个  $\Phi_1$  脉冲。 $\Phi_6$  是使输出二级管复位的复位管控制脉冲信号, 当  $\Phi_6$  为高电平时, 复位管导通, 输出放大器被复位; 当  $\Phi_6$  为低电平时, 复位管截止, 光电荷转换为电压信号输出, 复位一次输出一个信号, 脉冲占空比为 1:7。两相时钟信号  $\Phi_1$  和  $\Phi_2$  的频率与  $\Phi_6$  相同, 同时为了避免 MOS 电容中的信号电荷包向模拟移位寄存器转移不完全的情况, 要求  $\Phi_1$  和  $\Phi_2$  在并行转移时有一个大于转移信号  $\Phi_3$  持续时间的宽脉冲, 所以在设计驱动信号  $\Phi_1$  和  $\Phi_2$  时应考虑两部分内容: 一是根据系统时钟 4 分频产生方波电路, 二是形成所需要的宽脉冲, 如图 4.3 的时序波形所示。转移信号  $\Phi_3$  是使 MOS 电容中的信号电荷转移到移位寄存器中的转移栅控制信号,  $\Phi_3=1$  的时间应小于  $\Phi_1$  的宽脉冲时间。一旦转移信号  $\Phi_3$  置高电平, 光电图像信号  $\Phi_4$  以高电平来实现电荷转移,  $\Phi_4=1$  的时间应小于  $\Phi_3=1$  的时间宽度。电子曝光控制信号  $\Phi_5$  用于控制 CCD 曝光量的积分时间, 当  $\Phi_5$  的上升沿到来时, CCD 所有光电二极管清零, 开始积分, 当  $\Phi_5$  的下降沿到来时, 积分完成, 在光电二极管正常收集电荷包时,  $\Phi_5$  置低电平状态。

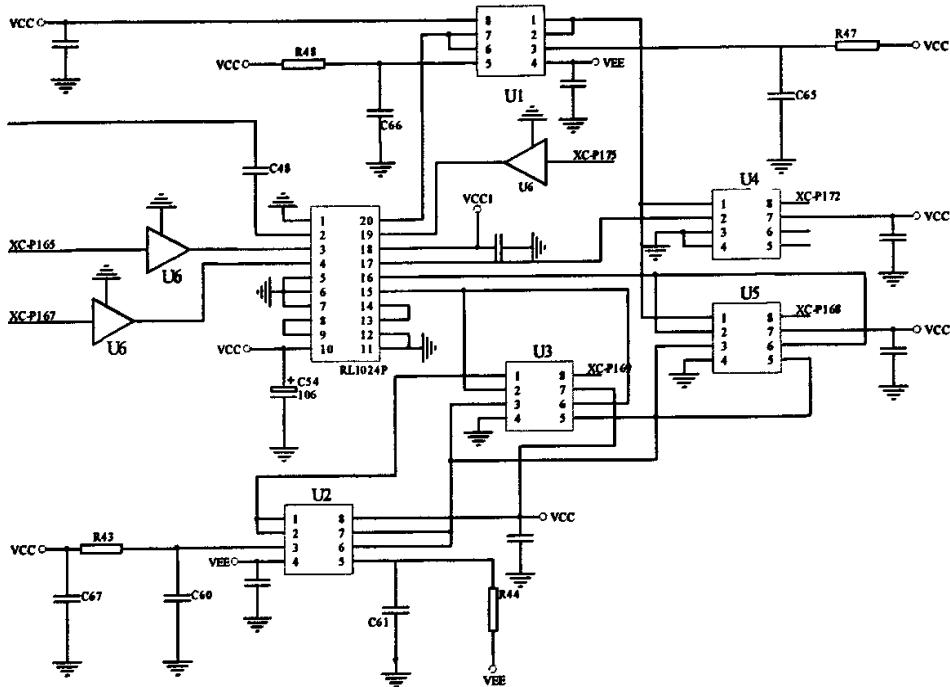

#### 4.1.3 CCD 驱动接口电路设计

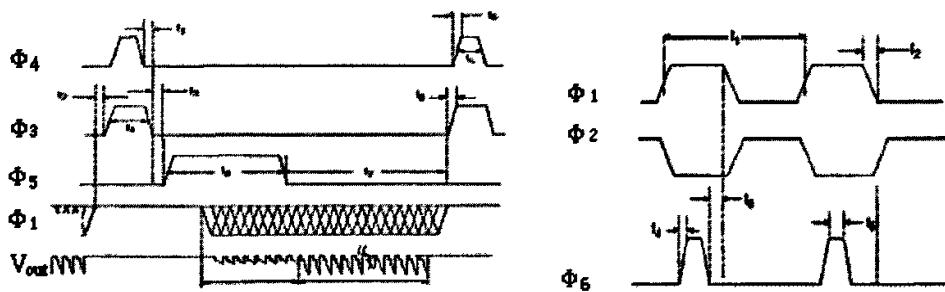

驱动电路是时序逻辑电路与 CCD 传感器之间的电学接口, 它提供了 CCD 正常工作要求的驱动电压的幅度。为了提高系统的集成度, 降低系统的功耗, 减小相机的体积和重量, CCD 的所有时序控制都是由 FPGA 产生的。从 XC3S50 发出的信号高电平都是 3.3V, 而 CCD 对信号电平的要求却不同, 如表 4.1 所示。从表中我们可以看出, CCD

需要 8 种不同的驱动电平钟，因此必须设计合理的硬件电路来能提供这 8 种不同驱动电平的输出。图 4.4 所示为 CCD 驱动电路的硬件电路原理图，此硬件电路提供 CCD 需要的 8 种不同驱动电平。

图 4.4 CCD 驱动电路的硬件原理图

Fig. 4.4 The hardware schematic of CCD drive circuit

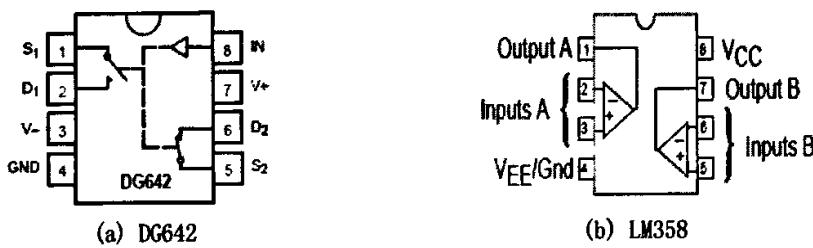

图 4.4 中所示的 U1 和 U2 为 MOTOROLA 公司生产的超低噪声双运算放大器 LM358，它的管脚结构图如图 4.5(b)所示，图 4.4 中 U1 为同相运算放大器，1 脚的电压值等于 3 脚的电压值，5 脚的电压值等于 7 脚的电压值。

图 4.5 DG642 和 LM358 的管脚图

Fig. 4.5 Pins structure of DG642 and LM358

图 4.4 中所示的 U3、U4 和 U5 是 TTL 驱动器 DG642，它应用在  $\Phi_3$ 、 $\Phi_4$  和  $\Phi_5$  的双极性时钟输出(例如-5V 到 5V)，时钟上限频率达 10MHz。DG642 的管脚结构图如图 4.5(a)所示，8 脚为输入脚，1 脚和 2 脚构成内部开关 switch1，5 脚和 6 脚构成内部开关 switch2。当 8 脚为高电平时，DG642 的 switch1 关闭、switch2 开启，反之，当 8 脚为低电平时，DG642 的 switch2 关闭、switch1 开启。

74HCT244TV 是 8bit 的快速 CMOS 线驱动器，它有 20 个管脚，图中用 U6 来表示，它采用 4 个端口并行输出来增加电流驱动能力，应用在  $\Phi_6$ 、 $\Phi_1$  和  $\Phi_2$  的单极性时钟输出(例如 0V 到 5V)，它的工作电压接 5V，信号时钟频率可高达 40MHz。在 CCD 的驱动时序中， $\Phi_1$ 、 $\Phi_2$  和  $\Phi_6$  的信号驱动时钟频率都为 10MHz，均低于 74HCT244TV 信号时钟频率的上限。

#### 4.1.4 基于 FPGA 的 CCD 时序逻辑控制的设计与仿真实现

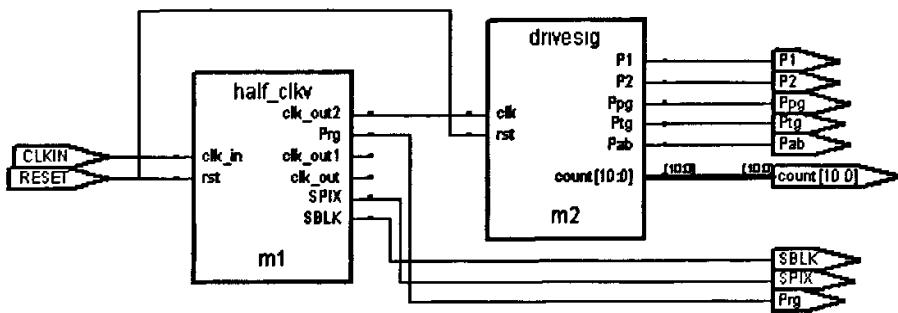

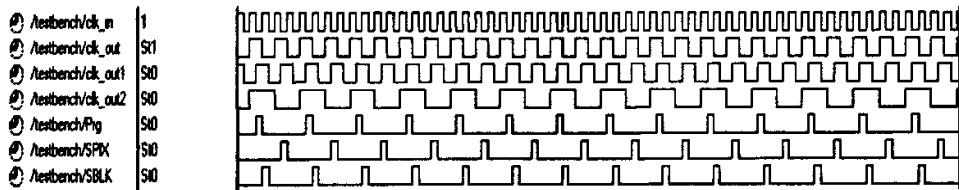

如图 4.6 所示可以看出各个模块的逻辑关系非常简洁，整个设计由两个模块完成。half\_clkv 模块是时钟生成模块，主要产生复位信号和一些后面要用到的中间变量。系统源时钟输入 CLKIN 为 20MHz，clk\_out 是它的 2 分频输出，输出引脚 clk\_out1 是 clk\_out 的 90 度相位移位信号，输出引脚 clk\_out2 是系统的 4 分频输出。如图，复位信号  $Prg=(clk\_out \cdot clk\_out1) \cdot clk\_out2$ ；输出引脚  $SPIX=(clk\_out \cdot clk\_out1) \cdot (\overline{clk\_out2})$ ， $SBIK=(\overline{clk\_out} \cdot clk\_out1) \cdot clk\_out2$ ，SPIX 和 SBIK 是后续实现图像数字器控制脉冲的两个中间变量。

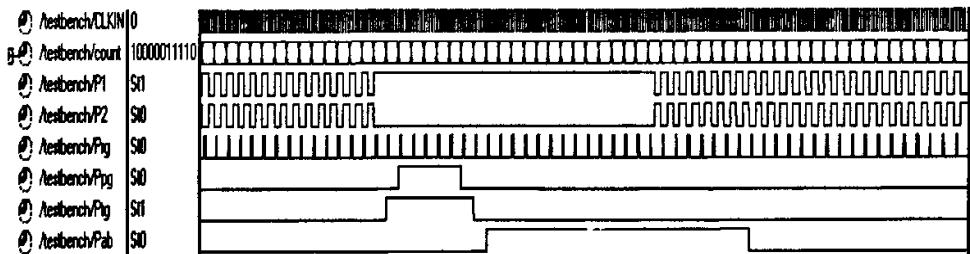

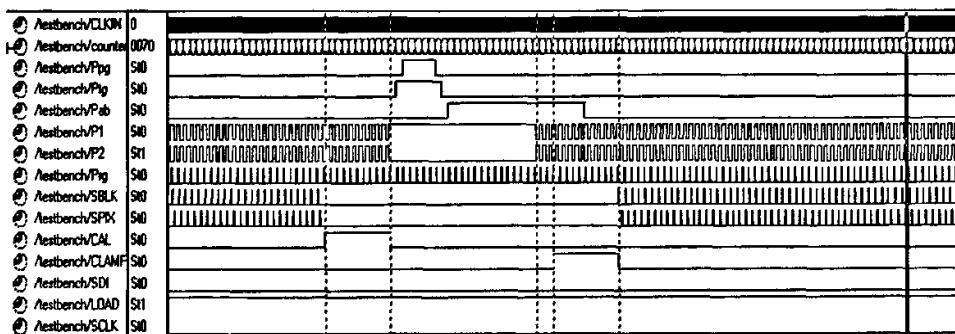

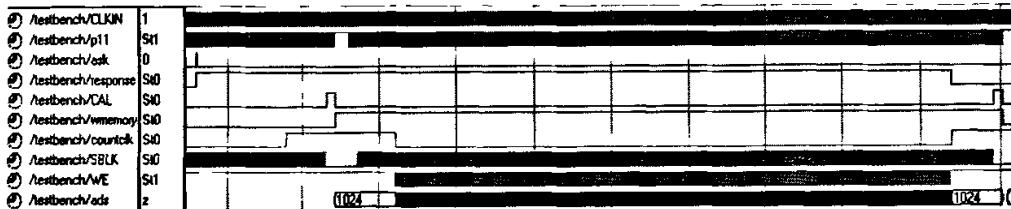

而 drivesig 模块主要产生 CCD 的驱动信号和 11 位计数器。图 4.7 示出了 TP1024P 的驱动时序经 FPGA 实现后的仿真结果图，图中所示的 count 为 11 位的计数器，用此移位计数器来控制实现两相时钟信号  $\Phi_1$  和  $\Phi_2$  的宽脉冲、转移信号脉冲  $\Phi_3$ 、光电图像信号脉冲  $\Phi_4$  和电子曝光控制信号脉冲  $\Phi_5$ 。它是以系统时钟的 4 分频 clk\_out2 的时钟节拍进行移位计数的，当每个 clk\_out2 节拍的上升沿到来时，计数器累计加 1。当 count 对移位脉冲进行计数满 1053 时，时钟信号的宽脉冲 p1 开始置 1；当计数器计数到 1054，转移信号 Ptg 置 1；计数到 1055 时，光电图像信号 Ppg 置 1；计数到 1060 时，Ppg 置 0；计数到 1061 时，Ptg 置 0；计数到 1069 时，电子曝光控制信号 Pab 置 1；计数到 1074 时，宽脉冲信号 p1 置 0；此时，计数器复位到 0 开始重新计数。时钟信号  $P1=clk\_out2 + p1$ ，时钟信号  $P2=\overline{P1}$ 。信号 Pab 曝光量的积分时间可由计数器 count 控制。

图 4.6 CCD 驱动时钟脉冲产生电路

Fig. 4.6 Generation circuit of drive clock pulse of CCD

图 4.7 CCD 驱动电路中各时钟之间关系的仿真图

Fig. 4.7 The clocks relation's simulation in CCD drive circuit

图 4.8 CCD 驱动时序仿真图

Fig.4.8 CCD's driving time sequence simulation chart

从仿真图 4.8 可以看出各种脉冲信号之间的时序关系完全符合线阵 CCD 的要求。

## 4.2 CCD 输出信号处理电路设计与实现

第二章已经就 CCD 的噪声进行了简单介绍，其中对图像质量影响较大的噪声是复位噪声、暗电流噪声。前面已经分析可知相关双采样是抑制复位噪声的有效办法。暗电流噪声具有随机性，由于环境的不同，CCD 的每一次工作时暗电流形成的噪声电压都会不同，所以电路必须具有实时检测和校正能力。相关双采样电路和黑电平补偿电路都可以用分立元件来实现，但技术难度较大、调试困难，而且所需器件较多，不利于系统

的集成和小型化，而且稳定性也不高。现在有些公司专门生产用于 CCD 输出信号处理的芯片，例如图像数字器 XRD989855 和 XRD98L56，不仅具有相关双采样、自动暗电平补偿功能，而且还具有可编程增益控制放大和 A/D 功能，性能和价格指标也令人满意。本系统采用了图像数字器对 CCD 的输出信号调理和数字化。

#### 4.2.1 图像数字器简介

XRD98L59 是低功耗的数字式动静态的 CCD 图像数字器，它包括有相关双采样器、8-bit 的数字可编程增益的 PGA，10-bit 模数转换器以及有哑像元平均器、噪点像元切割器和数字噪声抑制滤波器的自动偏移校正电路<sup>[23]</sup>。其主要性能参数如表 4.2 所示：

表 4.2 图像数字器主要性能参数表

Tab. 4.2 Main feathers of image digitizers

| 性能名称     | 参数            |

|----------|---------------|

| 模数转换器分辨率 | 10-bit        |

| 最大采样速率   | 20MHz         |

| 可调放大增益   | 6dB-38dB      |

| 相关双采样电路  | 有             |

| 采样的时钟极性  | 软件可调          |

| 采样点位置    | 3.5ns-17.6ns  |

| 控制接口     | SPI           |

| 工作电压     | 2.7V-3.6V     |

| 封装形式     | 28 脚 TSSOP 封装 |

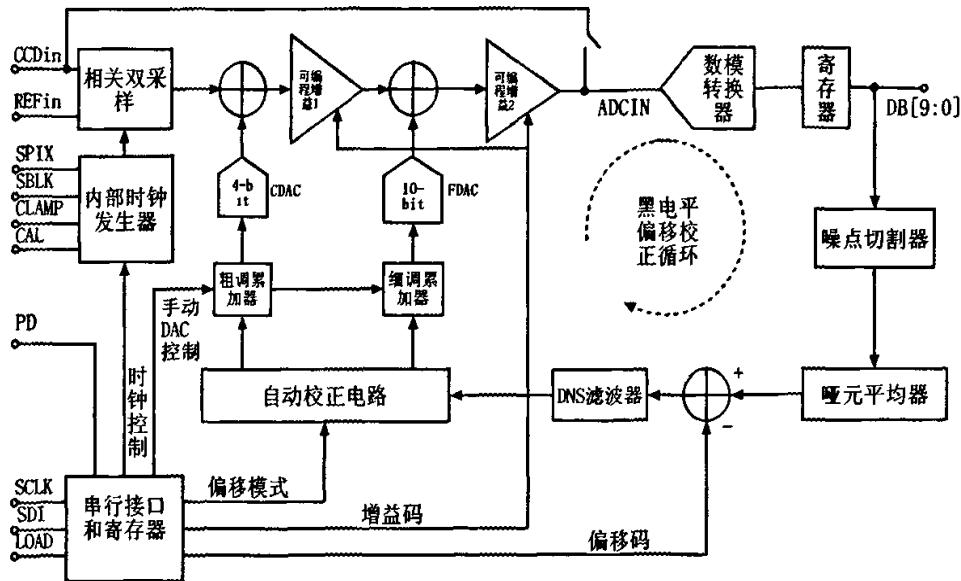

图 4.9 示出了图像数字器内部功能框图，CCDin 是相关双采样的输入，它与 CCD 模拟电压信号输出脚相连接；ADCIN 是测试 A/D 通道的引脚开关；ADC 是模/数转换器，输出 10-bit 的图像数字量；当偏移模式设定为自动时，自动校正电路补偿 CCD 输出信号的黑电平偏移量；数字噪声抑制滤波电路的目的在于消除黑电平偏移上微小变化；哑像元平均器通过命令字来决定采用多少哑像元进行平均；噪点切割器对于响应值超过哑像元理论最大值的已损坏的哑像元进行剪除处理，以防止此像元被纳入定标网络，影响整个系统性能；通过三线串行接口，设定增益码调节可编程放大器的放大倍数，对 CCD 视频电压进行放大；通过三线串行接口，设定偏移码使偏移量与黑电平期望输出值相等。

图 4.9 图像数字器内部功能框图

Fig. 4.9 Image digitizers' interior functional block

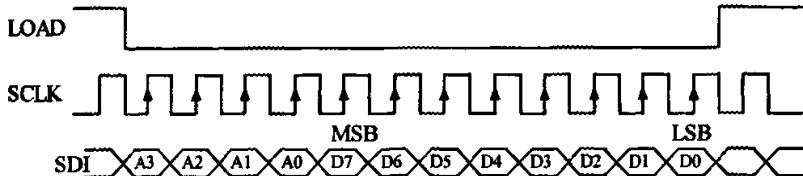

图 4.10 串行接口时序图

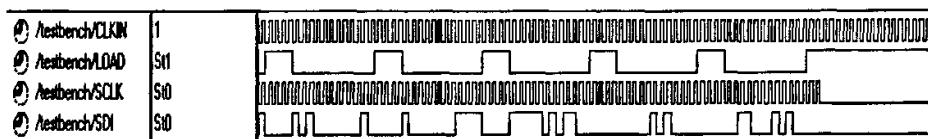

Fig. 4.10 The time sequence of serial interface

图像数字器的所有参数设定都是通过采用三线串行接口<sup>[20]</sup>来进行编程控制的，读写控制信号分别为 LOAD(锁存信号)、SDI(数据)和 SCLK(移位时钟)。接口采用 12-bit 移位寄存器，前 4-bit 为地址码，后 8-bit 为数据位。内部 10 个 8-bit 控制寄存器为图像数字器的工作状态设定和电路调试提供了很大的方便。图 4.10 为串行接口时序图：当 LOAD 信号置低时，激活寄存器，寄存器中的数据 SDI 串行移位，先移出 4-bit 的地址码，再移出 8-bit 的数据位，当 LOAD 信号置高时，移位寄存器中的数据并行置于串行接口寄存器阵列中。

下面简单介绍一下图像数字器的几个功能模块：

(1) 相关双采样电路

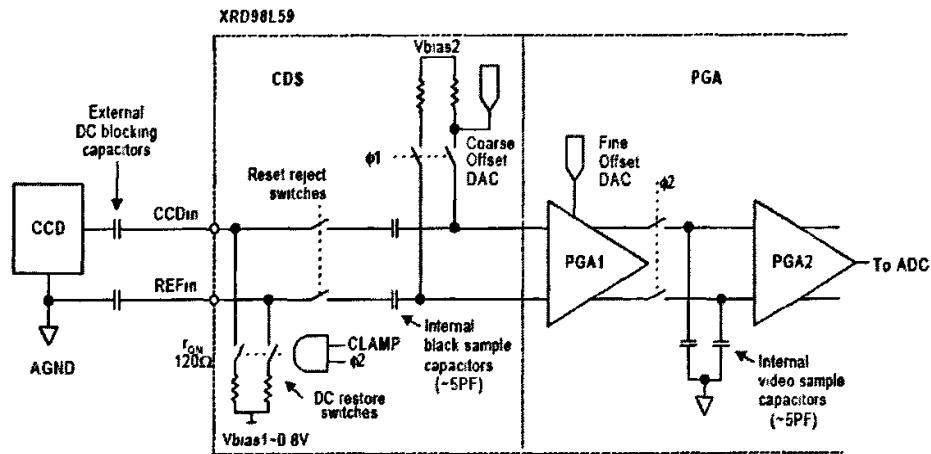

图 4.11 CDS 和 PGAs 原理框图

Fig. 4.11 Block diagram of CDS and PGAs

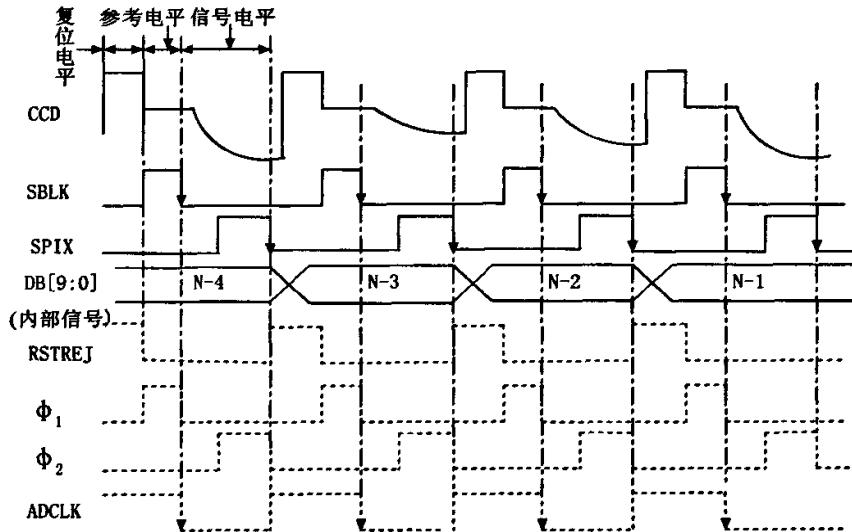

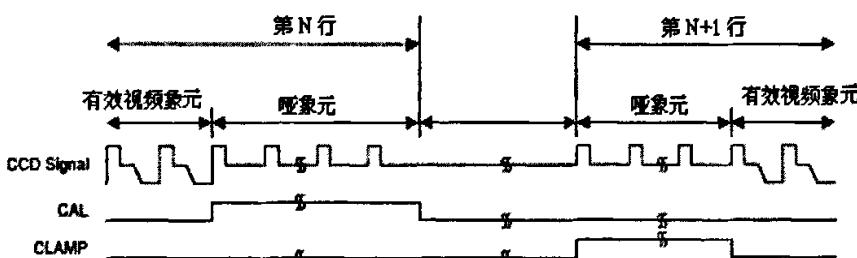

图像数字器的 CDS 原理图如图 4.11 所示。为了便于说明相关双采样的工作原理，我们将结合控制信号和内部节点信号的波形图进行分析，如图 4.12 所示。外部控制脉冲 SBLK(黑电平采样时钟)、SPIX(有效电平采样时钟)、ADCLK(采样时钟)经过内部时钟网络产生  $\Phi_1$ 、 $\Phi_2$  的内部电子开关控制脉冲，它们低电平时开关闭合。在每行像素周期开始时，由  $\Phi_2$  和 CLAMP 信号直流复位开关(DC restore switches)闭合，强制外部隔直电容箝位到 0.8V 的偏压电平  $V_{bias1}$ 。在每个像素周期的起始处， $\Phi_1$  作为暗电平采样开关被闭合，将 PGA 的输入端短路到第二个偏压电平  $V_{bias2}$ 。 $V_{bias2}$  是由 Coarse Offset DAC 产生，被用来从 CCD 输出信号中消除暗电平偏移。当  $\Phi_1$  开关断开时，像素参考暗电平被采样到内部暗电平采样电容。在每个像素周期，差分放大器 PGA1 通过内部暗电平采样电容像素电平和参考暗电平的差值转换为全差分信号形式。像素信号值采样开关  $\Phi_2$  闭合时，内部视频信号采样电容跟踪 PGA1 放大后的差分信号，Fine Offset DAC 在 PGA2 的正向输出端加上偏移调整补偿。RSTREJ 在 CCD 的复位电平时通过切断图像数字器输入减少了 CCD 复位噪声，在 SBLK 上升沿和 SPIX 下降沿之间断开来减少复位噪声。在每个 Reset 相位开始时 RSTREJ 断开来限制图像数字器的复位脉冲瞬时过渡，在黑电平抽取的时 RSTREJ 闭合，当 SBLK 是高电平时  $\Phi_1$  闭合，允许黑电平参考电压和  $V_{bias2}$  通过 C1 和 C2 电容。SPIX 高电平时  $\Phi_2$  闭合，黑电平参考电压和视频信号电压的差分信号通过电容 C1 和 C2 传送。差分放大器 PGA1 放大 CDS 输入 CCDin 和 REFin。SPIX 低电平时关闭  $\Phi_2$ ，将差分的像素值存储到电容 C3 和 C4。图像数字器可以通过软件设定测试引脚，当 SDI=010000000101 时，图像数字器进入测试状态，此时输入的数据跳

过相关双采样和放大器电路，直接进入 A/D 转换模块，从而测定图像数字器的通道是否正确。

图 4.12 CDS 时钟和内部信号时序图

Fig. 4.12 Timing diagram of the CDS clocks and internal signals

SBLK 在高电平时抽取黑电平，实际的抽样点在之后  $t_{BK}$ (是 SBLK 时间信号的孔径延迟)之后，SPIX 为高时抽取信号视频信号，实际的抽样点在延迟  $t_{VD}$ (是 SPIX 时间信号的孔径延迟)之后，SBLK、SPIX 的极性均可由串行口编程得到。SBLK 和 SPIX 的时钟延迟表如表 4.3 所示：

表 4.3 SBLK 和 SPIX 的时钟延迟表

Tab. 4.3 Delay table of SBLK and SPIX

| D7 | D6 | D5 | SBLK delay      | D4 | D3 | D2 | SPIX delay      |

|----|----|----|-----------------|----|----|----|-----------------|

| 0  | 0  | 0  | 3.5ns (default) | 0  | 0  | 0  | 2.7ns (default) |

| 0  | 0  | 1  | 5.5ns           | 0  | 0  | 1  | 4.7ns           |

| 0  | 1  | 0  | 7.5ns           | 0  | 1  | 0  | 6.7ns           |

| 0  | 1  | 1  | 9.5ns           | 0  | 0  | 1  | 8.7ns           |

| 1  | 0  | 0  | 11.5ns          | 1  | 0  | 0  | 10.7ns          |

| 1  | 0  | 1  | 13.5ns          | 1  | 0  | 1  | 12.7ns          |

| 1  | 1  | 0  | 15.5ns          | 1  | 1  | 0  | 14.7ns          |

| 1  | 1  | 1  | 17.5ns          | 1  | 1  | 1  | 16.7ns          |

## (2) 可编程增益控制

CCD 图像传感器的输出信号的大小随着入射照度的强弱而改变，只有通过信号处理系统进行增益、偏置调节，才能使输出的数字图像的亮度和对比度满足要求。如图 4.9 中 PGA 部分所示，图像数字器的 PGA 由两级实现，PGA1 实现粗略的增益控制，PGA2 实现精细控制。PGA1 提供 0dB、8dB 和 16dB( $1\times$ 、 $2.5\times$ 和  $6.25\times$ )增益。PGA2 根据串口输入的寄存器 GAIN 中的命令字 Gain[7 : 0](范围 0 到 255) 使得系统增益从 6dB 到 22dB 可调，步长为 0.125dB。下面的公式(4.1)可以根据 Code 的值计算 PGA 的增益：

$$Gain[dB] = 6 + \left( \frac{Code}{256} \times 32 \right) \quad (4.1)$$

## (3) 哑像元OB(Optical Black Pixel)的定标

不同 CCD 的哑像元位置和数目都是不一样的，在进入定标时，需要用 CAL 和 CLAMP 信号来定义用于定标的哑像元数目和位置，同时对于每行图像确定行头和行尾。CAL 和 CLAMP 是两个行时钟控制信号，有两种操作模式，具体的说就是根据控制寄存器命令字节的不同有 CAL&CLAMP 模式和 CAL ONLY 这两种模式。在控制命令字 Clamp Cal Bit 为 0 时，CAL&CLAMP 模式用 CAL 定义行尾 OB Pixel，用于暗电平定标，CLAMP 使得 CDS 的输入端进行直流箝位恢复。通常情况下，CLAMP 定义行头的 OB Pixel，如果行头的 OB Pixel 比行尾的多，可以定义 Clamp Cal=1，用 CAL 来定义行头的 OB Pixel，CLAMP 定义行尾，这种模式下必须注意 CAL 和 CLAMP 信号不能同时激活。CAL ONLY 模式下，CAL 来激活直流箝位恢复，CLAMP 来定义 OB Pixel 进行暗电平定标。在两种模式下，CAL 信号都要求至少 5 个像素周期。在本设计中采用了第一种模式，如图 4.13 所示。

图 4.13 哑像元定标时序图

Fig. 4.13 The time sequence of optical black pixel marking

## (4) 数字偏移校正控制

为了得到最大的分辨率和动态范围, 图像数字器采用数字控制的定标校正电路来调整信号偏移, 从图4.9可以明显地看清楚其反馈补偿的校正方式, 它的内部设置了多种功能。CAL、CLAMP已经定义了OB Pixel, 哑元平均器通过命令字来决定采用多少OB Pixel进行平均, 最多可以采用512个; 噪点切割器对于响应值超过哑像元理论最大值的已损坏的OB Pixel进行剪除处理, 以防止此像元被纳入定标网络, 影响整个系统性能。Coarse & Fine Accumulators和Offset Difference通过两个DAC根据输出值对CDS和PGA信号流程上的信号进行反馈调整, 校正系统偏移; DNS(Digital Noise Suppression)Filter电路的目的在于消除暗电平偏移上微小变化, 以免定标环对于测出的偏移过分敏感, 偏移值可以在串口手动设定, 也可以每个校正过程结束后重新系统测定。

### (5) ADC

图像数字器内部集成了 10-bit 分辨率、逐步逼近式的 ADC。ADC 转换由内部时钟 ADCLK 控制(参看图 4.9)。从视频信号输入到数字信号输出, 共需要 2.5 像素周期的流水线延迟。而从复位的上升沿计算, 从视频输入到视频信号输出有四个信号的延迟, 所以在存储时应该考虑这个因素, 否则将引起像素的整体移动, 而且在每一行的开始引起四个错误。ADC 的参考电压可以用内部或外部参考电压。内部参考电压是通过内部电阻分压网络来实现的。ADC 的 10 位并行数据输出总线具有三态功能, OE 为其三态控制脚。

## 4.2.2 图像数字器时序逻辑控制的设计与实现

本文在第 4.2.1 节对图像数字器图像数字器的各个模块进行了简单的介绍。下面将详细地介绍测试引脚、复位初始化、A/D 采样、定标和串行接口控制时序的 FPGA 实现过程。

上电工作开始时, 当 SDI=0100\_0000\_0101 时, 图像数字器可以进入测试状态, 此时输入的数据跳过相关双采样和放大器电路, 直接进入 A/D 转换模块, 从而测定图像数字器的通道是否正确。正确以后可以对图像数字器进行复位初始化, 使它的所有内部寄存器置默认值状态, 故设定 SDI=1111\_0000\_0001; 设定利用 SPIX 和 SBLK 的时钟的下降沿对 CCD 模拟输出量进行相关双采样, 采用 CAL&CLAMP 模式对哑像元进行定标, 用 CAL 对行尾的哑像元定标, 用 CLAMP 对行头的哑像元定标, 故设定 SDI=0011\_0101\_1111; 设定可编程放大器的放大倍数为 26dB, 根据公式

$$Gain[dB] = 6 + \left( \frac{Code}{256} \times 32 \right)$$

得 Code=10100000, 故设定 SDI=0000\_1010\_0000; 根据串行接口寄存器地址图, 当寄存器地址 A3A2A1A0=0010 时, 可通过对此寄存器中 8 位数据码的调节实现对相关双采样实际采样点位置控制, 故设定 SDI=0010\_XXXXXXXX, X

为调整值，假设有效电平采样实际位置相对 SPIX 延时 8.7ns 和黑电平采样实际位置相对 SBLK 延时 11.5ns 处，则 SDI=0010\_1000\_1100，采样点的延时时间要根据实际采集的图像情况进行调整。图 4.14 示出了用 FPGA 技术实现的三线串行接口控制时序仿真图，读写控制信号分别为 LOAD、SDI 和 SCLK。当 LOAD 信号置低时，激活寄存器，SDI 进行串行移位，当 LOAD 信号置高时，移位寄存器中的数据并行置于串行接口寄存器阵列中。根据系统的实际要求来设定 SDI 的值，图中 SDI 分别为 0100\_0000\_0101，1111\_0000\_0001，0011\_0101\_1111，0000\_1010\_0000 和 0010\_1000\_1100。

图 4.14 串行接口控制时序仿真图

Fig. 4.14 Time sequence simulation chart of serial interface control

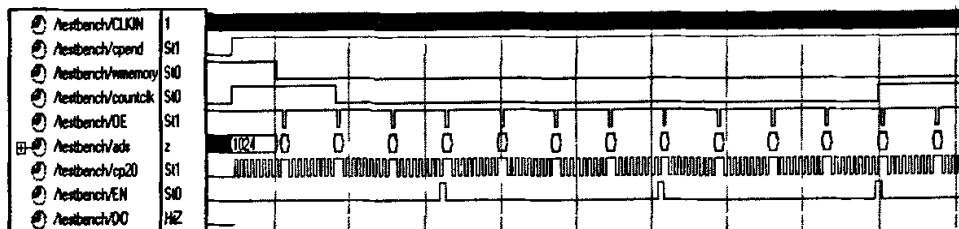

图 4.15 示出了相关双采样和哑像元定标控制时序仿真图, CCLK 为系统 20MHz 时钟, 移位计数器 counter 从 4 计数到 13 时, CLAMP 置高电平对 CCD 采集的一帧图像的行头 10 个哑像元进行定标, 其他计数时, CLAMP 置低电平状态。当 counter 从 1042 计数到 1051 时, CAL 置高电平对一帧图像的行尾 10 个哑像元进行定标, 其它计数时, CAL 置低电平状态。当移位计数器 counter 从 16 计数到 1039 时, SBLK、SPIX 对 CCD 输出的 1024 个正常模拟信号进行相关双采样, 从而抑制信号的复位噪声, 得到 CCD 有效视频值, 其它计数时, SBLK 和 SPIX 置低电平状态。图中还给出了 CCD 驱动电路的时序波形图。

图 4.15 相关双采样和哑像元定标控制时序仿真图

Fig. 4.15 Time sequence simulation chart of CDS and OB marking control

## 4.3 CCD 存储电路设计与实现

### 4.3.1 存储电路硬件设计

8 位精度 A/D 采样时钟频率为 5MHz, 其 1s 将产生 5MB 的数据量, 而且为了与计算机数据采集模块的速度相匹配, 为了有更多的时间用于数据的识别处理, 从图像数字器输出的数字信号在进入通信模块前需要大容量缓存来存储采样数据。通常构成缓存的芯片有三种: 双口 RAM、FIFO、SRAM。双口 RAM 具有两套独立的数据、地址总线, 可以从连个端口同时进行随机存取, 具有很大的灵活性, 利于对数据进行处理, 缺点是双口 RAM 管脚较多, 芯片面积比较大, 需要较大的 PCB 板布线空间, 价格比较昂贵; FIFO 也具有两个数据端口, 一端进行写操作, 另一端进行读操作, 两个数据端口均只有数据线而没有地址线, 简化了接口的实现, 但是数据只能顺序读写, 显得不够灵活, 不利于对数据进行处理; SRAM 只有一套数据、地址和控制总线, 通常实现数据交换需要两片 SRAM, 由数据采集部分和数据处理分别访问一片 SRAM, 并且可以来回切换, 使数据采集与处理可以同时进行, 这种方式灵活经济, 在综合考虑了性能、价格、实现方便性及 PCB 板面积要求后, 选取 SRAM 方式实现数据的高速缓存, 通过 FPGA 产生切换控制电路, 控制 A/D 转换器、通信模块和图像识别模块的分时读写<sup>[24]</sup>。

本设计中, 选取 CY7C199 作为外部 SRAM<sup>[25]</sup>。CY7C199 是 256K×16bit 的 3.3V COMS 高速静态存储器, 其输出使能响应仅需 5ns, 地址访问时间也仅需 10ns, 因此数据的读写时间极快。由于其内部完全由静态异步电路构成, 因此不必对芯片进行刷新操作, 可直接对无用数据进行覆盖。

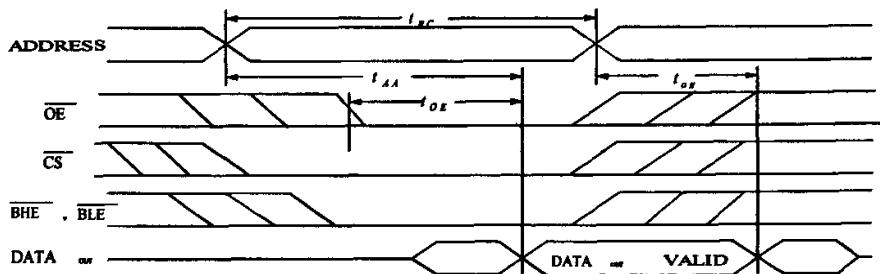

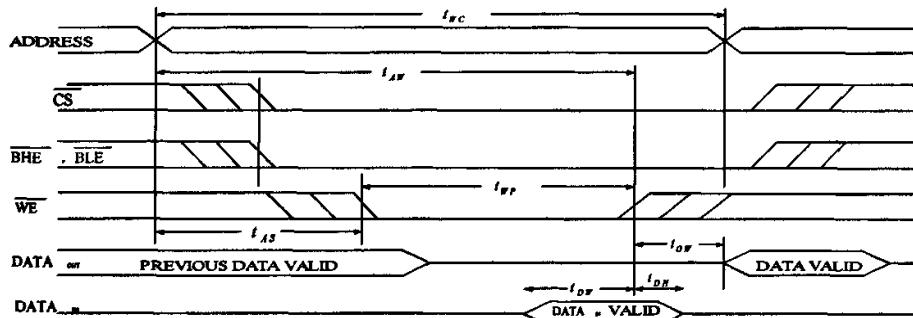

图 4.16 是 SRAM 的读时序波形图, 图 4.17 为它的写时序波形图。参数介绍分别如下:

图 4.16 CY7C199 的读时序图

Fig.4.16 The reading sequence of CY7C199

在读周期中, 写信号  $\overline{WE}$  总为高电平。读周期时间  $t_{RC}$  最小为 12ns;  $t_{AA}$  为地址选取时间, 它不超过 12ns;  $t_{OE}$  为输出使能到输出数据的有效时间, 不超过 6ns。 $t_{OH}$  为地址变化后的输出数据保持时间, 最小为 4ns, 故两次读信号  $\overline{OE}$  的间隔一定要大于这个保持时间, 读出数据才能有效。

图 4.17 CY7C199 的写时序图

Fig.4.17 The writing sequence of CY7C199

在写周期中, 读信号  $\overline{OE}$  总为高电平。写周期时间  $t_{WC}$  最小为 12ns;  $t_{AC}$  为地址有效到写有效的时间, 最小可为 0ns;  $t_{AW}$  为地址有效到写信号结束的时间, 不小于 8ns;  $t_{WP}$  为写脉冲宽度, 为保证数据能够正确写入, 此信号宽度不小于 8ns;  $t_{DH}$  为写入数据的保持时间, 它最小可为 0ns;  $t_{DW}$  为写信号低电平时的数据有效时间, 它最小可为 6ns。数据在写信号置高电平  $t_{ow}$  时间后存入存储器中,  $t_{ow}$  最小为 3ns。

在本设计中, 使能信号  $\overline{CS}$ ,  $\overline{BHE}$ ,  $\overline{BLE}$  均接地, 它们始终置低电平有效状态。

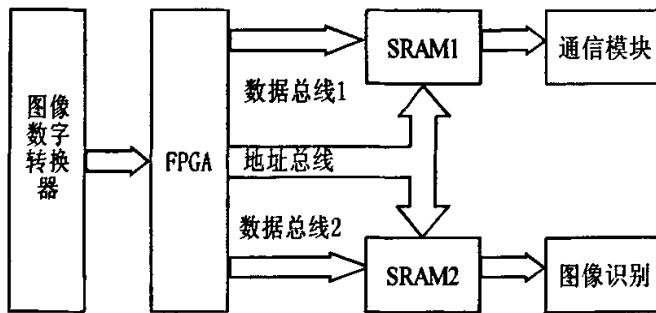

本系统使用了两片 SRAM, 为了减少 FPGA 的 I/O 引脚数量, 两片 SRAM 复用地址总线, 在设计中将两片 SRAM 的地址线、控制线分别接到 FPGA 相同的 I/O 口, 在 FPGA 内部将两组地址线复用, 但数据线分开使用, 这就组合成了一片 256K×32-bit 的 SRAM。

图 4.18 是本设计中外部 SRAM 的电路原理图, 由 FPGA 控制地址计数器计数实现对 SRAM 的地址总线的控制, 计数器采用的时钟信号为图像数字器的有效电平采样时钟 SPIX, 一个 SPIX 脉冲对应一个字节的 A/D 输出数字量, 即对应一位 CCD 光敏元的输出信号, 这样在计数器的输出端形成的地址就与 CCD 的每位数据形成一一对应的关系。在整机系统实验阶段, 当数据采集系统接收到采集命令时, SRAM1 存储一帧 CCD 采集的样本数据, 然后按通信模块时序读出, 传送给主控制板。在系统正常工作阶段, SRAM1 存储一帧 CCD 对白背景扫描的图像数据, SRAM2 存储图像二值化后的数据,

以供图像识别处理使用。在本系统中由于没有涉及到图像处理知识, 所以只使用 SRAM1 作为通信模块的存储缓存, 但在以后的应用中两块 SRAM 会使数据传送速率很大。

图 4.18 SRAM 电路原理图

Fig. 4.18 SRAM circuit schematic

#### 4.3.2 存储电路软件实现

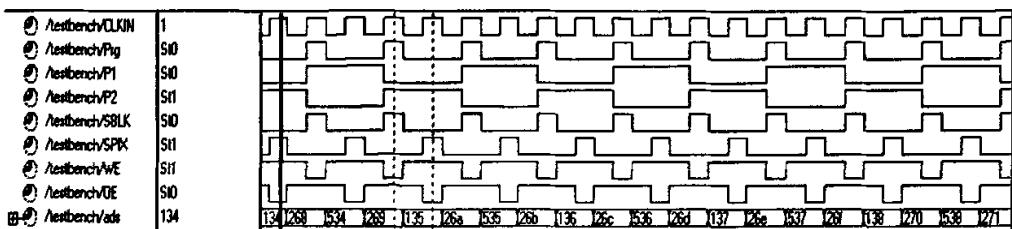

对 SRAM 芯片的读、写时序本身并不复杂, 但高速数据从 A/D 输出以及 FPGA 从 SRAM 中读出数据, 各个器件的时序之间必须配合一致。从图 4.3 中我们可以看出,  $\Phi_1$  和  $\Phi_6$  时钟决定了 CCD 的输出波形; CCD 的  $V_{out}$ 、A/D 的主要时钟信号关系如图 4.12 所示, 从图中我们可以看出, SBLK 的下降沿和 SPIX 的下降沿决定了 A/D 的数据输出保持时间。SRAM 的写时钟有效时, A/D 的输出数据应保持稳定状态。A/D 的输出相对于 SPIX 的下降沿有一定的延迟, 这是使用 A/D 器件内部采样点位置控制的结果, 实际的采样点位置要根据 CCD 的输出波形通过软件编程来调节。SRAM 的主要时钟信号仿真结果如图 4.19 所示, 其中 WE 是 SRAM 的写控制信号,  $WE = \overline{SBLK}$ ; OE 是 SRAM 的读控制信号,  $OE = \overline{SPIX}$ , ads 是存储器的地址。

图 4.19 SRAM 的主要时钟信号仿真图

Fig. 4.19 Main clock signals' simulation chart of SRAM

#### 4.4 通信电路硬件实现

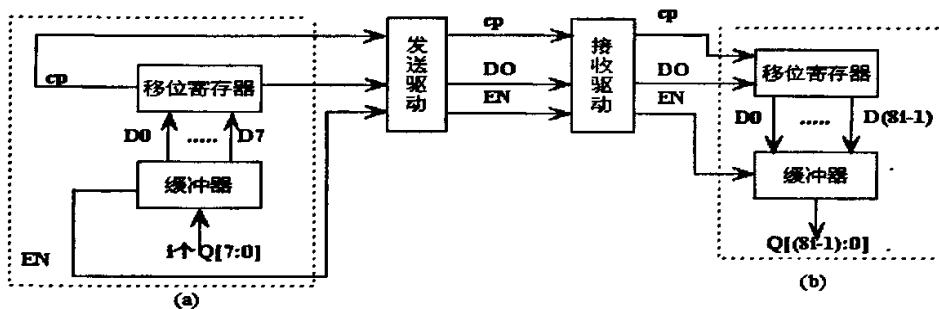

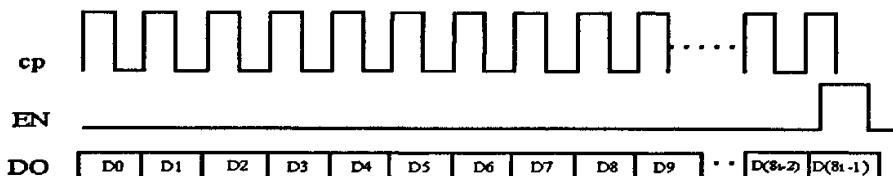

本课题的通信模块是根据一个 3 根信号线的串行接口协议设计的，这三个接口信号分别是串行数据(DO，主设备输出，从设备输入)、移位时钟(cp)和使能信号(EN)<sup>[26]</sup>。

由主设备时钟的出现与否来界定主从设备间的通信，FPGA 主控器一旦检测到接收芯片接收到主设备时钟信号，就开始传输数据，时钟信号无效后，传输结束。在此期间，使能信号可对从设备初始化，也可作为信号帧数据的开始和结束标志。

图 4.20 和 4.21 分别为通信模块结构图和对应的三个接口信号之间的时序关系图。由图 4.21 所示，待传输的数据一信号帧是由  $i$  个 8bit 的数据构成，信号帧的帧格式决定  $i$  的大小。

图 4.20 通信模块结构图

Fig.4.20 The structure of communication module

图 4.21 3 个接口信号之间的时序关系图

Fig.4.21 Sequence relations among the three interface signal

图 4.20 中的虚框(a)为通信模块的发送端，先将待发送的一个 8bit 数据存入 8 位的缓冲器中。通信开始后，将缓冲器中的数据先移入 8 位移位寄存器中，然后缓冲器再存入下一个 8bit 数据。同时，移位时钟 cp 的每个上升沿对应移位寄存器中一个串行数据的输出，8 个移位时钟，移出 8 个串行数据。在第  $8i$  个移位时钟节拍时，发送端已移出  $8i$  个串行数据即  $i$  个 8bit 数据，同时再延时  $1/4$  个 cp 时钟周期，使能信号 EN 置高电平状态，高电平持续到下一个 cp 下降沿来临时，如图 4.21 所示。相应地，虚框(b)为通信

模块的接收端,接收芯片一旦检测到发送端发来的移位时钟信号,就开始接收串行数据。移位时钟  $cp$  的每个下降沿对应一个串行数据移进接收端的 8bit 移位寄存器。当接收芯片接收到发送端发来的使能信号 EN 时,就利用 EN 的下降沿节拍将 8bit 移位寄存器中的值锁存到接收端的 8bit 缓冲器中。发送驱动器采用的是 MOTOROLA 公司生产的线性驱动器 MC1488,接收驱动器为 MC1489。MC1489 因为只有接收,所以是单 5V 电源工作,MC1488 需要正负 12V 电源。MC1488 将 TTL 电平转换为 RS-232C 电平,MC1489 将 RS-232C 电平转换为 TTL 电平。

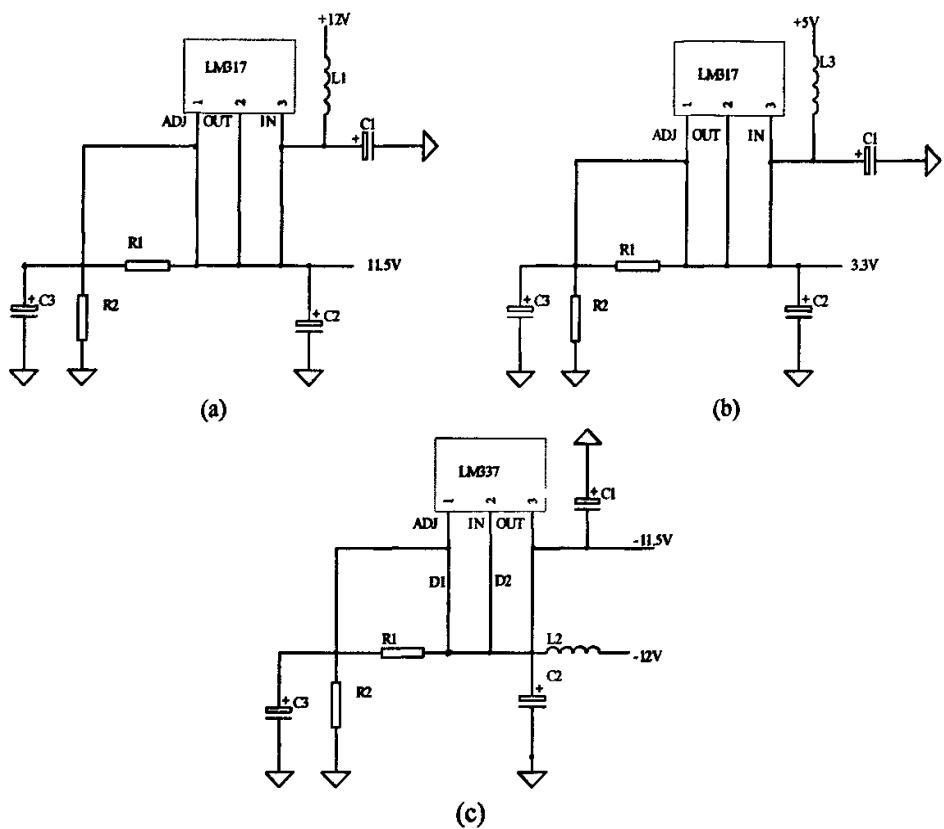

#### 4.5 电源电路实现

系统的大多数芯片都是标准的+5V电压供电,而CCD芯片TP1024P则需要多种直流偏置电压。为了解决供电问题,系统设计了电源电路。电源电路用于提供系统设计所需要的电压输出,-11.5V电压配合运算放大器LM358和时序驱动器DG642可以得到CCD所需要的偏置电平和驱动时序。

集成稳压器是指将不稳定的直流电压变为稳定的直流电压的集成电路。由于集成稳压器具有稳压精度高、工作稳定可靠、外围电路简单、体积小、重量轻等显著优点,在各种电源电路中得到了普遍的应用<sup>[27]</sup>。LM317、LM337是美国National公司生产的集调整管、基准电压、采样和保护电路于一体的三段可调正负输出集成稳压器。其三个端子分别为输入端、输出端和调整端,没有接地(公共端),是一种悬浮式电路结构。LM317、LM337的最大输入输出电压差为40V,输出电压1.25~37V(或-1.25~-37V)连续可调,输出电流0.5~1.5A,最小负载电流为5mA,调整端电流为50μA,电压调整率为0.02%,电流调整率为0.3%。LM317、LM337的1、2两脚之间的电压为恒定值1.25V,可以看作是基准电压。LM317、LM337在稳压精度、纹波抑制比、输出电压温度特性等方面都比较好,并且具有过流、过热保护和调整管安全工作区保护功能。

如图 4.22 所示,LM317、LM337 的应用非常方便,其输出电压  $U_0$  决定于  $R_2$  和  $R_1$  的比值,所以只要在输出端接入合适的阻值即可获得所需要的输出电压。LM317 的输出电压表达式  $U_0=1.25(1+\frac{R_2}{R_1})$ ,故(a)中  $U_0=1.25(1+\frac{2200}{270})=11.5V$ ; (b)中  $U_0=1.25(1+\frac{430}{270})=3.3V$ 。LM337 与 LM317 的原理相近,其输出电压表达式为  $U_0=-1.25(1+\frac{R_2}{R_1})$ ,故(c)中  $U_0=-1.25(1+\frac{2200}{270})=-11.5V$ 。电源电路中,  $C_1$  为滤波电容,  $C_2$  为消振电容,起稳定电路的作用,  $C_3$  是为了滤除纹波电压的滤波电容。

图 4.22 电源电路原理图

Fig. 4.22 Power supply circuit schematic

## 5 数据采集系统的数据传输与显示

### 5.1 相机板和主控制器通信的设计与实现

相机控制板和主控制板之间的数据交换在物理层上依靠 MC1488 和 MC1489 变成差分信号后通过串行通信接口进行传输。系统要通过通信接口进行有效的数据传输，往往还依赖于设计者设计的通讯协议，下面将具体在系统中自行设计的通讯传输协议。

#### 5.1.1 主控制板到相机板的通信

它主要完成主控制板对相机控制板的各种控制操作，如发送采集命令、设置图像处理器控制参数、定义控制操作等。

表 5.1 通信帧格式表

Tab. 5.1 Frame format table in communication

| 名称      | 功能代码 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

|---------|------|----|----|----|----|----|----|----|

| 复位命令    | 01   | 00 | 00 | 00 | 00 | 00 | 11 | 00 |

| CCD 曝光量 | 02   | 00 | 00 | 00 | 00 | 00 | 00 | b  |

| A/D 参数  | 03   | 00 | 00 | 00 | 00 | 00 | 0a | d  |

| 样本采集命令  | 05   | 00 | 00 | 00 | 00 | 00 | 11 | 00 |

表 5.1 表述了控制传输通信模式中所使用的信号帧的帧格式表。功能代码表示这帧的类型，其他参数有其各自含义。复位命令帧是相机板的全局复位命令信号。CCD 曝光量帧对 CCD 的曝光时间进行设置，参数 b 控制 CCD 的曝光量大小。A/D 参数帧对 A/D 转换器的参数进行设置，通过对 12-bit 寄存器阵列进行参数设定来设定其工作状态，a 为 4 位的地址码，d 为 8 位的数据位。如果接到样本采集命令，则相机板向主控制板发送一帧样本数据。

#### 5.1.2 相机板到主控制板的通信

它主要完成相机控制板向主控制板发送一帧 CCD 采集样本图像数据的操作，这一帧样本数据用于整机系统测试阶段。在此通信过程中，一旦相机控制板在控制传输通信过程中接收到主控制板发送过来的采集命令功能代码，它就要响应要求，存储一帧图像数据，随后发送给主控制板。

在相机到主控制板传输通信模式中, 传输数据包每帧定长为 4 个字节。一个字节表示 CCD 扫描图像经 A/D 转换后的 8-bit 数字图像数据, 在一帧样本图像传输过程中, 每 4 个字节的图像数据组成一组进行传输。

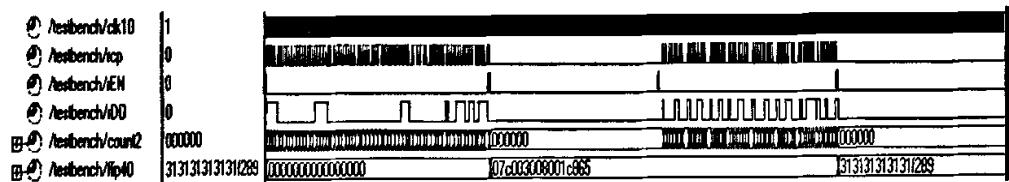

主控制板到相机板的 FPGA 实现过程如下: `rcp` 是主控制板发来的移位时钟, 当它的下降沿到来时, 系统以计数的方式逐一接收数据, 将数据移入 64 位的移位寄存器 `register` 中, 最先接收到的数据放到 `register` 的最低位, 第二个接收到的数据放到 `register` 的第 2 低位, 依次类推。当计数器 `count2` 从 0 计到 63, 移位寄存器接收完一帧的传输数据包。`rEN` 是控制使能信号, 当 `rcp` 的下降沿检测到 `rEN` 的高电平有效时, 则对计数器清零。另外当 `rEN` 的下降沿到来时, 将移位寄存器 `register` 的值传给锁存器 `flip40`。所以在此通信模块中, `rEN` 即为接收一帧数据开始的标志信号又为数据锁存的标志信号。`rDO` 是串行数据, 由主控制板发出, 其一个字节数据从低位到高位串行输出。

图 5.1 接收数据模块仿真图

Fig. 5.1 The receiving data module's simulation chart

图 5.1 示出了接收数据模块经 FPGA 实现后的仿真结果图。在仿真验证中, 系统采用 800KHz 时钟工作频率, 并预定串行二进制数据 `rDO` 的初值, 由 `rDO` 输入 `11100000_00110000_00001100_00000000_00010000_00001000_00111000_00011010`, 由 `flip40` 相应输出 `07c003008001c185`, 其仿真结果与理论分析一致。在接收数据模块中, 采用了计数器和锁存信号 `rEN` 双重检测的方法, 当 FPGA 接收一帧数据时, 若锁存信号到来时计数值不为 63 或计数值为 63 而未检测到锁存信号, 数据帧都被判定无效, 此时不把 `register` 的值传给锁存器 `flip40`, 从而保证了接收数据的可靠性。

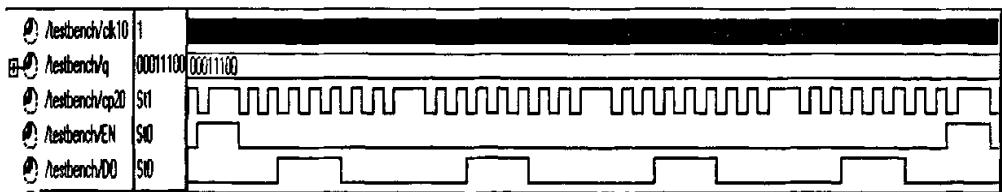

相机板到主控制板的通信程序的 FPGA 实现如下: 相机控制板发来移位时钟 `cp20`, 当它的下降沿到来时, 系统以计数的方式发送数据, 将数据 8bit 的 A/D 数字送入移位寄存器中, 最先发送的数据放到的最低位, 第二个接收到的数据放到第 2 低位, 依次类推。当计数器从 0 计到 32, 移位寄存器接收完一帧的传输数据包。`EN` 是控制使能信号, 当 `cp20` 的下降沿检测到 `EN` 的高电平有效时, 则对计数器清零。所以此通信模块中, `EN` 即为接收一帧数据开始的标志信号又为数据锁存的标志信号。

图 5.2 发送数据模块仿真图

Fig. 5.2 The transmitting data module's simulation chart

图 5.2 示出了发送数据模块经 FPGA 实现后的仿真结果图。在仿真验证中，系统采用 500KHz 时钟工作频率， $q$  为 SRAM 输出的 8 位数据，经并串转换为 DO 信号，在时钟的下降完成一位的转换，先发送的为最低位，然后发送的为高位，当计数器增加到 32 的时候，EN 在 cp20 的下降沿变为高电平，4 个字节的数据转化完毕，产生锁存信号。在仿真中  $q$  输入一定值为 00011100，转化成的 32 位串行数据为 00011100\_00011100\_00011100\_00011100。如图所示，其仿真结果与理论分析一致。

## 5.2 EPP 工作模式简介

计算机与外围设备的连接，有多种接口方式。串口是最通用的一种连接方法，但是它支持数据传输速率最大为 10~20KB/s，对于一般的数据采集和控制系统而言显得有些慢。SPP(Standard Parallel Port)的数据通讯速度比串口快，可以达到 150KB/s，但是用作数据输入时传输速度要牺牲很多，况且外设的设计并不比 EPP(Enhanced Parallel Port)简单。ECP(Extended Capabilities Port)相对 EPP 而言，其最大的优势是它支持 DMA 操作，但是获得 ECP 的高性能的代价是必须重新设计比 EPP 复杂得多的接口软件。USB(Universal Serial Bus)数据传输速度快，支持外围设备多，但 USB 接口必须要有专用的接口芯片的支持才能用在系统中。因此，对于需要高速传输数据，而且传输距离不长的情况下，使用 EPP 通信不需要增加设备，开发相对简单，是非常理想的一种通信方式<sup>[28]</sup>。

EPP 协议源于 Intel Xircom 和 Zenith 数据系统。作为一个提供高性能并口连接的方法，它仍与 SPP 兼容。EPP 协议为并行口外围设备带来了许多便利，它极大地改善了 PC 机并行口的数据传输率，使用 EPP 协议，系统可以获得 500KB~2MB/s 的传输速率，这种情况下，并行口外设近似于在 ISA 即插即用卡相同的性能水平下工作，从一个与并行口相连的设备获得这种等级的数据传输能力是 EPP 协议的主要特征之一。

EPP 协议是一种与标准并行口兼容且能完成双向数据传输的协议。该协议定义的并行口更像一个开放的总线，给用户提供了强大的功能和灵活的设计手段<sup>[29]</sup>。EPP 数据传输协议允许外设可以以适合它处理或储存数据能力的速率接收数据，这就保证了数据完

整性和防止数据丢失。这种“速率匹配”对主机和外围设备都是透明的。所有的并行口传输方法都利用了联锁的握手信号，这可以允许外围设备控制其本身操作所需的建立时间。

EPP协议控制板不受计算机内部空间的限制，克服了计算机内部总线的多样性，简化了系统的构建过程与结构，实现了系统硬件与工作软件在形式上的分离，系统测试与维护容易，系统故障修复、软件升级也相对简化。

在应用EPP协议时，需要在计算机的BIOS设置中将并口模式，本文系统主板默认EPP协议的类型为EPP1.9(本文在5.3.2中将对EPP1.7和EPP1.9协议类型做一简单介绍)。

### 5.2.1 EPP 协议信号的定义

EPP 协议定义了 8 比特多路数据/地址口通讯协议，并用高速数字逻辑电路实现。这些电路为主机与外设之间传输数据产生选通脉冲和通讯信号。EPP 标准为从并行口出来的每一根信号线定义了适用于 EPP 的名字。表 5.2 给出 EPP 信号的定义。

表5.2 EPP信号定义表

Tab.5.2 The table of EPP signal definition

| EPP信号   | 方向 | 引脚编号     | 信号描述                  |

|---------|----|----------|-----------------------|

| nWrite  | 输出 | 1        | 低电平表示写，高电平表示读         |

| nDstrb  | 输出 | 14       | 数据选通信号，低有效，正进行数据读/写   |

| nAstrb  | 输出 | 17       | 地址选通信号，低有效，正进行地址读/写   |

| nInit   | 输出 | 16       | 初始化信号，低有效，重置外设        |

| Intr    | 输入 | 10       | 外中断信号，低有效             |

| nWait   | 输入 | 11       | 低有效可以开始下一周期；高电平表示结束操作 |

| AD[0-7] | 双向 | 2-9      | 地址/数据线                |

| 用户定义    | 输入 | 12 13 15 | 可由用户根据不同需要进行设定        |

### 5.2.2 EPP 寄存器

从软件角度来看，EPP 是标准并行口寄存器 SPP 的扩展。SPP 由三个寄存器组成，从口的基地址开始依次为：数据口、状态口和控制口。PC 机并行口 1 的基地址为 378H，PC 机并行口 2 的基地址为 278H。EPP 利用 SPP 中没有定义的那些口扩展了 SPP 的寄存器。具体的 EPP 寄存器定义如表 5.3 所示。

通过生成一条单 I/O 写指令到“基址+4”，EPP 控制器就会产生必需的握手信号，并用 EPP 数据写周期来选通数据传输。对基地址+0～+2 的 I/O 操作，所产生的结果将

精确与标准并行口相同。这就保证了它与标准并行口外设和打印机的兼容性。而对“基地址+3”的I/O操作就产生地址周期。

口5~口7可根据不同的硬件实现完成不同的用途，它可用来完成16或32位软件接口，或是用作配置寄存器，也可根本不用。能用一条单指令传送接收数据就是EPP模式并行口能以ISA总线速率传输数据的原因。一个数据块能用一个简单的REP-I/O指令传输，而不是让软件完成一个完整的I/O软件循环。依靠主机适配器口设备和外设的能力，EPP口能以500KB~2MB/s的速率传输数据。

表5.3 EPP的寄存器定义及其功能

Tab.5.3 The definition of the EPP register

| 端口名    | 偏移    | 模式      | 读/写 | 描述                       |

|--------|-------|---------|-----|--------------------------|

| SPP数据口 | +0    | SPP/EPP | W   | 标准SPP数据口，没有自动选通          |

| SPP状态口 | +1    | SPP/EPP | R   | 读接口的输入状态                 |

| SPP控制口 | +2    | SPP/EPP | W   | 设置输出的控制线状态               |

| SPP地址口 | +3    | EPP     | R/W | 产生一个联锁的地址读/写周期           |

| EPP数据口 | +4    | EPP     | R/W | 产生一个联锁的地址读/写周期           |

| 没定义的口  | +5~+7 | EPP     | R/W | 不同的实现有不同的用途，可做16位和32位I/O |

### 5.2.3 EPP的传输周期说明

EPP协议共提供4种类型的数据传输周期：数据写周期、数据读周期、地址写周期和地址读周期。下面对这四种周期进行说明。

数据周期一般用于主机和外设间的数据传输，地址周期一般用于传送地址通道命令和控制等信息，地址周期和数据周期的区别仅仅在于端口选定nAstrb地址选通信号脉冲信号或nDstrb数据选通信号脉冲信号中的哪一种脉冲<sup>[30]</sup>。这些周期可以看成是两种不同的数据周期，而且地址周期和数据周期共用AD[0-7]双向数据/地址线。

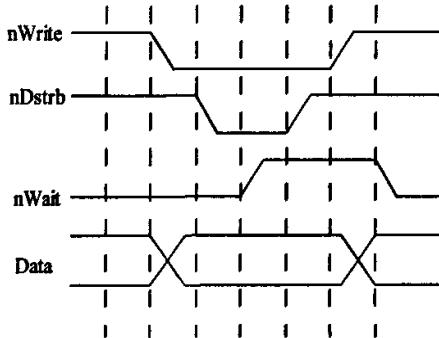

#### (1) 数据写入周期

数据写入周期就是完成计算机并行口的数据写入。每一个周期从并行口的数据线上写入一个8位的数据。它的步骤如下：首先外设的数据输出被禁止nWait为低电平，然后主机将nWait设置为低电平，并向EPP数据寄存器写入一个地址。这个字节将出现在D0-D7数据线上，并使得nDstrb成为低电平，接着外设再将nWait设置成高电平，表示做好了锁存数据的准备，之后主机将nDstrb置高，使得外设锁存数据，最后当外设做好读入下一字节的准备，后将nWait置为低电平，就完成了一个数据写入周期。数据写周期时序波形图如图5.3所示。

图5.3 数据写周期时序波形图

Fig. 5.3 Timing waveform of data writes cycle

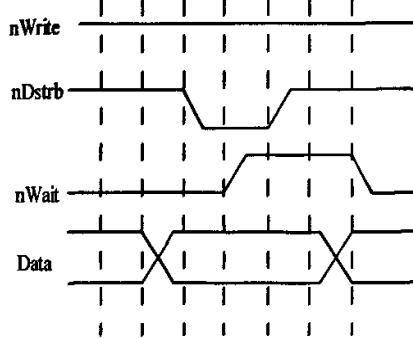

图5.4 数据读周期时序波形图

Fig. 5.4 Timing waveform of data read cycle

### (2) 数据的读取周期

数据读取周期就是完成计算机并行口的数据读取。每一个周期从并行口的数据线上读取一个8位的数据。它的具体的步骤如下：首先外设的nWait被置为低电平，然后主机将nWait设置为高电平，禁止输出D0-D7，并将nDStrb置为低电平，之后外设启用其D0-D7，输出向它们写入数据将nWait置高，表示已经准备好了待读数据，接着主机从EPP数据寄存器中读取D0-D7，并将nDStrb置为高电平，最后外设禁止数据D0-D7，将nWait置低，这样就完成了一个数据读取周期。数据读周期时序波形图如图5.4所示。

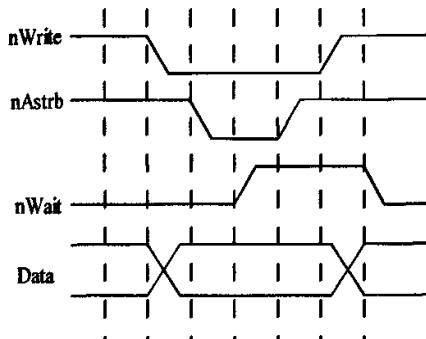

### (3) 地址的写入周期

地址写入周期就是完成计算机并行口地址的写入。其工作工程与数据写入周期相比仅仅是端口nDstrb数据选通信号脉冲信号换成了选定nAstrb地址选通信号脉冲信号。其地址写周期时序时序波形图如图5.5所示。

图5.5 地址写周期时序波形图

Fig. 5.5 Timing waveform of address write cycle

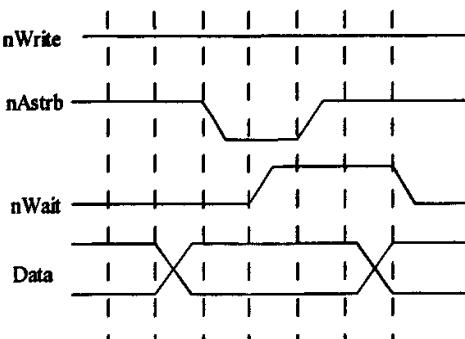

图5.6 地址读周期时序波形图

Fig. 5.6 Timing waveform of address read cycle

#### (4) 地址的读取周期

地址的读取周期就是完成计算机并行口地址数据的读取。每一个周期从并行口的数据线上写入一个 8 位的数据。其工作工程与数据写入周期相比仅仅是端口 nDstrb 数据选通信号脉冲信号换成了选定 nAstrb 地址选通信号脉冲信号。其地址读周期时序图如图 5.6 所示。

由 EPP 的读写时序可以看出，握手信号由硬件完成，整个数据传送发生在一个 ISA 周期内，因而使用 EPP 协议传送数据，系统可以获得 500KB~2MB/s 的传输率。

#### 5.2.4 EPP 使用的硬件连接

作为并行口电缆线的插座，计算机并行口电缆线两头都有 25 芯连接器，其中一头为了与计算机进行传输数据配置成插孔式，每一个触点都是针状的插头，这种设计是和计算机主板上的连接器相对应的，另外一头可以根据外设上的并行口连接器来选择。为了保证并行口传输的速率和稳定性，一定要使用内部有 25 股内线的电缆线，并且其 7 根地线要分别连接在相应的引脚上，这样在较长距离的传输上才能保证正常工作。本课题的数据采集系统的硬件电路上使用的就是插入式的接口与并行电缆线相连接。EPP 使用与标准并行口相同的 25 针 D 型插件。当其处于增强模式时，实际上只用了 8 条数据和 5 个信号，这 5 个信号的定义与以前相比有所改变。表 3 列出了 EPP 的电缆引脚分配。

表5.4 EPP电缆引脚分配

Table 5.4 Assign of EPP cable pin

| 25针插头 | 功能          | 25针插头 | 功能          |

|-------|-------------|-------|-------------|

| 1     | 写#          | 13    | 选择#         |

| 2     | 地址数据位0      | 14    | 数据选通#       |

| 3     | 地址数据位1      | 15    | 错误#         |

| 4     | 地址数据位2      | 16    | 初始化(与11脚相配) |

| 5     | 地址数据位3      | 17    | 地址选通#       |

| 6     | 地址数据位4      | 18    | 地(数据)       |

| 7     | 地址数据位5      | 19    | 地(与1脚相配)    |

| 8     | 地址数据位6      | 20    | 地(与10脚相配)   |

| 9     | 地址数据位7      | 21    | 地(与12脚相配)   |

| 10    | 中断#         | 22    | 地(与13脚相配)   |

| 11    | 等待#(与16脚相配) | 23    | 地(与14脚相配)   |

| 12    | 缺纸          | 24    | 地(与15脚相配)   |

|       |             | 25    | 地(与17脚相配)   |

### 5.3 EPP 接口设计与实现

为了实时的观测采集到的数据，我们将采集系统通过EPP协议与计算机连接并将数据在PC机上显示。数据采集系统的数据通信总体工作过程就是：首先由用户从控制面板上发出相应的指令，控制面板根据用户发出的指令调用相应的动态链接库中的并行口底层操作函数，然后被调用的底层操作函数就会向计算机并行口相应的端口写入数字脉冲，这些数字脉冲通过并行口电缆线传送给采集系统的硬件电路。硬件电路就可以根据所收到的脉冲信号进行工作，并将所采集到的数字信号通过并行口传送给计算机。控制面板程序就通过自身的波形显示程序在显示区显示波形，从而完成整个数据采集工作。下面将详细的介绍其硬件和软件实现的方法。

#### 5.3.1 硬件电路设计与实现

本数据采集系统通过标准的并行口连接电缆来和计算机的并行口进行通信。虽然在数据采集系统的设计中，并行口主要的核心器件，但其在硬件电路的设计中却是非常简单的。只须将并行口相应的管脚与采集系统对应的信号线相连接就可以了。

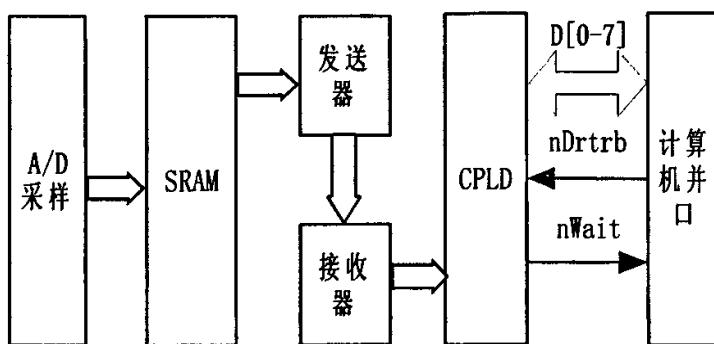

在设计中由于数据采集系统通过发送器MC1488和与其他模块进行通信，所以EPP接口电路中需要有接收器MC1489与之对应；因为MC1489接收到的数据为串行数据，故需要串并转换电路。另外，接口电路还要产生EPP协议握手信号。数据采集系统与主控制器通信的通信板可以很好的实现上述功能。通信板上有CPLD和接收器MC1489，其功能就是负责与计算机通过EPP协议进行数据通信，将接收到的串行数据转化为并行数据送入并口。CPLD可以通过引出的I/O接口灵活方便的实现与并口的通信。EPP接口结构图如图5.7所示。

图5.7 EPP接口结构图

Fig. 5.7 Structure of EPP interface

图像数字器中 A/D 的采样率为 5MHz, 而 EPP 协议的最大速率为 2MB/s, 所以为速度相匹配数据需要经 SRAM 缓存; 数据经 SRAM 缓存以后通过发送器 MC1488 将数据通过三线串口输入到通信板上的 MC1489 转化为有效信号, 然后经 CPLD 内部逻辑转化为并行数据, 并通过 CPLD 产生与并行口的 EPP 握手协议, 与计算机并口进行通信; 计算机将采集到的数据以图形显示出来。其中, 将 CPLD 内部逻辑转化的 8 位数据与并行口数据口 D[0-7]相连, 并行口引脚的 4 个控制端口中只使用了 2 个状态端口 nDrtrb 和 nWait 信号, 为系统的升级留了很大空间。

通信板所用的 CPLD 为 XC95216。XC95216 是 Xilinx 公司 XC9500 系列 CPLD 中的一种, 该系列 CPLD 可满足在系统可编程的要求, 增强的引脚锁定性能可避免更改电路板, 扩展的 JTAG 指令集允许对编程模式和在系统调试进行控制, 最少 10000 次的编程/擦除周期可实现系统区的重新配置和升级。

XC95216 器件包括 12 个功能块(FB)和多个 I/O 模块, 并通过 FastCONNECT 开关矩阵实现内部连接。I/O 模块完成不同电气特性下对输入/输出信号的驱动与匹配。每个功能模块包含 18 个宏单元, 宏单元是 XC95216 的基本结构, 由一些与、或阵列及触发器构成, 每个都可以独立配置为通过组合或寄存器实现功能。FastCONNECT 开关矩阵可完成布线功能, 以线与的方式实现不同宏单元输入与输出项之间的连接<sup>[31]</sup>。

CPLD 采用了 Xilinx ISE 5.2 开发环境。在设计输入方法上采用了 Verilog 硬件描述语言法; 采用了 ModelSim 5.5 进行仿真; 综合工具采用了 ISE 中内嵌 XST; 另外实现及配置工具采用了 ISE 自带工具。

### 5.3.2 软件设计与实现

系统软件可分为下位机软件和上位机软件两大部分。下位机软件, 即 CPLD 芯片程序的编写, 采用 Verilog 硬件描述语言, 可灵活实现接口所需要的各种功能。上位机图像采集软件是在 Windows 2000 下在 Visual C++ 6.0 环境下开发和实现的; Visual C++ 是在 Windows 环境下的一种功能强大、使用非常广泛的可视化编程工具, 它提供了丰富的关于位图操作的函数, 为开发图像处理系统提供了极大的方便。下面将结合 EPP 通信协议详细的介绍上下位机的软件设计与实现。

#### (1) 下位机软件设计与实现

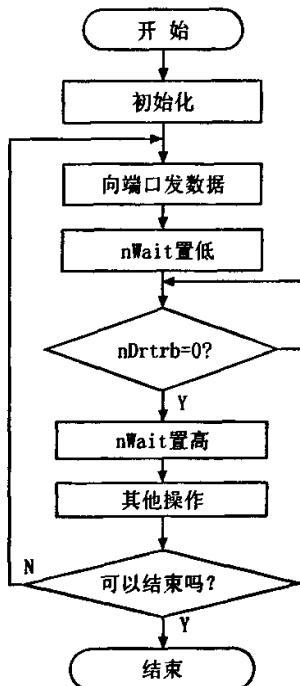

利用 EPP 并行接口实现通信板与计算机连接, 关键问题是结合 EPP 数据读写周期产生握手信号。从对 EPP 协议描述及图 5.4 可以看出, 外设在接收数据时将 nWait 拉低, 当 nDrtrb 跳到低后, 完成准备接收数据准备工作后, 将 nWait 拉高, 在 nDataStr 的上升沿将数据读入, 然后将 nWait 拉低, 做好接收下一个数据的准备。下位机流程图如图 5.9 所示。

图 5.8 下位机设计流程图

Fig. 5.8 Flow chart of lower computer

图 5.9 上位机设计流程图

Fig. 5.9 Flow chart of upper computer

检测系统以同步串行通信的方式向通信板传送数据。此串行通信的时钟信号由相机板提供。通信板上的 XC95216 先对相机板所发送的数据进行缓存，在每个时钟信号(clk)的上升沿读取一位数据(datain)，实现数据的串并转换，当其内计数器计为 8，且接收到信号板发送的锁存信号(en)时，则在锁存信号的上升沿将移位寄存器内 8 位数据锁存。XC95216 首先将 nWait 信号置低，然后检测 nDstrb 信号是否为低，当检测此信号为低时，在下一个时钟将之取反，满足了数据读周期时序要求，实现了 EPP 握手信号的实现。

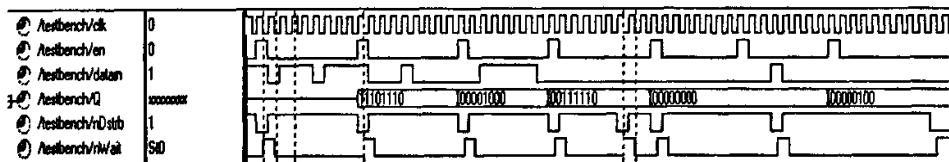

图 5.10 为 XC95216 的内部功能仿真时序图。通过仿真图可以得知 CPLD 很好的实现了数据的串并转换和 EPP 握手信号的产生(实际产生的握手信号在 6.2.7 中给出)。

图 5.10 XC95216 内部功能仿真时序图

Fig. 5.10 Time sequence diagram of XC95216 interior function

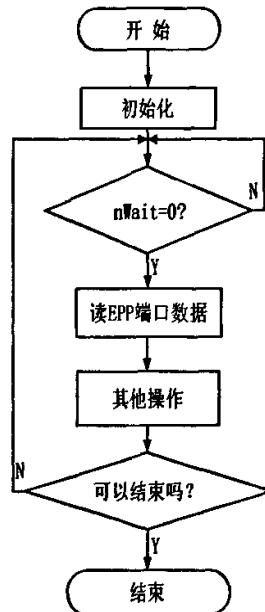

## (2) 上位机实现并行口 EPP 方式下的编程协议

上位机程序的功能主要完成数据的采集和将采集的数据以波形的显示。整个程序设计主要分成数据采集模块和波形显示模块。数据采集模块就是使用 VC++ 6.0 建立的静态的 MFC 应用程序，同时在控制面板上配置相应的控件，并将这些控件和需要执行的动作及底层操作函数相关联，实现用户的交互性功能，并按照 VC++ 6.0 调用动态链接库函数的方法进行添加源代码，完成控制面板的控制数据采集功能。波形显示模块的设计方法就是先在控制面板上定义一个矩形区域，规定好适合控制面板的坐标，根据采集的数据转化为可显示的坐标范围，在转化后的坐标处显示一个点，将采集到的一行 CCD 像素中相邻的两个点通过直线连接起来，就形成了一次积分时间采集到的波形，然后进行 CCD 信号下一行数据的采集<sup>[32]</sup>。

一般，在Win2000操作系统中程序开发者在应用程序级，即“用户模式”下，不能直接访问硬件。硬件的访问只限于操作系统通过设备驱动程序访问。这些设备驱动程序工作在“内核模式”，与操作系统处于一个级别。而编写设备驱动程序又是相当困难的，常常需要深入Windows底层去才能开发与特定硬件相匹配的属于系统的设备驱动程序<sup>[33]</sup>。为了解决上述问题，本文使用了已经编写好的驱动程序inpout32.dll，它提供两个函数inp32()和outp32()，调用这两个函数的话就可以写出在Win2000操作系统下通用的并口读写程序。它以DLL(动态连接库)的形式链入Win2000操作系统底层直接对I/O端口进行操作。这样，在VC++ 6.0应用程序中需要进行某种I/O端口操作时，调用相应的库函数，在该函数执行到用于控制I/O操作的API函数时，Win2000的I/O管理器将形成1个相应的I/O请求包交给该虚拟设备驱动程序，由相应的驱动程序例程调用硬件抽象层函数来完成指定的I/O端口操作。在使用inpout32.dll之前，应在VC工程设置中加入“.lib”、“.h”文件的路径，然后将inpout32.dll文件拷贝到工程目录下，然后就可以根据动态库中函数的参数要求调用相关函数了。

EPP 协议使用的简便还体现在它的软件编写上，EPP 完成对接口的读写只需调用数据输入语句 inp32() 和数据输出语句 out32() 就可以读写 2-9 脚(对应 D0-D7)的数据。上位机工作流程图如图 5.10 所示。当上位机将数据读取之后，就是将接收到的数据进行波形显示。首先在控制面板上创建一块合适的矩形显示区域，然后使用在显示区域上绘图的方法显示波形，最后添加各种操作功能完善各种命令。

## (3) EPP握手协议中关于超时的讨论

在握手协议的编写过程中需要注意，当nDstrb或nAstrb变为低电平后，需要nWait回送信号来实现联锁握手。这就限制外设必须在10μs内将nWait置为高电平。如果nWait没

有在规定的时间范围内变高，超时位(状态端口位0)将被置为1，就会发生超时错误，终止EPP周期。在某些系统中超时可能引起数据传输的阻塞。

关于超时位的讨论涉及到两个不同的EPP协议EPP1.7和EPP1.9。EPP接口最先有EPP1.7标准定义，由于硬件厂商的原因，EPP现有两个标准：EPP1.7和EPP1.9，可以在BIOS中进行设置。两者有如下不同点：

① EPP状态端口寄存器的最低位bit0，在EPP1.7中没有定义，在EPP1.9中定义为TMOUT。在EPP操作时序中，如果PC机数据(地址)选通信号变低后，且在10μs时间内，外设未能将nWait置为低，则TMOUT置1，表示超时。

② EPP1.9标准中，只有当nWait为低时，才能开始一个周期；但在EPP1.7中，无论nWait状态如何，nDstrb(nAstrb)都会被置低，从而开始一个新的数据(地址)操作周期。

本文所选主机BIOS默认为EPP1.9协议，因为超时位的存在，在使用并口EPP模式时超时位的检查和清除就变得十分必要。不同的芯片厂商清除超时位的方法又不尽相同。归纳起来超时位的清除共有以下三种情况：向状态寄存器第0位写1；向状态寄存器第0位写0；连续两次读状态寄存器第0位。经过实际测试使用第一种清除超时位的方法。

## 5.4 样本数据的采集与传输

相机控制板的A/D速率为5MHz，主控制板处理数据的时钟频率不能大于1MHz，EPP协议的最大传输速率为2MB/s，所以在发送采集数据前，要将采集的数据通过SRAM进行缓存，而且发送时钟频率不能太高。

在PC机上位机VC显示界面上要显示1024个像素，而在光电分选机主控制板中需要的像素要根据实际情况来设定，所以需要一个信号来控制一帧图像中的发送的有效像素个数。故在程序中根据信号countclk电平来决定像素的个数：信号countclk为低电平时，是有效的像素点；在高电平时，不将这些数据写入SRAM中。

下面将根据图5.12说明相机控制板如何将一帧数据传送到计算机并口的具体过程。信号ask是开关信号，在实验过程中用拨码开关进行控制，拨码开关与FPGA的P167脚相连，当拨下开关时，P167脚置低电平。当系统时钟CLKIN的上升沿检测到ask高电平时，则将用于存储传送数据信号的中间变量信号response置高。如果在response为高电平时，相机控制板就开始存储数据，会导致上传的样本数据可能不是一帧完整的CCD图像数据。当行尾定标信号CAL的下降沿检测到response高电平时，存储一帧样本数据的标志信号wmemory置高，等待下一个CAL的下降沿到来时wmemory置低，这样外部存储器就能根据标志信号wmemory存储一帧完整的CCD样本图像数据。这样

的话，外部存储器在信号 wmemory 为高且 countclk 为低状态下才开始存储样本数据。这样就很方便的控制了一帧采集数据像素的多少，实现了数据的有效采集。

图 5.11 写样本数据时信号时序仿真图

Fig. 5.13 Signal time sequence simulation chart once writing sample data

采集到的数据写入了 SRAM 以后，需要将采集到的数据从 SRAM 中读出并通过同步串行接口传送给通信板的 CPLD。cpend 是数据传输通信的开始标志信号，它是由 countclk 信号的上升沿检测到存储标志信号 wmemory 的高电平产生的。一旦系统时钟 CLKIN 上升沿节拍检测到 cpPEND 为高电平，相机控制板就要发移位时钟 cp20 给 CPLD 板，本课题设计中，设定与主控制板传输通信的移位时钟 cp20 的频率为 500KHz，与计算机并口的通信速率设为 800KHz。1 个字节的图像数据组成一组进行传输，与主控制器的传输样本数据时的信号时序仿真结果如图 5.14 所示。存储器读信号 OE 的时钟周期是移位时钟周期的 8 倍，即每 8 个 cp20 节拍产生一个读信号。EN 是块传输的使能控制信号，每 32 个 cp20 节拍产生一个使能控制信号。DO 是把读出的样本数据进行串行移位的输出数据，因为在仿真中，外部存储器中的数据为不定值，所以仿真图 5.14 中的 DO 的值也为不定值。发送给计算机并口的时序波形图与图 5.14 不同的只是传送的速率 cp20 变为了 800KHz，锁存信号 EN 以每 8 个字节进行锁存。

图 5.12 传输样本数据时信号时序仿真图

Fig. 5.12 The sample data's reading signal time sequence simulation chart

## 6 系统抗干扰设计和电路的调试与分析

### 6.1 系统的抗干扰设计

一个完整的光电分选机信号采集处理系统中有大量的器件，其中包括 FPGA、SRAM、线阵 CCD 和 A/D 等器件，因此电路较为复杂，且系统中的时钟频率较高，这样电路中的各种信号极易受到噪声的干扰。因此，系统抗干扰性能设计就显得尤为重要。

#### (1) 系统中元器件选择处理

元器件是构成部件或系统的基础，应尽量选择集成化程度高，抗干扰能力强，功耗小的器件。本系统中在 CCD 驱动电路的实现上采用可编程逻辑器件实现，CCD 信号的调试与 A/D 转换电路也选用了集成的专用图像数字器来实现，实现了器件的高集成化，提高了抗干扰能力。

#### (2) 系统中元件布局处理

各种电子元件在 PCB 板上的不同布局会影响整个系统的电磁干扰，因此在布局上，要把模拟信号部分、高速数字电路部分、噪声源部分三部分合理地分开，使相互间的信号耦合为最小。本硬件设计电路把 FPGA、SRAM、图像数字器和线阵 CCD 等器件规划在相机主板上，将系统的电源电压模块和用于通信的接口模块规划在相机电源板上，最后用电缆将两块电路板插接到一起。在每块电路板上各部分元件之间的引线尽可能短，减少了各种电磁干扰。

#### (3) 系统中电源和地线处理

本文中系统采用了四层印刷电路板技术，其中中间两层为 VCC 和 GND 层，上下两层为信号走线层，这样保证了几乎无限的电流吸收能力，起到防止噪声和在 PCB 板上为逻辑信号提供屏蔽的作用。由于系统中有数字电源和数字地、模拟电源和模拟地，但是系统主要以数字为主，所以 VCC 和 GND 层设计为数字电源和数字地层，模拟电源和模拟地以走线相连。虽然 VCC 和 GND 平面有增加走线电容负载的趋势，但是它们显著地减少了系统的噪声，大幅度地提高了系统的可靠性。模拟电源和模拟地不能提供整个平面，因此走线尽可能宽。最后在上下两层分别在数字部分铺数字地和在模拟部分铺模拟地。为了减少噪声干扰，通常在电源进入电路板处安装一个  $100\mu\text{F}$  的电解电容器，滤除低频干扰。模拟电源和数字电源、模拟地和数字地一般情况下是分开的，最后只在一点连接。为了减少噪声对元器件的干扰，在 IC 的每一个 VCC 和 GND 引脚之间接上一个  $0.1\mu\text{F}$  的小电容滤除高频干扰，而且要尽可能靠近器件。

#### (4) 系统中驱动电路处理

为正确驱动线阵 CCD 正常工作,采用了 16bit 的快速 CMOS 线驱动器 74HCT244TV 来增加电流驱动能力。为提高分选机信号采集处理系统与其他系统间通信的可靠性,在收发信端分别采用了 MC1488 和 MC1489 线驱动器,来提高信号的抗干扰能力。

## 6.2 系统的电路调试与分析

在完成系统的硬件及软件设计后,还需要对系统进行严格地调试。只有通过调试,才能发现问题,才能不断地改进与完善系统的设计。

本文对线阵CCD驱动模块、CCD信号调理及A/D转化模块、SRAM存储模块、通信模块、电源模块、计算机并口通信模块都进行了调试,并使各功能单元都满足了设计要求。下面在简单介绍了系统的调试方法以后对本文所设计的主要模块的调试过程进行了说明。

### 6.2.1 系统的调试方法简介

在系统调试的过程中,由于系统的复杂程度较高。需要采用一些调试的方法,这些方法不仅能够提高调试的速度,更关键的是能够提高调试的成功率,以下是本文中所使用到的一些调试方法:

(1) 信号测试点设置:在设计时,为了验证板上的各个元件间通信是否正常,各个元器件设计功能实现是否正确,便于用仪器来观察信号波形,需要为调试中用到的重要信号设置测试点或借助于标准的插座将信号引出,特别是对于FPGA这样的管脚密集的芯片。在设置信号测试点以后要加强对测试点的保护,避免测试信号之间由于非法接触产生短路损坏元器件。

(2) 手工复位设置:将电路中添加按键开关为系统提供硬件复位信号,这是在早期的调试工程中,系统的多个器件可能会进入非法工作状态;为使系统可以初始化,各部分重新进入缺省状态,手工复位是最简单的方法。

(3) 拨码开关设置:拨码开关是为了满足系统灵活性的要求,为不同模式预留的一些设置手段,对于调试是非常方便的,而拨码开关或跳线是较好的实现手段。

(4) 在使用示波器进行时序观察时,最好使用两个通道进行观察,这样才能找出各信号之间地相位和时序关系。

(5) FPGA/CPLD的调试过程中,可以先编写小段测试程序,如产生时钟分频信号的程序等。在测试程序顺利通过后,再去调试大的程序,这主要是为了保证FPGA/CPLD能够正常工作。

### 6.2.2 FPGA 和 CPLD 的调试

先检查FPGA的电源和地，接上下载电缆线，上电测试。在Xilinx ISE 7.1 开发环境下，设计一个简单的时钟分频电路，将生成的BIT文件下载到FPGA后，iMPACT软件显示下载成功，检查FPGA的DONE引脚为高电平，在相应的引脚用示波器看是否能正确的观察到波形。如果波形正确说明工作正常，不正确则对电路进行检查，找到问题解决后继续上面过程。

对CPLD的调试则需要通过将生成的JED文件通过电缆线下载到CPLD中，然后通过生成的程序来对其特定引脚测试来完成。

### 6.2.3 CCD 驱动的调试与分析

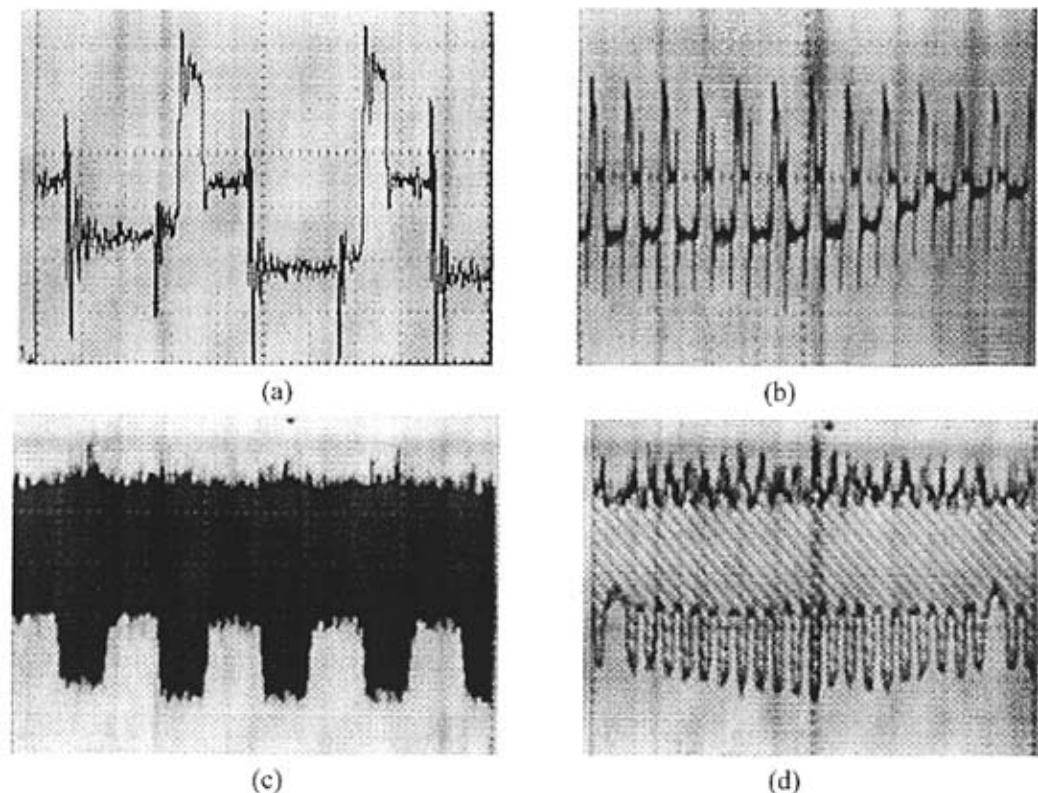

以焦距为 35mm 光学镜头和 CCD 组成摄像机，采用红光 LED 前景照明方案，对条形宽度为 3mm 的等间隔黑白相间的条纹图进行扫描。

在进行 CCD 驱动信号的调试分析时，首先对六路驱动信号进行测量，在都满足时序的要求下再对 CCD 接口驱动电路中  $V_{out}$  信号输出进行测量。保持线阵 CCD 和条纹图都静止不动，用示波器观察 CCD 正常工作时的波形如图 6.1 所示，(a)为输出电荷信号  $V_{out}$  通在示波器扫描频率为 2.5MHz 时得到的图像，像元的复位电平、参考电平和有效电平可以清晰的从图中看到。(b)为调节示波器的扫描频率后  $V_{out}$  的输出波形，从图中可以看到像元的有效电平大小不等：经实验可知有效电平与参考电平差值较大的像元对应为白色条纹，较小的对应于为黑条纹部分，所以可知白色条纹的幅值较大。继续调节波器的扫描频率可以得到图(c)，从图中可知对等间距的黑白条纹扫描，会得到一行高低相间的波形信号，而且高低相间的宽度几乎相同，说明黑白条纹的宽度相同。在扫描频率为 3KHz 时，将会得到了一帧完整的 CCD 数据图像，如图(d)所示：图中左右两端白色空隙的部分各有 27 个哑像元，而且其有效电平与参考电平的差值最小；左右 27 个哑像元之间的图像即为在镜头视场中出现的黑白条纹的图像。通过实验观察到输出电荷信号幅度  $V_{out}$  输出的正常电荷电压值随着光照的改变而改变，光照减弱，电荷量减小，信号电压亦减小，反之，光照增强，电荷量增加，信号电压增大；CCD 所需的光照强度与驱动 CCD 的频率有关，频率越高则所需的光照强度越大，反之则越小。一帧数据中出现等间距条纹的波形的个数与镜头的视角有关，当出现在镜头中的黑白条纹越多时，出现的等间距的倒置方波个数越多。从图 6.1 我们可以看到一个像元中有很大的噪声，而且有的噪声是固定噪声，所以需要进行消噪处理；经示波器测量白色条纹的电压幅度为 80mv~130mv，幅度较小，因此需要进行放大处理。

图 6.1 驱动 CCD 正常工作的波形图

Fig. 6.1 Waveforms when CCD is driven to work order

#### 6.2.4 图像数字器调试

图像数字器是一个集成的芯片，在调试过程中需要通过SPI总线对其进行正确的配置之后才能正确工作，其中关键的一环就是相关双采样时钟SBLK和SPIX的控制与实现。这两个时钟是由FPGA产生的，通过对FPGA的编程实现对采样点的位置的改变。在实验过程中采取FPGA粗调、A/D细调的方法来实现。首先通过编程将两个控制信号与CCD的控制信号对应起来，使得CCD输出信号和采样点的位置同步，然后通过软件对、A/D的实际采样点实现纳秒级的调试，找到最佳的调试点位置。采样点的位置对所成的图像影响很大，测试时当采样点都采用最小的时候，得到一幅全黑的图像，说明两采样点重合，当延迟一段时间以后，可以得到清晰的图像。

CCD 摄像机对等间隔黑白相间的条纹图进行扫描，扫描结果经 A/D 数字化，放入外部存储器中进行缓存，然后从存储器中把数据读出，可以用示波器观察图像数据。为了更方便的实现图像数字器的调试，本文采用基于 EPP 方式将缓存过的数据通过通信板

传送给计算机，计算机通过编程将数据实时的显示出来的方法，其采集到的数据在 EPP 调试模块中将加以介绍。

### 6.2.5 SRAM 调试

调试 SRAM 的正确存取，即控制信号是否正确，即在同一个地址写进去的数据是否与读出的数据一致。先用 Verilog 编写一个简单的 SRAM 控制模块来验证其是否正常工作，将验证程序下载到 FPGA 中，通过示波器观察验证结果，波形显示在 SRAM 的同一地址上写入数据和读出数据一致，证明数据读写命令正常。

### 6.2.6 相机板与主控制板之间的通信调试

相机控制板接收由主控制板发出的移位时钟信号  $rCP$ ，使能信号  $rEN$  和串行输入信号  $rDO$ 。经验证发送与接收数据相同，证明主控制器和相机板之间通信正确。

当相机板接收到功能码为样本采集命令帧后，将 1024 个字节的数据以计数加一的方式放入外部存储器中进行缓存，然后以每次传送 4 个字节的同步串行通信方式传送给主控制板。在试验中相机板发送固定的数据传送给主控制器，主控制器接收到数据在单片机的存储器中验证，经过验证发送与接收一致，证明相机板与主控制器之间通信正确。

相机板和主控制板的三线制同步串行通信，均由数据发送方提供同步时钟。主控制板发送数据给相机板的最高时钟约为 800KHz，这是由主控制板上的 PIC16F877 的系统时钟所决定的；而相机板发送数据给主控制板时，由于 PIC16F877 接收和存储一帧数据的时间约为  $32\mu s$ ，所以通信时钟频率要小于 1MHz，本文在实验时采用了 500KHz，足以满足通信要求。

### 6.2.7 数据采集显示模块调试与分析

在整个数据采集系模块调试过程中，上下位机之间的通信调试比较复杂，也是调试的重点。因为在本系统的设计中，脱离了相机板，计算机不能完成任何工作，同样，离开了计算机软件的控制，相机板就不能将数据传送给计算机，二者联系起来的桥梁就是通信。通信功能的调试包括能否通信和通信是否正确两个方面，CPLD自行设计测试程序进行测试，PC机可以使用并口通信助手进行测试。

首先将整个系统连接起来。首先将相机电源板与相机控制板通过电缆连接，这样能够很方便的测试关键引脚。相机控制板 25 针插座接口 B 与电源相连，25 针插座接口 A 经电缆线与通信板的 24 针插座 JP2 相连；相机控制板 MC1488 的与 FPGA 连接，并通过 MC1489 与 CPLD XC95216 的 P153、P152、P151 连接，这三个信号分别为 EN、DO 和 CLK；通信板上的 CPLD 的 P3、P5、P7、P9、P11、P12、P13、P14、P24、P25 引

脚分别并行口的 D0~D7、14 脚(nDstrb)、11 脚(nWait)通过电缆线连接连接；并口的地线连接到一起接通信板的地线。

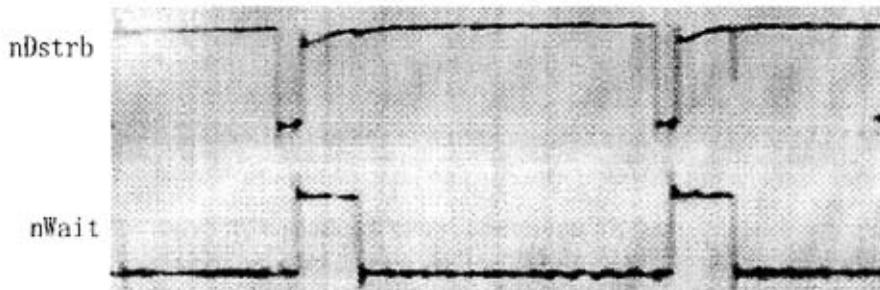

在通信板 CPLD 逻辑电路与 PC 机软件调试成功以后，就开始对握手电路进行调试。首先运行上位机 VC 程序对计算机并口进行查询，然后将 FPGA 通信程序配置下载到 XC3S50 上，拨动拨码开关发送请求发送数据命令，相机控制板将特定的数据通过通信板发送到并口，上位机检测相机控制板输入数据，此时可以通过示波器测试握手信号 nDstrb 和 nWait 波形。在电路设计正确的情况下，握手信号波形应满足设计要求，否则，修改 CPLD 程序和 PC 上位机程序，直到信号波形满足要求为止。在示波器上观察到的通信握手波形图如图 6.2 所示。与图 5.4 相比较可知，nDstrb 和 nWait 两个信号很好的满足了数据读周期时序要求，并且通过示波器字标可知 nWait 信号在  $10\mu\text{s}$  内置低，没有产生超时。值得大家注意的是，在并口 EPP 协议调试中要注意对超时位要及时清除，否则就会出现超时错误，造成数据堵塞。超时位清除方法参看 5.3.2 节。

图6.2 握手信号波形图

Fig. 6.2 Waveform of handshake signal

通信握手正确以后就可以进行数据发送接收功能的调试。在 CPLD 的输入管脚通过示波器观察输入的串行数据，输出脚查看并行数据。PC 机可以使用并口助手，由 CPLD 发送 8 位数据，在 VC 程序中显示数据，并与并口帮助的数据相比较，如果三者数据一致，则表明系统可以进行正常数据通信了。

由 EPP 协议可知其传送速率最大可达  $2\text{MB/s}$ 。但是在实验过程中发现，当相机控制板发送的时钟频率在大于  $1.2\text{MB/s}$  的速率后，上位机 VC 程序就不能正常的工作。经实验可知系统在  $500\text{KB/s} \sim 1000\text{KB/s}$  时，显示界面正常，接收数据正确，故实验中最终选定  $800\text{KB/s}$  的传送速率。

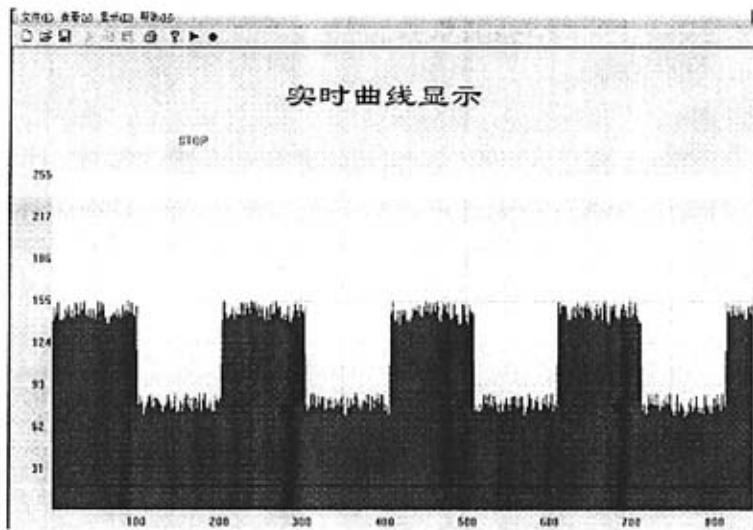

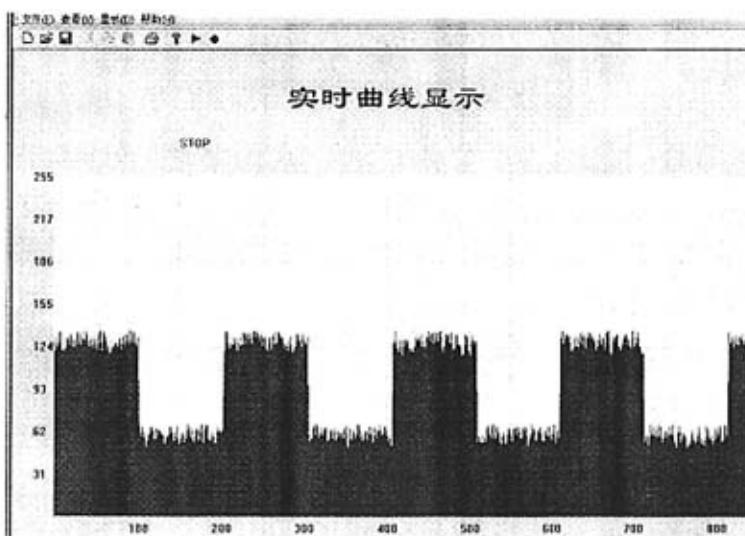

在经过上下位机系统的调试以后，就可以进行数据采集与实现了。保持线阵 CCD 和等间距的黑白条纹静止不动，将 FPGA 程序下载，对条纹对进行扫描；上位机将图像采

集显示程序打开并运行，按下请求发送数据开关，启动发送一帧数据命令，此时采集到的数据显示在屏幕上。此时，就可以很方便的观测由A/D采集到的数据，并可以根据显示图像分析图像数字器的工作情况，然后根据分析修改FPGA的程序，使图像数字器能够正常工作。下面的两幅图是在光照强度不同的情况下对黑白条纹采集到的数据。

图 6.3 数据采集波形图 1

Fig. 6.3 Waveform 1 of data acquisition

图 6.4 数据采集波形图 2

Fig. 6.4 Waveform 2 of data acquisition

由图 6.1(c)可知 CCD 相机每扫描一帧等间距的黑白条纹图像数据, 会得到一行接近于方波的波形信号, 在经过图像数字器相关双采样处理以后也会是一行方波。方波出现的个数由相机的视场所决定。经分析可知, 将图像数字器的处理以后得到的数据经过 SRAM 缓存以后经通信板发送到 PC 机以后, 输出来的信号是也应是高低相间的波形, 如果是这就说明图像数字器正常工作了, 反之, 则说明图像数字器没有正常工作需要对其控制时序进行调整, 其中主要的就是两个抽样点的控制时间控制调整很重要。经过实验得到正确的波形图如图 6.3 和图 6.4, 图中幅值较高的电平是白色条纹, 较低的电平是黑色条纹, 其电平的因为光照的强弱而不同。如图 6.4 可以看出, 由于噪声等影响, 其幅度有变化, 黑色电平幅值大小大约 70 左右, 白色电平幅值大约在 140 左右。我们还可以根据图像数字器图像数字器的 A/D 采样转换公式与图像数字器的可编程放大器增益公式得出黑色条形和白色条形中像素点的视频电压。

## 结 论

本文研究了一种基于 FPGA 的高速线阵 CCD 的数据采集系统。提出了线阵 CCD 的驱动电路和逻辑控制电路的时序实现方法，利用 FPGA 技术完成驱动时序的设计；通过 FPGA 控制图像数字器对 CCD 输出的模拟信号进行了信号调理和模数转换；完成了数据缓存电路的设计；自定通信总线协议，建立了同步串行通信系统，用 Verilog 语言实现了样本数据采集与传输设计；设计了数据采集电路与计算机并口通信的 EPP 接口电路；下位机利用 CPLD 技术完成了 EPP 握手信号和串并转换电路设计，上位机利用 VC++ 完成了并口的可视化控制平台开发。最后经过大量的实验调试，完成了课题设计要求。以下是本文设计上的几个主要特点：

- (1) 核心控制电路采用 FPGA 技术，实现了 CCD 的驱动时序、采样时序、存储与通信程序，满足了系统实时性的要求，使系统具有小型化、抗干扰及方便更改和升级的优势。

- (2) 本系统采用两片 SRAM 存储结构，具有非常高的数据传输速率。

- (3) 采用图像数字器，不仅很好地抑制了 CCD 的复位噪声，而且实现了信号的可编程增益放大和 10 位精度的模数转换，进一步提高了系统的集成度，抗干扰能力。

- (4) 采用并行口作为数据采集系统和计算机的通信接口，提高了系统的安全性，满足了中速数据采集的要求，而且可以图形化的观测信号采集情况，为以后实验打下良好的基础。

下面是本系统设计可进一步进行的研究工作：

- (1) 完善数据采集系统和计算机并口 EPP 通信协议，完成数据采集系统双向通信。

- (2) 完善 FPGA 中编写的各种程序，减小占用芯片资源；在 FPGA 中加入多种算法，使系统更有效地抑制 CCD 的各种噪声。

## 参 考 文 献

- [1] 张诚彬, 陆锡华. 色选机及其在粮食工业中的应用. 粮食与饲料工业, 1995, (1):1-4.

- [2] 张麟. 光电色选机及其应用. 农机与食品机械, 1997, (5):24-27.

- [3] 徐洪吉. 葡萄干颜色分选机的研究: (硕士学位论文). 长春:长春理工大学, 2002.

- [4] 范平. 浅析色选技术在中国的发展过程. 粮食科技与经济, 2005, (4):46-47.

- [5] 孟楚年等. 大米色选机. 粮食与饲料工业, 1997, (3):15-18.

- [6] 王诚, 薛小刚, 钟信潮. FPGA/CPLD 设计工具—Xilinx ISE 5. X 使用详解. 北京:人民邮电出版社, 2003.

- [7] 孙航. Xilinx 可编程逻辑器件的高级应用与设计技巧. 北京:电子工业出版社, 2004.

- [8] XILINX. Configuration and Readback of Virtex FPGAs Using (JTAG) Boundary Scan. Application Note, 2003, 12.

- [9] Kim Goldblatt. The 3.3V Configuration of Spartan-3 FPGAs. Application Note, 2005.

- [10] 徐欣, 于红旗, 易凡. 基于 FPGA 的嵌入式系统设计. 北京:机械工业出版社, 2005.

- [11] 夏宇闻. Verilog数字系统设计教程. 北京:北京航空航天大学出版社, 2003.

- [12] 王庆有. CCD 应用技术. 天津: 天津大学出版社, 2000.

- [13] 蔡文贵, 李永远, 许振华. CCD 技术及应用. 北京:电子工业出版社, 1992.

- [14] 黄素贞, 尹立新, 张国梁. 基于 CCD 的图像采集处理系统的研究. 电子技术应用, 2004, (10):69-72.

- [15] 佟首峰, 阮锦, 郝志航. CCD 图像传感器降噪技术的研究. 光学精密工程, 2000, 4(2):140-145.

- [16] 李艺琳, 冯勇, 安澄全. 用相关双采样技术提高 CCD 输出信号的信噪比. 电测与仪器, 1999, (5):31-32.

- [17] 万文, 王学良, 汪骏发. 基于 XRD98L61 的线阵 CCD 图像采集系统的设计. 电子技术, 2002, 6:378-382.

- [18] 葛云涛. 怎样选择摄像机. 丰唐光电技术资料, 2004.

- [19] 王忠. 我国谷物色选机应用技术现状及发展趋势. 农机化研究, 2006, (4):23~25.

- [20] 黄鸽. 光电分选机检测系统设计与实现: (硕士学位论文). 大连:大连理工大学, 2005.

- [21] XILINX. Spartan 3 Families Field Programmable Gate Arrays. Product specification. 2004.

- [22] PerkinElmer optoelectronics. P Series Linear Photodiode Array Imagers. Datasheet, 2002.

- [23] EXAR Corporation. XRD98L59-CCD image digitizers with CDS, PGA and A/D. Datasheet, 2001.

- [24] 陈朗, 王瑞. MPEG-4 系统中基于 FPGA 实现数据采集及预处理. 微计算机信息, 2005, 21(9):109-112.

- [25] Integrated Device Technology 3.3V CMOS Static RAM 4 Meg(256K × 16-bit) CY7C199. Datasheet, 2003.

- [26] Kahkoska J. Ease the debugging of Serial Peripheral Interfaces. Electronic Design, 2001. 10(49):63-64.

- [27] 刘爱华. 自制稳压电源. 实验技术与管理, 2005, (10): 79-91.

- [28] 贺纲, 安世奇, 江杰. EPP 模式下并行口与设备高速通讯的实现. 包头钢铁学院学, 2003, (6): 163-171.

- [29] 符冬阳, 贺贵明. 增强并行口EPP 协议及其应用. 计算机应用, 2001, (10): 62-63.

- [30] 薛斌. 基于EPP技术的CCD数据采集系统的设计研究: (硕士学位论文). 秦皇岛: 燕山大学, 2003.

- [31] XILINX. XC9500 In-System Programmable CPLD Family. Product specification, 1999: 1-16.

- [32] 侯整风, 胡军. VC++实现计算机并口的直接输入/输出. 淮南工业学院学报, 2002, (6): 33-37.

- [33] 杨定新, 葛哲学. 保护模式操作系统中使用WinDriver开发设备驱动程序. 微型机与应用, 2002, (1): 10-12.

## 攻读硕士学位期间发表学术论文情况

李明伟, 宗献波, 盛楠. 基于 CAN 总线的电梯轿厢控制器设计. 仪器仪表用户(由中国仪器仪表学会节能应用技术学会, 天津自动化仪表公司主办), 2006, 6. P34-P35. 属于学位论文第 5 章.

## 致 谢

在完成这篇论文之际，我要向在我研究生学习生活的两年半时间里给予我关心帮助的老师、同学、朋友们表示感谢。

首先我要感谢我的导师李明伟副教授。李老师严谨求实的治学态度，不辞辛劳的工作作风，对前沿科学的远见卓识，以及勇于开拓创新的精神，将令我受益终生。当我在研究中遇到问题时，李老师总能给予我悉心指导，使我顺利地完成了预定的研究任务；李老师在生活上也给予我无私的关怀和帮助，他教会了我治学，更教会了我做人，学生所取得的点点滴滴的进步都凝聚了他的心血与关爱。在此谨向恩师致以最崇高的敬意和衷心的感谢！

衷心感谢李承斌教授。李教授一直都在关心和帮助着我，常在百忙之中给我补充丰富的理论知识，帮助我解决学习上和生活上的难题，李教授以其严谨的治学态度和勤奋的工作作风为我树立了榜样。

另外，还要感谢本教研室的所有同学。感谢黄鸽师姐和杨光伟在课题开展过程中的积极帮助，感谢盛楠同学在生活学习中的帮助，感谢谯洋同学对我论文校正提出的宝贵意见，也感谢王用涛、张献梅、张倩同学对我生活和学习的无私帮助。

特别感谢多年以来一直关心和支持我的父母、亲友，他们的无私奉献是我永远难忘的。

最后，向关心和帮助过我的所有人表示感谢。