## 摘要

随着无线局域网应用不断扩展，通信市场对无线收发芯片的需求急剧上升。通常，射频接收机结构以超外差为主，并采用SiGe技术的BICMOS工艺进行射频收发模块的设计。这种方法最大的优点是具有极好的选择性和灵敏度，同时射频模块可完成高性能指标，但集成度及成本较高。近年来，随着移动通信的发展，成本和集成度成为无线局域网大规模推广应用的主要障碍，为了降低成本、提高集成度，需要采用Si技术的CMOS工艺来实现无线局域网射频芯片，同时接收机结构也越来越趋向于采用零中频接收机结构。

基于 WLAN802.11b 接收机射频前端的 CMOS 实现方案，本文采用二次变频的零中频接收机结构，根据 WLAN802.11b 标准规定，推导出射频前端各模块基本指标参数，并以提高集成度，降低功耗，降低成本以及保留适当余量为原则，采用 CMOS 工艺设计低噪声放大器及低噪声混频器模块。接收机射频前端采用了 1.8V 的电源电压，在低功耗下设计低噪声放大器以及低噪声混频器，射频前端各模块的设计都考虑到了低功耗对直流工作点、增益和线性度的影响。各模块通过改进电路结构和设计合理的直流工作点，在低功耗下依然保持了良好的性能。

通过分析 MOSFET 的各种噪声，重点研究特定功耗下输入匹配方法，得出 PCSINM 匹配方法满足模块的低功耗要求。并将此方法应用在基于 Chartered 0.18 $\mu$ m CMOS 工艺设计的低噪声放大器、低噪声放大器及混频器模块融合中，得到了较好的性能。分别采用 Chartered 0.18 $\mu$ m CMOS 及 JAZZ 0.35 $\mu$ m BICMOS 两种工艺设计了同种匹配结构的单端及差分低噪声放大器，分析了各自的仿真结果，并对 JAZZ 0.18 $\mu$ m BICMOS 设计的差分低噪声放大器版图进行了初步设计。最后给出了各个电路原理图的仿真结果并进行分析。

**关键词：**低噪声放大器；低噪声混频器；WLAN 802.11b

## Design of Low Noise Amplifier Based on WLAN802.11b

### Abstract

With the development of the WLAN (Wireless Local Area Networks) in recent decades, demand of single chip RF transceiver goes up in and out of China. Superheterodyne receiver which has excellent sensitivity and selectivity has been in communication domain. The main process of designing RFIC block is SiGe. However, the problems in application of WLAN are caused by cost and integration of RFIC block. The higher integration and low power dissipation have made the CMOS process and direct-conversion receivers attract people's attention.

According to the requirement of the WLAN802.11b, This paper used direct-conversion architecture with two conversions, planning for requirements of the RF blocks. With the principle of improving integration, lowering power dissipation, lowering cost and having some surplus, this paper has designed the components LNA and low noise mixer based on Chartered 0.18 $\mu$ m RF CMOS process. The transceiver RF front-end uses the 1.8V voltage supply. In the design of the RF front-end, the effect of the low dissipation must be considered since the low power supply limits the voltage swing of the circuit nodes and may affect the DC operation point, power gain and linearity of the RF front-end. The improved, suitable biased RF circuits are proposed to keep the excellent performance of the RF front-end even with low power supply.

This paper introduces two matching design techniques by analyzing the noise of MOSFET, and applies this match technique in LNA and mixer with low dissipation, and the two blocks are both based on Chartered 0.18 $\mu$ m CMOS process. As a result, very low noise figures become possible at very low power consumption levels. Moreover, the linearity of LNA had been improved with changing the architecture of the LNA, while minimizing the degradation of gain and noise figure. The differential LNA has been designed based on the JAZZ 0.35 $\mu$ m BICMOS process. So, the characteristic and layout of the differential LNA have been summed up.

The merged LNA and mixer have good performance in low power using the PCSINM technique, the Double direct-conversion receiver which using the merged LNA and mixer can lower cost and have abroad application in communication.

**Key Words:** Low noise amplifier; Low noise mixer; WLAN802.11b

## 独创性说明

作者郑重声明：本硕士学位论文是我个人在导师指导下进行的研究工作及取得研究成果。尽我所知，除了文中特别加以标注和致谢的地方外，论文中不包含其他人已经发表或撰写的研究成果，也不包含为获得大连理工大学或者其他单位的学位或证书所使用过的材料。与我一同工作的同志对本研究所做的贡献均已在论文中做了明确的说明并表示了谢意。

作者签名: 樊岩 日期: 2007.12.24

## 大连理工大学学位论文版权使用授权书

本学位论文作者及指导教师完全了解“大连理工大学硕士、博士学位论文版权使用规定”，同意大连理工大学保留并向国家有关部门或机构送交学位论文的复印件和电子版，允许论文被查阅和借阅。本人授权大连理工大学可以将本学位论文的全部或部分内容编入有关数据库进行检索，也可采用影印、缩印或扫描等复制手段保存和汇编学位论文。

作者签名: 樊岩

导师签名: 解伟平

2007 年 12 月 24 日

# 1 绪论

## 1.1 课题背景以及意义

无线通信网的市场应用很广阔，极大地推动了射频集成电路的发展；针对不同的应用要求，无线通信网可以分为无线广域网(WWAN)，无线局域网(WLAN)和无线个人网(WPAN)，现在已基本形成在相应领域中的通信标准。从不同的方面实现了无线通信。无线局域网是计算机网络和无线通信技术有效结合的产物。为人类的无线通信，移动个性化，家庭多媒体提供了可能。

其中，无线局域网 802.11b 仍然占领主要市场，随着底层技术的发展，芯片价格不断降低，无线网络系统将在今后一段时间内得到广泛应用。在我国无线局域网尚处于初步阶段，但是无论运营商还是设备制造商对无线局域网市场都有很大兴趣。可见，对无线传输的应用研究是非常重要，也是非常必要的。近年来，无线局域网的应用的不断扩展，对无线收发芯片的需求急剧上升。目前推向市场的无线局域网收发机芯片主要垄断在 Intersil, TI, Maximum 等几家大公司手中，而且基于性能和成本的考虑，这些产品都分为射频前端和基带处理部分，分别采用 SiGe 技术的 BICMOS 工艺和 Si 技术的 CMOS 工艺来实现。采用两种不同的工艺技术无疑提高了产品成本，并且无法实现单片集成的收发机，而成本和集成度是无线局域网大规模推广应用的主要障碍，为了降低成本和提高集成度，必须研究用 CMOS 工艺来实现无线局域网射频芯片。随着 CMOS 工艺最小线宽的不断缩小和特征频率的不断提高，采用 CMOS 工艺来实现射频芯片是有可能的。采用 CMOS 工艺来实现射频芯片，不但可以降低产品成本，而且在解决了实现中的难点问题后，可以将射频前端和基带处理部分集成在一块芯片上，实现单片集成的收发机，这必将推进整个无线局域网市场的发展。研究采用 CMOS 工艺来实现无线收发机射频前端芯片可以提高我国在这一方面的研究水平，其研制成功将产生可观的经济效益。

在智能家具方面，在 2006 年 3 月的国际集成电路研讨会上展示了一个新的 ZigBee 网络无线遥控娱乐平台。在无线数据通信方面，CMOS 射频电路更是用途广泛，如报警装置、音频和神经网络等。在军事方面，利用 CMOS 射频集成电路构筑不可见的微型监控器也是各个国家所关注的研究热点。在目前备受关注的 3G 便携端类，CMOS 射频集成电路也是前景良好。据报道，在 2004 年中国的手机普及率就已达到为 32%，还有上升的空间。可见 CMOS 射频技术拥有广大的市场。

目前在 LNA 方面，根据不同应用分别采用不同的电路结构。从工作形式分，有共栅 LNA、电流复用反相器式 LNA、共源 LNA 等。但在对噪声要求比较高的时候，通常采用共源结构。在共源结构中，又有多种不同的改进形式，如共源共栅 LNA、折叠共源共栅 LNA、利用噪声关联使噪声互消的共源 LNA 等。大部分情况都是以高功耗来换取高性能。

对于零中频接收机的研究，为了克服这种接收机所带来的缺点，一些研究将重点放在了混频器的设计上。比如有一种是多相混频器。其本振信号频率是射频载波频率的  $1/N$ ， $2N$  个普通混频器构成一个多相混频器。它克服了直流失调问题和对锁相环设计的苛刻要求。还有的是将 chopper 技术应用于混频器上，通过两次变频，将噪声信号分离开。也有采用谐波混频器，使用本振信号的二次谐波和射频信号混频。这样，当射频信号被下变频到基带时，自混频的失调产物则被变换到本振频率。在混频器方面，无源混频器有许多实现方式，如环形二极管电路、双栅结构等许多的电路形式，但多数是在 Gilbert 结构的基础上对源反馈或负载端进行改进。这种改进对于接收机整体系统来讲，增加了一定的串扰，而且这样的混频器往往要消耗多余的功耗，同时增加设计难度。

另一种方法是通过对接收机结构进行改进，可以减小直流失调和  $1/f$  噪声。有人采用两级下变频代替直接下变频的方法，先将射频信号下变频到一个较高的中频，再直接下变频到基带。一方面，由于在第二次下变频时使用的本振信号频率低且固定，因而泄漏较小，直流失调相对稳定，可以容易地去除。另一方面，混频器的  $1/f$  噪声也随之降低。这种结构的问题在于需要选择合适的中频频率，使最前端的带通滤波器可以提供足够的相对于第一本振的镜像信号抑制。总之。零中频接收机结构简单，具有很高的集成度。

最后，射频电路的版图也是很重要的。由于处理的是数字信号，版图的布局和布线都将对电路性能产生很大的影响。不适当的信号通路会使所设计电路产生振荡或是引起信号串扰；器件布局不适当则会引入额外的噪声，甚至使电路不能工作；器件的不匹配等因素也会大大的恶化电路的性能，另外，在版图设计时还应考虑各类寄生效应。寄生效应除了会引入噪声之外，还会造成信号功率损失、降低增益。如果不尽可能的降低各类寄生效应，那么版图引入的噪声甚至会超过电路的本征噪声。

目前，RFIC 设计中具有代表性的设计软件工具有安捷伦 (Agilent) 公司的 ADS，Applied Wave Research 公司的 Microwave Office 和 Analog Office，Ansoft 公司的 HFSS，CST 及 Ansoft Designer，Cadence 公司的 RFIC 设计软件等。它们都具有不同的特色，一般具有友好的设计界面，灵活、开放的架构，具有从综合到版图设计等不同层次的设计模块，支持第 3 方设计、测试软件，带有使用方便的物理设计工具和模型提取工具；

涵盖了小至元器件，大到系统级的设计和分析。但 RFIC 设计工具中仍然存在很多问题，需要深入研究和解决，特别是对电路的很多潜在影响因素尚缺乏深刻认识。射频电路中许多比较关键的元件，如电感、电容等，缺乏实用的准确等效电路或集总模型。在 RFIC 设计中，即使拥有比较精确的元器件模型，但使用这些元器件模型构成电路之后，因采用布局方法的不同，将会对电路性能带来极大的差异。总之，目前 RFIC 的设计精度和自动化程度仍然落后于数字电路设计，有待继续提高。

本文阐述了基于 WLAN 802.11b 的接收机系统及其部分射频模块的解决方案，并主要针对核心电路低噪声放大器进行设计，在此基础上进一步研究了接收机前端的噪声放大器以及混频器，从而将低噪声放大器与混频器融合。WLAN 802.11b 标准规定信号工作频率在 2.4GHz，该标准提供 11Mbps 的数据速率。

## 1.2 无线局域网 802.11b 系统标准

### (1) 无线局域网的发展

无线局域网利用电磁波在空气中发送和接受数据，减少了对固定线路的依赖。作为一种灵活的数据通信系统，它的应用范围同现在的有线局域网一样广泛，但其内在的灵活性是有线网络所不能相比的。目前无线局域网主要应用于某些需要得到数据服务但缺乏有线数据接入条件的环境，如会议中心、展览中心、机场和酒店等。但随着无线局域网硬件设备价格的下降以及传输速率的提高，无线局域网的应用领域也迅速扩展到企业内部局域网、校园网、家庭、医疗、销售、仓库管理、公共事业管理等许多领域。

1985 年，ISM 频段为无线网络设备供应商提供了无需申请就能直接使用的产品频段，极大地推动了无线产业的发展。表 1.1 对目前国际上应用比较广泛的无线局域网标准进行了比较<sup>[1-3]</sup>。

表 1.1 无线局域网标准

Tab. 1.1 WLAN standards

| 标准        | 频段     | 调制方式     | 数据率       |

|-----------|--------|----------|-----------|

| HomeRF    | 2.4GHz | FH       | 1-2Mb/s   |

| Bluetooth | 2.4GHz | FH       | 1Mb/s     |

| 802.11    | 2.4GHz | FH/DS    | 1-2Mb/s   |

| 802.11b   | 2.4GHz | DS       | 可达 11Mb/s |

| 802.11g   | 2.4GHz | OFDM     | 可达 54Mb/s |

| 802.11a   | 5GHz   | DMT/OFDM | 6-54Mb/s  |

在无线局域网的标准制定后，许多研究机构和公司加快了研制无线局域网产品的步伐，各种无线局域网产品大量出现，无线局域网的应用领域也不断扩展。中国四大电信运营商也开始进入这一领域：中国网通推出了“无限伴侣”，中国电信提出了“天翼通”，中国移动和中国联通则大力发展“GPRS+无线局域网”和“CDMA 1X+无线局域网”。

### (2) IEEE 802.11b 标准<sup>[4]</sup>

IEEE 802.11b 标准规定无线局域网应该工作在 2.4000~2.4835GHz 频段(美国、加拿大、除法国和西班牙之外的欧洲国家)或者 2.471~2.497GHz 频段(日本)或者 2.4465~2.4835GHz 频段(法国)或者 2.445~2.475GHz 频段(西班牙)，属于窄带范围。

IEEE 802.11b 无线局域网采用直接序列扩谱技术(DS-SS)，依调制方式的不同，可以提供四种数据传输率供用户选择，如表 1.2 所示。

表 1.2 IEEE 802.11b 规定的数据率和调制方式

Tab. 1.2 IEEE 802.11b data rate and modulation

| 数据率(Mb/s) | 调制方式  |

|-----------|-------|

| 1         | DBPSK |

| 2         | DQPSK |

| 5.5       | CKK   |

| 11        | CKK   |

## 1.3 本论文主要工作

本文讨论了基于 WLAN 802.11b 无线局域网的二次变频零频率接收机指标分配，要求低噪声放大器在低功耗下，达到噪声最小。采用 Chartered 0.18 $\mu$ m CMOS 工艺进行低噪声放大器、低噪声放大器及混频器的融合技术。

基于 WLAN802.11b 接收机射频前端的 CMOS 实现方案，本文采用二次变频的零中频接收机结构，根据 WLAN802.11b 标准规定，推导出射频前端各模块基本指标参数，并以提高集成度，降低功耗，降低成本以及保留适当余量为原则，采用 CMOS 工艺设计低噪声放大器及低噪声混频器模块。

第一章，绪论，主要介绍选题背景以及意义，论文的主要工作及内容。

第二章，介绍了接收机射频前端设计以及射频基础知识。

第三章，根据射频前端设计理论指导，对射频前端关键模块(LNA、mixer)进行噪声与线性度分析。

第四章，综合分析采用二次变频零中频接收机结构的设计，并对第一中频的选择进行了分析，给出了针对 WLAN802.11b 的低噪声放大器的设计方案以及仿真结果。采用

Chartered 0.18 $\mu$ m CMOS 及 JAZZ 0.35 $\mu$ m BICMOS 两种工艺设计了同种匹配结构的单端及差分低噪声放大器，分析了各自的仿真结果，并对 JAZZ 0.18 $\mu$ m BICMOS 设计的差分低噪声放大器版图进行了初步设计。

第五章，将 PCSINM 匹配技术应用于低噪声放大器与混频器的融合设计，即低噪声混频器。

第六章，结束语，总结论文的研究工作与不足之处，提出将来的研究方向。

## 2 射频接收机及工艺概述

射频接收机的主要作用是接受一定频段的信号，从很多信号中选出期望的信号，并放大到解调器所要求的电平值由解调器解调，将射频信号变成可以进行处理的基带信号。整个过程如图 2.1 所示。由于传输路径上的损耗和多径效应，接收机接受的信号微弱并且多变，有用信号周围往往有很多干扰信号，并且强度很大，这样就要求接收机有良好的灵敏度。由于干扰信号可能导致恶化输出信噪比，所以要求接收机有较大的线性动态范围。

图 2.1 信号接收过程

Fig. 2.1 Signal processing

### 2.1 射频接收机结构

射频接收机结构主要有三类：超外差接收机、零中频接收机和低中频接收机。接收机部分完成射频信号的接收、滤波、放大、混频器下变频，然后将信号传送到基带；发射机部分将信号上变频到载频，经过功率放大器放大后由天线发射出去。在超外差接收机中，射频信号先通过第一级混频器变到中频，然后在中频经过带通滤波、增益控制等处理后进行下变频。超外差接收机的主要缺点是要采用大量的片外高品质因子的无源元件，从而使整个接收机的面积、功耗和电路成本都大大增加。同时，超外差接收机还存在镜像频率干扰问题，使有用的射频信号及与本振信号对称的镜像频率信号同时被变换到相同的中频频带内，形成干扰。为了克服超外差接收机所固有的缺点，人们提出了目前备受青睐的零中频接收机结构。零中频接收机使用一个混频器，直接将带内的射频信号变到基带，从而消除了镜像信号的干扰。零中频接收机另一个明显的优点是省去了大量的片外无源元件，从而极大地节省了电路的面积和功耗。但是，零中频接收机存在另外一个严重的问题——直流失调，即在零中频接收机中，由于本振信号和接收端的载波信号的频率相同，会造成本振信号泄漏到接收机的输入端，从而形成本振信号的自混，产生较大的直流失调。零中频接收机可以实现极高的集成度。零中频接收机对通

往基带的信号进行了直接、正交的下变频转换。期望信号将自身作为镜像信号，因此可以实现充分的镜像信号抑制。在理论上，零中频接收机中根本不需要分立的高频带通滤波器，是可以实现完全集成的接收器。低中频接收机将天线频率直接下变频为较低的中频，即在若干100 kHz 的频率范围内。下变频采用正交方式，在现有的技术条件下，混频器之间的不匹配和正交振荡信号的幅度及相位误差使得只靠正交下变频来完成对镜像信号的抑制是不够的，必须加进其它的元件来增强抑制制度。综合以上各种因素，本课题采用零中频接收机结构。其中RF前端主要包括：低噪声放大(LNA)、混频器(mixer)。

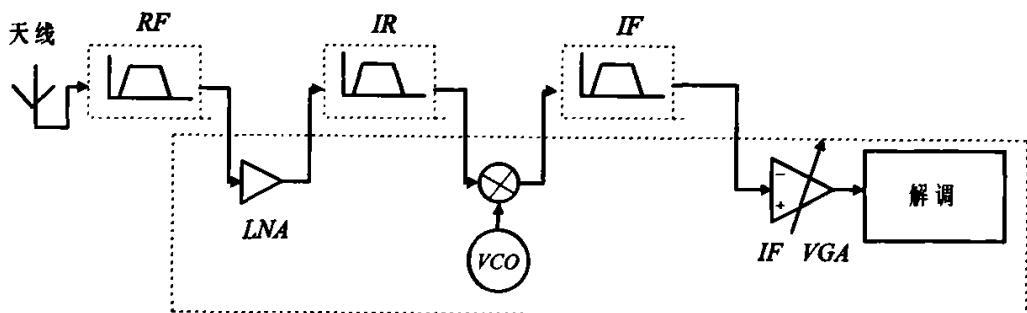

### 2.1.1 超外差接收机

超外差接收机结构方框图(如图 2.2)，此接收机结果具有成熟的理论以及广泛的应用。首先，接收机从天线上接收到的电平一般为-120dBm 左右。要放大到解调器可以工作的电平，一般要放大很多，比如 50dB 左右。采用超外差接收机方案后，将接收机的增益分配到各个模块，在中频和基带上作高增益的放大器更便捷和更稳定，所以我们将更多的放大放在基带。其次，如果在较低的固定中频上进行解调比较容易。

实现超外差式接收机遇到的一个主要问题是镜像抑制问题<sup>[5]</sup>，该问题是由于下变频器引起的，在下变频时除了有用信号被转换到中频外，镜像信号也被转换到中频，从而对有用信号造成干扰。外差式接收机的最大缺点是组合干扰频率点多。这是因为变频器往往并不是一个理想的乘法器，而是一个能完成相乘功能的非线性器件，会形成对有用信号的干扰，通常就是所说的寄生通道干扰。而消除这些干扰的唯一办法就是不让它进入变频器，这就需要在变频器前面加滤波器滤除。

图 2.2 超外差接收机结构

Fig. 2.2 Superheterodyne receiver

总体来说，超外差离不开具有良好选频特性的滤波器。这样的滤波器只能在片外实现，使得超外差接收机不能集成，如图2.2所示，滤波器都是放在片外的电路实现。但是

因为这种结构通过适当的选择中频和滤波器可以获得极好的选择性和灵敏度。所以这种结构认为是最可靠的接收机拓扑结构。

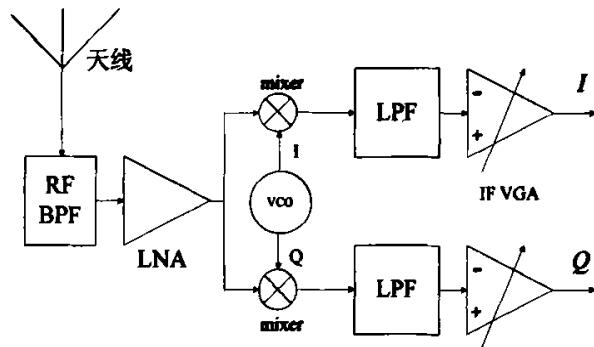

### 2.1.2 零中频接收机

把载频直接变频(Direct Conversion)为基带的方案也称为零中频方案。如图 2.3 所示。除了没有镜像频率干扰外，直接下变频的方案还有以下优点：接收机的射频部分只包含了高频低噪声放大器和混频器，增益不高，易于满足线性动态范围的要求，而且由于没有抑制镜频滤波器，也就不必考虑放大器和它的匹配问题；由于下变频器后面是基带信号，因此不必采用专用的中频滤波器来选择信道，而只须用低通滤波器来选择有用信道，并用基带放大器放大即可，而这些电路都是很容易集成的<sup>[6]</sup>。

图 2.3 零中频接收机结构

Fig. 2.3 Direct-conversion receiver

同时，有很多缺点<sup>[7-10]</sup>：1、本振泄漏：零中频方案的本振频率和信号频率相同，如果变频器的本振端口与射频端口之间的隔离性能不够好，本振信号就很容易从变频器的射频端口输出，再通过高频放大器泄漏到天线，辐射到空间，形成对邻道的干扰。这在外差式接收机中就不容易发生，因为外差式接收机的本振频率和信号频率相差很大，一般本振频率都落在前级滤波器的频带以外。2、直流偏差：直流偏差是零中频方案特有的一种干扰，它是由自混频引起的。如上所述，如果由本振泄漏的本振信号又从天线回到高频放大器，进入下变频器的射频端口，它和本振端口进入的本振信号经混频，差频为零频率，即为直流。同样，进入高频放大器的强干扰信号也会由于变频器的各口隔离性能不好而漏入本振口，反过来它又和射频端口来的强干扰经混频，从而形成直流。这些直流偏差在超外差式接收机中是不可能干扰有用信号的，因为那时中频不等于零。而在零中频方案中，将 RF 信号转变为中频为零的基带信号，这些直流偏差就叠加在基带

信号上，而且这些直流偏差往往比射频前端的噪声还要大，一方面使信噪比变差，而且这些大的直流偏差往往还可能使混频器后的各级放大器饱和，无法放大有用信号。但是，这些零偏差干扰可以通过后面的数字信号处理的方法减弱。也可以将下变频后的基带信号用电容隔直的方法耦合到基带放大器，以此消除直流偏差的干扰，但此法对于在直流附近集中了比较大的能量的基带信号是不合适的，这种方法会增加误码率。因此，减弱直流偏差干扰的有效方法是将要发射的基带信号经过适当的编码并选择合适的调制方式，使得接受并经过下变频率后的基带信号在直流附近能量减少，这时就可以用交流耦合的方法来消除直流偏差而不损失信号能量。

### 2.1.3 低中频接收机

低中频接收机是从零中频接收机发展而来的，它也通过正交下变频来完成镜像信号压缩，但与零中频接收机不同的是，下变频后信号处于一个比较低的中频（一到两倍的信号带宽），如图 2.4 所示。由于镜像信号不再与有用信号互为镜像，它的能量与有用信号相比是不可预知的（在最坏情况下，可能高达 50dB），这样对镜像信号抑制度的要求就非常的严格（在高质量的应用中，要求有 80dB 抑制度）<sup>[11]</sup>。

图 2.4 低中频接收机

Fig. 2.4 Low-IF conversion receiver

低中频接收机有较好的集成度，并克服了零中频接收机中的低频干扰问题，对镜像信号的抑制要求不高的场合。有很多蓝牙接收机都用这个结构。

## 2.2 射频接收机指标及射频集成电路基本概念

### (1) 射频接收机灵敏度

无线通信系统中的噪声包括各种干扰和射频电路元件本身的各种噪声，如 MOS 晶体管所产生的各种噪声。对于接收机的设计来讲，为了提高性能，就必须降低噪声的影

响, 提高接收机的灵敏度。它表征了系统的接收微弱信号的能力。影响接收机灵敏度的只有两方面: 接收机的内部噪声和接收机等效宽带噪声功率, 以及终端解调所需的信噪比要求。接收机的灵敏度公式(2.1)如下:

$$MDS = -174dBm/Hz + NF + 10\log B + SNR_{min} \quad (2.1)$$

上式是在假定天线的绝对温度为 290K, 系统带宽为 B, 解调门限为  $SNR_{min}$  的情况下的推导结果。 $SNR_{min}$  通常是由误码率并结合信号调制解调方式推导出来的。NF 的讨论针对的都是单级系统, 对于由多个子系统级联而组成的系统, 其中各子系统的噪声系数为  $F_n$ , 可获得功率增益为  $G_n$ , 并且各级间相互匹配<sup>[6]</sup>。则整个系统的噪声系数(式 2.2)为:

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_2 G_1} + \dots \quad (2.2)$$

系统前端的低噪声放大器(LNA)的噪声性能对整个系统的噪声性能有着极大的影响。从提高系统灵敏度的角度来讲, 要求其具有尽量低的噪声系数, 尽量高的功率增益。后面各级子系统带来的噪声, 由于前级的功率增益乘积很大, 所以它们的影响可以被减至很小, 甚至可以忽略不计。而且可以看出, 由于接收机第一级为滤波器, 这个模块没有增益, 反而有损耗, 这种无源有耗的滤波器, 对降低系统的噪声系数不利。

### (2) 接收机选择性与线性度

接收机的选择性定义为: 在邻近频率强干扰和信道堵塞的情况下, 接收机选择有用信号的能力。同时接收机还应当具备足够的线性性能去处理可以接受的失真信号。如果接收机在选择性和线性度方面不好, 那么就会产生互调分量而降低信号质量。一般来讲, 噪声确定了最小检测信号, 而失真度确定了接收机可处理的输入信号的最大功率。为了描述这种非线性, 引入了 1dB 压缩点( $P_{1dB}$ )和三阶交调点( $IIP_3$ )两个参数。前者定义为系统的功率增益下降 1dB 时输入信号的功率; 后者定义为系统的三阶非线性输出与一阶线性输出达到相等时的输入或输出功率, 分别被称为输入三阶交调点( $IIP_3$ )和输出三阶交调点( $OIP_3$ )。系统的三阶交调指标用下式(2.3)来表示。

$$\frac{1}{IIP_3} \approx \frac{1}{IIP_{31}} + \frac{G_1}{IIP_{32}} + \frac{G_1 G_2}{IIP_{33}} + \dots \quad (2.3)$$

### (3) 接收机动态范围

动态范围定义了接收机在检测噪声基值上的弱信号和处理无失真的最大信号的能力。用接收机输入端的最大信号和最小信号的比定义接收机的动态范围。无寄生动态范

围 SFDR (Spurious FreeDynamic Range) 和阻塞动态范围 BDR (Blocking Dynamic Range) 是特别重要的。SFDR 是以最大输入电平 (三阶互调分量低于噪声基值) 和最小可辨别信号  $P_{min}$  之间的比为基础的。SFDR 的表达式 (2.4) 如下：

$$SFDR = \frac{2}{3} [IIP_3 - P_{min}] - \frac{E_b}{N_0} \quad (2.4)$$

阻塞动态范围 BDR 定义为上限信号  $P_{dB}$  与最小可辨别信号  $P_{min}$  的差。计算前端接收链的最大增益时，需要考虑最大可能的带内阻塞。

#### (4) 接收机中频抑制与镜像抑制

中频抑制是指对中频干扰和噪声的削弱和抑制。可以通过将混频器设计成双平衡或环路，电路尽量对称，这样使中频干扰尽量和中频端口隔离，一般的混频器均给出了 RF 和 IF 端口的隔离度，这个隔离度在一个程度上反映了接收机的中频抑制能力，此外通过选择合适的频率的中频可以大幅度的提高中频抑制能力。频率  $2f_{LO} - f_{RF}$  称为镜像频率，在本振功率较大的情况下，必须考虑镜频对中频的影响。抑制镜像干扰的有效方法有：采用高中频使得镜频干扰尽量远离有用信号，然后采用二次变频得到所规定的中频。

#### (5) 增益压缩

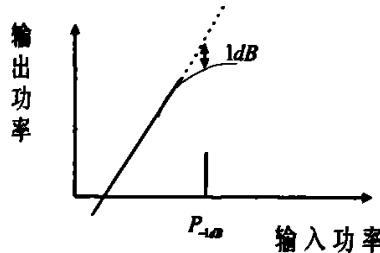

当输入信号很小时，输入信号功率与输出信号功率成线性关系。但是随着信号的变大，输出增益下降，如图 2.5 所示。也就是说对于处理信号有一个上限。这个指标反映了最大可以处理的信号。

图 2.5 1dB 压缩点

Fig. 2.5 1dB compression point

#### (6) 三阶交调点

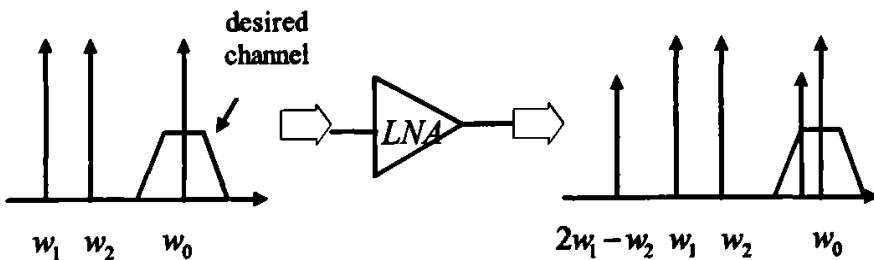

在射频系统中，三阶交调点 IIP3 是一个衡量器件线性度和失真性能的重要指标。当多个邻道信号传输时，邻道信号会由于电路的非线性，在输出端产生交调互调的干扰项。

三阶交调就是非线性电路输出端的三阶交调信号功率与输出信号功率相同时的输入信号功率点，即三阶交调点。图 2.6 说明了三阶互调信号的干扰信号，经过非线性电路，落于频带内而造成干扰现象<sup>[6]</sup>。

图 2.6 等幅双音信号及三阶分量关系图

Fig. 2.6 Dual-tone with the same amplitude signal and the 3<sup>rd</sup> order IM

#### (7) 噪声系数

信噪比(SNR)是同一个端口的功率  $P_{in}$  与噪声功率  $P_n$  之比。噪声系数与信噪比的关系是：噪声系数等于输入输出的信噪比之比，用 dB 来表示。其中，需要说明的是，混频器中分为单边带噪声与双边带噪声<sup>[4]</sup>。这是由于下变频后产生的中频信号的频率仅与射频信号、本振信号频率之差的幅度有关，因此射频信号和它的镜像信号都会被变换到相同的中频频带上。如果镜像信号频带位置不存在有用信号，这时测量出的噪声系数称为单边带噪声系数；如果有用信号同时出现在射频信号频带和镜像信号频带上，这时测量出的噪声系数称为双边带噪声系数。在大多数接收机系统中(如超外差、低中频接收机等)，镜像信号频带位置是不存在有用信号的，因此单边带噪声系数反应了混频器真实的噪声性能；而在零中频接收机中，有用信号同时出现在射频信号频带和镜像信号频带上，因此双边带噪声系数反应了混频器真实的噪声性能。由于在双边带噪声系数测量中，射频信号频带和镜像信号频带都存在有用信号，而在单边带噪声系数测量中，仅射频信号频带存在有用信号，因此前者的信号功率是后者信号功率的两倍。对同一个频率来说，前者的输入信噪比比后者高 3dB，因此通常来说，单边带噪声系数比双边带噪声系数大 3dB。

### 2.3 射频集成电路工艺

在射频以及模拟电路中，常常在 CMOS, GaAs, SiGe, BICMOS 等工艺中选择。具体方案需要在产品要求上进行折衷。

硅作为半导体材料应用已经有很长的历史了，随着技术应用改进，其应用程度已经非常成熟。随着半导体工艺以摩尔定律飞速发展，MOS 管沟道尺寸越来越小，特征频率越来越高，功耗也大大下降，成为 RFIC 一个非常好的技术发展平台<sup>[4]</sup>。对于数字电路，主流工艺是 CMOS 工艺，而对于模拟设计师来讲，常常在 CMOS, GaAs, SiGe, BiCMOS 等选择。具体方案需要在产品要求上进行折衷。

GaAs MESFET和异质结器件被认为是低产品率，高功耗和高价格，但它们仍在RF市场占有重要地位，尤其是在功放和前端开关中。GaAs 器件具有优越的电子迁移率和饱和迁移速度，所以GaAs的工作速度高，这使得它在目前的RF领域占据举足轻重的地位。然而，随着CMOS 技术的发展，CMOS管进入到深亚微米领域时代，Si工艺的特征频率可以和GaAs 相比拟。不过，基于Si的器件工作电压较高一些。GaAs由于本身具有的更高的低场迁移率，而这一点对器件的噪声指数至关重要，所以GaAs 仍将保持着一些很重要的性能优势。连接器件的欧姆电阻在影响噪声指数方面起重要作用。典型的 GaAs MESFET或PHEMT由金属栅组成，和基于硅栅的MOS 器件相比，它大大减小了串联栅电阻。在许多情形下，噪声指数中零点几分贝的改进对无线通信是至关重要的，在RF前端中，除开关和前端功放主要由GaAs实现之外，其余基本上由高级BJT工艺实现，在目前，高级BJT工艺是RF前端的主流工艺。因为双极型器件的截止频率 $f_T$  很高，工作电流小，所以功耗也小，此外，双极型器件的噪声也很小，这一点尤其是用在LO电路对噪声要求很严格的应用中。GaAs是一种性能优越的高频器件材料，但是工艺与传统的工艺不兼容，其集成规模很难与发展成熟的集成工艺相比，而且电路的制造成本非常昂贵。 SiGe BiCMOS技术凭借其频率特性好，噪声系数低，集成度高，成本低以及与传统工艺相兼容的优势，展现了其在无线通信领域的发展潜力。SiGe技术具有优于Si BiCOMS技术和GaAs技术的性能，可满足无线通信等现代无线电通信系统的要求。已在现代无线通信系统芯片设计制造中获得广泛应用，成为领域的主流技术。

SiGe技术在加入适量锗获得新的半导体性质的同时，做到硅所具有的高产量和低成本。可见，SiGe 具有无线通信所需要的各种优点：低功耗和低成本，可以传送和接受高频信号，同时也延长了移动设备的电池寿命。目前，这种技术引起了越来越多公司的注意。

### 3 低噪声放大器及混频器理论分析

#### 3.1 低噪声放大器拓扑结构

一般的 CMOS 低噪声放大器有四种结构<sup>[4]</sup>，这些结构都可以提供适合的功率和增益，但它们在噪声系数，输入匹配以及应用方面有所不同。

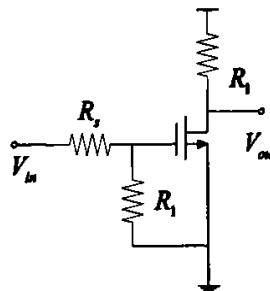

##### (1) 电阻匹配共源结构

如图 3.1 所示，当要把低噪声放大器在很大的宽带内稳定在  $50\Omega$  时，可以采用此结构。由于使用电阻作为输入端终端，将使得低噪声放大器的噪声指数很高，该电阻噪声又会经过放大器放大，增加了总的输出噪声。这种结构电路的噪声指数很高，更不适合设计低功耗 LNA。

图 3.1 电阻匹配共源结构

Fig. 3.1 Common source LNA with resistor termination

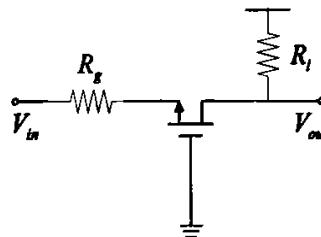

##### (2) 跨导匹配共栅结构

如图 3.2 所示，MOS 管底源级作为输入端，所以  $Z_{in} \approx 1/g_m$ ，所以如果输入阻抗要匹配到  $50\Omega$ ，就需要有固定的跨导，通过选择偏置和尺寸即可。

图 3.2 跨导共栅结构

Fig. 3.2 Common gate with transconductance match

跨导匹配共栅结构在输入匹配上是很容易实现的，但是它的噪声指数还不低，目前用的较少。

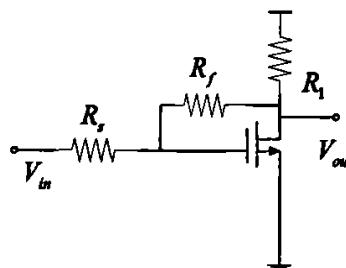

### (3) 并联-串联反馈结构

如图 3.3 所示，此结构采用旁路电阻反馈作为输入与输出端的电阻匹配。这样的电路也可以提供  $50\Omega$  匹配，输入阻抗如式 (3.1) 所示。

图 3.3 并联-串联反馈结构

Fig. 3.3 Parallel-series feedback structure

$$Z_{in} = R_f / (1 + A) \quad (3.1)$$

其中， $A$  为电路的增益。相对与其他结构的放大器，在相同噪声指数性能下，这种形式的放大器消耗更大的功率，因为它是宽带结构，一般使用在宽带的光纤通讯中。

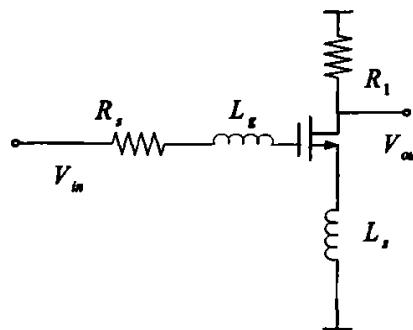

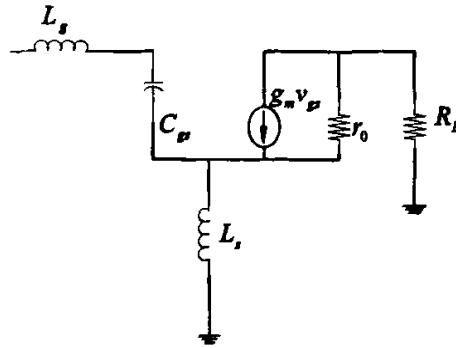

### (4) 电感共源极反馈匹配电路

如图 3.4 所示，这种结构通过源级负反馈  $L_s$ ，使得输入电阻为  $50\Omega$ ，这也是最常用的一种窄带低噪声放大器结构<sup>[4]</sup>。由于本文是窄带信号，所以采用这种方式，即可以达到功率匹配，又可以不增加多余的噪声<sup>[12]</sup>。

图 3.4 电感共源极结构

Fig. 3.4 Common source LNA with inductive degeneration

由于需要匹配到  $50\Omega$ ，采用电阻匹配共源结构以及串联-并联匹配结构都由于噪声太大，所以对比电感共源极反馈结构和栅极结构，如表 3.1 所示。

表 3.1 共源与共栅结构对比

Tab. 3.1 Comparison of commen source and commen gate

| 参数    | CSLNA | CGLNA |

|-------|-------|-------|

| 噪声因子  | -     | +     |

| 有效跨导  | +     | -     |

| 匹配稳定性 | -     | +     |

## 3.2 低噪声放大器的噪声源

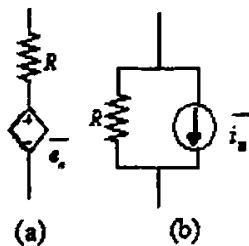

### 3.2.1 电阻的热噪声

电阻的热噪声可以等效为图 3.5 中所示的两个电路。图 3.5(a)是用电压源的形式，其均方值为：

$$\overline{e_n^2} = 4kT\Delta f \quad (3.2)$$

而图 3.5(b)是电流源的形式，其均方值为：

$$\overline{i_n^2} = \frac{4kT\Delta f}{R} \quad (3.3)$$

图 3.5 电阻噪声模型

Fig. 3.5 Resistor nosie model

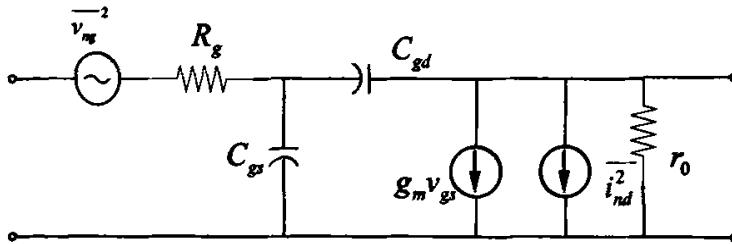

### 3.2.2 MOS 管的噪声分析

一般 MOS 管包括以下三中噪声<sup>[13]</sup>：漏极电流热噪声、栅感应噪声、闪烁噪声(1/f)。如图 3.6 所示。

#### (1) 漏极电流热噪声

通过详细的理论分析, 可以推导出漏极电流热噪声均方值, 如(3.4)式所示:

$$\overline{i_{nd}^2} = 4KT\gamma g_{d0}\Delta f \quad (3.4)$$

其中,  $g_{d0}$  是  $V_{DS}=0$  时的漏源电导。 $\gamma$  值随着管子工作情况不同而不同, 当  $V_{DS}=0$  时,  $\gamma$  为 1; 当长沟道饱和区时,  $\gamma$  为  $2/3$ ; 当短沟道饱和区时,  $\gamma$  为  $4/3 \sim 2$  之间。当  $V_{DS}$  很低时, 管子就像是一个电阻,  $\gamma$  为 1, 并且短沟道的噪声因子  $\gamma$  是长沟道的两倍多。主要因为在短沟道器件中, 高电场引起额外噪声。

解决方法:

- ① 尽量减小  $V_{DS}$ 。但是当它降低到  $V_{DSat}$  时候要注意线性度和增益。

- ② 在短沟道中, PMOS 管的噪声要小于 NMOS。

- ③  $r$  数值在偏置不同的情况下是变化的, 所以最好针对工艺设计来仿真  $r$  的数值。

图 3.6 MOSFET 噪声模型

Fig. 3.6 Noise model of MOSFET

## (2) 栅感应噪声

栅级感应噪声与漏级噪声有关, 所以不可以仅仅把栅级噪声加到输出级。栅级噪声不是白噪声。但是可以将栅级噪声等效为一个放大器的频率响应均匀的功率频谱。尽管这一噪声在低频中可以忽略, 但是射频中也应当引起重视。可以用式(3.5)表示。

$$\overline{i_{sg}^2} = 4KT\delta g_s \Delta f \quad (3.5)$$

其中, 参数  $g_s$  如式(3.6)所示:

$$g_s = \frac{w^2 C_g^2}{5g_{d0}} \quad (3.6)$$

## (3) 闪烁噪声(1/f)

MOS 的闪烁噪声大于双极性的，MOS 中的闪烁噪声如式(3.7)所示。

$$\overline{i_n^2} = \frac{K}{f} \frac{g_m^2}{WLC_{ox}^2} \Delta f \quad (3.7)$$

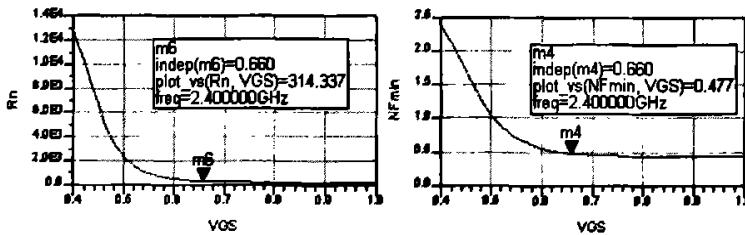

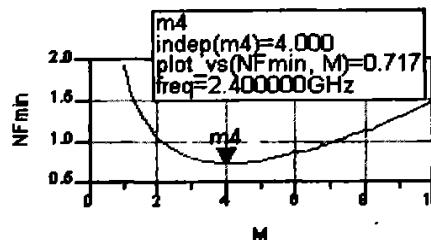

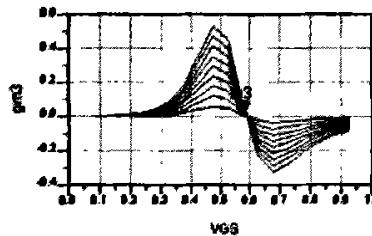

另外，在实际中，设计 MOS 管子的时候，栅指数对噪声也有影响，关于栅指数的选择，可以使得噪声系数改善。但是这种并联，也是有一个最优值的，并不是并联越多越好。如图 3.7 及 3.8 所示，在设计的过程中，要利用他们对噪声指数的影响来对电路进行设计。

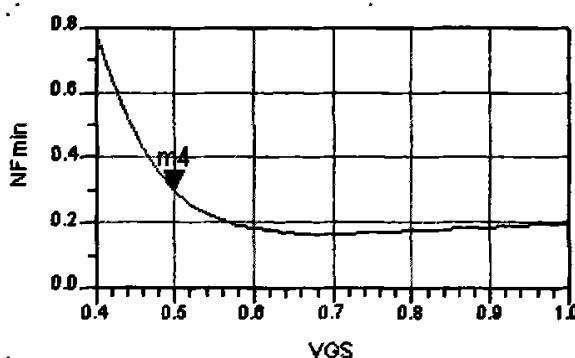

图 3.7 噪声指数与偏置关系 ( $M=1$ )

Fig. 3.7 Relation of noise parameters and bias ( $M=1$ )

图 3.8 噪声指数与偏置关系 ( $M=3$ )

Fig. 3.8 Relation of noise parameters and bias ( $M=3$ )

总之，目前绝大多数晶圆代工厂所提供的参数都是基于 BSIM3 模型，BSIM3 在模拟 MOSFET 噪声时最根本的问题在于仅仅考虑了漏极电流噪声，忽略了感应栅极噪声<sup>[14]</sup>，这样使得该模型应用范围限于低频电路，并且漏极电流噪声也必须进行修正，才可用于亚微米 MOSFET，因此，利用 ADS 等仿真工具无法对短沟道器件的高频噪声进行估计。当信号频率  $w$  大于  $w_s/5$ ，这个模型就无法描述 MOSFET 的高频行为，即非准静态效应 (NQS)<sup>[14]</sup>。

当沟道处于饱和状态, 即在沟道中某一个点处载流子速率饱和, 漏极电压变化对载流子数目与速率的影响已经很小, 也就是,  $C_{gd}$  的电容值为零, 因此, 对栅极感应噪声有贡献的只是沟道源端的电势波动。在相同频率下, 沟道长度越长, 非准静态效应越显著,  $R_{gs}$  也越大。所以在设计 LNA 的时, 模型的应用很重要, 这样对实际的版图设计有直接的好处。由于 BSIM3 不考虑栅级噪声, 所以我们采用的沟道尽量小, 这样也可以增加  $w_t$ , 使得 NQS 很小。

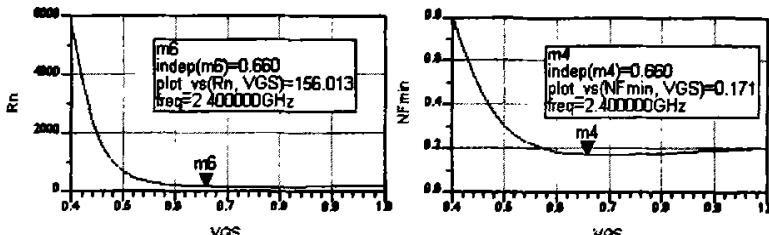

### 3.2.3 共源极电感负反馈的噪声分析

由 3.1 节分析可知, 源极电感负反馈由于其特有的优点, 本文将采用这种共源极结构并对此结构的噪声进行分析。图 3.9 是噪声等效模型。

图 3.9 源极负反馈噪声模型

Fig. 3.9 Noise model of common source with degeneration

根据二端口网络<sup>[4]</sup>计算噪声的方法, 得到噪声系数为:

$$F = 1 + \frac{R_g}{R_s} + \frac{R_i}{R_s} + \gamma g_{sd} R_s \left( \frac{w_0}{w_T} \right)^2 \quad (3.8)$$

其中,  $R_i$  是电感寄生电阻,  $R_g$  是 MOSFET 管栅极等效电阻,  $R_s$  是输入阻抗。

忽略 MOSFET 的密勒电容  $C_{gd}$ , 可以得到放大器的输入阻抗为:

$$Z_{in} = s(L_s + L_i) + \frac{1}{sC_g} + \frac{g_m}{C_g} L_s + R_s \quad (3.9)$$

## 3.3 低噪声放大器线性度分析

### 3.3.1 MOS 管的线性度分析

小信号输入时, 一个无记忆的、弱非线性系统的传输特性可以在其工作点附近用幂级数展开(忽略三阶以上的项), 饱和区工作的 CMOS 放大器通常增益压缩特性, 即

$\alpha_3 < 0$ ,  $\alpha_i$  代表  $i$  阶跨导, 随着信号幅度增加, 增益下降。当增益下降到比线性增益小 1dB 时, 输入信号的幅度为<sup>[15]</sup>由公式(3.10)、(3.11)给出:

$$A_{1dB} = \sqrt{\frac{4}{3}(1-10^{-1/20})} \left| \frac{\alpha_1}{\alpha_3} \right| \quad (3.10)$$

$$A_{IP3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \quad (3.11)$$

从式(3.10)和式(3.11)可以看出, 线性项的相对大小, 如果将 CMOS 射频 LNA 看作一个无记忆的系统, 可以运用上述幂级数展开的方法来分析<sup>[16]</sup>。但是, 不可能是无记忆的电路, 所以用 Volterra 幂级数方法。然而, 在定性分析线性度时, 仍然可以用幂级数的方法。

$$I_{ds} \cong f(V_{sd}) + f'(V_{sd})v_{gs} + \frac{1}{2}f''(V_{sd})v_{gs}^2 + \frac{1}{6}f'''(V_{sd})v_{gs}^3 = I_{DS} + g_1v_{gs} + g_2v_{gs}^2 + g_3v_{gs}^3 \quad (3.12)$$

单管的线性度的计算定性分析可以用幂级数来分析<sup>[16]</sup>, 得出公式(3.13):

$$P_{IP3} = \frac{8}{3} \frac{v_{sat}L}{u_1 R_s} V_{DSAT} \left(1 + \frac{u_1 V_{DSAT}}{2v_{sat}L}\right)^2 \quad (3.13)$$

对管子的了解, 可以很好的设计电路。总体来讲, 管子的设计先要进行初步的理论计算。然后再在 ADS 上仿真, 但是仿真出来的东西, 由于采用的器件模型的缺点, 以至于有些很有影响的参数没有考虑, 使得与实际的工艺制作有差别。这样的理论可以与版图设计相互联系, 比如, 在 BSIM3 中没有考虑栅级噪声电阻, 那么在设计中可以使得  $V_{sd}$  大些来降低栅级电阻的大小。在模型中也没有考虑栅级寄生电阻的噪声, 所以在版图设计的时候, 需要考虑使用插指栅极以及并联 MOS 管数目。所以在确定栅宽后, 找出 figure 数目  $W$  和并联管子数目  $M$  即可。

另外指出, 由于 PMOS 性能差以及小的电流驱动能力, PMOS 管一般在核心 RF 电路中并不采用。然而, PMOS 的小信号特性是很好的。所以, NMOS 和 PMOS 完全应用于 RF 核心电路, 而没有太大的性能减退。实际上, PMOS 已经在 RF 核心电路上应用很多, 例如: PMOS 对被用来产生负阻抗用于 VCO, 有源负载代替面积巨大的电感, 模拟运算放大器等等。

由于 CMOS 弱反型区的工作使得  $g_m/I$  的比例不如三极管好, 随着技术的发展 CMOS 与 BJT 之间的这种差距也在渐渐缩小, 而且 CMOS 的 V-I 曲线, CMOS 的三阶失真主要是由于迁移率的下降, CMOS 的 IIP3 是  $V_{od}$  的函数, 主要 CMOS 工作在强反型区, 那么 IIP3 一定比 BJT 高。

### 3.3.2 Cascode 电路的线性度分析

对于 MOSFET 来讲, 考虑噪声与功耗的要求 ( $V_{dsat}$  不超过 0.2V), cascode 跨导器的线性度在没有匹配网络的情况下, 一般不会超过 +9dBm, 而带有匹配网络的 cascode 跨导器的线性度更低, 大约不超过 +1.5dBm。分析表明带有匹配网络的 cascode 线性度等于未带匹配网络的线性度的  $Q_s^2$  分之一<sup>[17]</sup>, 这是 MOS 工艺带来的基本限制之一。

文献<sup>[17]</sup>研究关于输入管  $Q_s$  值与线性度的关系: 通过  $Q_s$  每增加一倍, 直流功耗下降一半, 但是归一化三阶交截点输入功率和输出功率也下降, 也就是说, 为了获得高的线性度, 不可避免要付出直流功耗的代价, 降低 LNA 输入回路的  $Q_s$  值。为了获得高线性度, 需要提高栅源偏置电压  $V_{od}$  和降低  $Q_s$ 。在低噪声系数意义上最佳的偏置点, 在线性度的意义上却是功耗效率最低的偏置点。可见, 为了获得高线性度, 需要提高栅源偏置电压  $V_{od}$  和降低  $Q_s$ 。

所以要采用电路结构的改进, 才可以使得电路线性度提高。在很多高端通信系统中, 例如 W-CDMA, IEEE 802.11b, DVB-T 等, 由于大多采用了 OFDM 的调制方式, 往往在要求低噪声的同时, 也对线性度有很高的要求<sup>[18-19]</sup>, 因此, 这时不能采用调低增益的方式来提高电路的线性度。

总之, 在电路设计完成后进行电路的仿真, 对于设计者来讲, 最好预先计算 IIP3 与 MOSFET 的偏置电压、尺寸之间的关系, 可以大大减少设计的反复次数。为此本文利用下式<sup>[19]</sup>, 对 IIP3 进行计算:

$$IIP3_{LNA} = 10 \log \left[ \frac{4 V_{od} (1 + \theta V_{od})^2 (2 + \theta V_{od})}{3 \theta} \right] + 20 \log [w_0 C_s (R_{eq} + R_{in}) \sqrt{\frac{50}{R_{eq}}}] - 10 \quad (3.14)$$

$\theta$  是一个沟道调制量, 取 1.2。线性度越好, 抗干扰越强。此外, cascode 结构的负反馈  $L_s$  的值越大, 对线性度越有利。但是这样使得增益下降, 噪声增大, 同样要求栅长  $W$  增大, 功耗增加, 所以线性度、增益以及功耗之间存在矛盾。

### 3.3.3 线性度改善方法

一阶近似的情况下, MOSFET 可以看成是输入电压到输出电流的跨导器, 其传输特性如式(3.15)所示。

$$I_{ds} \approx f(V_{od}) + f'(V_{od})v_{gs} + \frac{1}{2}f''(V_{od})v_{gs}^2 + \frac{1}{6}f'''(V_{od})v_{gs}^3 \\ = I_{ds} + g_1v_{gs} + g_2v_{gs}^2 + g_3v_{gs}^3 \quad (3.15)$$

(1)  $g_i(V_{gs}) = \frac{1}{i!} \frac{\partial^i I_d}{\partial V_{gs}^i}$ ,  $g_i$  一般取决于  $V_{gs}$  和  $V_{ds}$ , 通俗意义上的  $i$  阶跨导。FET 在饱和区可以忽略  $V_{ds}$  的影响。

(2) 在射频电路中常常用  $P_{-1dB}$  和  $HP_3$  来表示线性度的大小, 公式为 (3.16) 所示。

$$A_{dB} = \sqrt{\frac{4}{3}(1-10^{-1/20})} \left| \frac{g_1}{g_3} \right| \quad (3.16)$$

基于以上的线性度原理, 可见, 三阶交截点是由一阶跨导和三阶跨导共同决定的, 然而这两个指标都是由固定的偏置决定的, 即相互的关系固定, 所以一般采用外围电路进行改善。

在改善  $g_3$  的过程中有很多的方法: 一种前馈失真的抵消<sup>[20]</sup>, 这种技术依赖于准确的定标(包括主输入信号, 辅助增益级以及他们的转移函数)。利用 MGTR 和其它的电路设计一种线性度高的电路<sup>[21]</sup>, 主晶体管的负值峰值  $g_{m3}$  可由辅晶体管的正值  $g_3$  消除, 但是电路结构复杂。现在比较常用的是导数叠加法<sup>[22]</sup>, 其主要技术点: 当  $g_3$  (取决于  $V_{gs}$ ) 从弱反型区到反型区再到强反型区时, 由正变成负。导数叠加法可以使得线性度很大, 缺点在于对偏置的要求很高, 而且对与输入匹配的 Q 值很难控制, 所以噪声影响很大。本文将采用的是 PMOS 折叠放大器<sup>[23]</sup>, 采用了一个 PMOS 与 NMOS 结合的方式, 通过 NMOS 和 PMOS 三阶跨导的抵消可以使的线性度有很大的改善, 并且 NMOS 可以轻松的控制 Q 值使得噪声做到最小化(如图 3.10)。

$$i_{dc} = g_{1C}v_{gsB} + g_{2C}v_{gsB}^2 + g_{3C}v_{gsB}^3 \quad (3.17)$$

$$i_{dd} = g_{1A}v_{gsA} + g_{2A}v_{gsA}^2 + g_{3A}v_{gsA}^3 \quad (3.18)$$

$$v_{sgB} = c_1v_{gsA} + c_2v_{gsA}^2 + c_3v_{gsA}^3 \quad (3.19)$$

再带入输出总电流:

$$i_{dB} = i_{sA} + i_{sC} \\ \approx (g_{sA} + c_1g_{sC})v_{gsA} + (g_{sA} + c_1^2g_{sC})v_{gsA}^2 + (g_{sA} + c_1^3g_{sC})v_{gsA}^3 \quad (3.20)$$

由于 NMOS 和 PMOS 在饱和区三阶跨导都是负值, 从图 3.10 可以看出  $c_l$  也是负值, 那么这样总的输出三阶跨导可以调节到很小, 从而使得线性度有很大提高。

图 3.10 IMD 抵消方法(折叠式 PMOS 的共源共栅放大器)

Fig. 3.10 IMD sinking method (Cascode amplifier with the folded cascode PMOS IMD sinker)

### 3.4 混频器各参数对指标的影响

#### (1) 转换增益

对于双平衡混频器的增益:  $G_v = c \times g_m \times R_L$ , 如果开关中的器件是完全匹配的, 单平衡混频器的转换增益, 当开关级的偏置电流增加时, 开关对的转换增益下降; 本振信号的幅度增加时, 开关对转换增益增加, 并逐渐趋于 2/3.1415。

#### (2) 噪声因子

这种结果的电路包括很多因素的噪声, 驱动级的白噪声、开关级的热噪、本振端的噪声、1/f 噪声、高频噪声。首先, 驱动级的白噪声<sup>[24-25]</sup>, 如果单平衡混频器以及双平衡混频器, 有相同的驱动级晶体管的偏置与尺寸, 那么双平衡混频器的驱动级引入的噪声是单平衡混频器的两倍。第二, 开关级的热噪<sup>[26]</sup>: 忽略电容效应和输出电阻, 当开关对中的一个晶体管截止, 混频器的输出电流仅由尾电流  $I$  决定, 因此开关不产生噪声, 但是当开关都导通的时候, 开关产生噪声。即当  $V_{LO} = 0$  的时候, 开关引入的噪声最大。而且本振的幅度越大, 使得两个晶体管导通的时间越短, 这样开关引入的噪声就越小。开关级在混频器中引入的热噪声与电流成正比, 与  $V_{LO} = 0$  成反比。开关对在输出端所引入的热噪声是单平衡的两倍。第三, 本振端的噪声: 本振的噪声基底对混频器的噪声系数具有很大影响, 但匹配的双平衡混频器对本振信号有抑制能力, 所以本振信号的噪声基底对双平衡混频器没有影响。

其中，偏置电流越大，噪声越大，本振信号过零处斜率越大，噪声越小。如果把开关管看成理想开关。那么双平衡混频器的噪声与驱动级跨导成反比。第一，驱动级噪声的优化：可以低噪声放大器一样来优化。其次，开关对的噪声优化：减小偏置电流，会减少开关对的热噪声和  $1/f$  噪声，同时使得转换增益增加。增加本振幅度，会减少开关对的热噪声和  $1/f$  噪声，但会增加驱动级的热噪声贡献，同时会使得混频器的转换增益增加。第四， $1/f$  噪声优化：当驱动级理想，并不泄漏到输出，而是混频到本振信号的奇次谐波，在低频处不产生噪声，而当混频器开关不匹配时，驱动级的  $1/f$  漏到输出，产生低频噪声。而开关级  $1/f$  仅仅存在于偶次谐波处。最后，高频噪声优化：只有当开关对不是理想的情况下，开关对中的 MOS 存在同时导通，本振的输入端噪声才会对混频器输出端产生噪声贡献。但当到了高频，即使是理想开关，本振输入噪声也会对混频器产生噪声贡献，非直接噪声机制来实现。最后，节点寄生电容(特别是开关对共源节点的寄生电容)对混频器性能具有很大的影响。它将在混频器本振信号的偶次谐波处(包括直流)产生噪声。共源节点的波动与本振信号的幅度有关，当本振信号的幅度波动增大，对节点寄生电容充放电的瞬时电流也会很大，从而在混频器输出端产生很多强度很高的毛刺。并且，当  $V_{LO}$  接近 0 时，开关对中的晶体管同时导通，但由于共源节点电压波动，开关对中的晶体管可能离开饱和区，影响性能。可见，本振信号的幅度不是越大越好。

### (3) 线性度

首先，驱动级的线性度限制了混频器的最大线性度性能。混频器的线性度也受到开关级的影响，存在一个最优的本振信号幅度，可以最大程度的减小开关对引入的三阶交调项。为了提高混频器的线性度，就要提高驱动级的线性度；为了减小开关引入的三阶交调积最小，应对本振信号幅度和开关对尺寸进行优化，选择使三阶交调积最小的本振信号幅度和开关对尺寸。其次，在零中频中，二阶交调积很重要，这是因为驱动级的二阶非线性和开关对中晶体管的不匹配，以及开关对的非线性等都使得二阶交调干扰增加。

线性度有很多改善方法，由于混频器的线性度主要与驱动级和开关对有关，因此改善混频器的线性度应从提高驱动级的线性度和提高开关对的线性度两方面着手进行考虑。

## 3.5 低噪声放大器的匹配

在典型的接收机设计中，低噪声放大器是关键模块之一。低噪声放大器的设计主要在噪声、增益、线性度、阻抗匹配以及功耗之间进行折中，通常，LNA 的主要目的是在特定的功耗下，达到噪声与阻抗的同时匹配。LNA 的匹配方法很多：传统的噪声匹

配 CNM 技术<sup>[27]</sup>，噪声阻抗同时匹配 SINM 技术<sup>[28]</sup>，特定功耗噪声优化技术 PCNO 技术<sup>[4]</sup>，特定功耗噪声阻抗同时匹配 PCSNIMD 技术<sup>[29]</sup>。

### 3.5.1 CNM 技术

CNM 技术的思想就是对于一个放大器存在一个最优源阻抗  $Z_{opt}$  使放大器的噪声系数最小。所以通过在信号源和放大器间加上一个匹配电路，使得从放大器端看到的信号源阻抗等于  $Z_{opt}$ 。电路结构如图所示。用这种技术设计 LNA 可以获得的最小的噪声系数等于晶体管的  $F_{min}$ ，而这是由工艺和管子尺寸决定的。然而，由于  $Z_{opt}$  和  $Z_{in}^*$  固有的失配（这里  $Z_{in}^*$  是放大器输入阻抗的复共轭），所以在获得最优的噪声性能的时候可能经受一个显著的输入增益失配。所以，CNM 技术本身要求在增益和噪声性能上进行折中。

### 3.5.2 SINM 技术

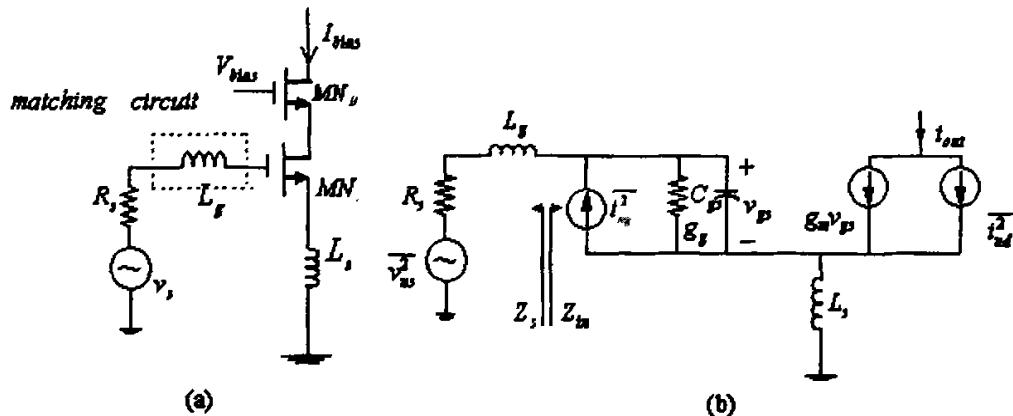

这种技术使用串联负反馈技术来改变  $Z_{opt}$  的值到期望点，电路简图以及小信号图，如图 3.11(a)、(b) 所示。串联反馈被用来 SINM 并且噪声系数不会恶化。用感性源负反馈作为串联反馈已被运用在共源或共源共栅拓扑结构中，尤其在窄带应用中用得更加广泛<sup>[30-32]</sup>。

图 3.11 SINM 方法 (a) SINM 电路图 (b) SINM 小信号等效图

Fig. 3.11 SINM method (a) Simplified schematic of SINM (b) Small signal circuit of SINM

$$Z_{opt} = Z_{opt}^* - sL_1 \quad (3.21)$$

$$Z_{opt} = \operatorname{Re}[Z_{opt}^o] - m \frac{1}{sC_{\sigma}} - sL_s \quad (3.22)$$

这种技术利用在输入晶体管的源极加上一个串联的电感，从而获得了实数的输入阻抗，从而实现输入阻抗匹配，而理想的电感是没有噪声的，所以就可以实现在不影响放大器的噪声性能的情况下实现阻抗匹配。满足了二端口网络理论，也满足了输入共轭匹配。输入失配而影响增益在一定范围可以忽略，但是最优输入阻抗的失配直接影响 NF，这是不可以忽略的。

值得注意的是，对于给定的  $L_s$ ，最优化噪声阻抗的虚部将自动被近似为输入阻抗的虚部的相反数， $\operatorname{Im}[Z_{in}] \approx -\operatorname{Im}[Z_S]$ 。以上所描述的 SNIM 设计方法论能够保证在输入匹配近乎完美的情况下使 LNA 的 NF 等于共源晶体管的  $NF_{min}$ 。这种方法的缺点是在晶体管很小和低频应用中， $\operatorname{Re}[Z_{opt}]$  将变大，这时为了使  $\operatorname{Re}[Z_{in}] = \operatorname{Re}[Z_{opt}]$ ，就需要大的  $L_s$ ，大的  $L_s$  将使  $NF_{min}$  显著增大，从而使可获得的噪声系数增大，而且这种方法没有功耗限制，不符合特定低功耗下的设计要求。

$$F = F_{min} + \frac{R_s}{G_s} [(G_s - G_{opt})^2 + (B_s - B_{opt})^2] \quad (3.23)$$

$$Y_{opt}^o = \alpha w C_{\sigma} \sqrt{\frac{\delta}{5\gamma} (1 - |c|^2)} - s C_{\sigma} (1 + \alpha |c|) \sqrt{\frac{\delta}{5\gamma}} \quad (3.24)$$

$$F_{min} = 1 + \frac{2}{\sqrt{5}} \frac{w}{w_T} \sqrt{\gamma \delta (1 - |c|^2)} \quad (3.25)$$

可见，噪声和增益匹配很难同时达到。噪声与增益的矛盾仍未解决。这就是 CNM 技术应用到 LNA 的缺点。

### 3.5.3 特定功耗噪声优化技术

由文献[4]推导的噪声二端口理论可知，假设  $B_s \approx B_{opt}$ ，通过将噪声因子中的因素转化成与功耗有关的因子，首先将噪声因子变成与输入 Q 值有关的式子，然后在将功耗转换为与 Q 有关，最后将两个相关的等式联立，求导数即可。考虑 MOSFET 的短沟道效应，漏极电流可以表示为式(3.26)，功耗表示为式(3.27)，考虑到饱和区时， $C_{\sigma} = \frac{2}{3} WLC_{\alpha}$ ，将与栅宽相关的一项  $Q_L$  改为式(3.28)，其中  $P_0 = \frac{3}{2} \frac{V_{dd} V_{sat} \mathcal{E}_{sat}}{w_0 R_s}$ ，它仅仅由 MOSFET 本身的物理和设计达到的指标有关，与栅宽无关。

$$I_d = WC_{ox}v_{sat} \frac{V_{od}^2}{V_{od} + L\varepsilon_{sat}} \quad (3.26)$$

$$P_d = V_{dd}WC_{ox}v_{sat} \frac{V_{od}^2}{V_{od} + L\varepsilon_{sat}} \quad (3.27)$$

$$Q_L = \frac{P_0}{P_d} \frac{\rho^2}{1+\rho} \quad (3.28)$$

将式(3.28)代入噪声表达式<sup>[4]</sup>(3.29)中, 得到噪声, 功耗以及栅宽的关系。

$$F = F_{min} + \frac{\gamma}{\alpha g_m R_s} \left[ 1 - \frac{Q_{opt}}{Q_L} \right]^2 \quad (3.29)$$

在给定功耗的情况下, 如果  $\rho \ll 1$ , 则  $\rho^2 \approx \frac{P_d}{P_0} \sqrt{\frac{\delta}{5\gamma} (1 - |c|^2)} (1 + \sqrt{\frac{4}{7}})$ , 此时, 对  $Q_L$  值求导, 那么就可以得到特定功耗下的  $Q_L$ , 这样就可以知道最优栅宽表达式, 如式(3.30)。

$$Q_{Lopt, P_d} = |c| \sqrt{\frac{5\gamma}{\delta}} \left[ 1 + \sqrt{1 + \frac{3}{|c|^2} (1 + \frac{\delta}{5\gamma})} \right] \quad (3.30)$$

那么 MOSFET 的最优栅宽为:

$$W_{opt} = \frac{3}{2} \frac{1}{wLC_{ox}R_s Q_{opt}} \quad (3.31)$$

### 3.5.4 PCSNIM 技术

这种结构可以满足在低功耗下, 功率与噪声匹配的同时性, 结构如图 3.12 所示。

同前几种方法推倒相同, 得到噪声指数如式(3.32)~(3.34)所示。

$$R_s = \frac{\gamma}{\alpha} \frac{1}{g_m} \quad (3.32)$$

$$F_{min} = 1 + \frac{2}{\sqrt{5}} \frac{w}{w_T} \sqrt{\gamma \delta (1 - |c|^2)} \quad (3.33)$$

$$Z_{opt} = \frac{\alpha \sqrt{\frac{\delta}{5\gamma(1-|c|^2)}} + j(\frac{C_t}{C_s} + \alpha|c|\sqrt{\frac{\delta}{5\gamma}})}{wC_s \left\{ \frac{\alpha^2 \delta}{5\gamma(1-|c|^2)} + (\frac{C_t}{C_s} + \alpha|c|)\sqrt{\frac{\delta}{5\gamma}} \right\}^2} - sL_s \quad (3.34)$$

为了同时满足噪声匹配和功率匹配, 需要满足一下条件, 如式(3.35)~(3.38)所示。其中,  $Z_{in}$  为输入阻抗,  $Z_s$  为源阻抗,  $Z_{opt}$  为噪声最优阻抗。

$$\text{Re}[Z_{opt}] = \text{Re}[Z_s] \quad (3.35)$$

$$\text{Im}[Z_{opt}] = \text{Im}[Z_s] \quad (3.36)$$

$$\text{Im}[Z_{in}] = -\text{Im}[Z_s] \quad (3.37)$$

$$\text{Re}[Z_{in}] = \text{Re}[Z_s] \quad (3.38)$$

将式(3.32)~(3.34)代入(3.35)~(3.38)得到计算公式(3.39)~(3.42)所示:

$$\frac{\alpha \sqrt{\frac{\delta}{5\gamma(1-|c|^2)}}}{wC_s \left\{ \frac{\alpha^2 \delta}{5\gamma(1-|c|^2)} + (\frac{C_t}{C_s} + \alpha|c|)\sqrt{\frac{\delta}{5\gamma}} \right\}^2} = \text{Re}[Z_s] \quad (3.39)$$

$$\frac{j(\frac{C_t}{C_s} + \alpha|c|\sqrt{\frac{\delta}{5\gamma}})}{wC_s \left\{ \frac{\alpha^2 \delta}{5\gamma(1-|c|^2)} + (\frac{C_t}{C_s} + \alpha|c|)\sqrt{\frac{\delta}{5\gamma}} \right\}^2} - sL_s = \text{Im}[Z_s] \quad (3.40)$$

$$sL_s + \frac{1}{sC_t} = -\text{Im}[Z_s] \quad (3.41)$$

$$\frac{g_m L_s}{C_t} = \text{Re}[Z_s] \quad (3.42)$$

可见, 与 SINM 技术不同的是加入了一个额外电容, 同时  $R_n$  和  $F_{min}$  不受增加电容的影响。

图 3.12 PCSINM 简化电路图

Fig. 3.12 Simplified schematic of LNA using PCSINM

## 4 低噪声放大器设计

### 4.1 工艺选择

由 2.3 节可以看出模拟设计师总是要在工艺的选择方面作出折衷, 成本(表 4.1)和上市时间也是 RFIC 设计时需要考虑的重要因素。在不远的将来, CMOS 技术在最终的生产成本方面具有绝对的优势, 这是 CMOS 技术在 RF 领域的潜在活力。然而, 深亚微米 CMOS 工艺也带来了一系列问题, 如功耗过大, 衬底耦合, 模型的不完善等。

可见, 随着工艺的发展, SiGe BiCMOS 以及 CMOS 越来越受到集成 RFIC 的关注。主要工艺的比较如表 4.1 所示。

表 4.1 工艺比较

Tab. 4.1 Process comparison

| 指标   | CMOS | Bipolar | GaAs |

|------|------|---------|------|

| 集成度  | 最高   | 较低      | 较低   |

| 速度   | 较低   | 较高      | 最高   |

| 功耗   | 较低   | 较高      | 较高   |

| 流片费用 | 较低   | 较高      | 最高   |

| 代工服务 | 方便   | 困难      | 困难   |

随着 CMOS 工艺深入到深亚微米领域, CMOS 的工作频率变得可以和 Si 双极型相比拟, 这样由 Si 双极型和 GaAs 模块组成的 RF 前端有望由低成本的 CMOS 工艺实现。另外, CMOS RF 前端也容易同后端的 CMOS 数字部分集成到同一衬底上, 从而大大提高了集成度和降低了功耗和成本。Si 器件的高集成避免了信号频繁从片内进出, 从而降低了整个系统的性能。所以本文采用 CMOS 工艺进行低功耗低噪声放大器设计, 对高集成度的单片收发机作出贡献。

### 4.2 IEEE 802.11b 接收机结构设计以及指标分配

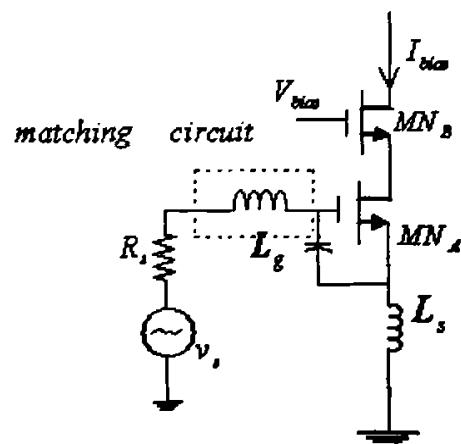

#### 4.2.1 本文接收机结构以及总体指标

基于 WLAN802.11b 的接收机结构很多都是超外差接收机, 但是不易集成。而零中频接收机的最大优点就在于集成度高, 功耗少。第二章指出零中频接收机的主要缺点是  $1/f$  噪声明显、本振泄漏。克服  $1/f$  噪声有两种方法, 首先, 使 MOS 管的面积上升, 在同样的宽长比率下面积增加, 这样会使得带宽下降, 特征频率下降, 在  $1/f$  噪声严重的

混频器或者本振中不可以采用这种形式。另一种方法<sup>[33]</sup>，根据公式 4.1，使得本振周期  $T_{LO}$  增加，即本振频率上升。所以接收机结构中，使第一级本振信号频率为 2.8GHz(而不是 2GHz)。这样可以使闪烁噪声下降。这也是采用两级本振的原因。

$$v_{n,0} = \frac{4IR}{S * T_{LO}} \times v_{n,sw}, \sqrt{v_{n,sw}^2} \propto \frac{1}{WL} \quad (4.1)$$

由零中频接收机的缺陷可以得出一个折中的结构，即双变频零中频结构，如图 3.1 所示。这样本振泄漏也可以克服掉，本振频率都落在前级滤波器的频带以外，所以不会产生本振泄漏。天线信号先下变换到一个高中频 IF(高中频的选择是为了使得第一级镜像抑制滤波器容易实现)，经过滤波和适度放大，再直接变换为基带的 I, Q 两路信号，见图 4.1。和外差式接收机相比，它不需要在 IF 进行 A/D 抽样，它的外接元件数也比多级变换的外差式接收机少得多；和零中频接收机相比，由于二级本振已经大大降低，串扰现象有所减轻(频率越高，串扰越严重)，同时，由于经过了一级中频后的滤波和放大，使得二次混频后的有用信号比直流失调和基带寄生信号幅度大很多，也减小了串扰带来的对输出信号 SNR 降低的影响。本设计中采用的零中频接收机中，第一级中频为高频，第二级中频为零频。虽然第二级的混频器输出端受到  $1/f$  噪声的影响很大，但并不能干扰信号，第一级混频器落在  $1/f$  噪声转换频率外。

图 4.1 二次变频零中频接收机

Fig. 4.1 Double conversion receiver

选择第一级中频非常重要：第一级中频要足够的高，使信号在进入第一级混频器时，镜像信号被 BPF 滤掉。而且第一级中频足够高，混频器可以是电感负载，从而可以克服电阻负载上的直流压降。但是，不是越高越好，第二级混频器输出有闪烁噪声，根据公式 4.1 可知，要求第一中频的选择要在能够去除镜像信号的情况下。

下，越低越好。取  $f_0/f_n \leq 6$ ， $f_n \geq \frac{2.4 \times 10^9}{6} = 400MHz$ ，所以选择本振信号 2.8GHz。

通过计算可知，镜像信号为 3.2GHz。

IEEE 802.11b 标准规定，当采用数据传输率为 11Mb/s 的 CCK 调制方式时，接收机的帧错误率(FER)应该小于  $8 \times 10^{-2}$ 。在保证这样的帧错误率的情况下，其最小输入信号功率为 -76dBm。若假设输入到模数变换器(A/D)的信号的信噪比(SNR)为 10dB 就能满足服务质量的要求，则对采用 22MHz 带宽信道的无线接收机来说，其噪声系数满足式(2.1)，其中 -174dBm/Hz 是天线的可获得噪声功率密度。在保证帧错误率小于  $8 \times 10^{-2}$  时，IEEE 802.11b 无线局域网接收机的最大输入信号功率为 -10dBm。

$$NF = (-76dBm) - 10\log(22MHz) - 10dB - (-174dBm/Hz) = 14.6dB$$

对于相邻信道抑制率，中心频率相差大于 25MHz 的两个信道，其信道抑制率最小应达到 35dB。信道抑制率的测试方法是：在相邻信道输入功率为 -35dBm 的阻塞信号，接收机应该在保证帧错误率小于  $8 \times 10^{-2}$  的情况下解调功率为 -70dBm 的信号。IEEE 802.11b 标准对相邻信道抑制率的规定对接收机的 1dB 压缩点提出了要求。

若假设输入到模数变换器(A/D)的信号的信噪比(SNR)为 10dB 就能满足服务质量的要求，则相邻信道总的载波功率必须满足： $PC \leq (-70dBm) - (-35dBm) - 10dB = -45dBc$ 。

根据邻近信道检测，可以假设有用信号功率和干扰信号功率分别为 -70dBm 和 -35dBm。并且两个信号频率间隔 25MHz。但是，在 WLAN802.11b 标准中，干扰信号是一个宽带信号，因此，考虑调制方式滤波器带宽为 6MHz 之后，计算得到的 CCK 的三阶交调信号比二源信号的三阶交调信号小 37dB，根据三阶交调公式以及其他计算公式可得：

$$IIP3 = \frac{1}{2} (3P_{int} - 37 - P_{int} + SNR_{min}) = 1/2(3*(-35) - 37 + 70 + 13) = -29.5dBm$$

假设解调器 A/D 满量程是 1V，那么 A/D 前的信号最大电平为 13dBm，所以有如下关系式子：

$$\text{系统最大增益} = 13 - (76) = 89dBm$$

$$\begin{aligned} \text{系统 AGC 的总范围} &= (-10) - (-76) - (\text{A/D 前电平最大波动值}) + \text{过剩增益} \\ &= (-10) - (-76) - 1 + 15 = 80dB \end{aligned}$$

接收机总体要求指标为：噪声为 14.6dB，最小接收灵敏度 -76dBm，最大接收功率为 -10dBm。为  $13 - (-76) = 89dB$ 。信道抑制率最小为 35dB，三阶交调为 -29dBm。此外，去

掉开关的 2.0dB 的插入损耗，则接收机其余部分为 10.6dB 的噪声。根据这些参数，分配给整机主要指标如表 4.2 所示。

表 4.2 主要指标

Tab. 4.2 Key parameter

| 性能指标      | 数值   |

|-----------|------|

| NF(dB)    | 14.6 |

| IIP3(dBm) | -28  |

#### 4.2.2 接收机各个模块指标分配

首先，要确定每个模块之间的输入输出阻抗，从天线进来的信号，经过低噪声放大器以及一阶混频器，再经过二阶混频器，通过低通滤波器，通过 VGA 放大，到 A/D 转化器。根据 4.2.1 节指标参数以及通过式 2.2 和式 2.3 反复叠代，最终得到各个模块的指标分配，阻抗匹配如表 4.3 所示。

表 4.3 各个模块阻抗分配

Tab. 4.3 Impedance requirements of RF blocks

| 电路模块    | 输入阻抗( $\Omega$ ) | 输出阻抗( $\Omega$ ) |

|---------|------------------|------------------|

| 射频带通滤波器 | 50               | 50               |

| 低噪声混频器  | 50               | 500              |

| 一级混频器   | 1000             | 500              |

| 二级混频器   | 500              | 500              |

| 中频放大器   | 500              | 100              |

| 低通滤波器   | 100              | 1000             |

| 可变增益放大器 | 1000             | 50               |

| A/D     | 50               | ~                |

其次，各个模块的增益指标分配，系统最大增益为 89dB。表 4.4 中的增益均为功率增益，因为输入输出都实现了共轭匹配，该增益就是可获得功率增益，如果模块的输入输出阻抗相同，那么功率增益与电压增益相同，否则功率增益与有载电压增益相差一个

阻抗变换比。增益分配遵循的原则是：(1) 不要把过多的增益分配在同一个频率上；(2) 射频模块的增益不能分配过高(电路设计困难)，但是射频频率的增益也不能太低，以免中频频率的增益负担过重，例如，射频的混频器采用了有源的结构就是为了增加在射频频率上获得的增益；(3) 如果后级损耗过大，应该在之前适时地引入增益级补偿这个损耗，避免后级噪声的恶化，例如，在无源多相滤波器前增加放大级；(4) 在电路模块具有多个选择时，应综合考虑系统其他参数的要求作出合适的选择，使系统的总体性能最优，例如：混频器的 IIP3 对系统的总体 IIP3 有很大影响，因此，第一级混频器侧重于噪声，第二级混频器的设计要侧重于 IIP3 指标的优化。

最后，线性度 IIP3 的分配，系统的总体 IIP3 满足了系统指标-28dBm 的要求。

表 4.4 各个模块主要指标分配

Tab. 4.4 Key parameters of the RF blocks

| 电路模块    | 增益 (dB) | IIP3(dBm) | 噪声 (dB) | 增益范围 (dB) |

|---------|---------|-----------|---------|-----------|

| 射频带通滤波器 | -3      | 100       | 3       | -3        |

| 低噪声混频器  | 15      | 5         | 4       | 0~20      |

| 一级混频器   | 8       | 3.5       | 13      | 0         |

| 二级混频器   | -0.8    | 6         | 11      | 10        |

| 中频放大器   | 10      | 3.5       | 20      | 10        |

| 低通滤波器   | 5       | 100       | 30      | 5         |

| 可变增益放大器 | 70      | 8         | 40      | 33~70     |

### 4.3 低噪声放大器设计与仿真

首先，降低 LNA 的功耗是设计中的首要问题。LNA 的功耗在射频接收机前端占有很大的比重，降低其功耗对整个接收机很重要。在同等增益的情况下，CMOS 电路比双极性晶体管功耗要大。器件尺寸的减小可以局部地解决这个问题。但是，如果要求考虑到动态范围的要求，那么功耗不会因为尺寸缩小而减小。所以，在保证系统性能的前提下，降低 LNA 的功耗是一个重要问题。

其次，短沟道效应使 LNA 设计更加复杂。短沟道的器件模型还没有健全。短沟道器件中高电场强度使载流子速度饱和，载流子温度升高，器件噪声增大。并且要注意  $V_{dsat}$  与偏置电压  $V_{od}$  的关系，在用短沟道设计电路时，一方面要避免太高的偏置电压，克服来自高场强带来的高噪声以及模型复杂程度带来的试验数据不稳；另一方面，偏置

电压太低则会降低器件的截至频率，使得 LNA 增益减少，线性度下降。因此找到 LNA 的最佳偏置点很重要。

再次，由于数字电路集成在一起，射频前端电路受到供电电压的限制，使得电路动态范围受到限制。数字电路一般采用最先进的工艺以减小面积以及成本。并且集成度在增高，简化系统供电，都要求射频电路的电压受到限制。所以，电压限制使得 LNA 的线性度大大下降。

此外，由于系统集成以及 SOC 的发展，集成了很多模块，封装尺寸越来越大，寄生参数对 LNA 的影响也越来越大。这就要求在设计 LNA 时，考虑到寄生参数下的 LNA 很重要。表 4.5 显示了近期低噪声放大器的设计指标与本设计指标的对比。

表 4.5 低噪声放大器指标对比

Tab. 4.5 Comparison of LNA parameters

| 文献   | 工艺(CMOS $\mu\text{m}$ ) | $P_c(\text{mW})$ | NF(dB) | S21(dB) | S11(dB) | $P_{-1\text{dB}}(\text{dBm})$ | 频率(GHz) |

|------|-------------------------|------------------|--------|---------|---------|-------------------------------|---------|

| [34] | 0.18                    | 8                | 2.7    | NA      | -24     | <-14                          | 2.4     |

| [22] | 0.18                    | 20               | 1.5    | NA      | NA      | -16                           | 2.4     |

| [35] | 0.18                    | 4                | 1.8    | 11      | NA      | -10                           | 2       |

| [36] | 0.18                    | 9.8              | 3.22   | 15      | NA      | -1                            | 2.4     |

| [37] | 0.13                    | 8.4              | 1.6    | 18      | NA      | -15                           | 2       |

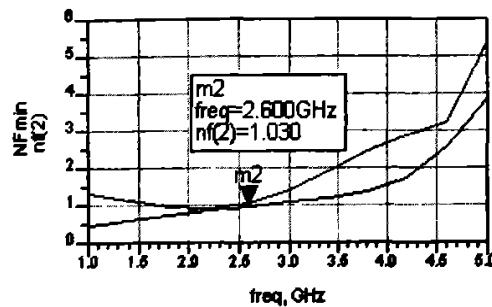

| 本文   | 0.18                    | 4.5              | 1.03   | 16      | -27     | -5                            | 2.4     |

#### 4.3.1 低噪声放大器设计指标

低噪声放大器在接收机部分是很重要的一级。第一，低噪声放大器是接收机中的第一级，为了降低总体接收机的噪声系数，就必须降低 LNA 的噪声系数，用 NF 或者  $nf(2)$  表示，单位用 dB 表示；第二，LNA 的增益影响着后几级的通体增益以及总体的线性度，一般用 S21 表示，单位 dB 表示；第三，要求 LNA 由足够的线性度，从而使得目标信号可以分辨出来，一般用 IIP3 和  $P_{-1\text{dB}}$ ，是输入功率的值，单位为 dBm；第四，由于集成度的发展，市场迫切要求便携式的产品，这样功耗的控制就显得很重要，用  $P_d$ ，单位为 mW。第五，大多数低噪声放大器与  $50\Omega$  特征阻抗的天线以及滤波器相连接，为了要传输最大功率，要求低噪声放大器的输入端必须与  $50$  欧姆有良好的匹配，用 S11 表示，单位为 dB。第六，隔离度。第七，稳定性。另外三阶跨导的单位为 A/V。因此在进行 LNA 设计时，如何采用折衷原则兼顾各项指标是尤为重要的。

本课题根据无线局域网 802.11b 的协议, 预期想要达到的设计指标如表 4.6 所示。

表 4.6 LNA 设计指标

Tab. 4.6 LNA design parameters

| 指标 | freq    | Pdc   | Vdd  | NF    | S11   | S22   | S21  | IIP3 | P <sub>1dB</sub> |

|----|---------|-------|------|-------|-------|-------|------|------|------------------|

| 本文 | 2.41GHz | <10mW | 1.8V | 1.2dB | -17dB | -18dB | 14dB | 1dBm | -10dBm           |

#### 4.3.2 低噪声放大器电路结构

由表 3.1 对比的 LNA 结构可以看出, 共源结构能够提供低的噪声和高的增益, 这符合设计目标。但是这种结构也存在几个缺点: 第一, 从 MOSFET 的输入端看进去没有实数阻抗(除了很小的  $R_g$ )。如果想用  $R_g$  作为匹配网络的一部分, 就会使电路对器件的变化非常敏感; 第二, 由于 MOSFET 棚漏交叠电容  $C_{gd}$  的存在, 会引起 Miller 效应, 输入与输出之间的隔离性变差, 这会导致稳定性问题。

对共源结构的第一个缺点通过在栅端串接一个电感来克服, 这样增加了一个自由度的同时调谐了 MOSFET 的栅源电容; 第二个缺点通过在输出端再接一级共栅放大器来克服。这样看来, 使用共栅放大器所带来的主要好处是消除 Miller 效应的影响, 增加反向隔离度, 从而提高放大器的稳定性, 但它同时也引入了一定的非线性和噪声。

#### 4.3.3 LNA 输入级定量设计

由于要求在特定的低功耗下设计低噪声放大器, 所以采用 CNM 和 SINM 设计方法行不通。采用特定功耗下的噪声最优化设计方法以及特定功耗下噪声与功率同时匹配两种方法对比, 选取一种来满足本文低噪声放大器的要求。

##### (1) 特定功耗噪声优化技术。

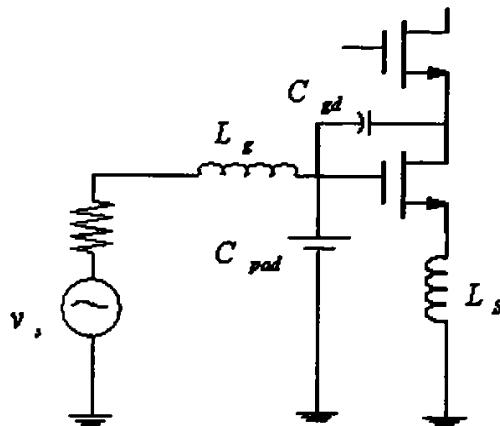

这种结构电路简图, 如图 4.2 所示。

对于典型的源极负反馈结构 LNA 来讲, 在一定的功耗下, 存在一个最优的输入管尺寸, 这个尺寸使得噪声系数最小, 但是并不一定等于最小噪声系数。这种方法在功耗大的时候可以同 SINM 一样, 使噪声系数等于最小噪声系数。在 5mW 下找出使得噪声系数最小的尺寸。由噪声优化技术可知特定功耗下的最小  $Q_{s,opt}$  值, 进而得出:

$$C_{gs,opt} = \frac{1}{wR_s Q_{s,opt}} \approx \frac{1}{2 \times \pi \times 2.4 \times 10^9 \times 50 \times 4.5} \approx 295 fF$$

$$W_{opt} = \frac{3}{2} \frac{1}{wLC_{ox}R_sQ_{opt}} \approx \frac{1}{3wLC_{ox}R_s} = \frac{1}{3 \times 2 \times \pi \times 2.4 \times 10^9 \times 0.18 \times 10^{-6} \times 8.5 \times 10^{-3} \times 50} = 289 \mu m$$

图 4.2 电路原理图

Fig. 4.2 Circuit schematic

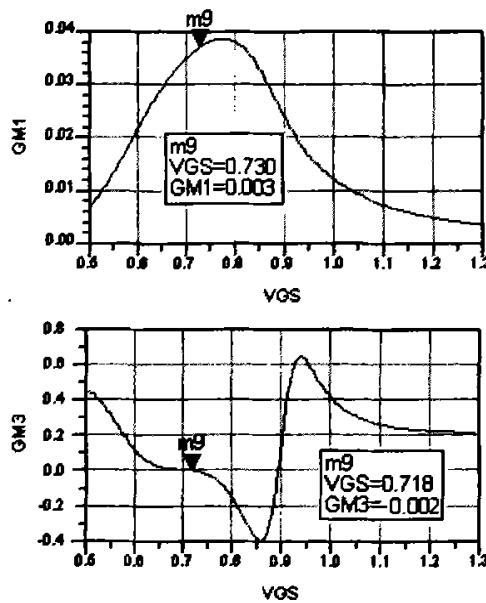

其次,选择偏置电压。选择偏置电压要同时兼顾噪声以及线性度指标,由图 4.3 以及图 4.4 可以看出,  $V_{GS}=0.7V$ , 由于功耗要求,  $I_{DS} < 5/1.8 = 2.7mA$ ; 当  $W_{opt}=260\mu m$ ,  $I_{DS}=6mA > 2.7mA$ , 所以选择  $V_{GS}=0.58V$ , 此时,  $I_{DS}=2.65mA$ , 即:  $NF_{min}=0.89dB$ 。

$$F_{\min} = 1 + \frac{2}{\sqrt{5}} \frac{w}{w_L} \sqrt{y\delta(1-|c|^2)} = 1 + \frac{2}{\sqrt{5}} \frac{2\pi \times 2.4 \times 10^9 \times 295 \times 10^{-15}}{2 \times 2.65 \times 10^{-3} / (0.58 - 0.28)} = 1.22$$

图 4.3 MOS 管的偏置与最小噪声的关系

Fig. 4.3  $NF_{min}$  versus  $V_{GS}$  of the MOSFET

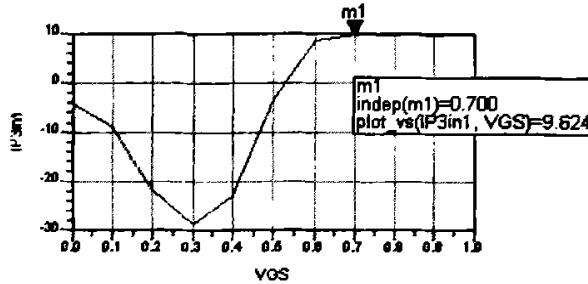

图 4.4 MOS 管的偏置与三阶交调 IIP3 的关系

Fig. 4.4 IIP3 and VGS of the MOSFET

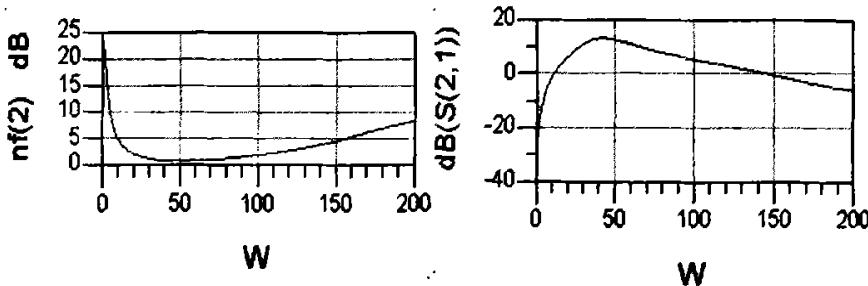

第三，在确定的偏置范围内，扫描 finger 指数选取最小的噪声影响度。由图 4.5 可以看出，finger 取值大概在 50-100 左右，选取 50。即  $count=W_{opt}/W=260\mu\text{m}/50\approx 5$ 。

图 4.5 MOS 管的噪声与栅指指数的关系

Fig. 4.5 Noise figure versus multi\_finger of the MOSFET

最后，进行功率匹配，源阻抗为纯阻抗  $50\Omega$ ：

$$R_s = w_t L_s = \frac{g_m}{C_{\mu}} \times L_s = \frac{u_n C_{ox} W V_{od} / L}{2/3 \times W \times L \times C_{ox}} \times L_s = \frac{0.0285 \times (0.65 - 0.36)}{2/3 \times 0.18 \times 0.18 \times 10^{-12}} \times L_s = 50$$

得出： $L_s = 0.17\text{nH}$ ，为了使虚部为零，满足： $w^2 (L_s + L_t) \times C_{\mu} = 1$ ，得  $L_t = 14.8\text{nH}$ 。

## (2) 特定功耗下噪声与功耗同时匹配技术

这种结构电路，就是在图 4.2 电路的基础上加上额外栅源电容。

第一，先确定直流工作点。偏置对 MOS 管的噪声和增益影响比较大。通过扫描 VGS，

确定最小噪声点的偏置大小。兼顾考虑 IIP3 的大小。通过仿真，如图 4.3 和图 4.4 可以看出：偏置取 0.7V 左右电压较为合适。为了低功耗，要求偏置电流小于 4mA。

第二，在确定的偏置范围内，扫描 finger 指数选取最小的噪声影响度。选择 60。

第三，确定栅宽。把噪声因子与宽度联系起来求导<sup>[29]</sup>：

$$W_{opt} = \frac{1}{Q(Q^2 + \frac{1}{4})^{1/2}} \sqrt{\frac{b}{3a}} \approx \frac{1}{Q^2} \sqrt{\frac{b}{3a}} = \frac{A_b}{2Q^2} \sqrt{\frac{5}{6}} \frac{3}{4w_0 R_s C_{ox} L} \quad (4.2)$$

其中，Q 值选取范围是根据线性度和对参数的灵敏度。在偏置一定的情况下，根据功耗要求选择适当的栅宽，最大不能超过 240μm。如果 Q 值选取越小，那么线性度就越好，所以要求 Q 值小于 4。我们选择 Q 的值为 2~3。

第四，确定其他的参数 Cex、Ls 和 Lg。确定了晶体管大小和偏置条件后，接下来就要做输入级匹配，确定栅源并联电容 Cex、输入电感 Lg 和源极负反馈电感 Ls。它们的计算公式如式(4.3)~(4.9)所示。计算当 Q 取不同值时的  $W_{opt}$ 、 $L_s$ 、 $L_g$ 、 $F_{min}$ 、 $C_t$  等几个参数的值，结果如表 4.7 所示。

$$C_{ex} = \frac{2}{3} W_{opt} \times l \times C_{ox} \quad (4.3)$$

$$P_{opt} = \frac{A_b}{2Q} \sqrt{\frac{5}{6}} \quad (4.4)$$

$$C_t = C_{ex} / P_{opt} \quad (4.5)$$

$$F_{min} = 1 + \frac{1}{Q} 4\beta^{1/4} (\gamma'/12)^{3/4} \sqrt{\frac{2w_0}{3u_{eff} R_s I_{ds}}} L \quad (4.6)$$

$$g_m = \frac{2u_0 C_{ox} W_{opt} I_{ds}}{(L \times A_b)^{1/2}} \quad (4.7)$$

$$L_s = \frac{R_s C_t}{g_m} \quad (4.8)$$

$$L_g = \frac{1}{w_0^2 C_t} - L_s \quad (4.9)$$

可见, 最优栅宽只与  $Q$  有关, 而与偏置电流无关, 与功耗无关。通过理论计算, 选择初始栅宽为  $114\mu\text{m}$ ,  $C_d$  为  $207\text{fF}$ ,  $L_s$  为  $0.75\text{nH}$ ,  $L_g$  为  $12.5\text{nH}$ 。

表 4.7 低噪声放大器的器件参数以及噪声性能

Fig. 4.7 Component values and noise performance of the LNA

(a) 偏置电流为  $2.5\text{mA}$

| $Id_s=2.5\text{mA}$    | $Q=2$ | $Q=3$ | $Q=4$ |

|------------------------|-------|-------|-------|

| $W_{opt}(\mu\text{m})$ | 114   | 60.7  | 28.5  |

| $P_{opt}$              | 0.373 | 0.249 | 0.189 |

| $C_{gs}(\text{fF})$    | 123.9 | 55    | 31    |

| $C_t(\text{fF})$       | 331   | 221   | 165   |

| $L_s(\text{nH})$       | 0.75  | 0.74  | 0.73  |

| $L_g(\text{nH})$       | 12.5  | 19.1  | 25.7  |

| $F_{min}(\text{dB})$   | 0.33  | 0.28  | 0.18  |

(b) 偏置电流为  $3\text{mA}$

| $Id_s=3\text{mA}$      | $Q=2$ | $Q=3$ | $Q=4$ |

|------------------------|-------|-------|-------|

| $W_{opt}(\mu\text{m})$ | 114   | 60.7  | 28.5  |

| $P_{opt}$              | 0.373 | 0.249 | 0.189 |

| $C_{gs}(\text{fF})$    | 123.9 | 55    | 31    |

| $C_t(\text{fF})$       | 331   | 221   | 165   |

| $L_s(\text{nH})$       | 0.62  | 0.61  | 0.60  |

| $L_g(\text{nH})$       | 12.6  | 19.2  | 25.9  |

| $F_{min}(\text{dB})$   | 0.3   | 0.26  | 0.12  |

#### 4.3.4 LNA 输入级分析

前面进行了理论计算, 但是理论计算在射频设计的电路中很必要, 作为实际设计的理论指导。

##### (1) 特定功耗噪声优化技术分析

根据理论, 当  $W_{opt}=260\mu\text{m}$  时, 在固定的偏置下, 仿真噪声系数最小。但是, 通过仿真电路栅宽度与噪声的关系, 如图 4.6 所示。

图 4.6 输入管子宽度与噪声的关系

Fig. 4.6 Gate width of input MOS

由式(3.27)计算得来最优栅宽  $W_{opt}$  与图 4.6 仿真得出的最优栅宽  $W_{opt}$ , 分别为  $260\mu\text{m}$ 、 $200\mu\text{m}$ , 两者的差别可以作这样的解释: ① Chartered  $0.35\mu\text{m}$  CMOS 的 MOSFET 模型为 BSIMv3.2, 并没有包含栅感应噪声; ② 计算时, 采用的 MOSFET 模型为简单

的平方率关系，即 MOSFET 工作于强反型区，没有考虑 MOSFET 工作于中等反型区以及弱反型区。实际上，在栅宽很大的情况下，栅源之间的直流偏置很小，MOSFET 工作于哪一区域取决于工艺参数，很难保证一直工作在强反型区，而是更接近中反型区。

③ 在设计的电路中，由于密勒效应以及寄生电容的影响，使得在输入管的栅源电容外仍然有额外电容的存在，如图 4.7 所示。

图 4.7 输入管栅极寄生电容

Fig. 4.7 Parastic capacitor on the gate of input MOSFET

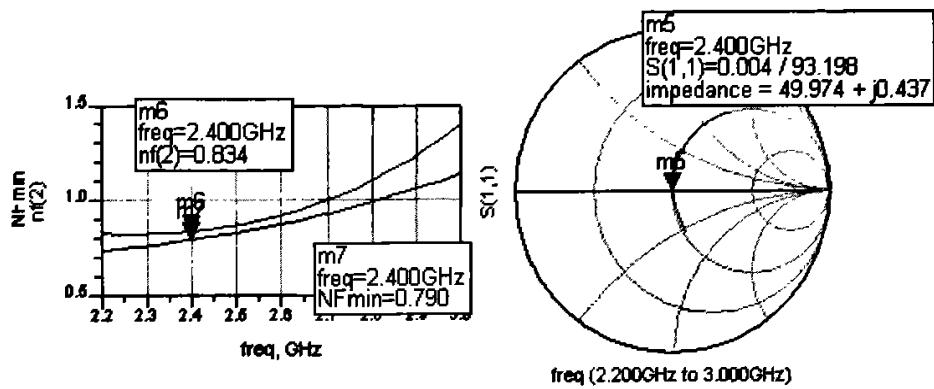

这样， $W_{opt}$  变小，匹配参数也要发生变化，根据公式(3.22~3.27)可以看出变化趋势为：在固定的功耗下，即偏置电流一定， $L_s$  减小， $L_g$  增大。以这样的趋势，调节参数，最终得到功耗匹配。仿真结果由图 4.8 所示，图 4.8(a)给出了噪声指数，在 2.4GHz 频率处，最小噪声为 0.79，这比理论计算 0.89dB 稍小。其实，由于寄生参数的影响使得对最优器件宽度的过大估计，而这又使得噪声系数比最小值大了 0.1dB。如果按照考虑  $C_{gd}$  的方法选取最优的器件宽度，就可以使得所得的噪声提高了 0.1dB。

而优化噪声为 0.834dB，优化得来的噪声指数与最小噪声指数不一样，这种技术是一种低功耗的 LNA 设计，在一定的功耗下，提供最优晶体管大小从而有最低的噪声。然而，LNA 的噪声大于 LNA 的最小噪声。原因在于： $Z_s$  和  $Z_{opt}$  失配或者  $L_s$  的值太大，所以使得最优噪声并不是最小噪声，即  $NF=NF_{min}$  不成立。因此，采用这种方法不会使得噪声为最小噪声，要采用下面一种方法才可以在低功耗下，噪声匹配，并且功率也同时匹配。如果加上实际电路，那么噪声就会更大，以至于超过 1dB。而且最初选择偏置的时候，没有按照最低噪声来选择，所以噪声可以做得更好。那么将采用同时匹配方案来解决这个问题。

图 4.8 电路仿真结果

(a) 噪声系数 (b) 最小噪声系数 (c) S11

Fig. 4.8 Simulation results

(a) noise figure (b) NFmin (c) S11

## (2) PCSINM 技术分析

同样，这种技术的输入管的栅宽理论计算也没有考虑到栅极寄生电容的影响，但是这并不影响输入级管子宽度大小的选择，栅极寄生的电容都可以被外加电容所吸收，这也是这个结构的好处之一。

通过仿真在初始值附近进行优化。通过仿真可知，当  $Q$  为 2，电流  $2.5\text{mA}$  时， $VGS$  为  $0.68$  时，仿真出来栅宽为  $120\mu\text{m}$ ，这个值比理论稍大，然后，对  $L_s$  在  $0.75\text{Nh}$  附近进行扫描，使得输入阻抗为  $50\Omega$ （图 4.9c）；接着调节  $C_{ex}$  使得  $NF \approx NF_{min}$ ，即实现噪声匹配。但是由于输入等效阻抗随着  $C_{ex}$  的增大而减少，所以仍然要调节  $L_s$  使得输入阻抗再次回到  $50\Omega$ ，这样反复调节，直到噪声与增益同时匹配，最后，利用  $L_g$  使得输入阻抗虚部为零。如图 4.9 所示。图 4.9(a)给出了噪声指数，在  $2.4\text{GHz}$  频率处，最小噪声为  $0.319$ ，这比理论计算  $0.33\text{dB}$  稍小。图 4.9(a)和(b)、(c)表明电路可以低功耗下噪声匹配与阻抗匹配同时达到。

PCSNIM 技术的限制是噪声电阻  $R_n$  的值有点高。噪声电阻  $R_n$  并不受外加电容  $C_{ex}$  的影响，只依赖于跨导  $gm$  的值，所以，小的晶体管尺寸以及低的功耗可能引起很大的  $R_n$ ，从而如果偏置稍微变化一点，就会使得 LNA 的噪声有很大的波动，而且使得 LNA 的成品率大大降低，这样就对偏置稳定性有了很大的要求。

图 4.9 输入级的噪声匹配与功率匹配同时匹配

Fig. 4.9 The input amplifier with simultaneous noise match and impedance match

通过对比，可以知道这四种匹配方案的优缺点，如表 4.8 所示。

表 4.8 四种匹配方法对比结果

Tab. 4.8 The results of four matching methods

| 参数       | CNM | SNIM | PCNO | PCSNIM |

|----------|-----|------|------|--------|

| NF=NFmin | +   | +    | -    | +      |

| 功耗约束     | -   | -    | +    | +      |

| 功率匹配     | -   | +    | +    | +      |

### (3) 棚源电容对线性度的影响

在射频电路中，线性度也是一个重要的参数要考虑。低噪声放大器的线性度由于是小信号处理，所以三阶交调体现的很重要。根据文献[38]可知线性度的推导方式。但是文章中并没有考虑寄生电容以及外加棚源电容对线性度的影响。

通过再次推导，可得三阶干扰项为式(4.10)：

$$HD_3 = \left| \frac{1}{24} \nu_{in}^2 \times \frac{1}{(1-sC_p)^2} \left( 2K_{gm-3} + \frac{3r_s K_{gm-2}^2}{(1+2sC_i + r_s g_{mi})} \right) \times \frac{(1+3sC_i)}{(1+3sC_i + r_s g_{mi}) g_{mi} \times (1+sC_i + r_s g_{mi})^2} \right| \quad (4.10)$$

从式(4.10)可见, 随着  $C_t$  和  $C_p$  的增加, 三阶交调干扰项下降, 从而线性度可以上升。

#### 4.3.5 LNA 偏置及共栅管设计与分析

由于 LNA 在芯片中, 对噪声有决定性的作用。所以, LNA 的版图一般都与其他模块相互隔离, 有很多电路中的偏置结构都是采用镜像电流源形成偏置电压, 这样就浪费了芯片的面积, 所以本文采用的是自偏压形成的恒跨导偏置, 这样的偏置源来稳定增益和输入阻抗以克服温度及电源电压的影响。

在设计 LNA 的时候, 第一个 MOS 管主要是针对低噪声来设计的, 第二个 MOS 管重点应当放在线性度的设计上, 之所以选择共源共栅的结构主要是要抑制栅源电容的 MILLER 效应。当然在这个过程中注意对增益, 噪声, 线性度的影响。

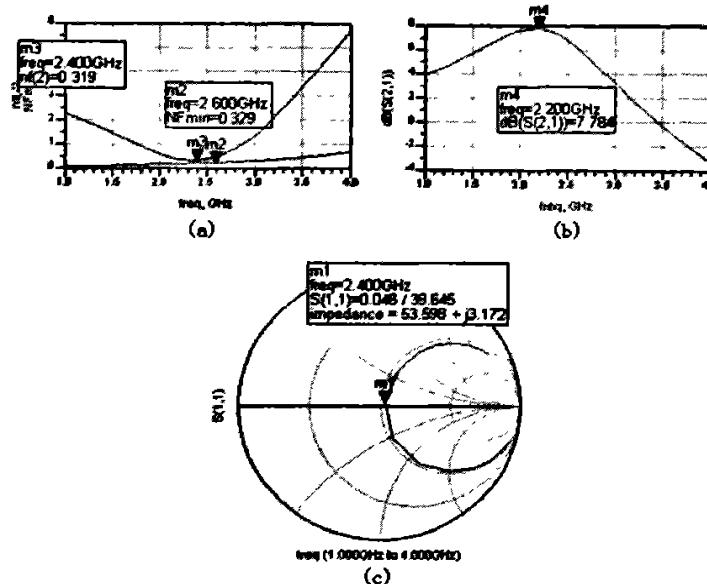

首先, Cascode 场效应管对低噪声放大器的噪声性能的影响常常被射频集成电路工程师忽略。根据文献[6]可知: 如果  $\omega_0$  远小于  $\omega_r$  并且  $\gamma_2 g_{d02}$  与  $\gamma_1 g_{d01}$  是相差不多或者  $\gamma_2 g_{d02} < \gamma_1 g_{d01}$  的话, 这种假设才成立。第一个条件在大多数情况下都可以满足, 但是第二个条件只有当两个场效应管的宽度是相当的或者  $M_2 < M_1$  才可以成立。在实际应用中, 常常取值相等<sup>[4][52][29]</sup>。在这种情况下,  $M_2$  管对低噪声放大器的噪声系数影响很小。但这并不代表  $M_2$  的宽度能远小于  $M_1$  以提高低噪声放大器的噪声性能。但是, 实际上  $M_2$  不能远小于  $M_1$ , 如果  $M_2$  的宽度很小, 那么需要一个很大的  $V_{GS2}$  才可以使得电流通过。由于  $V_{DS1} = V_{DD} - V_{GS2}$ , 一个很大的  $V_{GS2}$  使得  $M_1$  进入饱和区, 这样在很大程度上就恶化电路噪声。Cascode 管对噪声的影响: 存在一个最优点使得总体噪声最小。为了把 cascode 场效应管的影响加入考虑设计中, 仿真了几种情况, 如表 4.9 以及图 4.10 所示: 当  $W_1$  与  $W_2$  近似相同时,  $W_2$  的改变对噪声系数的影响几乎没有, 但是当  $W_2$  远小于  $W_1$  时,  $M_1$  进入饱和区, 噪声系数大大恶化, 当  $W_2 > 2W_1$  时, 随着  $W_2$  的增大噪声系数而增大。其次, cascode 管对线性度的影响也很重要。存在一个点使线性度最高, 本文这两个管子只要求关注于噪声, 同时不能取太小, 否则线性度受到很大破坏。所以, 取噪声最小的第二个管子的长度取  $50 \times 2 = 100 \mu\text{m}$ 。

表 4.9 宽度与噪声关系图

Fig. 4.9. Noise figure versus W

| 指标     | W2=50μm | W2=100μm | W2=200μm |

|--------|---------|----------|----------|

| NF(dB) | 0.685   | 0.559    | 0.694    |

图 4.10 楼宽与噪声关系图

Fig. 4.10 Noise figure versus M

(6) 基本结构确定后，增加 PMOS 管进行设计

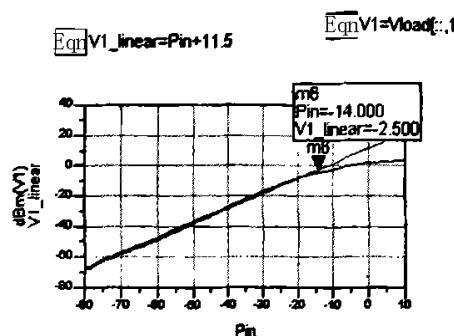

图 4.11~4.12 为 LNA 没有加上改善电路的三阶跨导的仿真及线性度仿真，由图 4.11 可知，仅仅在一个偏置点上，三阶跨导的值较小，仅仅有一个偏置电压才能够满足，这样的电路是不存在的。而这个电路仿真出来的 1dB 压缩点为-14dB，不能满足 LNA 的指标。

图 4.11 偏置与三阶跨导的关系

Fig. 4.11 Bias versus the 3<sup>rd</sup> conductance

图 4.12 1dB 压缩点

Fig. 4.12 1dB compression

由前面所述的线性度的原理,如图 3.10 所示的电路可达到较高的线性度。但是它也有自己的缺点就是引起增益和噪声的下降,但由于 PMOS 的偏置电流很小以及由于 PMOS 的低速率使得 NMOS 的一阶跨导并没有减少很多,所以增益的影响不是很大。于是,本文采用三阶跨导的叠加原理使得线性度提高。

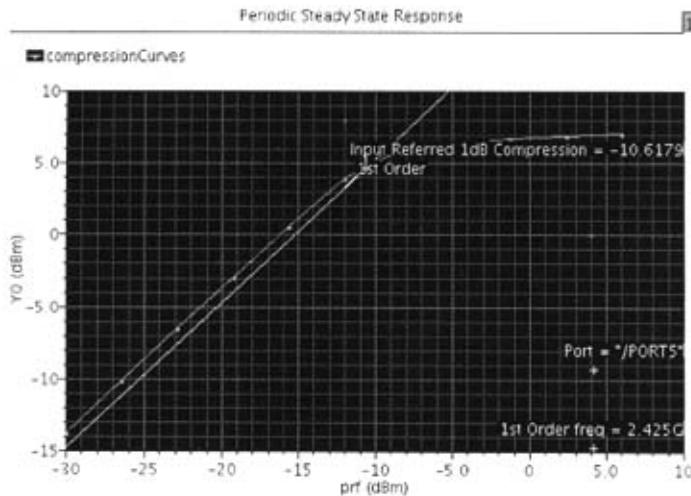

本文低噪声放大器电路中采用的电感 Q 值最大只有 6~7,所以由于电感引入的噪声还是很大的,可见电感片内实现在 RFIC 领域中是至关重要的。图 4.13~图 4.14 是改善电路的三阶跨导仿真及线性度仿真,而图 4.13 中可以看出,在较大的偏置范围内,三阶跨导都可以保持一个很小的值,但没有得到趋近于 0 的三阶跨导值,这是由于还有一些寄生的影响不可能使得三阶跨导完全为零,所以线性度也不可能为无限大。图 4.14 得到的 1dB 压缩点达到了-5dB,满足了本文 LNA 线性度的要求。

图 4.13 偏置与一阶三阶跨导的关系

Fig 4.13 Bias versus the 3<sup>rd</sup> and 1<sup>st</sup> conductance

最后设计输出匹配电路,它主要受到共栅管输出电感和输出电容的影响。通过仿真 S 参数,调节  $L_0$  及  $C_0$  可以将输出电阻匹配到  $500\Omega$ 。

图 4.14 1dB 压缩点

Fig. 4.14 1dB compression

#### 4.3.6 完整 LNA 电路及仿真结果

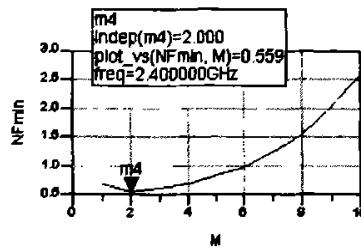

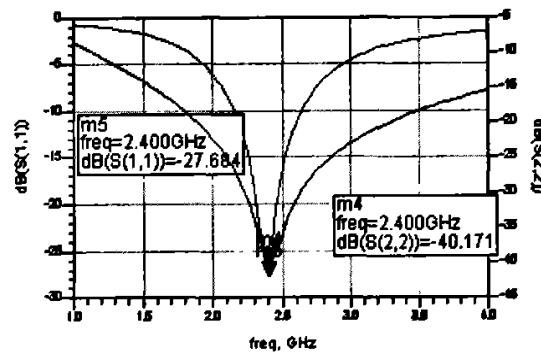

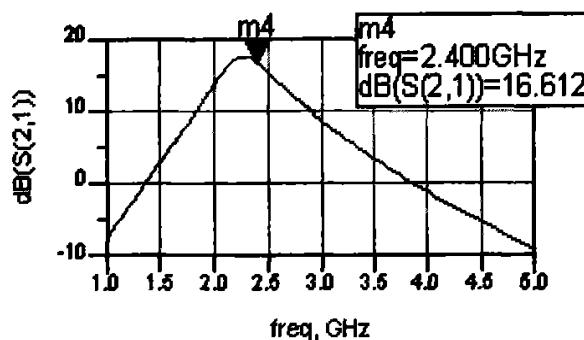

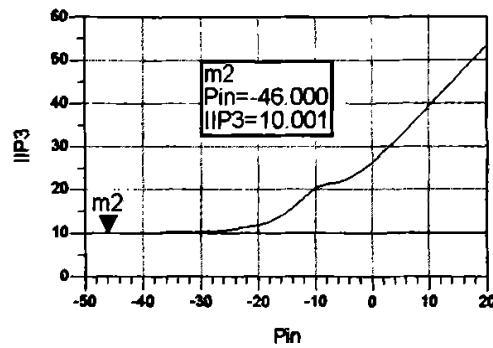

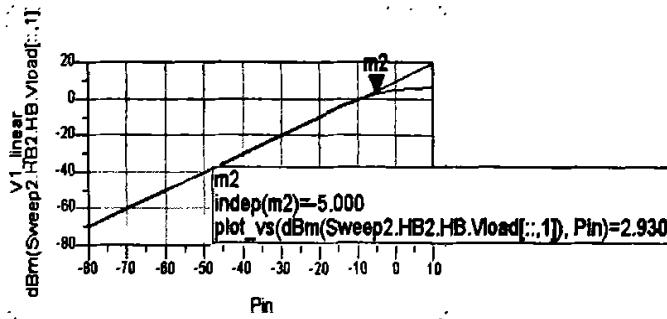

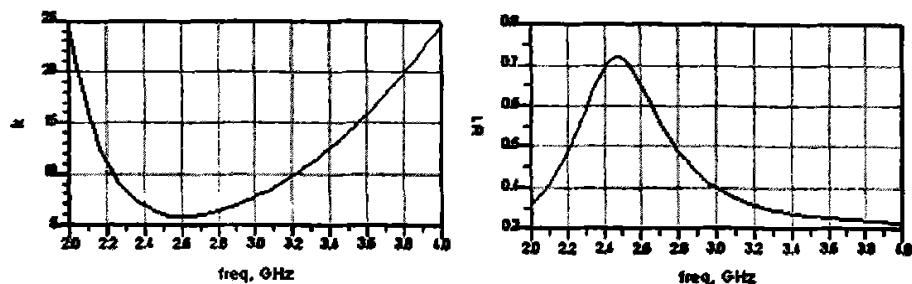

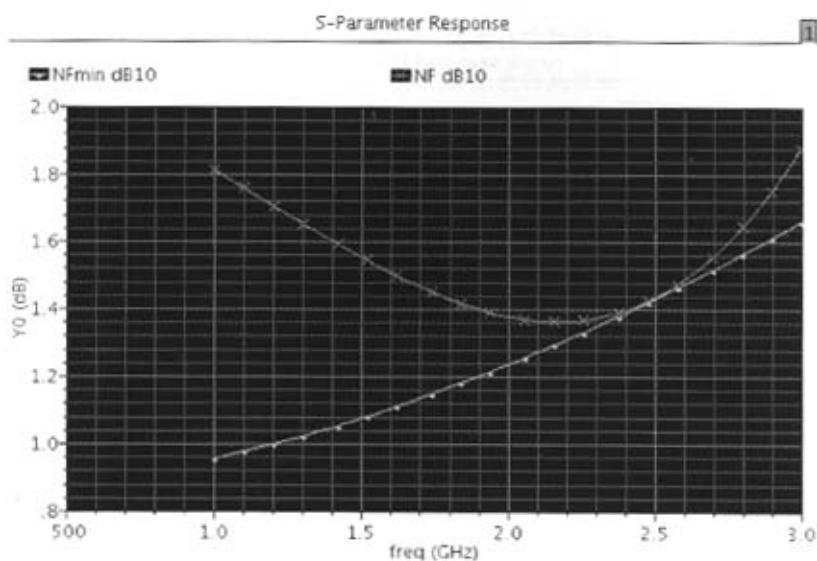

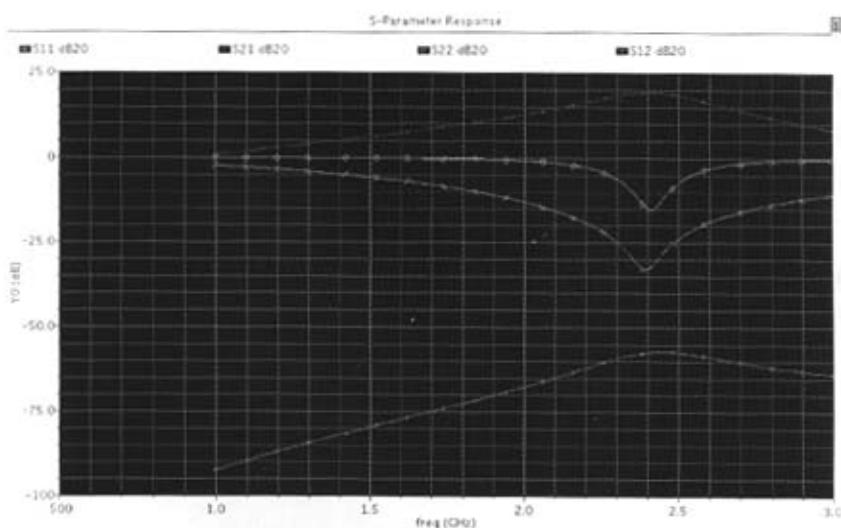

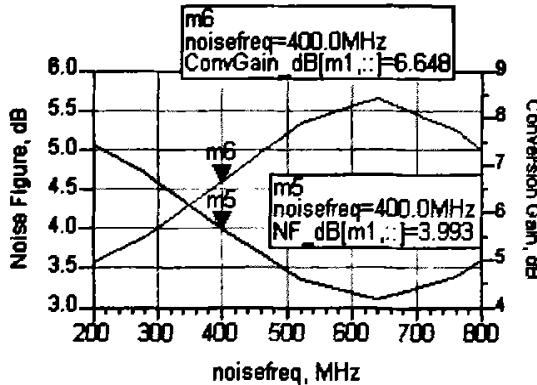

图 4.15~4.21 给出了最终电路及仿真结果, 图 4.15 是电路图, 图 4.16 是电路仿真噪声, 在 2.4GHz 频段的最小噪声就等于电路的噪声即噪声匹配, 噪声为  $0.998\text{dB} < 1.2\text{dB}$ , 比单管的最小噪声  $0.319\text{dB}$  大, 这是因为其他 MOS 管以及工艺中的电感电容都有寄生电阻, 也同样对噪声有贡献; 图 4.17 反映出反射系数  $S_{11}$  及  $S_{22}$ , 它们表示输入输出端口的匹配程度, 都大于  $-15\text{dB}$ , 这说明有很好的匹配度。图 4.18 表示增益大小  $S_{21}$ , 达到  $16.6\text{dB}$ ; 图 4.19 及图 4.20 分别是三阶交调以及 1dB 压缩点, 表示线性度性能,  $P_{1\text{dB}}$  是  $-5\text{dBm}$ ,  $\text{IIP3}$  是  $10\text{dBm}$ 。图 4.21 是对电路稳定性仿真的曲线。在 ADS 中, 结合稳定条件: 当  $K > 1$  且  $B > 0$  时电路无条件稳定。由图 4.21 看出, 本电路是绝对稳定的。

图 4.16 噪声

Fig. 4.16 Noise figure

图 4.17 反射系数  $S_{11}$  和  $S_{22}$

Fig. 4.17 Reflection parameter  $S_{11}$  and  $S_{22}$

图 4.18 增益  $S_{21}$

Fig. 4.18 Gain  $S_{21}$

图 4.19 线性度 IIP3

Fig. 4.19 Linearity IIP3

图 4.20 线性度 1dB

Fig. 4.20 Linearity 1dB

图 4.21 稳定性

Fig. 4.21 Stability

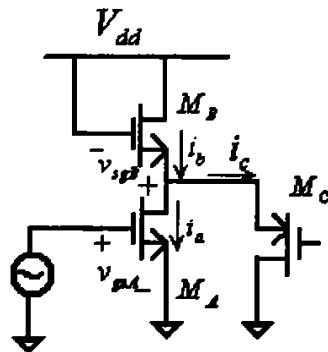

## 4.4 差分 LNA 设计与仿真

### 4.4.1 差分 LNA 设计原理图及仿真结果

单端 LNA 结构至少有一个重要的缺点，即没有共模抑制能力，这种考虑在混合信号应用中特别重要，因为在这种应用中无论是电源电压还是衬底电压都可能含有噪声。而差分连接的一个重要优点是它有抑制共模干扰的能力。为了使在高频时的共模抑制最大，关键的是绝对要使版图尽可能的对称。

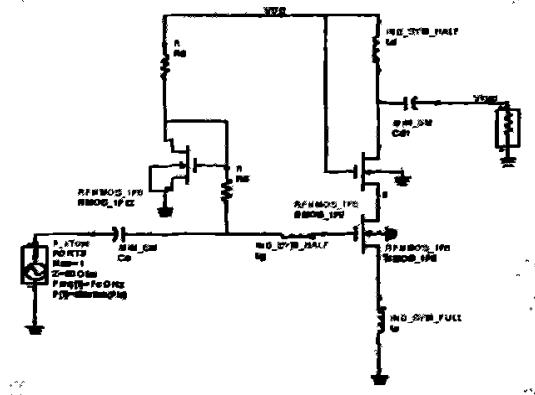

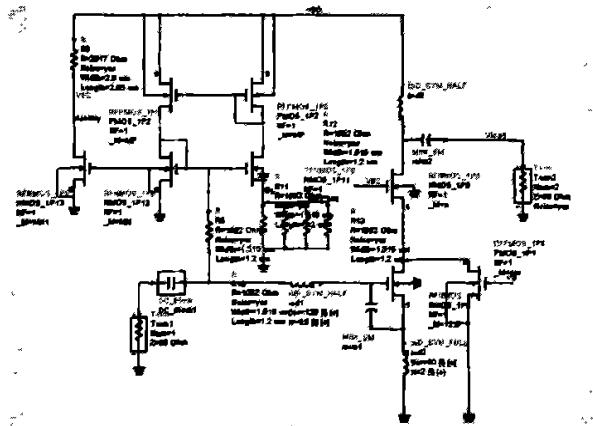

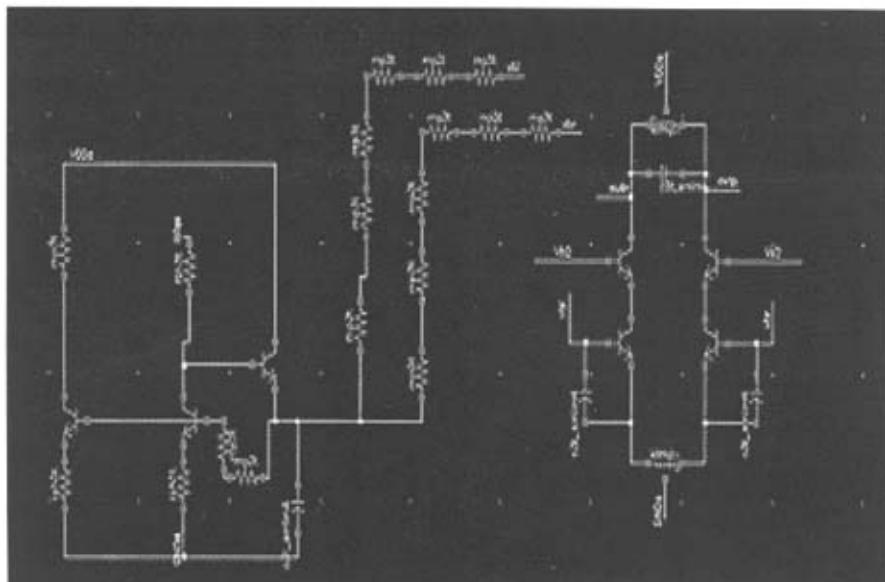

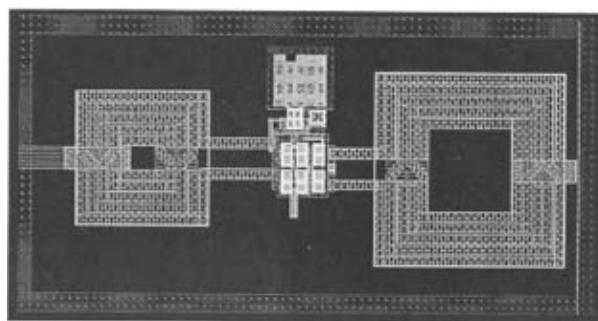

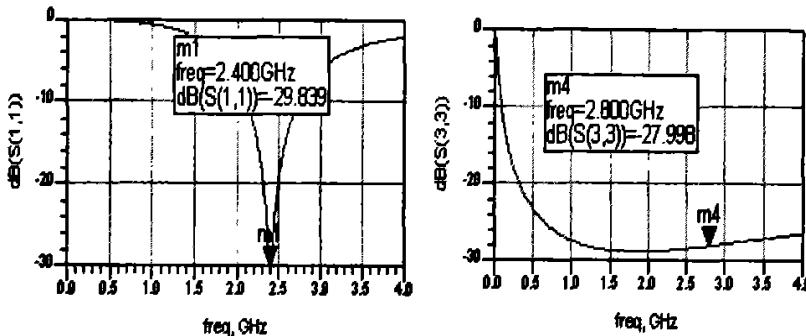

采用 JAZZ 0.35 $\mu\text{m}$  BICMOS 工艺设计差分 LNA，并采用差分输入的方法来防止外接寄生电感的影响，设计过程与单低噪声放大器类似，同时输入匹配仍然采用 PCSINM 的方法，与单端 LNA 设计过程相同。Cadence 仿真环境下，采用相同输入匹配结构设计的差分低噪声放大器原理图如图 4.22 所示。通过对差分低噪声放大器仿真，仿真结果如图 4.23~4.25 所示。仿真指标如表 4.10 所示。

图 4.22 电路原理图

Fig.4.22 Circuit schematic

图 4.23 噪声

Fig. 4.23 Noise figure

图 4.24 S 参数

Fig. 4.24 S parameter

图 4.25 线性度 1dB 压缩点

Fig.4.25 Linearity 1dB compression

表 4.10 LNA 设计指标对比

Tab. 4.10 Comparison of LNA design parameters

| 指标     | freq    | Pdc    | Vdd  | NF     | S11   | S21    | IIP <sub>3</sub> | P <sub>1dB</sub> | 工艺               |

|--------|---------|--------|------|--------|-------|--------|------------------|------------------|------------------|

| 单端 LNA | 2.41GHz | 5mW    | 1.8V | 0.99dB | -27dB | 16.6dB | 10dBm            | -5dBm            | 0.18μm<br>CMOS   |

| 差分 LNA | 2.41GHz | 10.8mW | 3V   | 1.39dB | -34dB | 20dB   | N/A              | -10dBm           | 0.35μm<br>BiCMOS |

这两个低噪声放大器都是 2.4GHz 频段工作, 从理论上讲<sup>[4]</sup>, 为达到相同的噪声, 相同的工艺差分放大器的功耗是单端放大器的两倍, 噪声系数是单端放大器噪声系数的两倍, 增益与单端低噪声放大器的增益相同。观察表 4.10 的指标对比, 由于工艺 0.35μm 的 MOS 管特征频率比 0.18μm 小, 所以噪声系数应当比单端噪声系数的两倍大, 但  $0.99 \times 2 = 1.98 > 1.39$ , 这是因为双极性晶体管的特征频率大于 MOS 管, 从而有利于噪声下降, 以及增益的上升。通常, 差分放大器的线性度都要比单端好, 用特定功耗噪声优化技术构成的电路线性度指标 P<sub>1dB</sub> 只有 -14dBm, 小于 -10dBm, 而对于有匹配电路的单端 LNA, 采用变换结构的方法来产生高的线性度, 本文在低功耗下, 线性度指标 P<sub>1dB</sub> 达到了 -5dBm。

由此可见, CMOS 工艺设计的 LNA 可以满足在功耗很低的情况下, 噪声也满足要求。随着 CMOS 工艺最小线宽的减小, CMOS 工艺将高集成、高性能、低成本、低功耗的高频单片功能收发芯片成为可能, 即可以实现 2GHz 以上的射频与数字控制集成。

#### 4.4.2 版图设计

##### (1) 版图设计

电路设计完成后进行了版图设计。版图设计主要是根据射频集成电路版图的设计要点进行:

- ① 信号连线的金属条宽度应该根据直流大小比例选取。

- ② 最短信号线原则, 即连线越短越好。这样可以减少寄生电感。

- ③ 连线金属应该遵循能用高层不用低层金属的原则, 以减小寄生电容效应。

- ④ 晶体管、电容等器件上不能安排金属走线, 并且要避免不同层金属线之间重叠。

- ⑤ 两条金属走线是同层而且是平行时, 若其是差分信号线则二者间距离越小越好; 若不是, 则越大越好。

- ⑥ 尽量避免 90 度转角, 如果非要转角, 那么将拐角处弄成弧形。

版图设计结果可能严重影响射频电路设计的性能, 因此在进行射频电路的版图设计时, 主要需要考虑到匹配性, 对称性。模拟电路和数字电路布局以及射频信号的天线效应等问题。在本次 LNA 的设计中主要考虑的是输入对称管的匹配和级联问题。MOS 管可以通过共质心版图布局以及做成双栅 MOS 管等方法解决。应当注意这些寄生效应的消减方式, 比如如何减少寄生电容。特别在画版图的时候, 比如电路需要尽可能匹配时就必须考虑了。寄生电感的影响也是应当注意的, 不应使走线太长。版图如下图 4.26 所示:

图 4.26 JAZZ 0.35 $\mu$ m BICMOS 的低噪声放大器版图初步设计

Fig. 4.26 The initial layout of LNA based on JAZZ 0.35 $\mu$ m BICMOS

## (2) 版图验证

除了设计初步的版图外, 还要在版图上加上接触 pad 线, 要进行版图的设计规则检查(DRC), DRC 是检查版图的几何尺寸是不是符合工艺规定; 电气规则检查(ERC), 检查 Power, Ground 的短路等指定的电气特性; 版图与电路对照(LVS), 从版图中根据器件与节点识别提取出的电路与原设计电路作对比检查, 以检查布局前后电路的连接方式是否一致, 如 MOSFET 的 L、W 值是否相符合。但是, 一般不做 ERC 检查, 因为 LVS 中的检查也可以查到电气规则的特性要求。最后, 还要提取参数(LPE), 参数提取将在前仿真中没有考虑到的寄生的电阻、电容等参数从生成的版图中提取出来, 然后反标到网表文件中, 供电路设计者做版图后仿真之用。进行后仿真的时候, 后仿真在 DRC、ERC、LVS 和 LPE 后进行, 根据包含了寄生参数的网表文件来做仿真, 以检查版图中的寄生器件对电路的影响。然后进一步调整电路参数以达到设计指标。接着再将仿真后的网表再重新做版图设计; 这样的过程可能要反复几次才能达到最终的设计目标。

## 4.5 LNA 实际设计考虑因素

### 4.5.1 输入管栅极寄生电容

图 4.7 所示的栅极寄生电容, 影响了放大器的性能。除了对栅极宽度选择有影响外, 还对射频信号有很大的衰减, 严重影响功率增益。由于 LNA 电路信号进入芯片之前实际上是功率输入而不是电压输入, 一个对地的寄生电容是尤其要尽力避免的。这个电容无法避免, 那么应该尽可能的减小它的影响。

其次, 这个电容还会改变输入阻抗值, 等效的输入阻抗值约为<sup>[39]</sup>:

$$\text{Re}(Z_{in}) = \left( \frac{C_p}{C_p + C_s} \right)^2 R_s \quad (4.11)$$

这样就使得从输入端看进去的电阻比实际的小。对于本文要设计 LNA, 一个 1pF 的  $C_p$  将使所得到的输入阻抗不大于  $8\Omega$  (做  $50\Omega$  匹配), 所以在实际设计中, 需要增加额外的匹配电路, 使电阻匹配到所需要的值, 也可以通过增加反馈电感值来增大等效电阻。

### 4.5.2 输入管源极寄生电容

一个源级负反馈电感会在 MOS 的栅极形成一个等效正电阻。而一个与源级相连的电容, 在栅极将引起一个负值电阻。这一电阻负反馈电感形成的等效正电阻值相互抵消, 使输入管栅极的实际等效电阻比之前的公式(3.38)计算的小。

#### 4.5.3 负载对输入阻抗的影响

通常共源 LNA 采用共源共栅结构，即在共源 MOS 管之上级联一个共栅 MOS 管，以完成输入与输出的隔离。这一结构首先是为了缓和密勒效应而使用的。然而，除了密勒效应，还有一类机制也要求在输入与输出之间进行隔离。这就是由负载引起的输入端的等效负电阻<sup>[4]</sup>。如图 4.27 所示，此时输入阻抗如式(4.12)所示。在负载可与  $r_0$  相比时，则输入的等效电阻会大幅度减小，恶化阻抗匹配。采用共栅级联 MOS 管可以在一定程度上减轻由大的负载引起的输入端的等效负电阻。

普通 MOSFET 包括的寄生元件主要包括：栅电阻  $R_g$ 、栅和漏之间、以及栅和衬底之间的交叠电容  $C_{gs0}$ 、 $C_{gd0}$ 、 $C_{pb0}$ ，源端串联电阻  $R_s$ ，漏端串联电阻  $R_d$ ，源、漏和衬底之间的 PN 结，衬底电阻网络。这些参数对器件的高频特性起着重要作用。 $C_{gd}$  在强反型的情况下因沟道的屏蔽作用可以忽略。在实际 CMOS 工艺中，如 Chartered 0.18 $\mu\text{m}$  标准 CMOS 工艺， $C_{ds}$ 、 $C_{sb}$  很小，一般只有几十 fF，所以，通过  $C_{ds}$ 、 $C_{sb}$  耦合到输入端的噪声很小，可以忽略。

$$Z_{in} = \frac{1}{sC_p} + sL + \frac{g_m L}{C_p} \cdot \frac{r_0}{r_0 + Z_L + sL} \quad (4.12)$$

图 4.27 接负载的共源 MOS

Fig. 4.27 Common source with load

#### 4.5.4 本章小节

本章根据第三章的几种低噪声放大器拓扑结构，比较了它们的优缺点，得出源极负反馈应用广泛的结论。针对源极负反馈讨论了几种匹配方法，推导了其最优噪声阻抗，输入阻抗公式，对比四种优化技术如表 4.7 所示。运用 PCSNIM 方法设计了一个低噪声

放大器，并且在通过改变电路结构，使得线性度有很大提高。通过设计 JAZZ 0.35 $\mu$ m 的差分低噪放，比较了单端与双端低噪放，比较了两种工艺的不同，通过实验数据说明两种流行工艺的影响。

分析了寄生效应的影响，这些寄生效应对设计仿真中的影响以及克服方法。

结合版图设计的一些经验，初步设计了 JAZZ 0.35 $\mu$ m BICMOS 的版图，对下一个阶段的工作，比如版图后仿真验证，作了一个简要的介绍。

## 5 低噪声放大器及混频器融合设计

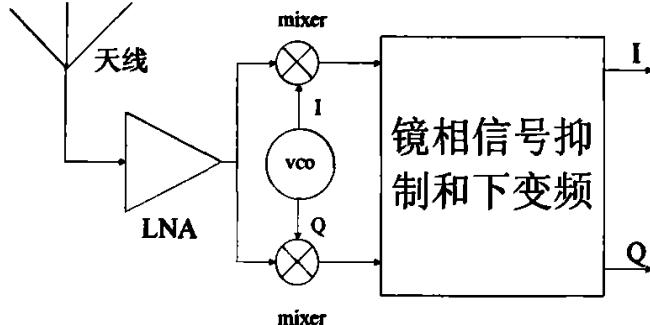

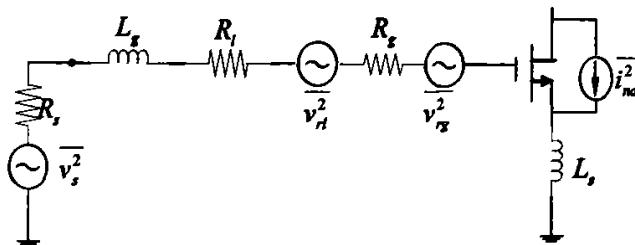

### 5.1 电路结构选择

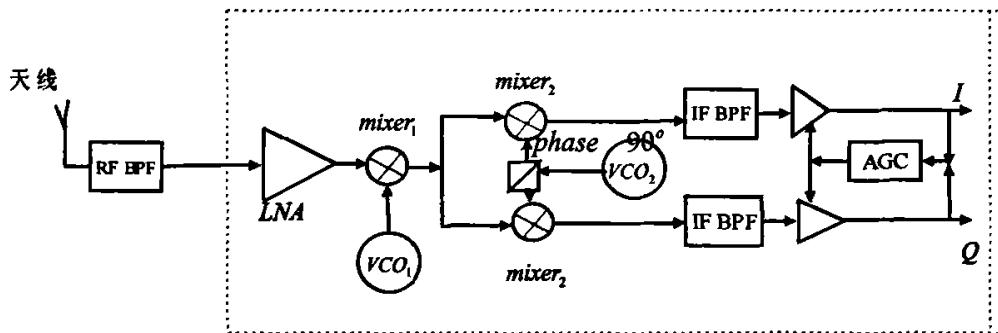

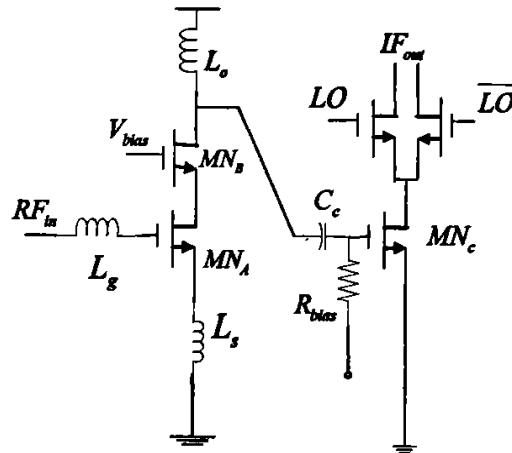

一般接收机第一级有源级为低噪声放大器，第二级为混频器。通过电容相连（如图5.1所示），单端LNA由源级负反馈构成，它的负载应当由负载电感电容调节到期望的频带。LNA输入MOS管将电压信号变成电流信号，然后通过负载电感又变成电压，给下一级混频器输入。这个电压驱动混频器的跨导，再一次变成电流。最后，通过开关级又将其变成电压输出。

图 5.1 传统低噪声放大器与混频器的级联

Fig. 5.1 Conventional LNA and mixer cascaded

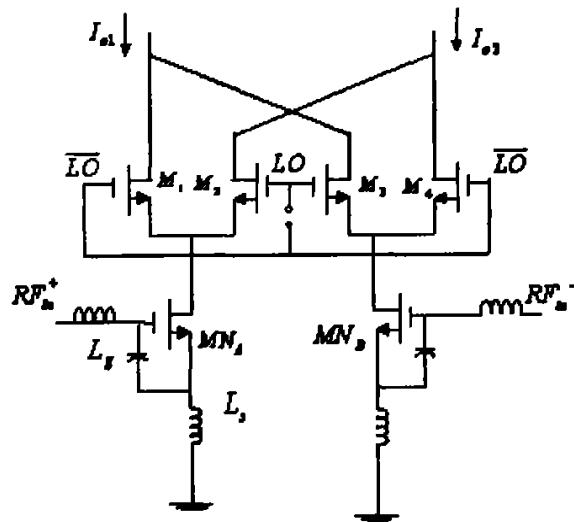

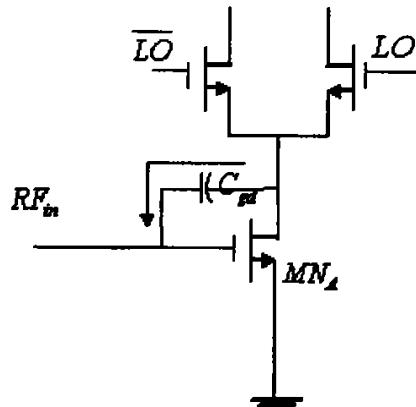

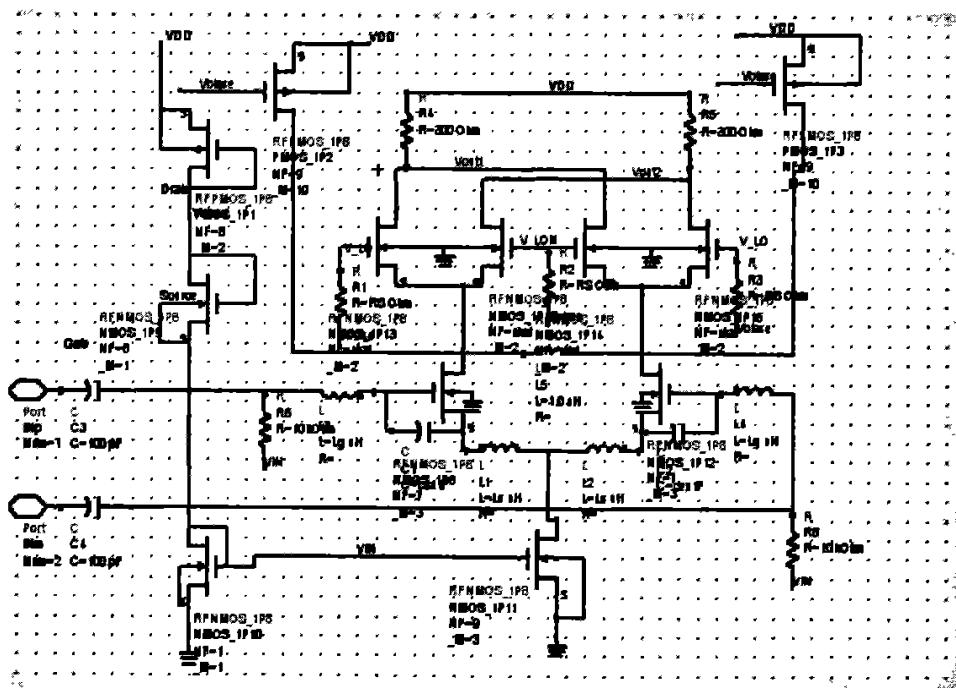

大信号可能通过信道进入LNA，这样可以使得LNA或mixer输入级有可能进入三极管区。从而使得混频器压缩。把LNA与mixer由电压相互连接的方式变成由电流方式的连接。这样就是低噪声放大器与混频器的融合设计，即低噪声混频器。这个电路的工作过程与混频器相同是：在图5.2中，本振信号假设足够强，使得上面的晶体管M1~M4都近似为理想开关对。这些开关对在本振信号控制下，将跨导级产生的电流周期性地由一边转换到另一边。差分对MN<sub>A</sub>~MN<sub>B</sub>（双平衡混频器）构成混频器的跨导级，将输入射频电压信号转换为电流，送入开关对的共源节点。再由开关选择输出哪边信号到输出端，同时完成信号的变频，并且低噪声混频器输入端电阻匹配到50Ω。

另一个重要的问题就是隔离度，在传统的LNA与mixer中，混频器输入级与低噪声放大器cascode级可以有效隔离，相比而言，现在的结构中不能有效的隔离本振信号以及

输入信号，那么本振信号可以通过低噪声放大器到天线，这样就会有一个很大的干扰。而本文接收机结构很好地解决了这个问题，采用双变频零中频接收机结构。这样即便是有很大的本振信号漏到输入端，也会通过第一级滤波器滤掉。而且，本文在电路结构上选择开关对共源节点谐振的方法使得线性度提高以及隔离度增加。

图 5.2 设计简单原理图

Fig. 5.2 Simplified schematic

此外，在这个电路中，两个混频器的管子都连在LNA的漏端，对于大信号，共源上的电压随着两个中的最高栅电压变化，出现在输入端的栅极形成了一个共模信号<sup>[40]</sup>，如图5.3所示。所以，需要采用有尾电流的方式来消除共模信号。

本文采用电路结构，如图5.4所示。在低功耗、低噪声的要求下，实现信号的混频。这个电路的线性度主要限制在两点：输入端MOS管的过驱电压以及输出电阻大小。为了减小开关对共源节点处寄生电容对三阶交调点的影响，可以在共源节点并联一个电感到地。该电感与共源节点寄生电容在 $2f_{LO}$ 处谐振，使得开关对的共源节点在 $2f_{LO}$ 频率处呈现为一个低阻抗，补充共源节点寄生电容充放电所需要的电流，减小开关对引入的三阶交调积和二阶交调积。

根据要求换算出对驱动级噪声系数，跨导以及线性度的指标。在驱动级和负载都确定的情况下，通过仿真来确定最优的开关对晶体管的尺寸，偏置以及本振信号幅度。在这个过程中，开关对晶体管的偏置电压要设置合适，避免驱动级中的晶体管工作时离开

饱和区，混频器偏置电流和负载阻抗也不能太大，避免开关对中的晶体管导通时离开饱和区。

图5.3 差分对干扰信号

Fig. 5.3 Two differential pairs including offsets

图 5.4 低噪声放大器和混频器融合设计原理图

Fig. 5.4 Merged LNA and mixer schematic

## 5.2 电路优化设计

### 5.2.1 增益部分设计

把 MOS 管栅极的宽度  $W$  增大, 栅极的长度  $L$  减小都可得到大的混频增益。增加电流也是提高增益的一个方法。但是此电路的设计并不是一般的混频器的设计, 而是要考虑到线性度与噪声之间的折中, LNA 晶体管宽度设计要兼顾动态范围以及噪声。并不像仅仅设计 LNA 时, 输入管只关注于噪声, 使得特征频率越大越好。所以设计这种融合电路的时候并不是像单纯设计 LNA 与 mixer 电路的输入级。

### 5.2.2 开关部分设计

本振信号过零处斜率越大, 噪声越小, 线性度越好。开关对转换时间反比于本振信号幅度, 正比于平衡对的过驱电压。当一对开关管工作在导通状态时, 我们希望另外一对开关管完全截至。如果两对开关管在同一时间都有电流流过, 就会产生噪声。

### 5.2.3 输出负载设计

混频器可以采取三种负载形式: 电阻作负载、晶体管作负载和 LC 并联谐振电路作负载, 电阻作负载比较简单, 它不会引入非线性, 而且具有很宽的带宽, 是混频器中最常用的负载形式, 但电阻上会引入直流压降, 为了不使开关对和驱动级中的晶体管离开饱和区, 电阻的阻值不能太大。另外在负载上加入一个并联电容作为低通滤波器。增大负载电阻  $R_L$  值可以增加混频器的变频增益, 但是如果电阻  $R_L$  值过大, 使得在凡两端的电压降过大, 使得混频器的净空 (headroom) 电压减小, 线性度变差, 所以在设计时电阻  $R_L$  值需要适当的考虑。正交解调器中的混频器为下变频器, 输出的中频信号的带宽为 25MHz, 在设计时可以在电阻两端并联一个电容, 形成一阶的低通滤波器滤除泄漏到输出端的 LO 和 RF 的高频信号。在设计中  $R_L$  取值大约为几百欧姆,  $C_L$  的取值约为几个 pF, 所以得到的带宽大概为几百 MHz, 完全可以滤除输出端的 LO 和 RF 高频信号, 至于混频器产生的一些互调低频信号, 可由片外的低通滤波器完成滤波。

### 5.2.4 设计步骤

这与混频器的设计不一样的是: 由于混频器一般的噪声很大, 所以才要使得 LNA 作为处理信号的第一阶, 即 LNA 的最大作用就是做到最小的噪声并且功耗尽可能的低 (在系统中占有的功耗最小)。而 mixer 既要处理信号也要使得处理后的信号保真, 主要作用就是将两个信号混频, 并且线性度要做到不使得输入信号遭到破坏。所以可以看出在混频器的跨导级不是专注于噪声最小 (这与 LNA 有大的区别), mixer 的跨导级的偏置

使得开关级速度和线性度最好(有时候根据开关级来定输入级的偏置)，然后再在偏置中找到使得噪声最小的  $W$ 。

第一步，选择  $W_{opt}$ ，首先选择偏置，由  $IIP3$  可知大于  $0.6V$  就可以使得线性度最大。而由第四章可知，选择  $0.7V$  使得噪声最小，所以偏置电压为  $0.7V$ 。

第二步，在一定的功耗  $4mA \times 1.8$  以及跨导(满足噪声的计算)下，设计管子的尺寸。根据噪声要求，其中选择  $M$  为： $M=4$ 。

第三步，选择  $L_s$  和电容  $C_{ex}$ 。选择  $L_s$  的时候要注意： $L_s$  太大使得噪声增加，并且使得增益下降。但是可以提高线性度。由于我们的偏置选取是根据线性度为主要目标。所以在  $L_s$  的选择上一定要注意。由于差分输入，使得寄生电感不会影响输入匹配。由于总体的增益和  $S21$  的关系不大，所以可以不使得其值大于 10。由于增加了  $C_{ex}$  使得驱动级的  $W$  下降，在节省功耗的情况下，使得电路的噪声改善，并且在低功耗的情况下使得线性度增加。可见  $C_{ex}$  的作用使得在特定的功耗下，使得线性度与噪声都得到满足。把  $VDS$  设置成 0.7 可以避免在交流的时候，当  $LO$  有大的负摆动时，使得驱动级仍在饱和区。

第四步，设计电路的偏置点，设计中尽量使得开关级的  $VGS=Vth$ ，这样便可以使得开关级趋于理想状态。等到设计好偏置点后，考察共模输入范围与差模导致的输出摆幅。

经过计算，可以知道范围，通常  $LO$  的幅度不可能大于 0.3，所以符合条件。

接下来做  $LO$  口和输出口的匹配。射频电路的端口必须匹配，设计匹配网络有两种方法，一是采用解析方法求出元件的值；二是利用  $Smith$  圆图作为图解设计工具。第一种方法可以得到非常精确的结果，并适合于计算机仿真。然而，由于第二种方法不需要复杂的计算，且更加直观和容易验证，对于初步设计也比较省时。

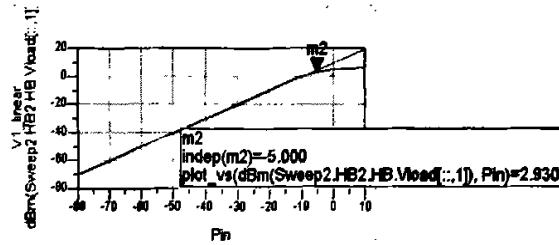

### 5.2.5 模拟结果以及分析

#### (1) 噪声

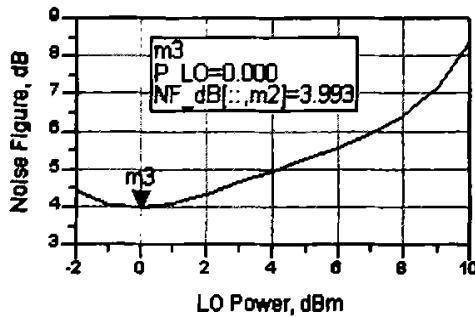

根据第三章关于混频器的噪声论述以及低噪声放大器的噪声详细分析，可知，混频器中噪声的改善，除了增大电路中的电流以外，还有一种方法就是提高本振信号的幅度。这两种方法都是以功耗为代价的。本文采用  $2.8GHz$  的本振频率，即中频频率(噪声频率)为  $400MHz$ 。

图 5.5 所示，噪声与本振的关系，可以看出本振幅度越大，噪声越低，但是如果过大使得管子截至或者饱和，那么噪声就会突然增大。本振的幅度为了不让本振电路功耗过大，选择  $0dBm$  作为最佳本振功耗。

图 5.6 所示, 本振为 0dBm, 并在一定的中频范围内, 噪声与增益的关系。可以看出, 噪声在 400MHz 最低, 这是由于输入端与输出端匹配的原因, 使得在这个输出频率处噪声最低, 增益最大。图 5.7 所示, 表示输入端与本振端的匹配, 都达到了要求。而本振端的匹配程度要求不严格, 在实际中, 由于只要求电压匹配就可以, 而不需要功率匹配。

图 5.5 噪声与本振的关系

Fig. 5.5 Noise figure versus LO

图 5.6 噪声与增益的关系

Fig. 5.6 Noise figure versus gain

## (2) 线性度

线性度也是表征混频器的一个重要指标,  $P_{-1dB}$  越大, 表明处理大信号能力就越强。IIP<sub>3</sub> 越大, 就表明抗干扰能力越强。

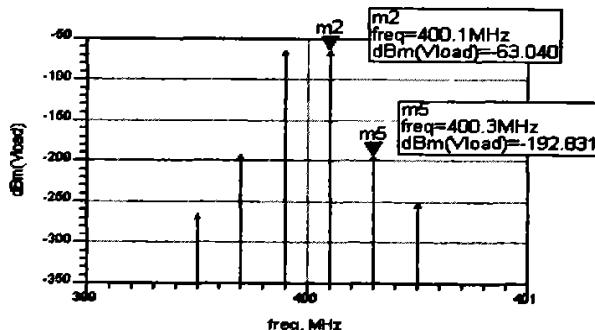

如图 5.8 所示, 根据输出功率谱计算三阶交调, 根据公式(4.11), 得到本设计三阶交调点为:  $-4.5\text{dBm}$ 。

$$IIP_3 = \frac{P_{Fund} - P_{IMD}}{2} + P_{in} \quad (4.11)$$

图 5.7 输入端及本振端的匹配

Fig. 5.7 The match of signal input and LO input

图 5.8  $IIP_3$  的仿真结果

Fig. 5.8  $IIP_3$  simulation result

### (3) 增益与隔离度

混频器的增益与低噪声放大器的增益概念不一样, 低噪声放大器是把一个固定的中心频率放大, 增益可以用 S 参数直接仿真, 而混频器的增益是从一个频率变换到另一个频率, 是表示中频输出及射频信号输入的比值, 不能用 S 参数来表示。线性度与增益是矛盾参数, 一般的混频器注重线性度, 而本文中是将低噪声放大器与混频器融合, 所以在线性度与增益之间的选择, 更偏向于增益的要求, 增益指标如图 5.6 所示。

还有一个重要的指标，就是隔离度的要求。本文的隔离度仿真指标如图 5.9 所示。如果缺乏隔离度，那么可能引起中频放大器的过载以及本振信号通过天线辐射出去。本文采用的 Gilbert 混频器有较好的隔离度。

| PORT-TO-PORT ISOLATION         |                               |                                   |

|--------------------------------|-------------------------------|-----------------------------------|

| LO to Output<br>isolation (dB) | LO to Input<br>isolation (dB) | Input to Output<br>isolation (dB) |

| P_LO2F<br>87.1                 | P_LO2RF<br>95.1               | P_RF2F<br>44.4                    |

图 5.9 隔离度仿真

Fig. 5.9 Isolation simulation

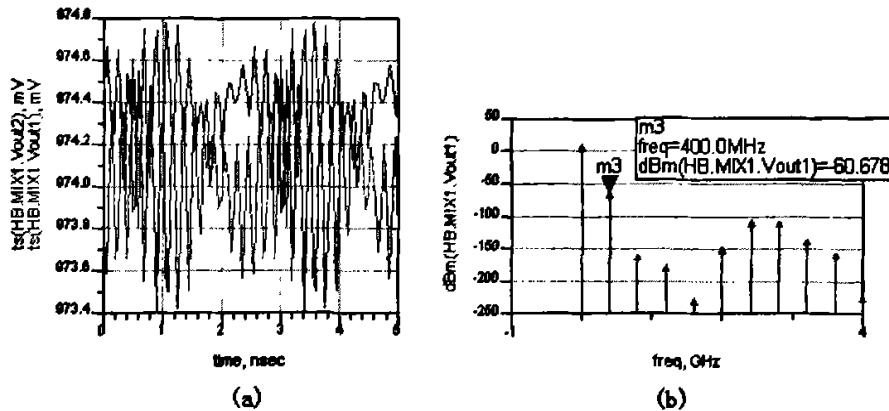

#### (4) 输出端口瞬态

输出端口的波形还有很多频率分量，由于隔离度的原因，还可能存在射频输入波。图 5.10 为中频输出口的谐波以及时域波形。

尽管采用对称设计也不可能使得两边的参数完全一致，在原理图设计的时候就要考虑到这一点，如图 5.10(a) 所示，两个波形出现了相位差。由图 5.10(b) 可知，输出中含有许多谐波以及射频波分量，由于乘法器是间接地产生混频，所以这些非线性通常会产生许多不希望的频谱分量，还有就是隔离度产生的问题。

图 5.10 输出端时域及频域分析

Fig. 5.10 The time-domain and frequency-domain analysis

#### (5) 设计指标对比

表 5.1 混频器指标对比

Tab. 5.1 Comparison of mixer parameters

| 文献   | 工艺(CMOS $\mu\text{m}$ ) | Pc(mW) | NF(dB) | 增益(dB) | IIP <sub>3</sub> (dBm) | 频率(GHz) |

|------|-------------------------|--------|--------|--------|------------------------|---------|

| [40] | 0.35                    | 21.6   | 3.4    | 23     | -1.5                   | 2.1     |

| [41] | 0.5                     | 10     | 11.5   | -1.5   | 11                     | 1.96    |

| [42] | 0.35                    | 14     | 11     | 17     | 5.5                    | 1.57    |

| [43] | 0.13                    | 1.6    | 14.8   | 5.4    | -2.8                   | 2.4     |

| [44] | 0.18                    | 23.1   | 18.5   | 18     | 11.5                   | 1.9     |

| 本文   | 0.18                    | 7.2    | 3.99   | 6.64   | -4.5                   | 2.4     |

## 结 论

随着射频芯片价格不断降低, 无线局域网得到了广泛的应用。目前, 射频收发采用 SiGe 工艺实现, 而基带处理采用 CMOS 工艺实现, 不同的工艺无疑提高了产品成本, 并且无法实现单片集成的收发机。无线局域网大规模应用要求芯片具有低成本、高集成度的特点。射频收发采用 CMOS 工艺实现可以射频前端和基带处理部分集成在一块芯片上, 将 CMOS 工艺应用于零中频接收机结构可以实现单片集成的收发机, 这必将推进整个无线局域网市场的发展。研究采用 CMOS 工艺来实现零中频接收机芯片可以提高我国在这一方面的研究水平, 其研制成功将产生可观的经济效益。

本文采用二次变频零中频接收机结构, 结合 WLAN802.11b 的应用背景, 通过系统的链路分析确定了低噪放等模块的设计指标。将 Chartered 0.18 $\mu$ m CMOS 工艺设计的单端低噪声放大器与 JAZZ 0.35 $\mu$ m BICMOS 工艺设计的差分低噪声放大器进行对比研究, 证明了 CMOS 工艺可以实现设计模块的设计。深入研究两种匹配方法, 通过理论计算以及仿真实现得出: 在相同功耗的前提下, PCSINM 技术比优化技术的噪声性能高 0.4dB, 分析可知, PCSINM 技术可以有效的将寄生电容充当额外电容的作用, 减少了寄生效应, 同时推导 PCSINM 技术中外加电容对线性度的影响。通过增加 PMOS 使电路的三阶跨导降低, 改善线性度:  $P_{1dB}$  提高 9dB, 噪声恶化了 0.4dB。实现功耗仅为 4.5mW, 噪声仅为 1.03dB 的低噪声放大器, 而增益与线性度指标也满足要求。从而, 证明了 PCSINM 技术低功耗设计的可行性。

通过低噪声放大器的研究, 指出实现低功耗射频模块的设计可以通过输入级匹配的方法来解决。将此种方法应用到二次变频零中频接收机的低噪声放大器与第一级混频器的混合中, 仿真实现了低功耗 7.2mW, 低噪声 3.99dB 的融合模块设计。

低噪声放大器及混频器是接收机的关键模块设计, 但整个系统链路还需要本振, 缓冲器以及中频放大器等模块的设计, 本文的接收机链路指标分配为以后的其他射频模块设计提供了参考, 继而可以对整个链路进行分析实现。

本论文的研究结果证明了用 CMOS 工艺实现射频集成电路的可行性, 为进一步实现低功耗射频单芯片通信电子系统提供了技术积累。

## 参 考 文 献

- [1] 张国艳, 黄如, 张兴等. CMOS 射频集成电路的研究进展. *微电子学*, 2004, 34(4):377-383.

- [2] Razavi B. A 60GHz CMOS receiver front-end. *IEEE Journal of Solid State Circuits*, 2006, 41(1):17-22.

- [3] Geier J. *无线局域网*. 王群译. 北京:人民邮电出版社, 2001.

- [4] Thomas H L. *The Design of CMOS Radio Frequency Integrated Circuits*. California: Stanford University, 1998

- [5] Gerson A S. *Low-power HF microelectronics:a unified approach*. United Kingdom: The Institution of Electrical Engineers, 1996.

- [6] 陈邦媛. *射频通信电路*. 北京:科学出版社, 2002.

- [7] Wambacq P, Willy M C. *Distortion Analysis of Analog Integrated Circuits*. California: KLUWER ACADEMIC PUBLISHERS, 1998.

- [8] Paul R G, Robert G M. *Analysis and Design of Analog Integrated Circuits*, 3<sup>rd</sup> edition. New York: Hardcover, 1993.

- [9] Bautista E E, Bastani B, Heck J. A high IIP2 downconversion mixer using dynamic matching. *IEEE Journal of Solid-State Circuits*, 2000, 35(12):1934-1941.

- [10] 徐建, 孙大有. 无线接收机RF前端研究. *东南大学学报*, 2000, 30(3):136-141.

- [11] Long J R, Copeland M A. The Modeling, Characterization, and Design of Monolithic Inductors for Silicon RF IC's. *IEEE Journal of Solid-State Circuits*, 1997, 32(3):357-369.

- [12] 陈继新, 洪伟. 800MHZ CMOS 低噪声放大器的设计. *微波学报*, 2005, 21(B04):107-111.

- [13] Morifuji E, Momose H S, Ohquro T et al. Future perspective and scaling down roadmap for RF CMOS. *VLSI Technology, Symposium on Digest of Technical Papers*, Kyoto, 1999:163-164.

- [14] Huang Q, Piazza F, Orsatti P et al. The Impact of Scaling Down to Deep Submicron on CMOS RF Circuits. *IEEE Journal of Solid-State Circuits*, 1998, 33(7):1023-1036.

- [15] Keng Leong Fong. High-frequency analysis of linearity improvement technique of common-emitter transconductance stage using a low-frequency-trap network. *IEEE Journal of Solid-State Circuits*, 2000, 35(8):1249-1252.

- [16] Theerachet S, Thomas H L. RF Linearity of Short-Channel MOSFETs. *First International Workshop on Design of Mixed-Mode Integrated Circuits and Applications*, 1997:81-84.

- [17] Chunbing Guo, Chi-Wa Lo, Yu-Wing Choi et al. A fully integrated 900-MHz CMOS wireless receiver with on-chip RF and IF filters and 79-dB image rejection. *IEEE Journal of Solid-State Circuits*, 2002, 37:1084-1089.

- [18] Young-Gi Kim, Shin-Young Yoon, Hyuk Kim. A dual band SiGe MMIC LNA and mixer with ground shield for WCDMA and CDMA applications. *IEEE Radio and Wireless Conference*, 2001:41-44.

- [19] Dawkins M, Burdett A P, Cowley N. A single-chip tuner for DVB-T. *IEEE Journal of Solid-State Circuits*, 2003, 38(8):1307-1317.

- [20] Ding Y W, Harjani R. A +18 dBm IIP3 LNA in 0.35um CMOS. *IEEE Solid-State Circuits Conf*, 2001:62-63.

- [21] Bonkee K, Jin S K, Kwyro L. A New Linearization Technique for MOS RF Amplifier Using Multiple Gated Transistors. *IEEE microwave and guided wave letters*, 2000, 10(9):371-373.

- [22] 曹克, 杨中华, 汪蕙. 高线性低电压低噪声放大器设计. *半导体学报*, 2004, 25(11):1364-1369.

- [23] Tae S K. Post Linearization of Cascode CMOS Low Noise Amplifier Using Folded PMOS IMD Sinker. *IEEE Microwave and Wireless Components Letters*, 2006, 16(4):182-184.

- [24] Terrovitis M T, Meyer R G. Noise in current-commutating CMOS mixers. *IEEE Journal of Solid-State Circuits*, 1999, 34(6):772-783.

- [25] Klumperink E A M, Louwsma S M, Wienk G J M et al. A CMOS switched transconductor mixer. *IEEE Journal of Solid-state circuits*, 2004, 39(8):1231-1240.

- [26] Terrovitis M T, Meyer R G. Noise in Current-Commutating CMOS Mixers. *IEEE Journal of Solid-State Circuits*, 1999, 34(6):772-783.

- [27] Haus H A, Atkinson W R, Branch G M et al. Representation of Noise in Linear Twoports. *Proceedings of the IRE*, 1960, 48(1):69-74.

- [28] Voinigescu S P, Maliepaard M C, Showell J L et al. A Scalable High-Frequency Noise Model for Bipolar Transistors with Application Optimal Transistor Sizing for Low-Noise Amplifier Design. *IEEE Journal of Solid-State Circuits*, 1997, 32(9):1430~1439.

- [29] Andreani P, Sjoland H. Noise Optimization of an Inductively Degenerated CMOS Low Noise Amplifier. *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, 2001, 48(9):835~841.

- [30] Tsukahara Y, Chaki S, Y Sasaki et al. A C-band 4-stage low Noise Miniaturized Amplifier using Lumped Elements. *IEEE MTT-S International Microwave SymposiumDigest*, Orlando, 1995:1125~1128.

- [31] Heaney E, McGrath F, O' Sullivan P et al. Ultra Low Power Low Noise Amplifiers for Wireless Communications. *Technical Digest-GaAs IC Symposium (Gallium Arsenide Integrated Circuit)*, San Jose, 1998:49~51.

- [32] S S. Taylor On the optimum width of GaAs MESFETs for Low Noise Amplifiers. *IEEE Radio Frequency Integrated Circuits Symposium*, Baltimore, 1998:139~142.

- [33] Mahdavi S, Abidi A A. Fully Integrated 2.2-mW CMOS Front End for a 900-MHz Wireless Receiver. *IEEE Journal of Solid-State Circuits*, 2002, 37(5):662-669.

- [34] 孔晓明, 黄风义, 王志功. 低功耗2.4GHz 0.18um CMOS 全集成低噪声放大器设计. *电气电子教学学报*, 2006, 28(1):54-56.

- [35] Huang J C, Ro-Min Weng, Cheng-Chih Chang et al. A 2V 2.4GHz Fully Integrated CMOS LNA. *IEEE Circuits and Systems*, 2001, 4(4):466~469.

- [36] Allstot D J, Xiaoyong Li, Shekhar S. Design Considerations for CMOS Low-Noise Amplifier. IEEE Radio Frequency Integrated Circuits Symposium, Fort Worth, Texas, 2004: 97~10.

- [37] Nguyen T K, Oh N J, Cha C Y et al. Image-Rejection CMOS Low-Noise Amplifier Design Optimization Techniques. IEEE Trans Microwave Theory and Techniques, 2005 : 538~547.

- [38] Baki R A, Tsang T K K, El-Gamal M N. Distortion in RF CMOS Short Channel Low Noise Amplifiers. IEEE Transactions on Microwave Theory and Techniques, 2006, 54(1) : 46~56.

- [39] Sivonen P, Parssinen A. Analysis and Optimization of Packaged Inductively Degenerated Common-Source Low-Noise Amplifiers With ESD Protection. IEEE Transactions on microwave theory and techniques, 2005, 53(4) : 1304~1313.

- [40] Sjoland H, Karimi-Sanjaani A, Abidi A A. A Merged CMOS LNA and Mixer for a WCDMA Receiver. IEEE Journal of Solid-State Circuits, 2003, 38(6) : 1045~1050.

- [41] Allam E A, Nisbet J J, Maliepaard M C. Low-Voltage 1.9-GHZ Front-End Receiver in 0.5  $\mu$ m CMOS Technology. IEEE Journal of Solid-State Circuits, 2001, 36(10) : 1434~1443.

- [42] Svelto F, Deantonio S, Montagna G et al. Implementation of a CMOS LNA Plus Mixer for GPS Applications with No External Components. IEEE Transactions on VLSI Systems, 2001, 9(1) : 100~104.

- [43] Hermann C, Tiebout M, Klar H. A 0.6V 1.6mW transformer-based 2.5GHz downconversion mixer with +5.4dB gain and -2.8dBm IIP3 in 0.13- $\mu$ m CMOS. IEEE Transactions on Microwave Theory and Techniques, 2005, 53(2) : 488~495.

- [44] 褚方青, 李巍, 苏彦锋等. 一种新型的基于GSM1900标准的1.9 GHz混频器. 半导体学报, 2006, 27(3) : 467~472.

## 攻读硕士学位期间发表学术论文情况

- [1] 樊君, 解永平, 戴由旺.《高性能 CMOS 低噪声放大器的设计》. 仪器仪表学报增刊, 2007, 28(4): 457-458(内容与论文第四章相对应)

## 致 谢

本论文的整个研究过程中，我始终得到了许多老师和同学的关心和帮助，使我得以不断的克服困难，解决问题，顺利地完成毕业设计。特别是在导师解水平副教授的悉心指导下完成的，在论文的选题、研究方法和具体实现等方面，导师都给予了宝贵的建议和指导，在关键时刻总是启发和开拓我的思路，可以说论文中的每一点都凝聚着老师的心血。导师严谨的治学态度在我心中留下了深刻的印象，并使我受益终生。当我的科研工作遇到困难的时候，解老师总是能够高屋建瓴的指出问题的症结所在。在研究生阶段，解老师从生活、学习等多方面都给予了我无微不至的关心和帮助，使我在学习、科研动手能力上都有很大的提高，为今后的学习和工作打好了坚实的基础。在此我谨向解水平老师表示衷心的感谢和深深的敬意。

感谢电信学院所有关心和帮助过我的老师们，你们的教诲使我终生难忘！

感谢我们330实验室的各位兄弟姐妹们，陪伴着我的整个研究生阶段，大家众志成城，团结一心。无论在生活方面还是学习方面，大家总是能够无私地向需要的同学提供力所能及的帮助，在此，我对他们表示真诚的祝福与感谢。

最后，我特别要感谢我的家人，尤其是我的父母，是他们在生活以及精神上给了我极大的支持，为我创造了良好的学习条件，是他们平时无微不至的关怀，使我更加有动力与勇气面对一次又一次的挑战，在此真诚地祝福他们身体健康，幸福美满。