仿真结果吻合了理论的分析。为了进一步研究电路的特性，还做了一个实验电路验证了仿真的结果，给出了实验的关键波形，对实验数据进行处理，分析了电流的效率、储能电容电压和谐波含量等等。

**关键词：**单级变换器；直接功率传递；功率因数校正；并联

## Abstract

Two-stage structure is widely used in conventional AC/DC converters to achieve high power factor and regulated output voltage. These converters are cascaded with AC/DC power factor correction stage and DC/DC output voltage regulating stage. The first stage is used to regulate the input current waveform and unity power factor is obtained. The second stage is used to regulate the output voltage tightly to center value with low ripple. Since input current and output voltage are regulated independently, two-stage converters have good performance of unity power factor and tightly regulated output voltage. On the other hand, these converters have complex structure and high cost and the efficiency is low in theory because the input power is processed twice to reach the output.

Single-stage PFC AC/DC converter combines the two stages into one stage. The function of power factor correction is automatically achieved with the converter working in discontinuous-current-mode and output voltage is regulated only. The cost is lowered down because the power stage and the control circuit are simple.

High DC bus voltage stress is a serious problem in single-stage PFC AC/DC converters. The structure needs to be rebuilt to lower down the devices' voltage and current stress. In general terms, the imbalance between input and output power causes the high voltage of bulk capacitor of single-stage converter. So the power flow of the converter needs to be optimized with the concept of direct power transfer (DPT). Based on DPT concept, most of the input power is processed once to reach the output and only a few part of the input energy need to be stored in the bulk capacitor. The optimized power flow insures the problem of high voltage of the bulk capacitor. Three typical single-stage PFC AC/DC converter topologies based on DPT concept are given. They are Flyback-Boost converter, single-stage parallel PFC converter and DC bus voltage feedback single-stage converter. The performance of these converters is analyzed and compared. Theory analysis and experiment show that these converters can lower down the bulk capacitor's voltage and the devices' voltage current stress effectively.

Single-stage parallel bi-flyback AC/DC converter is selected to carry on a deep research. The main content is including three parts: theory analysis; circuit design process; simulation and experiment.

Firstly, the structure and working principle of single-stage parallel bi-flyback AC/DC converter are introduced. The design guidelines and key parameters are analyzed. Extended topologies based on DPT concept are proposed. According the problems of the converter, improving advice is introduced.

Then design process including the relationship of parameters, control and drive circuit, transformer, etc. is given.

At last, with the simulation soft of SIMetrix/SIMPLIS, waveforms of rectified line voltage, line current, output voltage of error amplifier, current on the two switches, voltage on bulk capacitor are obtained. The effect of bulk capacitor value and inductors ratio is analyzed with simulation. The results show coincidence between theory and simulation. A real circuit is built to verify theory and simulation and some key waveforms are given. Efficiency, capacitor voltage and harmonic content are analized.

**Key words:** single-stage converter; direct power transfer; power factor correction; parallel;

# 华南理工大学

## 学位论文原创性声明

本人郑重声明：所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。除了文中特别加以标注引用的内容外，本论文不包含任何其他个人或集体已经发表或撰写的成果作品。对本文的研究做出重要贡献的个人和集体，均已在文中以明确方式标明。本人完全意识到本声明的法律后果由本人承担。

作者签名：刘小光 日期：2005年6月9日

## 学位论文版权使用授权书

本学位论文作者完全了解学校有关保留、使用学位论文的规定，同意学校保留并向国家有关部门或机构送交论文的复印件和电子版，允许论文被查阅和借阅。本人授权华南理工大学可以将本学位论文的全部或部分内容编入有关数据库进行检索，可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

保密□，在\_\_\_\_年解密后适用本授权书。

本学位论文属于

不保密√。

(请在以上相应方框内打“√”)

作者签名：刘小光 日期：2005年6月9日

导师签名： 日期：2005年6月9日

# 第一章 绪论

在 20 世纪 80 年代中后期, 开关电源功率因数校正 (Power Factor Correction) 技术引起了国内外许多学者的重视。本章介绍功率因数校正技术的产生背景、发展情况和研究热点。

## 1.1 电流谐波的产生、危害和功率因数校正技术

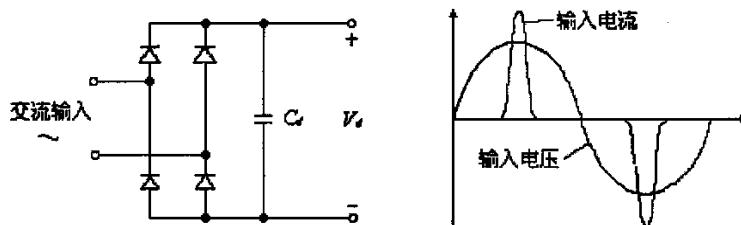

在采用交流电网作为工作电源的用电设备中, 直流开关电源是必不可少的部分。一般开关电源的前级为一个简单的 AC/DC 变换器, 由普通二极管整流桥实现, 其输出是不可调节的直流电压  $V_d$ , 一个大电容  $C_d$  用来滤除低频纹波, 从而把交流电整为直流电  $V_d$ 。使用二极管整流桥作为电网与用电设备的接口时, 由于二极管导通角很小, 当交流电压大于电容电压时, 此整流电路才能够从电网中抽取能量, 因此电网仅在每个工频周期的一小部分时间里(即正弦电压的峰值附近)给负载提供能量。其典型电路及输入电流波形如图 1-1 所示。

图 1-1 简单的二极管单相整流电路及输入电流波形图

Fig.1-1 Typical rectifier circuit and input current waveform

这种非控整流使得输入电流波形发生严重畸变, 并呈脉冲状。这种呈尖峰状的非正弦电流包含丰富的高次谐波, 系统的功率因数很低, 如在中大型非控整流设备中, 输入电路的功率因数大致在 0.5~0.7 左右, 有的甚至更低。输入视在功率远大于有功功率。如把此部分的内阻抗等效为  $Z_s$ , 电流谐波越大, 即  $Z_s$  越大, 网侧电压的畸变就越明显, 这就是电流谐波产生的二次效应。

电流波形的畸变及因此产生的网侧电压波形的畸变还给系统本身和周围环境带来一系列的危害: 对电力系统产生污染, 电流谐波使得线路和配电变压器过热, 引起电网 LC 谐振, 或高次谐波电流流过电网的高压电容, 使之过流, 过热而损毁; 在三相线路中, 中线电流三次谐波的叠加会使得线路过流而发生故障; 对通信系统产生干扰, 还可引起仪器仪表和保护装置的误测量、误动作。这就是通常所说的“谐波污染”。

随着用电设备日益增多, 谐波污染问题引起了越来越广泛的关注。基于限制

电流波形畸变和谐波，使电磁环境更加干净的宗旨，一些世界性的学术组织提出了谐波限制标准，如 IEC555-2, IEEE519 等，对电力电子和电气设备的电流谐波进行限制。对于数量多而且分散的中小功率单相电源系统，最理想的方法是在电源内部采取功率因数校正(Power Factor Correction, 简称 PFC)电路，从根本上消除谐波源。在电源内部采取功率因数校正电路，从根本上消除谐波源的功率因数校正技术由此产生，采用现代高频功率变换技术的有源功率因数校正技术更是有效的手段。

功率因数校正技术对开关变换器的功率因数进行校正，不仅能够提高变换器功率因数，减小输入电流的谐波成分，而且减小了因谐波成分对电网以及通讯和自动化设备可能产生的干扰，同时增加了同样电流有效值下的输入功率，提高电源转化效率。因而研究功率因数校正技术对开关电源的发展具有重要的实际意义，因此功率因数校正在电力电子变换器中的意义愈来愈明显，已成为目前一个重要的研究方向。

## 1.2 PFC技术的发展

### 1.2.1 提高 AC/DC 变换器输入侧功率因数的主要思路

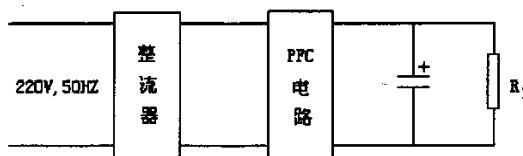

分析图 1-1 所示的电路可知，对于整流电路而言，由于人们想得到一个较为平滑的直流输出电压，所以采用电容滤波。正是整流二极管的非线性和电容的共同作用，使得输入电流发生了畸变。如果去掉输入滤波电容，则输入电流变为近似的正弦波，提高了输入侧的功率因数并减少了输入电流的谐波，但是整流电路的输出不再是一个平滑的直流输出电压，而变为脉动波。如果欲使输入电流为正弦波，且输出仍为平滑的直流输出，必须在整流电路和滤波电容之间插入一个电路，这个电路就是 PFC 电路，如图 1-2 所示。

图 1-2 含有 PFC 电路的 AC/DC 电路

Fig.1-2 AC/DC converter with PFC

### 1.2.2 PFC 技术的演变和分类

#### (1) 从无源功率因数校正到有源功率因数校正的演变

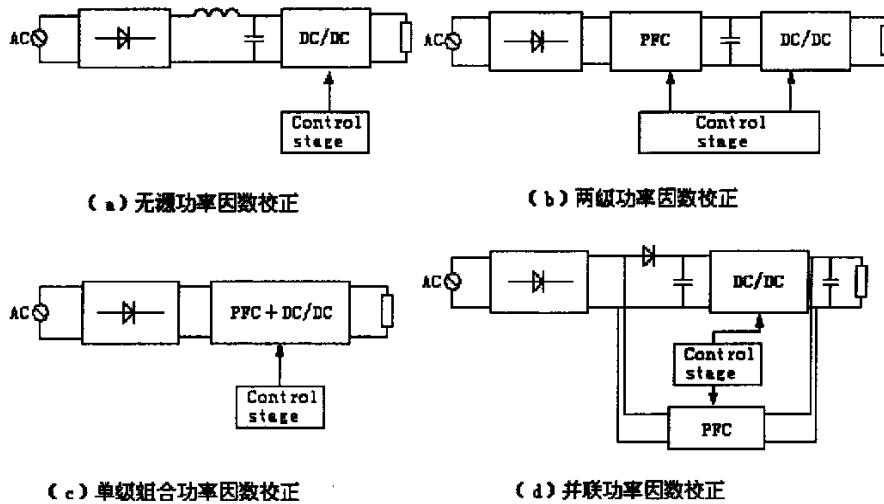

回顾 PFC 技术的发展历程，最早人们是采用电感器和电容器构成的无源网络进行功率因数校正，如图 1-3(a)所示。无源功率因数校正技术所需的滤波电容器和滤波电感器的取值较大，因此电路往往较笨重。无源 PFC 技术的主要优点是

设计简单、成本低、运行可靠；但是，无源滤波电感的体积大，而且难以得到很高的功率因数。在现代开关电源中，变换器向着高功率密度的方向发展，无源功率因数校正技术已经不能满足现代开关电源的技术要求。

20世纪80年代，现代有源功率因数校正技术应运而生。由于变换器工作在高频开关状态，这种有源功率因数校正技术具有体积小，重量轻，效率高，功率因数可接近1等优点。80年代的有源功率因数校正技术可以说是基于boost变换器功率因数校正的年代，在此期间的研究工作主要集中在对工作在连续导电模式（CCM）下的boost变换器的研究上，这类变换器的控制方式一般是基于所谓“乘法器”（Multiplier）的原理；连续导电模式下的功率校正技术可以获得很大的功率转换容量，但是对于大量应用的200W以下的中小功率容量的情形，却是非常不合适的，因为这种方式往往需要较复杂的控制方式和电路。80年代末提出了利用工作在不连续导电模式（DCM）下的变换器进行功率因数校正的技术，由于其输入电流自动跟踪输入电压，因而可实现接近1的功率因数。这种PFC技术在文献中称为自动功率因数校正，也称为电压跟随器（Voltage Follower）。这种有源功率因数校正技术因其控制简单（仅采用一个控制变量，即输出电压）而倍受青睐，但是一般不能应用于较大的功率变换中。

图 1-3 功率因数校正的电路结构

Fig.1-3 Circuit structure of power factor correction converter

- (a) Passive power factor correction;

- (b) Two-stage power factor correction;

- (c) Single-stage power factor correction;

- (d) Parallel power factor correction.

图 1-4 单相功率因数校正变换器的功率关系

Fig.1-4 Relationship between input and output power of single phase power factor correction converter

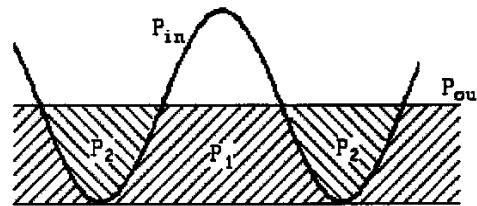

另一方面，假定可以获得单位功率因数，则变换器的输入功率和输出功率如图 1-4 所示。可见，在所有的 PFC DC/DC 变换器中，在半个工频半周期内瞬态输入功率是脉动的，而后接 DC/DC 变换器的输出功率是恒定的。因此，在任何 PFC 电路都必须有足够输出滤波电容存储半个工频半周期内不平衡的能量。这个大电容不仅导致 PFC 电路动态响应慢，而且产生了两倍工频的输出电压纹波。因此为了获得稳定的输出电压，传统的有源功率因数校正系统是如图 1-3(b)所示的 PFC+DC/DC 的变换器的两级级联结构。前一级 PFC 功能通常是基于“乘法器”原理工作于连续电流模式的 Boost 变换器。两级 PFC 方案具有优良的性能，输入电流的总谐波畸变 (THD) 一般小于 5%，功率因数可以到 0.99 或更高；由于前级储能电容电压  $V_B$  近似恒定，DC/DC 变换器可以得到优化；此外，由于  $V_B$  相对较高，对于一个给定的保持时间可采用较小的储能电容。但两级 PFC 方案输出功率需要经过两级处理，显然效率较低，同时也存在体积大，电路复杂、成本高等问题。这使得两级 PFC 方案不适用于低功率应用，如 200-300W 以下的功率范围。目前欧洲强制要求市场上出售的 75W 以上的电子设备必须满足 IEC1000-3-2 电流谐波标准限制，而且不久会改为对 50W 以上的电子设备强制执行。由于在低功率应用中采用两级方案的成本太高，在竞争日益激烈的环境下，许多厂商和科研机构都开始关注单级 PFC 技术，如图 1-3(c)所示。单级 PFC 变换器就是基于电压跟随器原理工作于不连续模式的变换器。单级组合 PFC 技术通过消除一些冗余元件，将级联的两个功率级的功率开关合并成一个功率开关，共用一套控制电路而得。单级 PFC 变换器的电路拓扑尽管简单，但与两级功率因数校正电路相比通常并不能获的更高的效率，同时大部分此类变换器只能工作在不连续导电模式 (DCM) 和通过变频控制，共用开关管增加了控制的困难。为了解决两级和单级 PFC AC/DC 变换器的缺点，一些新颖的功率因数校正原理及拓扑结构被提出来，例如图 1-3(d)所示的并联功率因数校正技术。在一个开关周期内，部分输入功率可通过一次变换到达输出，剩余输入功率需经两次变换，使输出电压得到快速与精确调节。这种电路的效率高于两级变换器和单级组合式变换器。

二十世纪 90 年代以来,一些新技术、新方法开始应用于有源功率因数校正变换器中。软开关技术和功率因数校正技术结合以提高变换器的性能。近年来,有关连续导电模式下功率因数校正的控制新方法的研究也有不少报道,主要有单周期 (One Cycle) 控制, 滑模 (Sliding Mode) 控制以及其他新控制方法。进入 21 世纪, 基于数字信号处理器的数字控制 PFC 开始研究, 并取得了一定成果[3~10]。

## (2) 有源功率因数校正技术的分类

从不同的角度, 功率因数校正技术有多种分类方法。从电网供电方式可以分为单相 PFC 电路和三相 PFC 电路。从电路构成来看可分为无源 PFC 电路和有源 PFC 电路。

对单相 PFC 技术而言, 一般认为有两种基本的有源功率因数校正技术, 一种是变换器工作在连续导电模式的“乘法器”型 (Multiplier); 另一种是变换器工作在不连续模式的“电压跟随器”型 (Voltage Follower)。实际上, 这两类技术并不能完全囊括有源功率因数校正的所有技术, 比如磁放大 PFC 技术、三电平 (Three-Level) PFC 技术和不连续电容电压模式 (DCVM) PFC 技术等。

还可以从采用的软开关技术的角度进一步对上述两种方式的有源功率因数校正技术加以分类。从软开关特性来划分, 有源 PFC 电路可分为两类, 第一类是零电流开关 (Zero Current Switching, 简写为 ZCS) PFC 技术, 第二类是零电压开关 (Zero Voltage Switching, 简写为 ZVS) PFC 技术。按实现软开关的具体方法还可以进一步划分, 有并联谐振型 (Parallel Resonant Converter, 简写为 PRC)、串联谐振型 (Serial Resonant Converter, 简写为 SRC)、串并联谐振型 (Serial Parallel Resonant Converter, 简写为 SPRC; 也叫 LCC) 以及准谐振型 (Quasi-Resonant Converter, 简写为 QRC) 等软开关谐振有源功率因数校正技术。

从控制方法来分, 有源功率因数校正电路可以采用脉宽调制 (PWM)、频率调制 (FM)、单环电压反馈控制、双环电流模式控制、数字控制、滑模 (Sliding Mode) 控制以及单周期 (One Cycle) 控制以及其他各种控制方法。

从拓扑结构上划分, 有源功率因数校正电路可分为预调整器型 (Preregulator) PFC 电路以及单级组合 PFC 变换器两种形式, 后者被认为是较理想的有源功率因数校正电路结构。

## 1.3 两种基本的PFC结构

一般认为有两种基本的有源功率因数校正技术, 一种是变换器工作在连续导电模式的“乘法器”型; 另一种是变换器工作在不连续导电模式的“电压跟随器”型。所谓连续导电模式 (CCM) 和不连续导电模式 (DCM) 一般是指在一个开关周期内, 变换器的电感上流过的电流是否连续。CCM 意味着电感上的电流始终不会为零, 而 DCM 意味着在一个开关周期内电感的电流有一段时间为零。

### 1.3.1 乘法器 PFC 技术

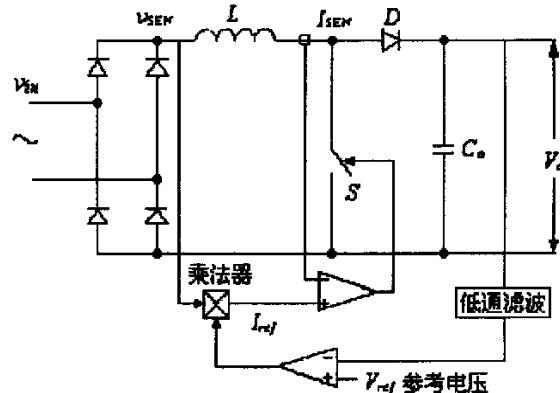

80 年代中期, 有源功率因数校正技术的研究以乘法器方式为主。乘法器技术通常采用两级结构的 PFC 电路, 且电路工作在 CCM 模式。其基本原理如图 1-5 所示。

图 1-5 典型的乘法器方式 PFC 电路的组成

Fig. 1-5 typical Multiplier PFC

图中 boost 变换器的电感电流就是输入电流, 电感电流被采样并被控制, 使其幅值与和输入电压同相位的正弦参考信号成正比, 从而达到功率因数校正的目的; 乘法器方式 PFC 电路还可以根据输出电压反馈信号, 利用一个乘法器电路来控制正弦参考电流信号, 从而获得可调整的输出电压。因此这种方案要求采用电压电流双环控制, 常用的控制方法有峰值电流控制、滞环电流控制、平均电流控制等等。

乘法器方式是目前比较成熟的 PFC 技术, 其输入功率因数可达 0.99 以上。它可以实现输入电流波形控制和输出电压调节的双重功能, 因此工作于 CCM 的 PFC 电路均采用乘法器控制技术, 相对于 DCM 模式, 其输入和输出电流纹波小, 电磁干扰小, 滤波容易; 电流有效值小, 器件导通损耗小, 故适应于大功率应用场合。

由于功率平衡的原理, Boost PFC 变换器的输出有两倍工频的电压纹波, 而且大的输出滤波电容造成了动态响应慢。因此, 这种 PFC 变换器通常后接一个 DC/DC 变换器, 这样变换器的整体结构就是 AC/DC+DC/DC。前一级实现 PFC 功能, 这一级也称为电压预调节器; 后一级实现稳压输出的功能。因此, 这种结构的变换器也称为两级变换器。

### 1.3.2 电压跟随器 PFC 技术

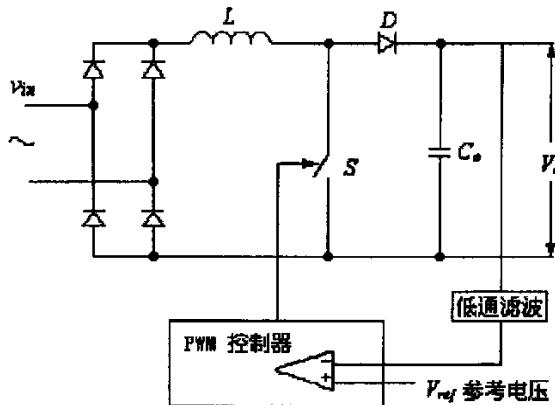

利用不连续导电模式进行功率因数校正的概念在 80 年代后期被提出, 有人称

之为自动功率因数校正，即电压跟随器 PFC 技术。由于工作在 DCM 的变换器的输入电流自动跟随输入电压，因而可以实现接近 1 的输入功率因数。这种功率因数校正技术也被称为电压跟随器。该变换器工作在不连续导电模式下，开关 S 由输出误差信号控制，开关周期为常数。由于峰值电感电流基本与输入电压成正比，因此，输入电流波形自然地跟随输入电压波形。这种 DCM 方式的优点是控制简单，一般用于中小功率变换场合中。研究发现，所有基本变换器类型，如 buck、boost、buck-boost、Cuk、Sepic 和 Zeta 变换器等在不连续导电模式下都可用于构成电压跟随器方式的 PFC 的电路。其控制方法可以采用恒频、变频、等面积等多种方式。基本电压跟随器型 PFC 电路可用图 1-6 所示的 boost 变换器来说明。

该变换器工作在不连续导电模式，开关 S 由输出电压误差信号控制，开关频率为常数。由于在每个开关周期内，峰值电感电流基本上正比于输入电压，因此输入电流波形自然地跟随输入电压波形。事实上，对不同的变换器结构，输入电流波形会出现不同程度畸变，但这对输入功率因数的影响并不明显。与乘法器型 PFC 电路相比，电压跟随器技术常采用单级功率因数校正拓扑结构，既具有输入功率因数校正功能，又能实现输出电压的调节，同时采用恒频单一占空比控制方式，不仅简化了控制电路，降低成本，也能减少变换器的损耗；仅要求一个电压控制环，故控制简单、成本低廉，电源体积可大大减小，适用于很多特殊场合；而且变换器工作在不连续导电模式下，避免了 boost 变换器中因输出二极管反向恢复电流而带来的问题。

图 1-6 基于 boost 变换器的电压跟随器型 PFC 电路的组成

Fig. 1-3 voltage follower PFC based on boost converter

电压跟随器型 PFC 技术的一个缺点是其输入电流波形为脉动三角波。因此其前端需添加一个小容量的滤波电容以滤除高频纹波。另一个缺点是其较高的开关峰值电流会带来较大的开关关断损耗，开关管同时承受较大的电压电流应力，并产生严重的电磁干扰(EMI)。同时，开关寄生电容引起的开通损耗仍不能避免，随

着开关频率的提高，开通损耗也会增大。

临界连续导电模式是介于连续导电模式和不连续导电模式之间的一种工作模式，其电感电流在下降到零后立刻上升，因此这种工作模式有着和 DCM 模式相同的特性；但在控制方法上由于要采样电感电流，需双环控制，控制方式接近于 CCM 模式。根据主电路的特性，一般将其归类于 DCM 中，其控制方式属于变频控制<sup>[9]</sup>。

电压跟随器型 PFC 变换器将 PFC 功能和 DC/DC 功能整合在一个变换器中，通常也称为单级 PFC 变换器。

## 1.4 单级变换器的研究热点

单级 PFC AC/DC 变换器具有控制简单，成本低廉的优点，不过由于仅仅调节输出电压，功率因数校正功能通过电路工作于 DCM 状态来自动获得，PFC 功能和 DC/DC 功能共用开关管造成输入电流不能得到最好的调节。单级 PFC AC/DC 变换器面临的两个最大的问题是：

- (1) 输入电流的整形，尽可能提高 PF，根本目的是抑制谐波含量；

- (2) 降低储能电容的电压，降低成本，减小开关电压应力。

为此，国内外学者尝试各种方法改进单级 PFC AC/DC 变换器，试图解决以上两个问题，但是又不会损害单级变换器的其他性能优点。

## 1.5 本文的内容安排

本文研究了基于直接功率传递原理的单级并联变换器。为了降低中间储能电容电压，提高单级 PFC AC/DC 变换器的工作效率，引入直接功率传递原理，对单级 PFC AC/DC 变换器的拓扑进行了深入地研究并对一种单级并联双反激 AC/DC 变换器进行了改进，加以实验验证。

本文按以下章节进行论述。

第一章 绪论。阐述本研究课题的背景，PFC 技术的分类，发展现状和技术热点。

第二章 单级 PFC AC/DC 变换器储能电容电压高的问题和直接功率传递原理。详细地解释了在单级 PFC AC/DC 变换器拓扑中储能电容电压升高的成因。为了解决这个问题，在直接功率传递原理的指导下，给出了三个典型的拓扑。在这些拓扑中，由于功率平衡问题得到较好的解决，储能电容电压明显降低。

第三章 详细的介绍了单级并联双反激电路的构成和工作原理。分析了电路的设计准则和关键的性能参数。提出了根据并联概念拓展的电路拓扑。对单级并联双反激变换器提出了改进的意见。

第四章 电路的设计。给出了设计这个电路的详细过程，包括各电路参数的决定关系，控制驱动电路的设计，变压器的设计等等。

第五章 仿真与实验。介绍了仿真软件 SIMetrix/SIMPLIS 的功能特点。用这个仿真软件对单级并联双反激电路进行仿真，采样了输入电压，输入电流，反馈环误差放大器的输出电压，两个支路开关管的电流，储能电容电压等关键波形。对储能电容值和电感量比值的变化对电流波形的影响给出了仿真对比结果。仿真结果吻合了理论的分析。实验电路进一步验证了理论分析和仿真结果。拍摄了实验电路的关键波形，对电路的工作性能指标进行了系统的分析。

## 第二章 单级 PFC 变换器直流母线电压应力的问题和直接功率传递原理

第一章的论述表明，假设在单位输入功率因数情况下，变换器的输入功率是以两倍工频正弦变化的。而输出通常是恒定的。这样，就需要一个储能元件来平衡输入和输出功率的差值。这就是带 PFC 功能的 AC/DC 变换器中间储能电容必须存在的原因。

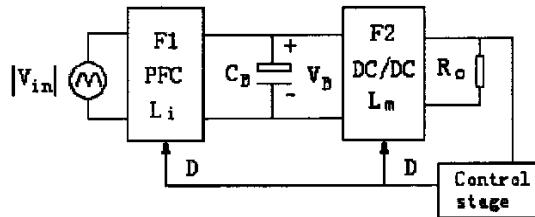

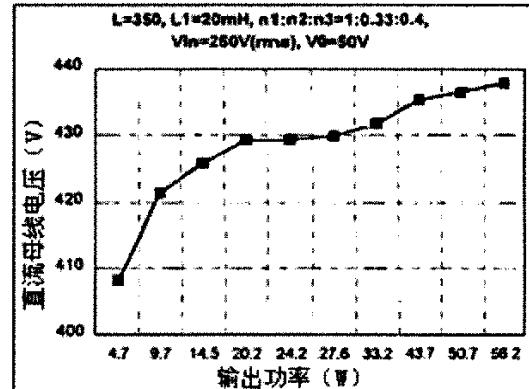

如图 2-1 所示。为了表述直流母线电压应力的概念，使用 PFC 框和 DC/DC 框两个功能框图来表达单级 PFC 变换器。PFC 框实现功率因数校正功能，通常是一个 Boost 变换器。DC/DC 框对输出电压的紧密调节，实现 DC/DC 变换功能。在这两个功能框之间有一个储能电容，承受输入功率和整流电压的变动，平衡输入功率和输出功率。

图 2-1 单级 PFC AC/DC 变换器的原理框图

Fig.2-1 Schematic diagram of single-stage PFC AC/DC converter

在两级 PFC AC/DC 变换器中，由于 PFC 级和 DC/DC 级分别控制，中间储能电容的电压可以独立地受到调节，因此不存在储能电容电压升高的问题。在单级 PFC AC/DC 变换器中，PFC 功能是由电路结构和工作模式自动完成的，反馈环仅仅调节输出电压使其稳定，而中间储能电容电压则不受控制。这样在电路工作的时候就存在中间储能电压升高的问题。以下将采用典型的 BIFRED 单级 PFC AC/DC 变换器拓扑来说明中间储能电容电压升高的原因。

为了抑制电容电压，许多文章在这方面进行了大量的研究[11~22]。其中一个解决的思路是将直接功率传递[23]的概念引入单级 PFC 变换器。在这些电路中，由于电路结构的改进，抑制了中间电容上的电压。

## 2.1 单级变换器BIFRED的结构

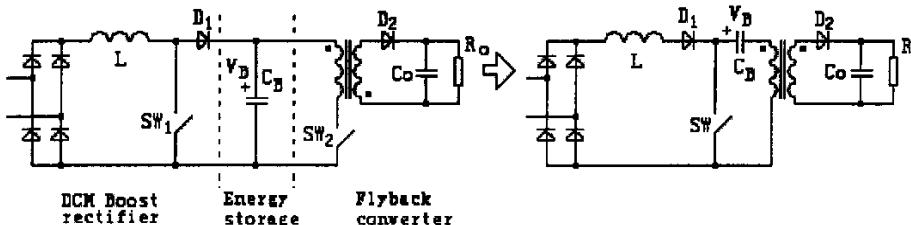

由于 DCM Boost 变换器具有固有的 PFC 功能，它和其他的变换器组合可以得到带固有 PFC 功能的单级 PFC 拓扑。在 1992 年，Michael M. 等人提出了集成反激变换器的 DCM Boost 变换器（Boost Integrated with Flyback Rectifier/Energy storage/Dc-dc converter, BIFRED）。如图 2-2 所示。BIFRED 变换器由 Boost 变换器和 Flyback 变换器组合而成，实际上是输入端串了一个二极管（D<sub>1</sub>）的隔离式 SEPIC 变换器。Boost 电感（L）工作在 DCM 模式，使得输入电流自动跟踪输入电压，DC/DC 变换器工作在 CCM 模式。

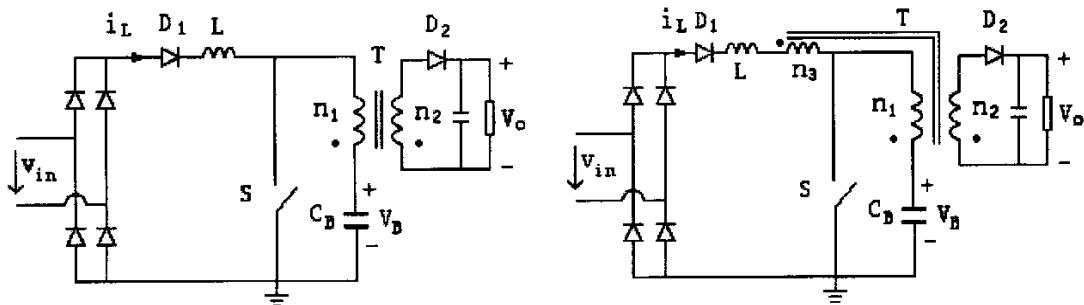

图 2-2 把 DCM Boost 变换器和 Flyback 变换器（左）组合成 BIFRED 变换器（右）

Fig 2-2 Integrate DCM Boost and Flyback converter into BIFRED converter

## 2.2 单级PFC变换器中储能电容电压的问题

单级变换器一个重要的问题是如何控制储能电容电压  $V_B$ 。

在两级 PFC 变换器中，储能电容电压  $V_B$  被调节在 380~400V。但是在单级 PFC 变换器中只有一个控制电路，因此  $V_B$  没有被控制在一个稳定的值，它随输入电压和负载的变化而变化。为了使电路具有较低的成本，希望  $V_B$  能够低于 450V，这样可以采用应用广泛而且价格低廉的额定电压为 450V 的电解电容，因为电解电容的额定电压越高，价格越高。同时也能减小其他器件，如开关管和二级管的电压应力。

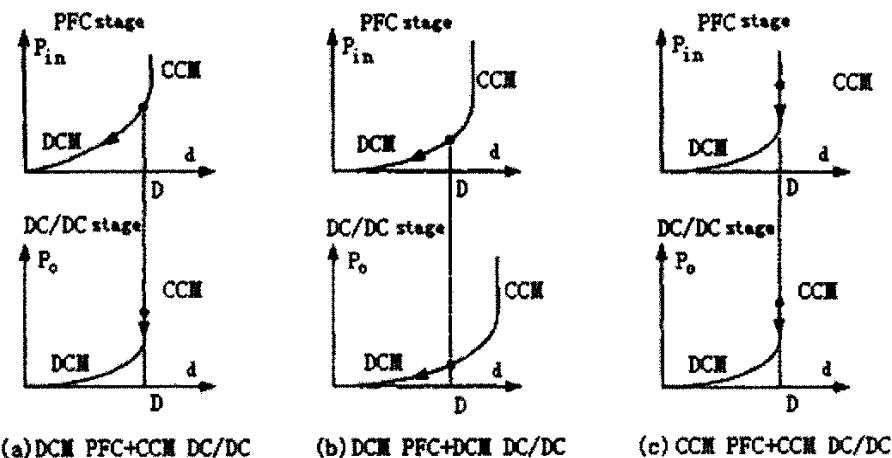

图 2-3 显示了 PFC 级输入能量和占空比的关系，以及 DC/DC 级的输出能量和占空比的关系。PFC 级和 DC/DC 级都可以工作在 DCM 或 CCM 状态，它们之间有三种可能的组合：

- 1、DCM PFC+CCM DC/DC

- 2、DCM PFC+DCM DC/DC

- 3、CCM PFC+CCM DC/DC

下面对这三种组合进行分析。

- 1、DCM PFC+CCM DC/DC

DCM 工作方式是指在一个开关周期结束，电感把所有存储的能量全部传递到下一级或负载。当负载变轻时，输出功率减少，由于 DC/DC 级工作在 CCM 状态，

占空比基本不变，但 PFC 级的输入功率同重载时一样，如图 2-3(a)所示。这样，充入储能电容的能量和从储能电容抽走的能量不平衡，引起储能电容电压  $V_B$  上升。为了保持输出电压一致，电压反馈环调节输出电压，占空比减小。这样输入能量相应减少。这个动态调节过程要到输入功率和输出功率平衡后才停止，达到一个新的功率平衡点。对于 PFC 级，输入能量的变化的周期是半个交流周期，因此输入和输出能量均衡只有过了半个周期才有效。显然，负载突变时，由重载到轻载的后果是明显的增加了  $V_B$ 。

通过变频控制可以降低储能电容电压。对于图 2-2 的 BIFRED 变换器如果工作在 DCM PFC+CCM DC/DC 模式时，可以得出  $V_B$  为

$$V_B = \frac{v_g}{2} \left[ 1 + \sqrt{1 + \frac{n^2 V_o}{I f_s I_o}} \right] - n V_o \quad (2-1)$$

其中  $v_g$  为输入电压经整流桥整流后的电压， $n$  为变换器的匝比， $f_s$  为电路的开关频率， $V_o$  和  $I_o$  分别为输出电压和电流。由此可见  $V_B$  随输出电流的减小或输入电压的上升而上升，同时还受开关频率的影响。当轻载时增加开关频率，能减小  $V_B$ ，当满载时可以提高开关频率。但为了使  $V_B$  降到 450V 以下，需要开关频率变化很大。如果负载从满载到 10% 满载变化，则轻载时开关频率可能时满载时的 10 倍。因此，很难对电感和滤波器进行优化设计，而且轻载时效率也不高。

图 2-3 PFC 级输入功率与占空比关系曲线及 DC/DC 级输出功率与占空比关系曲线

Fig.2-3 Relationship between duty cycle and input power of PFC stage or output power of DC/DC stage

## 2、DCM PFC+DCM DC/DC

如果 PFC 和 DC/DC 级都工作在 DCM，那么当负载变轻时，根据 DC/DC 变换器电压反馈环特性，占空比也降低。如图 2-3(b)所示，随负载变轻，占空比减

小，输入功率也相应降低。这样在 DCM PFC 和 DCM DC/DC 结合时，轻载时储能电容电压过高的现象有所减轻。但是，当 DC/DC 变换器工作在 DCM 模式时，电流峰值高，增加了导通和开关损耗，降低了效率，特别不适合输出电压较低、输出电流较大的应用中。由于储能电容电压  $V_B$  主要在轻载时偏高，在输出电压较高、电流较小的情况下，有些拓扑使 DC/DC 变换器在输出负载较高时工作在 CCM 状态，轻载时工作在 DCM 状态。

### 3、CCM PFC+CCM DC/DC

PFC 级工作在 DCM 方式需要一个比较大的 EMI 滤波，而且电流应力高，降低了效率。如果 PFC 级和 DC/DC 级都工作在 CCM，如图 2-3(c)所示，即使轻载时，占空比也保持一致。输入和输出功率可以自动平衡，输入功率可高可低，取决于负载。因此，CCM PFC 结合 CCM DC/DC 变换器的输入及输出功率可自动均衡，轻载时没有储能电容电压高的问题，而且这种方式效率最高。但是 PFC 级工作在 CCM 状态的功率因数比工作在 DCM 要差，设计上也比较复杂。由于 PFC 级的有效占空比  $D_{eff}$  受 DC/DC 级的占空比限制，很难找到一种拓扑作为 PFC 级，能够在固定占空比情况下保持 PFC 完全工作在 CCM 状态。

因此，单级 PFC 变换器的主要问题是在使输入电流谐波满足 IEC-1000-3-2 Class D 标准和输出电压快速调节的同时，找到抑制储能电容电压  $V_B$  过高的方法。

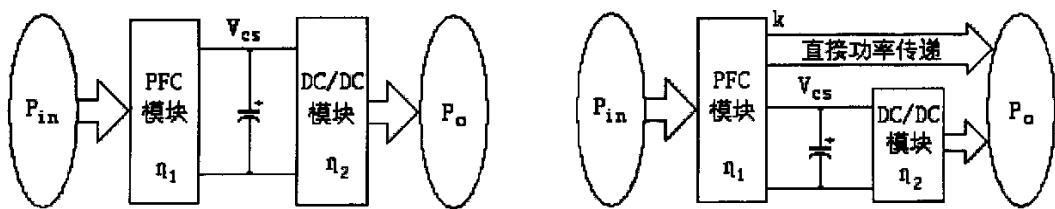

## 2.3 直接功率传递原理

典型的两级或者单级 PFC 变换器都有两个功能模块，分别是 PFC 模块和 DC/DC 模块。AC 输入功率首先经 PFC 模块转换成直流功率储存在中间储能电容，然后储存的直流功率再经 DC/DC 模块处理成需要的直流输出功率。这样输入功率经过两次处理才到达输出。如图 2-4(a) 所示，假设 PFC 模块和 DC/DC 模块的效率是  $\eta_1$  和  $\eta_2$ ，相应地有

$$P_o = P_{in} \eta_1 \eta_2 \quad (2-2)$$

于是单级 PFC 变换器的效率为

$$\eta = \eta_1 \eta_2 \quad (2-3)$$

从上面的等式可以看出，总效率是每个功率变换模块的乘积，两次功率处理使得变换效率下降。

实际上，为了达到良好的输出功率调节，将全部输入功率进行两次处理是不必要的。我们可以允许主要的输入功率只经过一次处理，而让较小的功率经过二次处理以保持总的输出功率为常数。如图 2-4(b)所示，输入功率经 PFC 模块出来， $k$  部分功率直接传递到输出，剩余的  $(1-k)$  部分功率储存在储能电容中，然后由 DC/DC 模块处理，输出功率由这两部份共同组成。我们有

$$P_o = P_{in} \eta_1 k + P_{in} \eta_1 \eta_2 (1-k) \quad (2-4)$$

于是单级 PFC 变换器的效率为

$$\eta = \eta_1 k + \eta_1 \eta_2 (1-k) \quad (2-5)$$

即

$$\eta = \eta_1 \eta_2 + (1-\eta_2) \eta_1 k \quad (2-6)$$

对比 (2-3) 式和 (2-6) 式, 显然基于直接功率传递的变换器具有更高的效率。

对这种功率传递, 一部分功率只处理一次, 称为直接功率传递 (Direct Power Transfer)。基于直接功率传递原理, 可以开发出具有更高效率和更高额定功率的单级 PFC 变换器。

图 2-4(a) 传统的两级和单级 PFC 原理图;

图 2-4 (b) 直接功率传递原理图

Fig.2-4 (a) Conventional PFC converter schemes;

Fig.2-4 (b) Direct Power Transfer scheme

直接功率传递的理论主要是从提高效率的角度提出的一种改进功率流向的方法。功率处理过程的优化, 为其他电路性能参数的改善带来方便。根据直接功率传递原理, 可以发展出许多单级 PFC 变换器拓扑, 这些拓扑在抑制过高的中间电容电压应力方面具有显著的效果。

## 2.4 几个改进的单级PFC拓扑及其中间电容电压应力分析

以下将介绍三个基于直接功率传递原理改进的单级 PFC AC/DC 变换器拓扑, 这些拓扑有效地抑制了中间储能电容电压的升高。

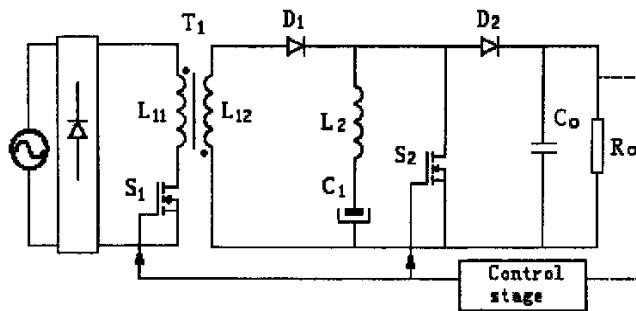

### 2.4.1 Flyback-Boost 变换器<sup>[11]</sup>

电路拓扑如图 2-5(a)所示。这个电路可以认为是由一个反激变换器和一个 Boost 变换器组合而成, 两个内部变换器使用同一套控制电路。在这个电路中, 变压器  $T_1$  和电感  $L_2$  均工作于不连续电流模式。变压器  $T_1$ , 开关管  $S_1$  和二极管  $D_1$  构成内部反激变换器。电感  $L_2$ , 开关管  $S_2$  和二极管  $D_2$  构成内部 Boost 变换器。首先内部反激变换器从电源线吸收功率。其中一部分功率经过  $D_1$  和  $D_2$  直接传递到输出, 这部分功率只经过一次处理, 约占总输出功率的 70% (参看图 2-7(a)中输入功率和输出功率的关系分析)。另一部分功率经  $D_1$ ,  $L_2$  储存在储能电容  $C_1$ 。通过开关管的开通和关断,  $C_1$  的能量再经  $L_2$ ,  $D_2$  反馈到输出, 这部分功率经过二次处理, 约占总输出功率的 30%。电路的功率流向如图 2-5(b)所示。

图 2-5(a) Flyback-Boost 变换器拓扑

Fig.2-5(a) Topology of Flyback-boost converter

图 2-5(b) 功率流向图

Fig.2-5(b) Power flow of Flyback-boost converter

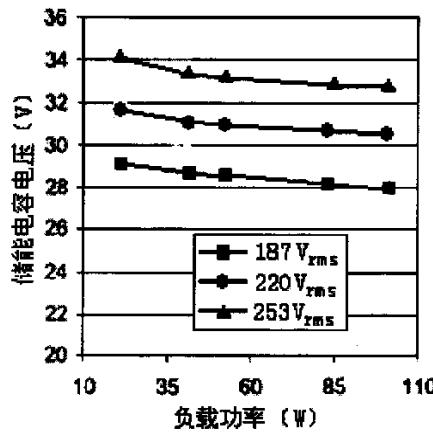

由于经过反激变换器降压，储能电容上的电压大大下降，甚至低于输出电压。一个设计方案如下：输出功率 100W，输出电压 56V，AC 线电压  $187V_{rms} \sim 265V_{rms}$ 。储能电容的电压变化曲线如图 2-6 所示。从图中可以看出，这个方案的电容电压

图 2-6 储能电容电压变化

Fig.2-6 Voltage variation on the bulk capacitor

只有 30V 左右。另外，本方案电容变化范围为 29V 到 34V，只变化了 1.17 倍，

变化很小。在通用输入电压( $85V_{rms}$ ~ $265V_{rms}$ )下,这个优势更加明显。

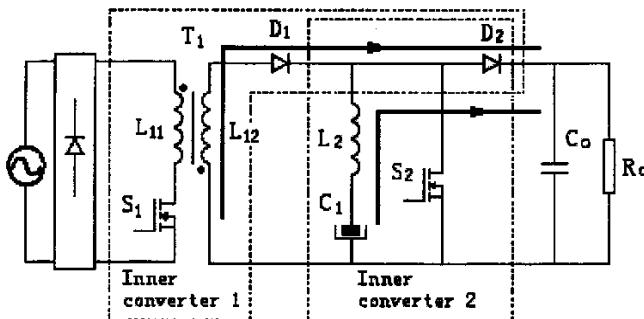

#### 2.4.2 单级并联 PFC 变换器<sup>[13]</sup>

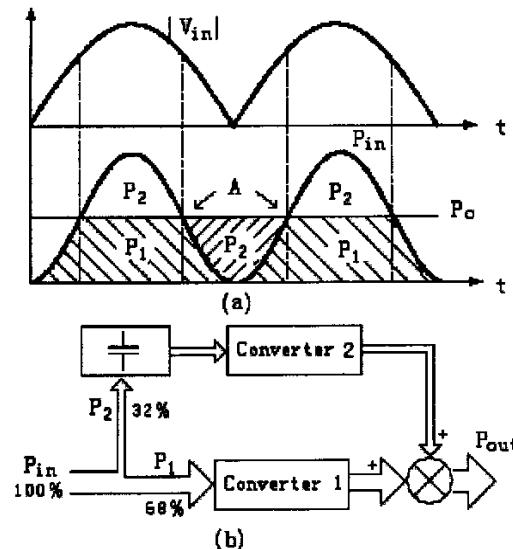

在 2.4.1 Flyback-Boost 方案中,输入功率全部经过内部反激变换器,然后一部分功率直接输出,另一部分送到内部 Boost 变换器进行二次处理。实际上,如果刚开始就将输入功率分成两部分,由两个内部变换器分别处理,同样可以满足要求,这就是并联功率因数校正 (parallel power factor correction) 的思想<sup>[12]</sup>。在功率因数为 1 的情况下,输入功率和输出功率的关系如图 2-7(a)所示。从图 2-7(a)中可以看出,功率  $P_1$  部分可以直接传递到输出,只有  $P_2$  部分功率需要储能电容充放电处理。 $P_2$  是半个工频周期中输入功率和输出功率不平衡的部分,占总

图 2-7(a) 并联功率因数校正原理图

Fig.2-7 (a) Parallel PFC scheme

图 2-7(b) 实现单级并联 PFC 的双反激电路

Fig.2-7 (b) Parallel bi-flyback converter with PFC

输出功率的 32%。并联功率因数校正的全部功率都是一次处理,理论上可以获得

更高的效率，功率元件的额定值降低。

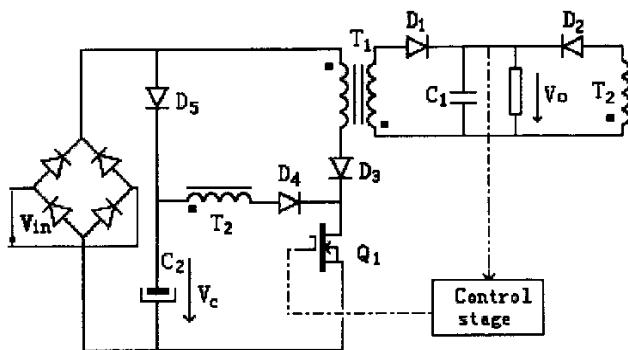

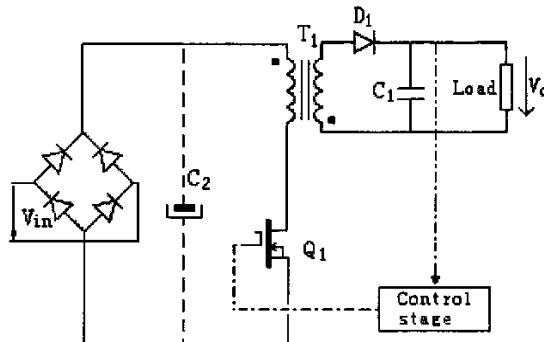

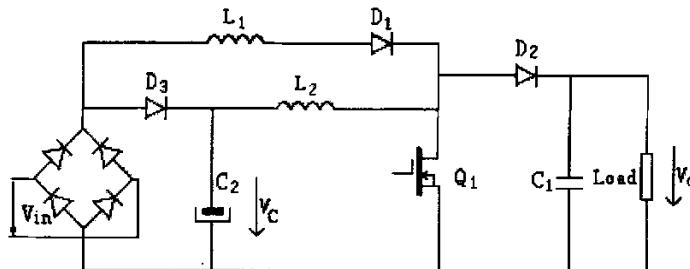

一个简单的单级并联双反激 AC/DC 变换器如图 2-7(b)所示。

在这个电路中，变压器  $T_1$ ，开关管  $Q_1$  和二极管  $D_1$  构成主反激变换器；变压器  $T_2$ ，二极管  $D_2$  和开关管  $Q_1$  构成辅助反激变换器。这两个变换器共用一个开关管  $Q_1$ 。储能电容  $C_2$  是辅助支路的输入，它经由  $D_5$  充电至输入电压峰值。 $D_3$  和  $D_4$  可以避免两个反激变换器之间形成环流。当  $Q_1$  闭合时，AC 电源给  $T_1$  原边电感充电， $C_2$  给  $T_2$  原边电感充电；开关关断时， $T_1$  和  $T_2$  原边电感储存的能量反激到输出。

这个变换器用两路输入（AC 主回路和储能电容  $C_2$ ）给负载供电。大部分功率由 AC 主回路承担，储能电容在工频周期的中间部分（此时输入电压高）从 AC 电源吸收能量，主要在电压过零点附近释放能量。

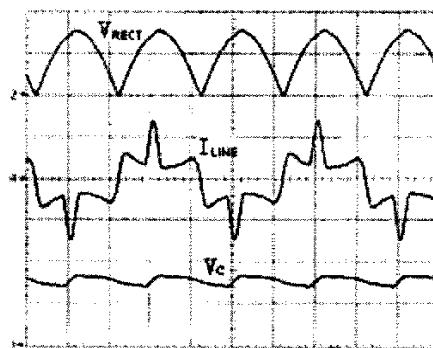

电路的电压电流波形如图 2-8 所示。从图中可以看出，储能电容在线电压半个周期的中间部分充电，并且主要在输入电压非常小的时候释放部分电量，电压被钳位在输入电压峰值而且与负载无关。

图 2-8 整流线电压 (100V/div)，线电流 (2A/div) 和储能电容电压 (100V/div)

Fig.2-8 Rectified voltage (100V/div), line current (2A/div) and voltage on the bulk capacitor (100V/div)

这个方案功率电路简单，成本低，体积小；输入功率全部一次处理，提高了变换效率；储能电容处理的功率较小，电压被钳位在输入电压的峰值。因为两个反激变换器均工作于 DCM，电容电压独立于负载。因此，它不会造成器件额外的电压应力，降低了对高压器件的要求。这是相对于其他单级 PFC 电路最重要的不同点。

这个电路的缺点是：两个反激变换器均工作于 DCM，功率较小；线电流不正弦化，功率因数较低。

### 2.4.3 直流母线电压反馈

图 2-9(a)和图 2-9(b)是基本的 BIFRED 变换器和具有母线电压反馈的 BIFRED

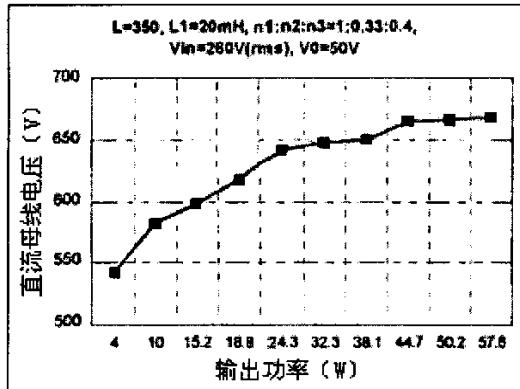

变换器。前面已叙述,基本的 BIFRED 变换器的实质是 DCM 的 Boost 变换器+CCM 的 Flyback 变换器。由于 PFC 级和 DC/DC 级之间功率不平衡引起高直流母线电压,这种电路是不实际的。图 2-10(a)是基本的 BIFRED 变换器直流母线电压仿真曲线。从图中可以看出,当负载达到 50W 时,母线电压已经超过 650V,而开关峰值电压将超过 1000V。

图 2-9 (a)基本的 BIFRED 变换器; 图 2-9 (b)具有直流母线电压反馈的 BIFRED 变换器

Fig.2-9(a) Basic BIFRED converter; Fig.2-9(b) BIFRED converter with bus voltage feedback

在修正的电路中,在 Boost 电感之后串入一个附加变压器绕组  $n_3$ ,反馈系数为  $n$ 。当  $S$  导通,Boost 电感充电时,  $n_3$  上反馈来自母线储能电容上的电压,电感  $L$  上的电流为

$$i_L = \frac{|v_{in}| - nV_B}{L} t \quad (2-7)$$

从上式可以看出,当母线电压具有上升的趋势时,输入电流下降,输入功率自动减小,从而保证输入和输出功率的平衡。于是,直流母线电压被限制在一定范围内。另外,反馈绕组将部分功率直接传递到输出,这样可以降低器件的额定值,提高变换效率。具有母线电压反馈的 BIFRED 变换器直流母线电压仿真曲线如图 2-10(b)所示。

应用母线电压反馈的概念,可以推导出一些新的拓扑。实际上,只要保证 PFC 功能是由 DCM 的 Boost 变换器实现,这个方案可以推广到任意单级 PFC 变换器。这个电路的缺点是:虽然降低了直流母线电压,由于引入反馈绕组,电感电流存在死区,输入电流波形的品质变差。

#### 2.4.4 抑制电容电压的效果对比

单级 PFC 设计最关心的问题之一是在输入电压最大值且负载最轻时,直流母线上的电压应力要小,也即是储能电容上的电压应力要小。根据直接功率传递原理改进的单级 PFC 变换器提高了变换效率。由于电路结构的改进,有效地控制了直流母线电压应力。

在 Flyback-Boost 方案中,储能电容位于反激变换器降压之后,电压低于输入

电压峰值，甚至低于输出电压，而且随输入电压的变化小；在单级并联双反激 AC/DC 变换器方案中，全部功率都是一次处理的，原理上可以得到更高的效率，储能电容电压被钳位在输入电压峰值；直流母线电压反馈方法有效的抑制了电容电压的上升，可以衍生出许多改进拓扑。

图 2-10(a)没有母线电压反馈的 DC 电压变化；图 2-10 (b)具有母线电压反馈的 DC 电压变化

Fig.2-10 (a) DC voltage variation

without bus voltage feedback;

Fig.2-10 (b) DC voltage variation

with bus voltage feedback

这三个方案有一个共同的缺点是由于只对电压进行采样控制，而且为了达到较高的效率，对功率流向进行改进，导致输入电流不正弦化。不过 IEC1000-3-2 D 类标准对功率因数没有特殊的规定，只要能满足谐波要求，就能通过该项规定。设计的目的是满足谐波标准而不是追求高功率因数。因此这个缺陷在实际应用中是可以接受的。

## 2.5 本章小结

本章用典型的 BIFRED 单级 PFC AC/DC 变换器电路解释了中间储能电容在轻载时电压升高的工作机理。引起这个问题的根本原因是输入功率和输出功率之间的瞬时不平衡。为了解决这个问题，引入直接功率传递原理，从结构上对单级 PFC AC/DC 变换器进行改进。列举了三个典型的基于直接功率传递原理改进的单级 PFC AC/DC 变换器拓扑。这些拓扑有效地抑制了中间储能电容电压。

### 第三章 单级并联双反激 AC/DC 变换器的工作原理

在 2.4.2 节中，介绍了一个简单的具有快速输出电压调节的单级并联双反激 AC/DC 变换器。本章详细介绍这个变换器的工作原理。它与其他文章提出的拓扑主要的不同是储能电容上的电压被钳位在输入电压，电压保持常数。这个方案的原理演示如图 3-1。这个变换器可以由反激变换器推导得出，由于只增加了无源元件，它只有一个开关和单环控制。可以看出这个变换器具有两个内部输入，储能电容是其中之一。

因此，这个变换器的主要优点如下：

- (1) 简单的功率级：低成本和体积；

- (2) 功率只处理一次：效率高。

这个变换器的线电流非正弦化但是它的谐波含量可以通过适当的设计加以控制，因此，这个变换器可以设计符合中小功率 ( $<500W$ ) 标准。

图 3-1 原理框图

Fig.3-1 Proposed approach of bi-flyback converter

#### 3.1 提出的变换器

这个变换器是在 DC/DC 变换器的基础上增加一些附加元件形成的（在 AC/DC 应用中这些元件是必需的）。控制策略类似于一个 DC/DC 变换器，输出电压是唯一的控制量，因此实际的变换器非常简单。虽然输入电流没有被控制，但是可以符合 IEC1000-3-2 关于低频谐波的标准。

这个变换器可以从一些已知的变换器推导，这里使用反激变换器去解释。DC/DC 反激变换器的功率级如图 3-2。变换器由变压器  $T_1$ ，三极管  $Q_1$ ，二极管  $D_1$  和输出电容  $C_1$  组成。

具有储能电容  $C_2$  的反激变换器特性：在二极管整流桥的输出增加一个大电容  $C_2$ （如图 3-2），变换器的输入电压几乎是常数，很容易得到良好调节的输出电压。然而，由于电流峰值高，导通时间短，线电流含有大量谐波。

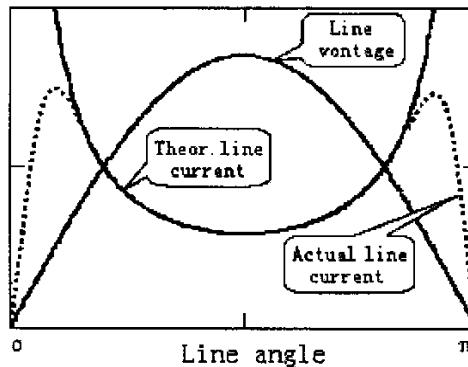

没有储能电容  $C_2$  的反激变换器特性：这是一个输入电压从 0 到  $V_{IN,PEAK}$ （图 3-2）的 DC/DC 变换器。在理想情况下，使用这样一个单变换器吸收 AC 电源给

负载供电是期望的。然而，用这个简单的变换器不可能在负载端得到良好调节的输出电压。图 3-3 显示了在一个工频半周期为了保持输出功率恒定的理论线电流。可以看出，由于输入电压是正弦的，在线电压过零点附近，需要从 AC 电源吸收几乎无穷大的电流。因此，如果仅仅使用一个简单的变换器（没有储能电容  $C_2$ ），在这些输入电压过零点附近会发生输出电压降落。

图 3-2 反激变换器的功率级

Fig.3-2 Power stage of flyback converter

图 3-3 没有储能电容的变换器的理论和实际输入电流

Fig.3-3 Theoretical and actual line current using a single converter without bulk capacitor

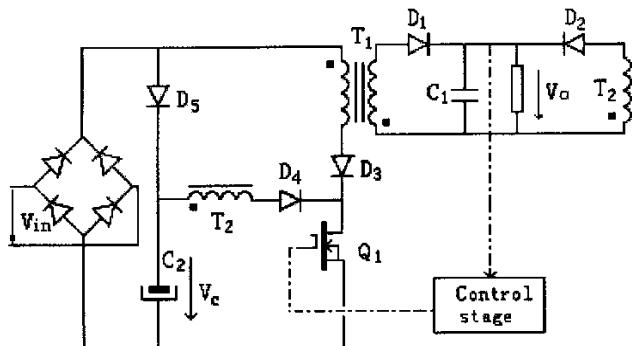

提出的变换器：提出的变换器复合了上述的两种情况，由两个变换器分别承担了这两种电流，共同决定输入电流的波形。为了达到这点，这个变换器有两个内部输入：第一个连接到整流桥，另一个连接到储能电容。这个电容通过二极管充电到输入电压峰值。

提出变换器的功率级如图 3-4 所示。它是基于图 3-2 的简单反激变换器附加一些无源元件而成的。变压器  $T_2$ ，二极管  $D_2$  组成了一个辅助反激支路，这个辅助支路的输入是储能电容  $C_2$ ，它通过二极管  $D_5$  充电到输入电压峰值。这个辅助支路处理的功率数量由设计决定。为防止在这两个反激支路之间形成电流环流，两个变压器分别串联二极管  $D_3$  和  $D_4$ 。两个并联的反激支路使用同一个开关  $Q_1$  和控

制环路。同样，他们共享输出电容  $C_1$ 。

图 3-4 提出的双反激变换器的功率级

Fig.3-4 Power stage of the proposed bi-flyback converter

这个变换器的目标是同时从两个内部输入给负载供电 (AC 电源和储能电容  $C_2$ )。储能电容主要在线电压过零点，输入电压低时提供能量。变换器的大部分功率直接由 AC 电源送到输出，

储能电容  $C_2$  在工频半周期的中间部分从 AC 电源吸收能量。因为只有一部分负载功率从储能电容抽取，所以它吸收的峰值电流也比较小。

变换器的两个变压器可以工作在任何导通模式 (CCM 和 DCM)。出于效率的考虑，对低功率最合适的选择是两个变压器同时工作在 DCM。以下都假设电路工作在这个模式。

这个变换器相对两级方法的主要不同如下：

优点：

1、更小体积和更低的成本：由于单开关和单环控制，改善了体积和成本。

2、高效率：由于输出功率处理一次，效率改善。而两级方法中输出功率是处理两次的。

缺点：电流非正弦

对比于其他的单级方案：

优点：

1、储能电容电压被钳位：因此，它不会增加装置附加的电压应力。这是相对于其他参考文献中提出拓扑最重要的不同，它们表现出更高的电压应力。

2、输出功率处理一次。

缺点：一些单级方案比双反激变换器有更少的附加元件。

这个电路还有一个另外的优点：由于一些负载有待机需要 (电脑，VCR's 等等)，变压器  $T_2$  可以在待机模式中提供电源。这样，在轻载的时候屏蔽变压器  $T_1$  通路 (用继电器)，负载只由  $T_2$  供电，可以减小损耗。

总的来说，单级双反激变换器是体积，成本和效率之间一个好的折衷，是低功率应用好的选择。

以下部分将分析变换器在一个开关周期的工作过程以及电路的设计指南。

### 3.2 电路的工作原理

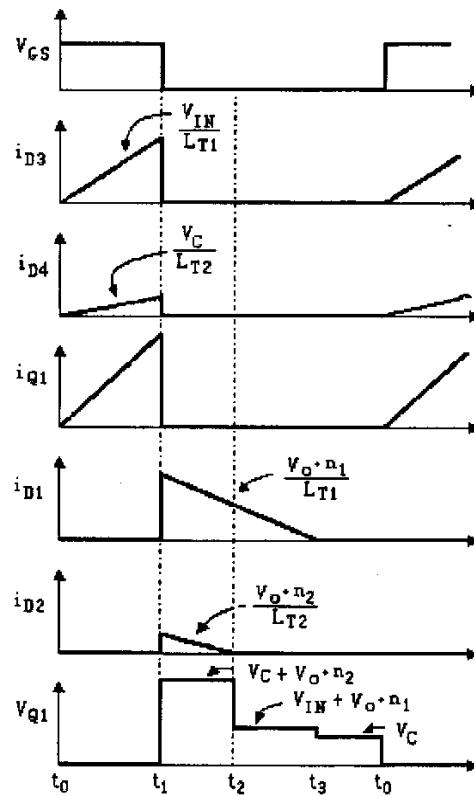

变换器在一个开关周期的主要理论波形如图 3-5。变换器的两个支路都假设工作在 DCM。

区间 ( $t_0-t_1$ ):  $t_0$  时刻，开关管打开。两个变压器的原边电感分别从 AC 电源和储能电容线性充电。这些电流的斜率取决于输入电压和每个变压器的电感。即  $T_1$  的原边电感  $L_{T1}$  上施加了瞬时整流线电压  $V_{IN}$ ;  $T_2$  的原边电感  $L_{T2}$  上施加了瞬时  $V_C$  (几乎是常数电压，等于  $V_{IN,PEAK}$ )。两个电流叠加后流过开关管  $Q_1$ 。在区间最后，变压器已经储存了能量。

图 3-5 变换器在一个开关周期的主要波形

Fig.3-5 Main waveforms of the converter in a switching cycle

区间 ( $t_1-t_2$ ): 在  $t_1$  时刻开关管  $Q_1$  关断。变换器副边的二极管  $D_1$ ,  $D_2$  开始导通，变压器释放之前储存的能量。因此，在这个区间，开关上的电压的最大值在  $V_{IN}+V_O \cdot n_1$  和  $V_C+V_O \cdot n_2$  ( $n_1$ : 1 和  $n_2$ : 1 分别是  $T_1$  和  $T_2$  的变比)。那就是强制对

$T_1$  和  $T_2$  消磁的电压。 $D_3, D_4$  其中一个二极管，阻断在两个电压差。

区间  $(t_2-t_3)$ ：在  $t_2$  时刻，其中一个变压器复位（这里以  $T_2$  为例），那么在这个区间只有一个变压器在进行消磁过程  $(T_1)$ 。因此，二极管  $D_1$  继续导通，变压器  $T_1$  的能量继续释放到输出。开关管上的电压是这个变压器反激的电压与它的输入电压的加和与另一个支路的输入电压两者中的较大值。在这种情况下，由于  $T_2$  首先退磁，开关管的电压是在  $V_{IN}+V_{O \cdot n_1}$  和  $V_C$  之间的较大值。

区间  $(t_3-t_0)$ ：在  $t_3$  时刻，变压器  $T_1$  复位，因此在这个区间电路中变压器和开关管都没有电流流过，输出电压由输出滤波电容  $C_1$  提供。开关管  $Q_1$  的电压等于储能电容上的电压，因为它比瞬时输入电压高。在  $t_0$  时刻，新的开关周期开始。

### 3.3 设计准则

这个变换器最重要的设计任务是确定每个支路的功率分配  $(P_{MAIN}$  和  $P_{AUX}$ )。功率的分配在电流谐波含量和变换器定级为标准 IEC1000-3-2 A 或者 D 当中扮演了重要的角色。这个可以通过  $T_1$  和  $T_2$  的原边电感进行控制  $(L_{T1}$  和  $L_{T2}$ )。

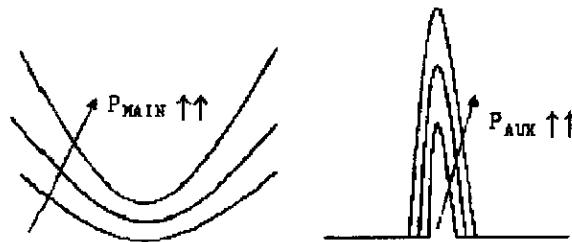

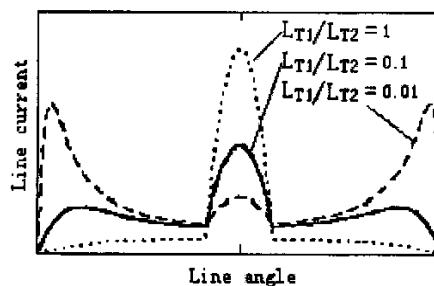

图 3-6 表明了在一个工频半周期理想的输入电流波形对应  $P_{MAIN}$  和  $P_{AUX}$  的函数，注意实际电流波形是两个的加和。总的来说，分配更多的功率通过主支路更有利，因为它可以减少线电流的峰值部分。主支路承担功率  $P_{MAIN}$  增加，将导致线电流的谐波含量也增加；然而，由于辅助支路输入电流的减少，电流波形更容易避开 class D 标准的包络线 (Class D 标准更严格)，这样变换器只需要满足 Class A 标准。对于 Class A，只对谐波电流强加了绝对值限制，因此，在一定功率水平是可能达到这个标准的。

图 3-6 在一个工频半周期中双反激变换器的两部分电流波形

Fig.3-6 Two parts of the input current waveforms of the bi-flyback converter in a line half-cycle

假设在储能电容  $C_2$  上是一个常数电压  $V_C$ ，忽略电压纹波，就可能得到变换器主要参数对于线相角的函数等式。

由于变换器的两个变压器工作于 DCM，在一个开关周期每个变压器的峰值电流（参看图 3-5 中的  $i_{D3}$  和  $i_{D4}$ ）可以通过 (3-1) 和 (3-2) 计算

$$I_{LT1,PK}(\omega t) = \frac{V_{IN}(\omega t)}{L_{T1} \cdot f} \cdot d(\omega t) \quad (3-1)$$

$$I_{LT2,PK}(\omega t) = \frac{V_C}{L_{T2} \cdot f} \cdot d(\omega t) \quad (3-2)$$

$V_{IN}(\omega t)$ 是瞬时线电压,  $d(\omega t)$ 是对线相角的占空比函数,  $L_{T1}$ 和 $L_{T2}$ 是变压器的磁性电感,  $f$ 是变换器的开关频率。在一个开关周期平均, 可以得到输入电流的低频演变如下

$$I_{LT1,Avg}(\omega t) = \frac{\frac{1}{f} \int_0^{\frac{1}{f}d(\omega t)} \frac{V_{IN}}{L_{T1}} \cdot t dt}{1/f} = \frac{V_{IN}(\omega t)}{2 \cdot L_{T1} \cdot f} \cdot d^2(\omega t) \quad (3-3)$$

$$I_{LT2,Avg}(\omega t) = \frac{\frac{1}{f} \int_0^{\frac{1}{f}d(\omega t)} \frac{V_C}{L_{T2}} \cdot t dt}{1/f} = \frac{V_C}{2 \cdot L_{T2} \cdot f} \cdot d^2(\omega t) \quad (3-4)$$

将电压乘以电流, 得到每个支路的输入功率

$$P_{LT1,Avg}(\omega t) = \frac{V_{IN}^2(\omega t)}{2 \cdot L_{T1} \cdot f} \cdot d^2(\omega t) \quad (3-5)$$

$$P_{LT2,Avg}(\omega t) = \frac{V_C^2}{2 \cdot L_{T2} \cdot f} \cdot d^2(\omega t) \quad (3-6)$$

这两个功率等式的加和等于在每个开关周期供应负载的输出电压

$$P_{LT1,Avg}(\omega t) + P_{LT2,Avg}(\omega t) = P_o = \frac{V_o^2}{R} \quad (3-7)$$

用  $V_{IN,PEAK} \cdot \sin(\omega t)$  代换  $V_{IN}(\omega t)$ , 用  $V_{IN,PEAK}$  代换  $V_C$ , 代入 (3-7), 得到占空比关于线相角的表达式如下

$$d(\omega t) = \frac{V_o}{V_{IN,PK}} \cdot \sqrt{\frac{2 \cdot L_{T2}}{RT \cdot \left(1 + \frac{L_{T2}}{L_{T1}} \cdot \sin^2(\omega t)\right)}} \quad (3-8)$$

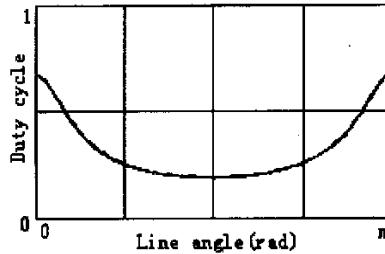

根据理论上的占空比演化表达式 (3-8) 可以描绘出图 3-7 (假设  $L_{T1}/L_{T2}=0.1$ )。当输入电压接近零点时为最大值, 因为这时只有辅助支路释放能量到输出。一旦计算出占空比, 输入功率波形 ( $P_{MAIN}$  和  $P_{AUX}$ ) 可以很容易的用 (3-5) (3-6), 和 (3-8) 推导。等式 (3-9) (3-10) 表明每个支路处理的功率

$$P_{MAIN}(\omega t) = \frac{V_o^2}{R} \cdot \frac{\sin^2(\omega t)}{\frac{L_{T1}}{L_{T2}} + \sin^2(\omega t)} \quad (3-9)$$

$$P_{AUX}(\omega t) = \frac{V_o^2}{R} \cdot \frac{L_{T1}}{L_{T2}} \cdot \frac{1}{\frac{L_{T1}}{L_{T2}} + \sin^2(\omega t)} \quad (3-10)$$

从 (3-9) (3-10) 得到的功率波形如图 3-8 所示 (变换器功率 100W,  $L_{T1}/L_{T2} = 0.1$ )。注意到辅助支路主要在输入电压过零点附近给负载供电。

图 3-7 在一个工频半周期中占空比的演化

Fig.3-7 Example of the duty cycle evolution in a line half-cycle

图 3-8 在一个工频半周期中两条支路的功率分配

Fig.3-8 Power distribution between branches in a line half-cycle

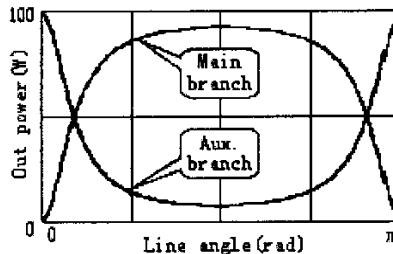

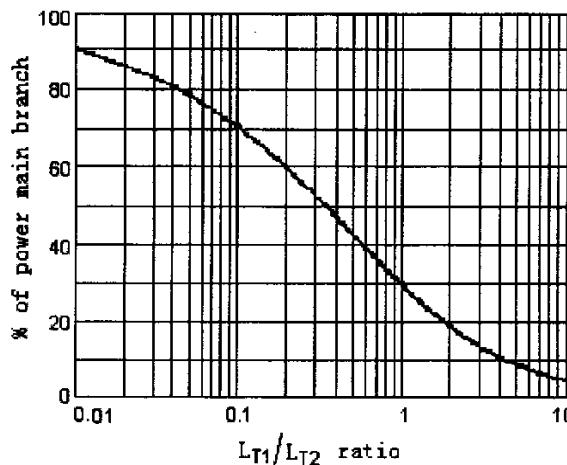

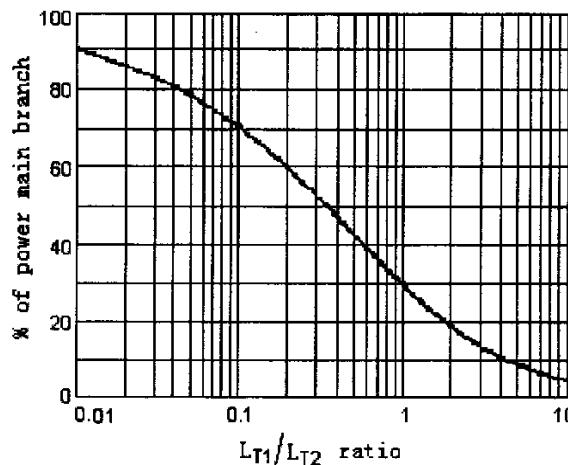

从这些等式推导可知,  $L_{T1}/L_{T2}$  是这个变换器最重要的参数 (当变换器工作于 DCM)。在一个工频周期对 (3-9) 和 (3-10) 进行平均, 可以得到分配到每个支路的功率数量, 如图 3-9 所示。如期望的那样, 比值  $L_{T1}/L_{T2}$  越小, 主支路处理的功率越高。

在这个变换器中, 占空比以两倍工频周期性地变化, 如 (3-8) 式所示。最大占空比发生在  $\omega t=0$ , 最小发生在  $\omega t=\pi/2$ 。占空比的变化是设计中需要考虑的一个因素。用极值代入 (3-8) 式, 可以得到占空比的最大值和最小值的比

$$\frac{d_{MAX}}{d_{MIN}} = \sqrt{1 + \frac{L_{T2}}{L_{T1}}} \quad (3-11)$$

可以看出在变换器工作于 DCM 情况下, 这个比值只取决于  $L_{T1}/L_{T2}$ 。电路正常工作时, 希望占空比的变化幅度越小越好。为了让  $d_{MAX}/d_{MIN}$  尽可能小,  $L_{T1}/L_{T2}$  应尽可能大, 即应该让更多的功率经辅助支路处理。这是电路设计折衷的另一个原则。

图 3-9 主支路处理的功率百分比与  $L_{T1}/L_{T2}$  比值的函数关系Fig.3-9 Percentage of power managed by the main branch as a function of the  $L_{T1}/L_{T2}$  ratio

### 3.4 线电流的分析

比值  $L_{T1}/L_{T2}$  在线电流的谐波含量中扮演了重要的角色。

$L_{T1}/L_{T2}$  越大，在工频半周期的中部储能电容  $C_2$  要求的峰值电流越高，因此谐波含量增加。

另一方面，如果  $L_{T1}/L_{T2}$  非常小，主支路在接近线电压过零点时吸收了很高的电流。在这种情况下，谐波含量也高。

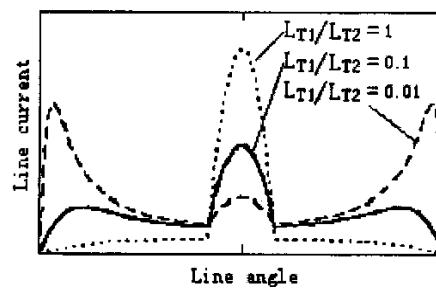

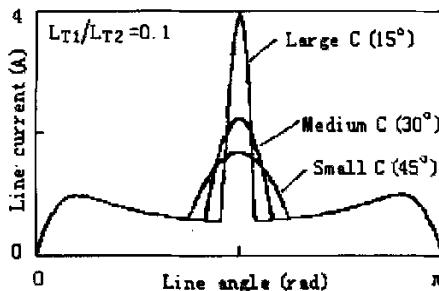

经测试，从谐波含量的角度，最好的设计发生在  $L_{T1}/L_{T2}$  约为 0.1（假设二极管  $D_5$  的导通角为 30 度）。在这点上，主支路处理的功率大约为 70%。图 3-10 显示了对不同  $L_{T1}/L_{T2}$  值下的理论线电流。

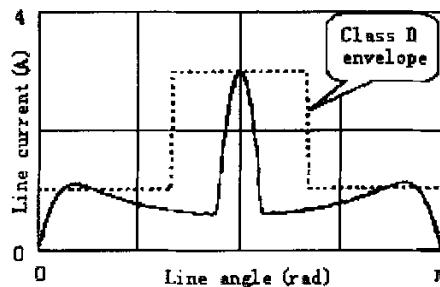

另外，由于线电流的特殊波形，经合适的设计，容易避开 IEC1000-3-2 的 Class D 标准，而在中等功率范围符合这个标准。例如，在二极管  $D_5$  通角 30 度下，而且  $L_{T1}/L_{T2}$  小于 0.2，线电流波形属于 Class A。得到的理论线电流波形如图 3-11。即使储能电容用相对高尖峰的电流充电，它也超出了 IEC1000-3-2 Class D 的包络线。这样就允许变换器处理更多的输入功率。

图 3-10 一个工频半周期中对应不同的  $L_{T1}/L_{T2}$  比值的线电流Fig.3-10 Line current for several  $L_{T1}/L_{T2}$  ratios in a line half-cycle

图 3-9 主支路处理的功率百分比与  $L_{T1}/L_{T2}$  比值的函数关系Fig.3-9 Percentage of power managed by the main branch as a function of the  $L_{T1}/L_{T2}$  ratio

### 3.4 线电流的分析

比值  $L_{T1}/L_{T2}$  在线电流的谐波含量中扮演了重要的角色。

$L_{T1}/L_{T2}$  越大，在工频半周期的中部储能电容  $C_2$  要求的峰值电流越高，因此谐波含量增加。

另一方面，如果  $L_{T1}/L_{T2}$  非常小，主支路在接近线电压过零点时吸收了很高的电流。在这种情况下，谐波含量也高。

经测试，从谐波含量的角度，最好的设计发生在  $L_{T1}/L_{T2}$  约为 0.1（假设二极管  $D_5$  的导通角为 30 度）。在这点上，主支路处理的功率大约为 70%。图 3-10 显示了对不同  $L_{T1}/L_{T2}$  值下的理论线电流。

另外，由于线电流的特殊波形，经合适的设计，容易避开 IEC1000-3-2 的 Class D 标准，而在中等功率范围符合这个标准。例如，在二极管  $D_5$  通角 30 度下，而且  $L_{T1}/L_{T2}$  小于 0.2，线电流波形属于 Class A。得到的理论线电流波形如图 3-11。即使储能电容用相对高尖峰的电流充电，它也超出了 IEC1000-3-2 Class D 的包络线。这样就允许变换器处理更多的输入功率。

图 3-10 一个工频半周期中对应不同的  $L_{T1}/L_{T2}$  比值的线电流Fig.3-10 Line current for several  $L_{T1}/L_{T2}$  ratios in a line half-cycle

图 3-11 在一个工频半周期中线电流波形和 Class D 的 envelope

Fig.3-11 Line current waveform and Class D envelope in a line half-cycle

计算这个理论线电流的谐波含量,发现更小的谐波含量是在  $L_{T1}/L_{T2}$  约等于 0.1 的时候得到的。对 100W 输出功率,谐波含量远离 IEC1000-3-2 强加的限制,所以线电流可以满足高功率水平的规范。注意由于效率的原因,这个变换器合理的功率规格是在 100W-200W。

线电流波形的尖峰部分受电容  $C_2$  的影响很大。图 3-12 表明给这个电容充电的影响。电容越高,导通角越小,谐波含量越高。不过储能电容的取值不会影响两个支路的功率分配(只取决于  $L_{T1}/L_{T2}$  比值),因为储能电容上的电压已经假设为常数,忽略低频纹波。

图 3-12 在一个工频半周期对应不同储能电容的线电流波形

Fig.3-12 Line current waveform in a line half-cycle with different capacitors (conductor angle)

另外,这个变换器储能电容(图 3-4 中  $C_2$ )的体积比常规反激变换器的电容(图 3-2 中的  $C_2$ )小,因为它需要过滤的电流纹波更小(约为 1/4)。这个优点带来的好处是体积减小和成本下降。

### 3.5 扩展到其他拓扑

提出的变换器是基于反激变换器拓扑改进的。实际上,大部分已知的拓扑(正激, Boost, SEPIC)都可以应用这个原理,只需要增加几乎同样的元件。在这些拓扑中,电路的两个输入支路共用一个开关。这些变换器的实现不需要隔离,非

常简单。

图 3-13 表明这个方法应用于 Boost 变换器成为双 Boost 变换器的电路方案。可以看出这个方案非常简单，只需要在 Boost 变换器的功率级增加两个二极管和一个电感。如果这个变换器设计工作于电感连续导通模式，串联于  $L_2$  的二极管可以去掉。

这些变换器的主要应用是电池充电器。双反激变换器适用于低功率和中等电压 (12V, 24V 和 48V) 场合。双 Boost 推荐用于高压电池充电器。

图 3-13 双 Boost 变换器的功率级

Fig.3-13 Power stage of the proposed bi-boost converter

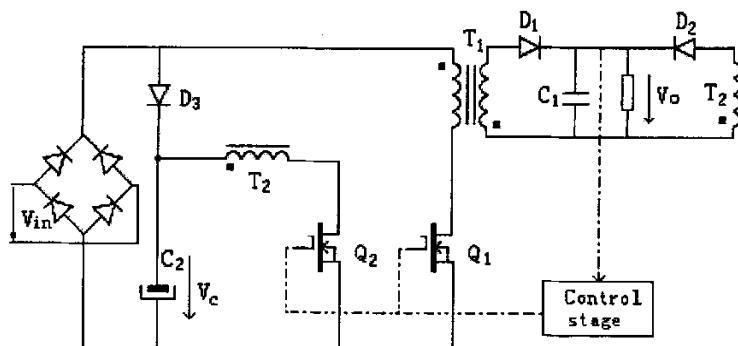

### 3.6 拓扑的改进

从图 3-4 可以看出， $T_1$  支路和  $T_2$  支路的电流均流过  $Q_1$ ，即开关管  $Q_1$  承担的电流是  $i_{T1}$  和  $i_{T2}$  的叠加，这大大增加了  $Q_1$  上的电流应力。此外，分别串联于  $T_1$  和  $T_2$  的两个二极管流过了大电流，引起较大的功率损耗。因此，对电路作如下改动：将  $T_1$  支路和  $T_2$  支路分拆，分别串联  $Q_1$  和  $Q_2$ ，同时取消串联二极管，如图 3-14 所示。

图 3-14 改进的双反激变换器的功率级

Fig.3-14 Power stage of the improved bi-flyback converter

电路经如此改进以后，去掉了两个串联在主功率回路的二极管，虽然增加了一个开关管，但是两个开关管的电流额定值较原来一个开关管低。

改进后的电路工作过程不变。原来流过  $Q_1$  的总电流现在分成两路，由两个开关管分别承担。

### 3.7 本章小结

本章介绍了单级并联双反激 AC/DC 变换器的演化过程，详细地分析了电路的工作原理，工作性能和设计要求。最后对本拓扑进行了改进。

## 第四章 电路的设计

在本电路拓扑中，两个并联的反激变换器均工作于不连续导电模式。为了合理的设计这两个变换器，首先介绍不连续模式反激变换器的基本原理，然后阐述各电路参数之间的关系和设计流程。这样，电路的电参数就基本上确定了。本章还给出了控制和驱动电路，变压器等的设计过程。

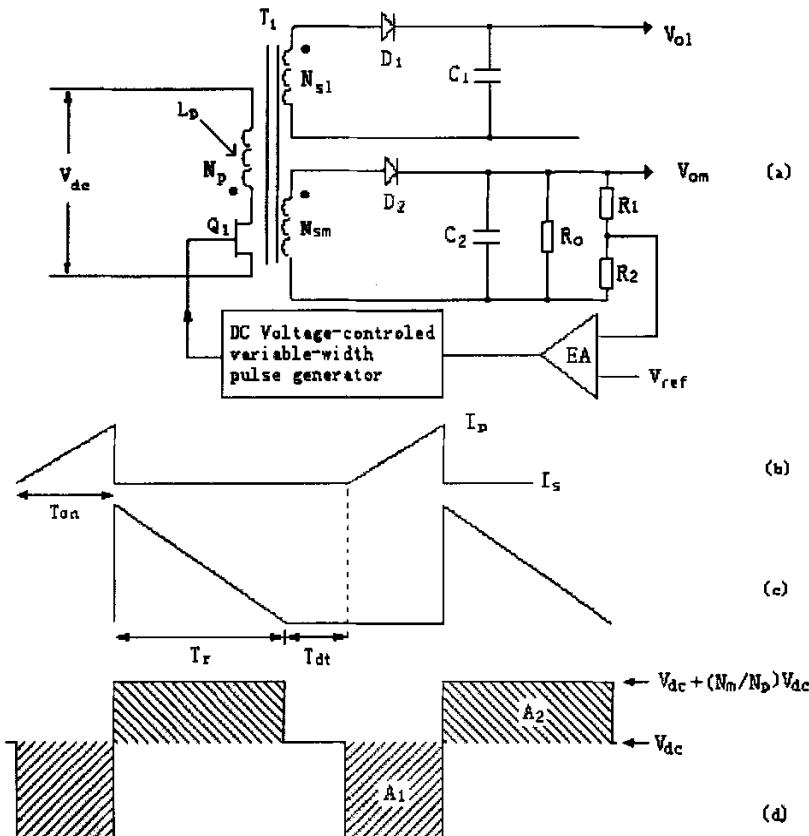

### 4.1 不连续模式反激变换器的基本原理

反激变换器在开关管导通期间，变压器储能，负载电流由输出滤波电容提供。在开关管关断期间，储存在变压器中的能量转换到负载，提供负载电流，同时给输出滤波电容充电，并补偿开关管导通期间损失的能量。

图 4-1(a)是反激变换器的基本拓扑。图中有两个输出电路，一个主输出和一个从输出。负反馈闭合环路采样主输出电压  $V_{om}$ 。 $V_{om}$  的采样值与参考值比较，输出的误差信号放大信号控制  $Q_1$  的导通时间脉冲，使得  $V_{om}$  的采样值在电网和负载变化时等于参考电压，从而稳定输出电压。从输出跟随主输出得到相应的调节。

在  $Q_1$  导通期间， $N_p$  上施加了一个固定的电压( $V_{dc}-1$ ) (这里假设开关管的导通压降是 1V)，并且流过以斜率  $dI/dt=(V_{dc}-1)L_p$  线性上升的电流，这里  $L_p$  是原边的磁性电感。在导通时间的最后，原边电流上升到  $I_p=(V_{dc}-1)T_{on}/L_p$ ，如图 4-1(b)所示。这个电流代表电感上储存的能量为

$$E = \frac{L_p(I_p)^2}{2} \quad (4-1)$$

这里  $E$  的单位为焦耳 (J)， $L_p$  的单位为亨 (H)， $I_p$  的单位为安培 (A)。

当  $Q_1$  关断，磁性电感上的电流强制使所有线圈上的极性反向。假设这时没有从次级绕组，只有主次级绕组，由于电感中的电流不能瞬时改变，在关断的瞬时，原边电流转换到次级，幅值为  $I_s=I_p (N_p/N_m)$ 。

经过几个周期以后，次级 DC 电压  $V_{om}$  已经建立。随着  $Q_1$  关断， $N_m$  上的同名端为正极性，电流从同名端流出，并且线性地下降(图 4-1(c))，斜率为  $dI_s/d_t=V_{om}/L_s$ ，其中  $L_s$  是次级电感。如果次级电流在下一个导通时间之前下降到 0，则储存在原边电感的能量全部释放到负载，称这个电路工作于不连续模式。输入功率表示为在  $Q_1$  一个导通时间  $T$  释放的能量  $E$ ，那么在这个周期的最后，从  $V_{dc}$  吸收的功率为

$$P = \frac{1/2 L_p(I_p)^2}{T} W \quad (4-2a)$$

另由于  $I_p = (V_{dc} - 1)T_{on}/L_p$ , 那么

$$P = \frac{[(V_{dc} - 1)T_{on}]^2}{2TL_p} \approx \frac{(V_{dc} T_{on})^2}{2TL_p} W \quad (4-2b)$$

从 (4-2b) 式可以看出, 只要保持  $V_{dc} T_{on}$  的积为常数, 则反馈环保持输出电压为常数。

图 4-1 不连续模式反激变换器。当  $Q_1$  导通, 所有整流二极管反向偏置, 输出电流由输出电容提供。 $N_p$  相当于一个纯电感, 负载电流在  $N_p$  中线性地建立直到峰值  $I_p$ 。当  $Q_1$  关断, 原边储存的能量  $\frac{1}{2} L I_p^2$  释放到副边, 提供负载电流, 并补充电容在  $Q_1$  导通期间损失的能量。

如果电流在下一个导通周期开始之前到达 0, 电路就是不连续的。

Fig.4-1 Discontinuities-mode flyback converter. When  $Q_1$  is on, all rectifier diodes are reverse-biased and all output capacitors supply load currents.  $N_p$  acts like a pure inductor and load current builds up linearly in it to a peak  $I_p$ . When  $Q_1$  turns off, the primary stored energy  $\frac{1}{2} L I_p^2$  is delivered to the secondaries to supply load current and replenish the charge on output capacitors which they had lost when  $Q_1$  was on. The circuit is discontinuous if the secondary current has decayed to zero before the start of the next turn-on.

## 4.2 输出电压和输入电压, 导通时间, 负载的关系

假设变换器的效率为 80%, 则

$$\text{输入功率} = 1.25(\text{输出功率})$$

$$= \frac{1.25(V_o)^2}{R_o} = \frac{1/2(L_p I_p^2)}{T}$$

从 (4-2b) 式可以看出, 最大导通时间  $\overline{T_{on}}$  发生在最小供电电压  $V_{dc}$ , 所以

$$I_p = \frac{V_{dc} \overline{T_{on}}}{L_p},$$

那么  $1.25(V_o)^2/R_o = 1/2 L_p V_{dc}^2 \overline{T_{on}}^2 / L_p^2 T$  即

$$V_o = \frac{V_{dc} \overline{T_{on}}}{2.5 T L_p} \sqrt{\frac{R_o}{2.5 T L_p}} \quad (4-3)$$

这样当  $V_{dc}$  或  $R_o$  上升时, 反馈环会通过减小  $T_{on}$  来调节输出。  $V_{dc}$  或  $R_o$  下降时, 则增加  $T_{on}$ 。

## 4.3 电路设计的流程和各参数之间的决定关系

### 4.3.1 确定原边/副边匝数比

在正确的设计流程中, 有很多参数需要确定, 首先是选择原边/主副边匝数比  $N_p/N_{sm}$ 。这个参数决定了在功率开关管上的最大关断电压应力  $\overline{V_{ms}}$  (不考虑漏感尖峰)。忽略漏感尖峰, 在最大 DC 输入  $\overline{V_{dc}}$  和 1V 整流压降下, 最大开关电压应力是

$$\overline{V_{ms}} = \overline{V_{dc}} + \frac{N_p}{N_{sm}} (V_o + 1) \quad (4-4)$$

假设漏感尖峰为  $0.3V_{dc}$ , 在保证开关管相关参数 ( $V_{ceo}$ ,  $V_{cer}$  或  $V_{cev}$ ) 的最大额定值有大于 30% 的安全裕量下,  $\overline{V_{ms}}$  的选择应尽可能低。

### 4.3.2 确保磁芯不饱和, 电路保持不连续模式

为了保证磁芯不会偏离磁滞环路, 导通伏-秒积 (图 4-1(d)中的 A1) 必须等于复位伏-秒积 (图 4-1(d)中的 A2)。假设  $Q_1$  导通压降和  $D_2$  正向导通压降均是 1V,

$$(\underline{V_{dc}} - 1) \overline{T_{on}} = (V_o + 1) \frac{N_p}{N_{sm}} T_r \quad (4-5)$$

这里  $T_r$  是复位时间，也是次级电流需要的回复到 0 的时间，参看图 4-1(c)。

为了保证电路工作于不连续模式，设置死区时间（图 4-1(c)中  $T_{dt}$ ），以便最大导通时间  $\overline{T_{on}}$ （在  $V_{dc}$  最小时发生）加上复位时间  $T_r$  时只有整个周期的 85%。留出  $0.2T$  的裕量应付  $R_o$  的意外下降，因为根据 (4-3) 式，如果  $R_o$  减小，反馈环会增加  $T_{on}$  以保持  $V_o$  为常数。

由于误差放大器设计在不连续时可以保持环路稳定，如果电路间歇性地进入连续模式，将会发生振荡。振荡发生的过程如下，DC 负载电流的增大或者  $V_{dc}$  的减少引起误差放大器增加  $T_{on}$  以保持  $V_o$  为常数，参看 (4-3) 式。 $T_{on}$  的增加导致死区时间  $T_{dt}$  的减小，甚至次级电流在  $Q_1$  下一个导通时间开始之前没有下降到 0，这就是连续模式的开始。如果误差放大器没有非常低的带宽来应付这种情况，电路就会发生振荡。为保证电路保持不连续模式，最大导通时间要满足以下关系

$$\overline{T_{on}} + T_r + T_{dc} = T$$

即

$$\overline{T_{on}} + T_r = 0.85T \quad (4-6)$$

当  $N_p/N_{sm}$  已经由 (4-4) 式根据确定的  $\overline{V_{dc}}$  和  $\overline{V_{ms}}$  计算出来时，(4-5) 式和 (4-6) 式中就只有两个未知数，那么可以从这两个等式得出

$$\overline{T_{on}} = \frac{(V_o + 1)(N_p/N_{sm})(0.85T)}{(V_{dc} - 1) + (V_o + 1)(N_p/N_{sm})} \quad (4-7)$$

### 4.3.3 由最小输出电阻和最小 DC 输入电压确定的原边电感

从 (4-3) 式，原边电感为

$$L_p = \frac{R_o}{2.5T} \left( \frac{V_{dc} \overline{T_{on}}}{V_o} \right)^2 = \frac{(V_{dc} \overline{T_{on}})^2}{2.5T P_o} \quad (4-8)$$

### 4.3.4 开关峰值电流，最大电压应力

如果是双极性三极管，在峰值电流为

$$I_p = \frac{V_{dc} \overline{T_{on}}}{L_p} \quad (4-9)$$

时应该有可接受的高增益。这里  $V_{dc}$  是确定的。 $\overline{T_{on}}$  由 (4-7) 式计算得出,  $L_p$  由 (4-8) 式计算得出。

如果是 MOSFET, 应该将从 (4-9) 式得出的计算值增大 5-10 倍作为峰值额定电流, 以便它的导通电阻足够低, 产生低压降。

### 4.3.5 原边和副边均方根电流

原边电流是具有峰值  $I_p$  (由 (4-9) 式计算得出) 的三角波。它的均方根值是

$$I_{rms(primary)} = \frac{I_p}{\sqrt{3}} \sqrt{\frac{\overline{T_{on}}}{T}} \quad (4-10)$$

这里  $I_p$  和  $\overline{T_{on}}$  由 (4-9) 式和 (4-7) 式给出。

副边电流是峰值为  $I_s = I_p (N_p/N_s)$  的三角波, 导通时间为  $T_r$ , 原边/副边匝数比  $N_p/N_s$  由 (4-4) 式给出,  $T_r = (T - T_{on})$ 。则次级均方根电流为

$$I_{rms(secondary)} = \frac{I_p (N_p/N_s)}{\sqrt{3}} \sqrt{\frac{T_r}{T}} \quad (4-11)$$

知道了均方根电流, 就可以确定变压器原边和副边的线径。按 500 圆密耳/安培计, 将上述计算的均方根值乘以 500, 即得到导线的圆密耳值。

### 4.3.6 输出滤波电容的确定

输出滤波电容根据输出电压纹波的要求来确定。必须保证在最大输出电流 ( $I_{o(max)}$ ) 时电压纹波 ( $\Delta V$ ) 仍然在规定范围内

$$C_o = \frac{I_{o(max)} (T - T_{on})}{\Delta V} \quad (4-12)$$

由于在开关管关断的瞬间, 副边峰值电流流过输出电容的等效串联电阻  $R_{esr}$ , 引起电压降落。因此, 实际中  $C_o$  的取值比计算值大。

## 4.4 根据以上结论计算本电路电参数

根据以上推导公式, 就可以对两个并联的反激变换器进行设计。由于两个之路处理的功率有分配关系, 首先需要确定功率在两个之路上的分配, 即确定  $L_{T1}/L_{T2}$  的比值大小。

第三章已经说明, 从谐波含量的角度, 最好的设计发生在  $L_{T1}/L_{T2}$  约为 0.1。在这点上, 主支路处理的功率大约 70%。但是实际电路中这样的选择却是不可行的。由于此时  $d_{max}/d_{min} = 3.32$ , 占空比需要在一个很大的范围内周期性的变化。在保证两个变换器都工作在不连续模式的情况下, 占空比的大范围变化造成电路

的工作条件非常恶劣(参考第五章仿真分析)。如果取  $L_{T1}/L_{T2}$  为 0.2, 则主支路处理的功率为 60%,  $d_{max}/d_{min} = \sqrt{1 + \frac{L_{T2}}{L_{T1}}} = \sqrt{6} = 2.45$ 。在这种情况下,  $d_{min}$  可以设计的比较大, 而  $d_{max}$  可以设计的比较小。占空比小范围变化的好处是大大降低了电路的电流应力和电压应力。

另一个影响谐波含量的因素是中间储能电容。如果储能电容取值大, 则中间电流尖峰大, 不利于 PF; 如果储能电容取值太小, 则两头电流大, 也不利于 PF。仿真表明, 32V, 3A 时, 150uF 是较好的选择, 充电角度为 28.9 度。

由于假设变压器  $T_2$  的输入电压是恒定的, 设计较为方便, 因此首先确定  $T_2$  原边电感  $L_{T2}$ 。当  $L_{T2}$  确定以后, 变压器  $T_1$  原边电感  $L_{T1}$  可根据比值关系确定。

最大导通时间  $\overline{T_{on}}$  的设定。仿真表明, 若  $\overline{T_{on}}$  设得过大, 为了保证变换器工作于 DCM, 变压器  $T_2$  副边电流将非常大, 原边  $Q_2$  电压应力大。

设最大导通时间为  $5 \times 10^{-6}$  s, 根据(4-7)式

$$\overline{T_{on}} = \frac{(V_o + 1)(N_p/N_{sm})(0.85T)}{(V_{dc} - 1) + (V_o + 1)(N_p/N_{sm})} = \frac{(32 + 1) \times n_2 \times 8.5 \times 10^{-6}}{(127 - 1) + (32 + 1) \times n_2} = 5 \times 10^{-6} \quad (4-13)$$

解得  $n_2 = 5.45$ , 取  $n_2 = 5$

则根据 (4-8) 式

$$L_{p2} = \frac{R_o}{2.5T} \left( \frac{V_{dc} \overline{T_{on}}}{V_o} \right)^2 = \frac{(V_{dc} \overline{T_{on}})^2}{2.5T P_o} = \frac{(127 \times 5 \times 10^{-6})^2}{2.5 \times 10 \times 10^{-6} \times 96} = 168uH \quad (4-14)$$

取  $L_{p2} = L_{T2} = 200uH$ , 则  $L_{p1} = L_{T1} = 0.2L_{p2} = 40uH$

对于变压器  $T_1$ , 取  $n_1 = N_{p1} : N_{s1} = 1 : 0.8$

正常工作时, 占空比不断周期性变化, 相关的电流电压波形也呈周期性变化, 以下按照变换器在一个周期中的最不利情况计算。

(1) 原副边匝数比以及开关管电压应力

$T_1$ :  $n_1 = 1 : 0.8$

$T_2$ :  $n_2 = 5 : 1$

根据 (4-4) 式

$Q_1$  最大电压应力

$$\overline{V_{ms1}} = \overline{V_{dc}} + \frac{N_{p1}}{N_{s1}} (V_o + 1) = 135 \times \sqrt{2} + \frac{1}{0.8} (32 + 1) = 232.2V \quad (4-15)$$

$Q_2$  最大电压应力

$$\overline{V_{ms2}} = \overline{V_{dc}} + \frac{N_{p2}}{N_{s2}} (V_o + 1) = 135 \times \sqrt{2} + \frac{5}{1} (32 + 1) = 355.9V \quad (4-16)$$

## (2) 开关峰值电流和均方根电流

根据 (4-9) (4-10) 和 (4-11) 式

$$I_{p2} = \frac{V_{dc} \overline{T}_{on}}{L_{p2}} = \frac{127 \times 5 \times 10^{-6}}{200 \times 10^{-6}} = 3.175A \quad (4-17)$$

$$I_{p1} = \frac{V_{dc} T_{on}}{L_{p2}} = \frac{127 \times 2.04 \times 10^{-6}}{200 \times 10^{-6}} = 6.477A \quad (4-18)$$

$$I_{rms2(primary)} = \frac{I_{p2}}{\sqrt{3}} \sqrt{\frac{\overline{T}_{on}}{T}} = \frac{3.175}{\sqrt{3}} \sqrt{0.5} = 1.296A \quad (4-19)$$

$$I_{rms2(secondary)} = \frac{I_{p2} (N_{p2} / N_{s2})}{\sqrt{3}} \sqrt{\frac{T_r}{T}} = \frac{3.175 \times 5}{\sqrt{3}} \sqrt{0.35} = 5.422A \quad (4-20)$$

$$I_{rms1(primary)} = \frac{I_{p1}}{\sqrt{3}} \sqrt{\frac{\overline{T}_{on}}{T}} = \frac{6.477}{\sqrt{3}} \sqrt{0.204} = 1.689A \quad (4-21)$$

$$I_{rms1(secondary)} = \frac{I_{p1} (N_{p1} / N_{s1})}{\sqrt{3}} \sqrt{\frac{T_r}{T}} = \frac{6.477 \times 1.25}{\sqrt{3}} \sqrt{0.204 \times 0.8} = 1.888A \quad (4-22)$$

将计算值乘以 500 得圆密尔值，即可以确定变压器原边和副边的线径

## (3) 输出滤波电容

根据 (4-12) 式

$$C_o = \frac{I_{o(max)} (T - T_{on})}{\Delta V} = \frac{3 \times (5 \times 10^{-6})}{0.8} = 18.75 \times 10^{-6} \mu F \quad (4-23)$$

实际取值比这个大很多

## 4.5 控制和驱动电路的设计

## 4.5.1 电压电流型 PWM 集成控制器 UC3823

UC3823 系列 PWM 控制集成电路是高频开关电源应用的最佳选择。精心的设计缩短了通过比较器和逻辑电路的传播延迟时间，增大恶劣带宽和误差放大器的输入输出相应的转换速率。这种电路既能用于电流型控制也能用于电压型控制，具有输入电压前馈功能。

它的保护电路部分包括一个限流比较器、与 TTL 电平兼容的关闭端口和一个可兼做最大占空比钳位的软启动端。为了环路的稳定性减少输出电压纹波，逻辑电路完全由锁存器控制。带有 800mV 滞后电压的欠压锁定电路保证了低启动电流。在欠压锁定期间，电路是高阻抗输出。电流参考端 (11 脚) 是一个输入到电流限制比较器的直流电压。

这种器件专门设有双推挽输出以便对功率 MOS 栅极之类的电容性负载源出

或吸入高峰值电流。它的导通定义为高电平。

### (1) 主要特点

- 兼顾电压型、电流型控制；

- 开关频率高达 1.0MHz；

- 50ns 的传输延迟时间；

- 大电流双推挽输出 (1.5A 峰值) 功能；

- 宽频带误差放大器；

- 完全锁存的逻辑电路具有双脉冲抑制；

- 逐个脉冲电流抑制；

- 软启动/最大占空比抑制；

- 欠压锁定电路具有滞后，低启动电流 (1.1mA)。

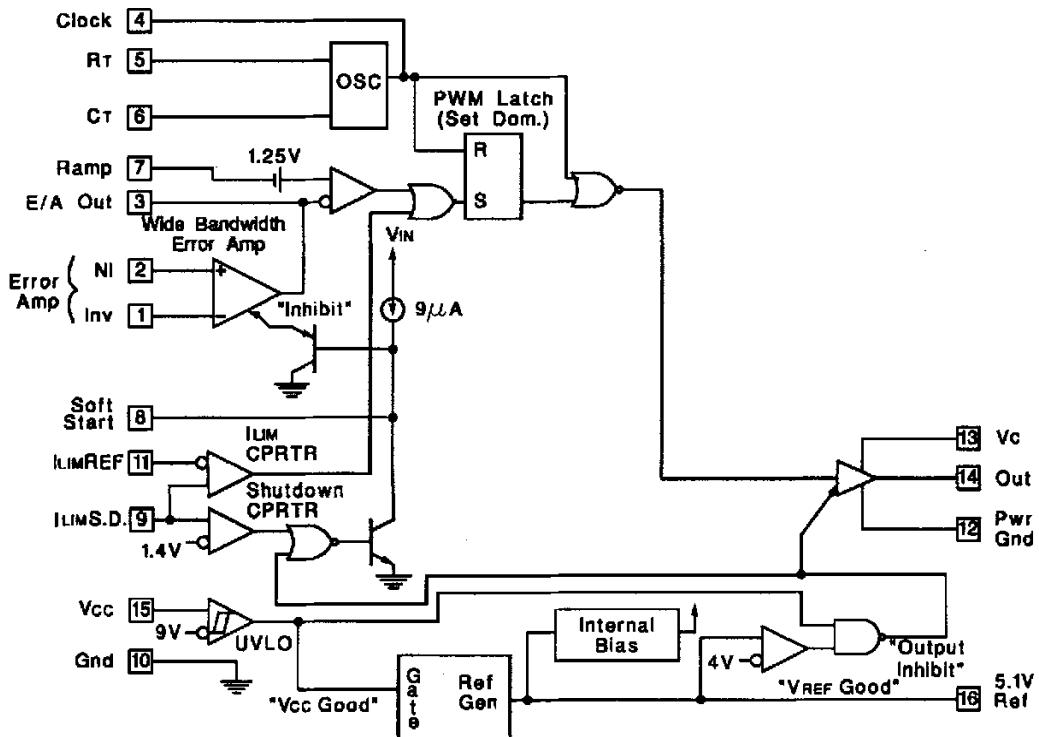

### (2) 功能原理框图与引出端功能

UC1823 的内部原理框图如图所示。它的引出端功能为：1 端为误差放大器的反相输入端；2 端为误差放大器的同相输入端；3 端为误差放大器输出端；4 端为振荡器输出端；5 端接定时电阻  $R_T$ ；6 端接定时电容  $C_T$ ；7 端为电流型控制与电压型控制的选择端，当该端与 6 端相连时，电路工作在电压型控制状态，当在该端加一电流波形时，电路就工作在电流型控制状态；8 端为软启动端；9 端为限流关断端；10 端为地端；11 端限流参考电平输入端；12 端为输出地；13 端接集电极电源  $U_C$ ；14 端为 B 输出；15 端为供电电源  $V_{CC}$ ；16 端为基准电压源输出端。

### (3) 主要电气参数

电源电压 (13, 15 端) ..... 30V

输入电流，源出或吸入 (14 端)

直流 ..... 0.5A

脉冲 (0.5μs) ..... 2.0A

模拟输入

(1, 2, 7, 8, 9, 11 端) ..... 0.3V 至 +6V

时钟输出电流 (4 端) ..... 5mA

误差放大器输出电流 (3 端) ..... 5mA

软启动吸入电流 (8 端) ..... 20mA

振荡器充电电流 (5 端) ..... 5mA

功率耗散 ( $T_A = 60^\circ\text{C}$ ) ..... 1W

贮存温度范围 ..... -65°C ~ 150°C

引线温度 (焊接, 10s) ..... 300°C

注意：所有电压以地端 10 为参考，电流以指向芯片接线端为正。

图 4-2 UC3823 内部原理框图与引出端功能

Fig.4-2 Block diagram of UC3823

在仿真中用 UC3825 来代替 UC3823。UC3825 的基本原理和 UC3823 一致, 不同的是误差放大器输出电平与锯齿波信号比较获得 PWM 控制信号之后, 没有直接送到输出, 而是经分频后再送到两路输出, 这样实现了两路交错的输出占空比信号, 但是就有  $d < 50\%$  的限制。将 UC3825 的两个输出进行逻辑与, 则相当于 UC3823。

## 4.5.2 交错控制的实现

为了减小输出电压纹波, 希望功率级两个并联支路交错工作, 而且两路交错信号不受  $d < 50\%$  的限制。因此, 需要对 UC3823 的输出占空比信号进行处理, 产生与原信号相差 180 度相位的同样的占空比信号。

### 4.5.2.1 实现占空比信号延时 5us 的原理

首先用 UC3823 获得单个占空比信号。电路正常工作时, 这个信号周期性地变化。由于开关周期是恒定的 10us, 只要对已获得的占空比信号延时 5us, 相当于移相 180°, 即可得到另一个交错控制信号。具体的实现过程如下

为了延时 5us, 而且保持占空比信号不变, 则需要采样的信息包括上升沿时刻, 延时时间和下降沿时刻。经过逻辑门电路和延时处理, 可获得需要的信号。延时

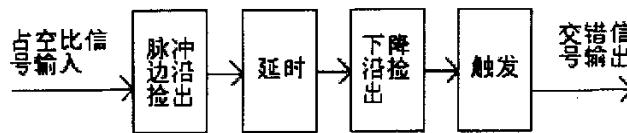

电路的原理框图如下所示。

图 4-3 获得交错信号的原理图

Fig.4-3 Interleaved signal process

### 各功能框图的实现

#### (1) 脉冲边沿检出电路

图 4-4 所示是三个脉冲边沿检出电路及其对应的输入、输出波形。

图 4-4(a)由一个施密特触发与非门 (1/4MM74HC132) 和一个 RC 微分电路构成。当输入脉冲上升沿到达时, 微分电路 R 上出现正尖脉冲, 从而与非门输出一个负的窄脉冲。所以该电路对输入脉冲的每个上升沿都输出一个负脉冲, 其宽度由 R、C 的参数决定, RC 不能太大, 以保证相邻的两个输入脉冲产生两个负脉冲输出; 若取 C>500pF, 则应在与非门输入端串联数 k 欧的限流保护电阻。

图 4-4(b)与图 4-4(a)类似, 用来检测输入脉冲的下降沿。

图 4-4(c)由三片二输入与非门 (74HC00) 构成。输入脉冲由 A 点加入, 经反相得到  $\bar{A}$ , 再经 8 个反相器延时得到  $\bar{B}$ , 将  $\bar{B}$  反相, 得到 B。A 与  $\bar{B}$  经与非门得到 C,  $\bar{A}$  与 B 经与非门得到 D。各点波形如图所示。当输入波形 A 出现正跳变, C 输出一个负脉冲; 当输入波形 A 出现一个负跳变, D 输出一个负脉冲。从而分别检出了上升沿和下降沿。

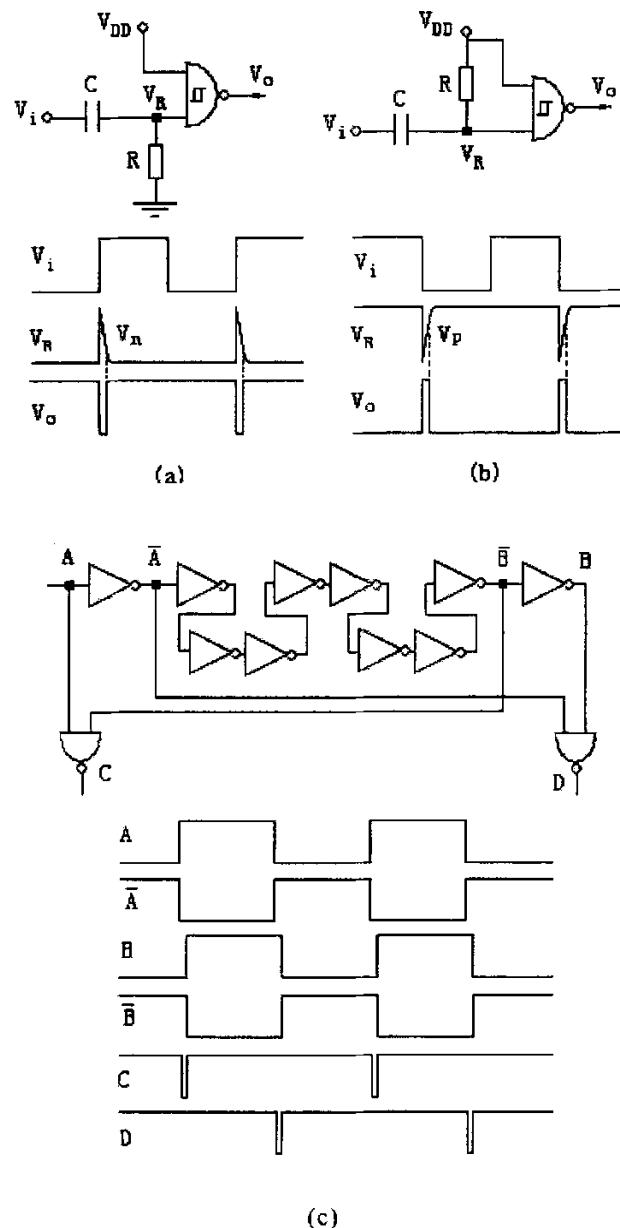

#### (2) 利用 555 型定时器实现事件定时

检出占空比信号的上升沿和下降沿以后, 将检出信号输入延时电路, 实现 5us 的延时。555 定时器具有价廉、通用的特点, 市场上供货方便, 在这里使用 555 定时器。电路的设计要求是, 将检测出的上升沿或下降沿信号送入由 555 构成的延时电路, 555 输出在触发以后延时 5us。采用的电路如图 4-5 所示。由 555 电路的定时关系, 可求得定时元件值如下

$$R_A C = \frac{T}{1.1} = \frac{5\mu s}{1.1} = 4.545 \times 10^{-6} \quad (4-24)$$

选择电容 C=1nF, 则定时电阻值为

$$R_A = \frac{4.545 \times 10^{-6}}{1 \times 10^{-9}} = 4.545 \times 10^3 \Omega \quad (4-25)$$

图 4-4 脉冲边沿检出电路

(a)上升沿检出电路; (b)下降沿检出电路; (c)两种边沿检出电路

Fig. 4-4 Pulse edge checkout circuit

(a) Rising edge checkout; (b) Trailing edge checkout; (c) Both edge checkouts

图 4-5 利用 555 型定时器实现事件定时

Fig.4-5 Timing circuit using 555

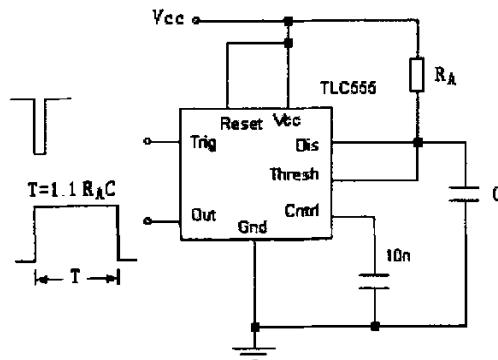

### (3) 触发

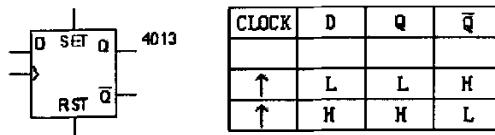

边沿触发的 D 触发器，在时钟转换时将数据输入传送到输出端 Q 和  $\bar{Q}$ 。如 CMOS CD4013 为正沿触发的 D 触发器。图 4-6 给出了正沿触发的 D 触发器的逻辑符号和真值表。事实上，在本电路应用中，D 输入和 Clock 端悬空，只接置 1 和置 0 端。

图 4-6 正边沿触发 D 触发器

Fig.4-6 D flip-flop and its logic scheme

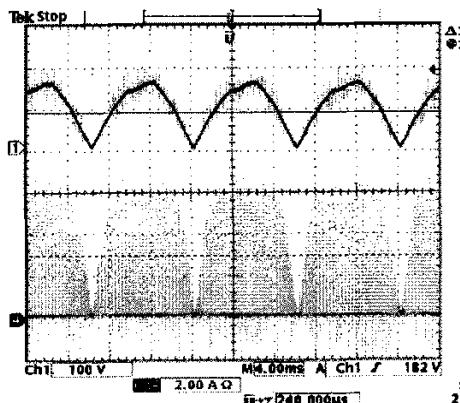

#### 4.5.2.2 电路全图和关键点仿真和试验波形

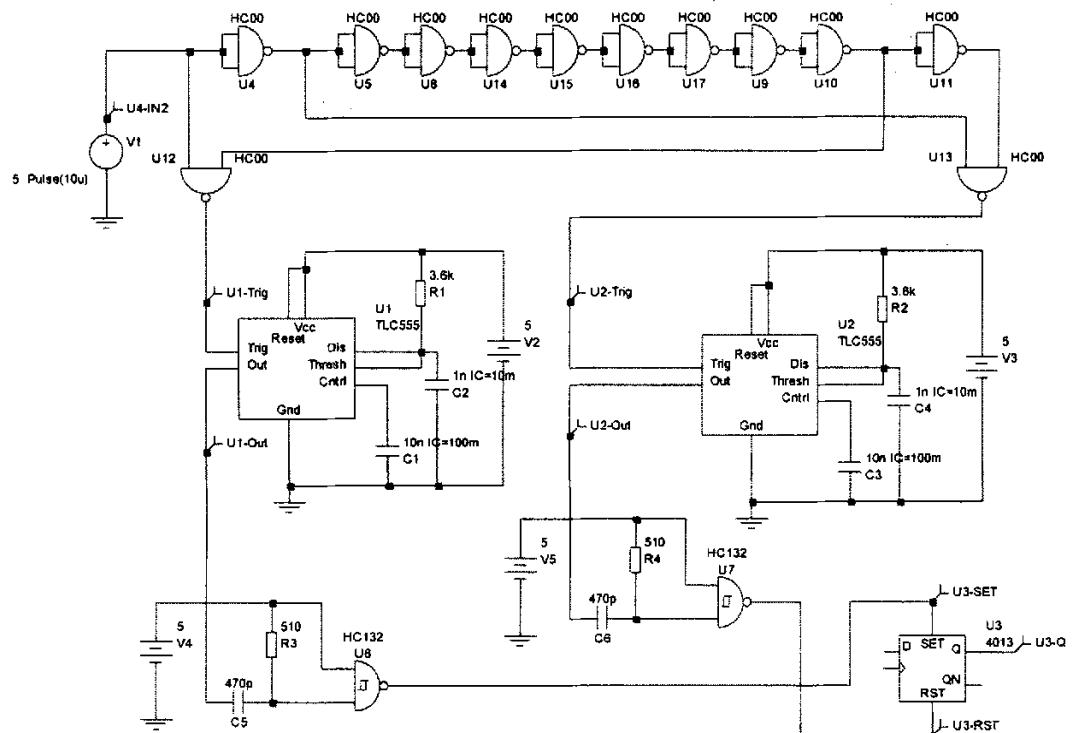

仿真电路全图，仿真关键波形图和分别如图 4-7 和 4-8 所示。

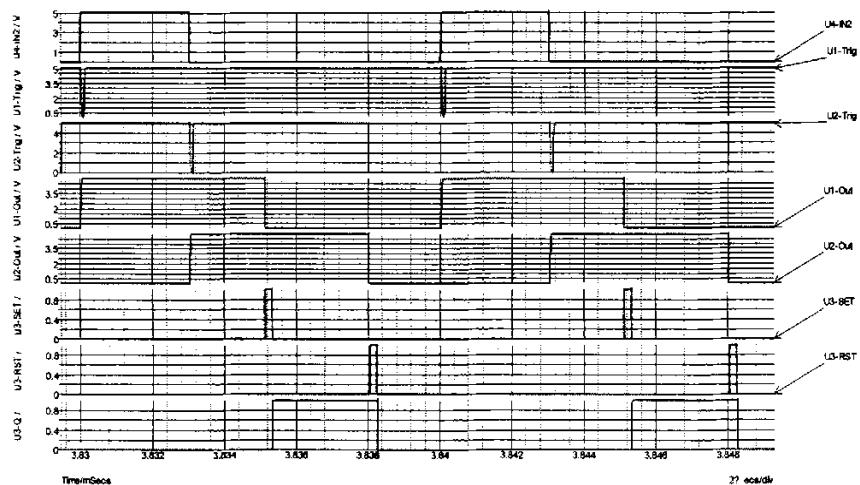

实验测试关键波形如图 4-9 所示。图 4-9(a)是输入占空比信号  $d > 50\%$  的输入和输出波形；图 4-9(b)是输入占空比信号  $d < 50\%$  的输入和输出波形。从这两个测试波形可以看出，延时电路工作正常，无论  $d > 50\%$  还是  $d < 50\%$ ，都可以将正常工作时不断变化的占空比信号延时 5us 形成交错信号。

图 4-7 延时电路全图

Fig.4-7 Timing delay circuit

图 4-8 各关键点仿真波形

Fig.4-8 Simulation waveforms

图 4-9 输入 (Ch1) 和输出 (Ch2) 的测试波形

Fig.4-9 Test waveforms of input (Ch1) and output (Ch2)

#### 4.5.3 驱动电路的设计

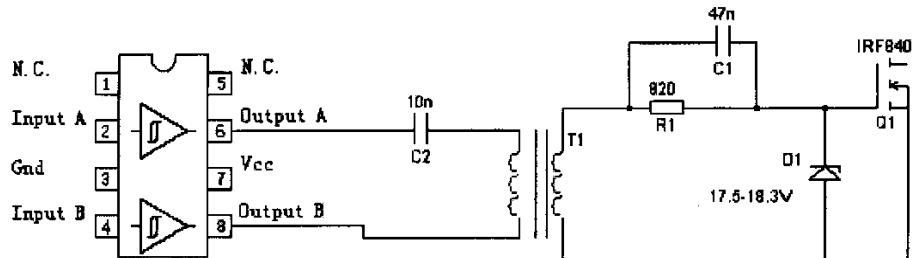

为提高电路的效率及功率器件工作的可靠性, 一般需要将控制电路的输出信号加以功率放大。本文采用 MC34152 加隔离变压器驱动的方法来设计驱动电路, 如图 4-10 所示。

MC34152 的外围电路简单, 应用方便。它是 8 管脚的同相推挽驱动芯片。2 脚与 4 脚为两路控制信号输入, 经过芯片内部的推挽放大, 直接输出同相的两路驱动信号(7 脚及 5 脚)。为使芯片更加稳定地工作, 一般在芯片的电源端并联一个滤去高频干扰的瓷片电容和一个滤去低频干扰的电解电容。

当电路的功率较大及工作频率较高时, 一般要将控制电路与主电路隔离。本文采用隔离变压器来实现隔离。MC34152 的输出经一隔直电容后输入到隔离变压器的原边。

本文所设计的驱动电路简单可行, 驱动波形比较理想: 有快速的上升沿, 并有一定的过冲, 以加速开通, 减小了开通损耗; 同时, 有反偏截止电压, 提供了足够的反相门极驱动, 减小了下降时间。

图 4-10 驱动电路

Fig.4-10 Driving circuit

## 4.6 变压器的设计

在 4.4 节中，已经设计了变压器的一些参数，包括原边副边匝数，线径。现在需要进一步确定变压器磁芯和绕制参数。

由于两路并联输出， $T_2$  支路在过零点附近完全承担全部功率， $T_1$  支路在输入电压峰值附近承担主要功率，设计需满足以下要求：

- (1)  $T_2$  可独立承担全部功率，且工作于 DCM，即  $T_2$  按 96W 标准来设计。

- (2)  $T_1$  在过零点附近不承担功率，在输入电压峰值附近承担主要功率。 $96W \cdot 0.6 = 57.6W$ 。应按照 60W 以上进行设计。

选择磁芯型号。磁芯的选择取决于设计本身的考虑和设计者个人的偏好。表 4-1 给出了磁芯型号和通过功率的关系总览。这可以便于设计者作出初始的选择。每个磁芯型号都被开发应用于特定的应用，因此他们都有优点和缺点，这依赖于变换器类型，绕制技术等等。

表 4-1 100 kHz 开关频率下通过功率对应的磁芯型号

| POWER RANGE<br>(W) | CORE TYPE                                                                     |

|--------------------|-------------------------------------------------------------------------------|

| < 5                | RM4; P11/7; T14; EF13; U10                                                    |

| 5 to 10            | RM5; P14/8                                                                    |

| 10 to 20           | RM6; E20; P18/11; T23; U15; EFD15                                             |

| 20 to 50           | RM8; P22/13; U20; RM10; ETD29; E25; T26/10; EFD20                             |

| 50 to 100          | ETD29; ETD34; EC35; EC41; RM12; P30/19; T26/20; EFD25                         |

| 100 to 200         | ETD34; ETD39; ETD44; EC41; EC52; RM14; P36/22; E30; T56; U25; U30; E42; EFD30 |

| 200 to 500         | ETD44; ETD49; E55; EC52; E42; P42/29; U37                                     |

| > 500              | E65; EC70; U93; U100                                                          |

根据表 4-1，变压器  $T_1$  和  $T_2$  均采用磁芯 RM12。RM12 的有效磁芯参数如表 4-2 所示。

表 4-2 RM12 的有效磁芯参数

| SYMBOL        | PARAMETER        | VALUE        | UNIT      |

|---------------|------------------|--------------|-----------|

| $\Sigma(I/A)$ | core factor (C1) | 0.388        | $mm^{-1}$ |

| $V_e$         | effective volume | 8340         | $mm^3$    |

| $l_e$         | effective length | 56.6         | mm        |

| $A_e$         | effective area   | 146          | $mm^2$    |

| $A_{min}$     | minimum area     | 125          | $mm^2$    |

| $m$           | mass of set      | $\approx 45$ | g         |

设计变压器  $T_1$  和  $T_2$

对于  $T_2$ , 按照  $\overline{T_{on}} = 5 \times 10^{-6} s$  计算

$$N_p = \frac{V_s T_{on}}{\Delta B_{ac} \cdot A_e} = \frac{155 \times 5}{0.25 \times 146} = 21.23 \quad (4-26)$$

取  $N_p = 25$  匝, 则  $N_s = 5$  匝。

对于  $T_1$ , 如果按照  $\overline{T_{on}} = 5 \times 10^{-6} s$  计算

$$N_p = \frac{V_s T_{on}}{\Delta B_{ac} \cdot A_e} = \frac{155 \times 5}{0.25 \times 146} = 21.23 \quad (4-27)$$

因为最大值  $\overline{T_{on}}$  时,  $T_1$  承担功率为 0, 因此 (4-27) 式计算值偏大。如果按最小值

$$\underline{T_{on}} = \frac{5}{2.45} = 2.04 \times 10^{-6} s \text{ 计算}$$

$$N_p = \frac{155 \times 2.04}{0.25 \times 146} = 8.66 \quad (4-28)$$

综合 (4-27) 和 (4-28) 式, 取  $N_p = 15$  匝, 则  $N_s = 15 \times 0.8 = 12$  匝

确定线径。根据 (4-19)、(4-20)、(4-21) 和 (4-22) 式, 将均方根电流乘以 500, 即得到圆密尔值。根据圆密尔值查得相应的线径。

|       |    |          |                      |     |       |

|-------|----|----------|----------------------|-----|-------|

| $T_1$ | 原边 | $1.689A$ | $\times 500 = 844.5$ | 圆密尔 | AWG20 |

|       | 副边 | $1.888A$ | $\times 500 = 944$   | 圆密尔 | AWG20 |

| $T_2$ | 原边 | $1.296A$ | $\times 500 = 648$   | 圆密尔 | AWG22 |

|       | 副边 | $5.422A$ | $\times 500 = 2711$  | 圆密尔 | AWG16 |

实际绕制参数。

|       |                     |                    |                     |

|-------|---------------------|--------------------|---------------------|

| $T_1$ | 原边                  | AWG19              | 15 圈一层              |

|       | 副边                  | AWG24 $\times 2$   | 12 圈一层              |

|       | $L_p = 39.95 \mu H$ | $L_k = 1.06 \mu H$ | $L_s = 24.62 \mu H$ |

$$N_p: N_s = 15: 12$$

$T_2$  采用三明治绕法

$$\text{原边 } AWG26 \times 3 \quad 15 \text{ 圈里层} \quad 12 \text{ 圈外层}$$

副边 5 层铜皮

$$L_p = 204.1 \mu H \quad L_k = 3.51 \mu H \quad L_s = 8.40 \mu H$$

$$N_p: N_s = 25: 5$$

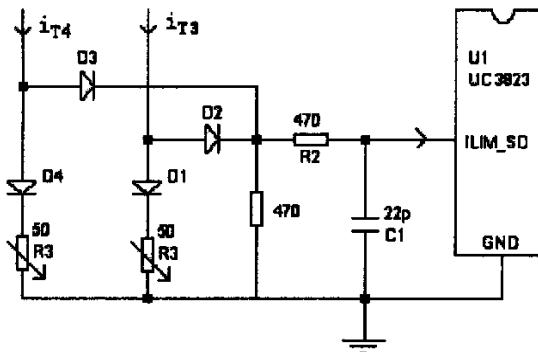

## 4.7 限流电路的设计

为了防止在变换器启动或者重载的情况下发生过流，需要对电路进行限流。将串联在输出端的电流互感器感应到的电流信号送入控制芯片的电流限制端，可以实现限流的目的。合理的调节电路参数，可以设定限流的幅值。电路图如图 4-11 所示。

图 4-11 限流电路

Fig.4-11 Current limited circuit

## 4.8 本章小结

本章给出了单级并联双反激 AC/DC 变换器详细的设计过程。根据反激变换器的参数决定关系和变换器的规格，确定了变压器原边电感、占空比决定关系、变换器的电压电流参数、输出滤波电容等参数。详细介绍了控制和驱动电路、变压器和限流电路的设计过程。

## 第五章 仿真与实验

### 5.1 仿真软件SIMetrix/SIMPLIS简介

SIMetrix 是一种数字-模拟混合信号电路仿真器，具有使用简单，仿真精度高，速度快的特点。它基于两个公开的程序 SPICE 和 XSPICE 开发。虽然起源于这两个程序，但是只有 30%的应用代码可以从他们中找到，而大量的仿真代码都是全新的，或者是为了提供新的分析特性和解决收敛问题而重新编写。另外 SIMetrix 包括原理图通道和波形特性分析，这是原始 SPICE 程序所不具有的。

SIMPLIS 是专用于开关功率系统快速建模的电路仿真器。它是分段线性系统仿真 (SIMulation for Piecewise Linear System) 的简写。它在 SIMetrix 的高级版本 SIMetrix/SIMPLIS 上提供。和 SPICE 一样，SIMPLIS 是元件级的仿真器。但是在仿真开关电路时它比 SPICE 快 10~50 倍。它使用一系列直线段来对器件建模来达到这个速度，而 SPICE 需要求解非线性方程来建模。这样 SIMPLIS 在仿真速度和精度上折衷，在大多数场合，特别是在高水平仿真开关功率系统时，仿真精度和细节的损失并不重要。

### 5.2 仿真电路原理图

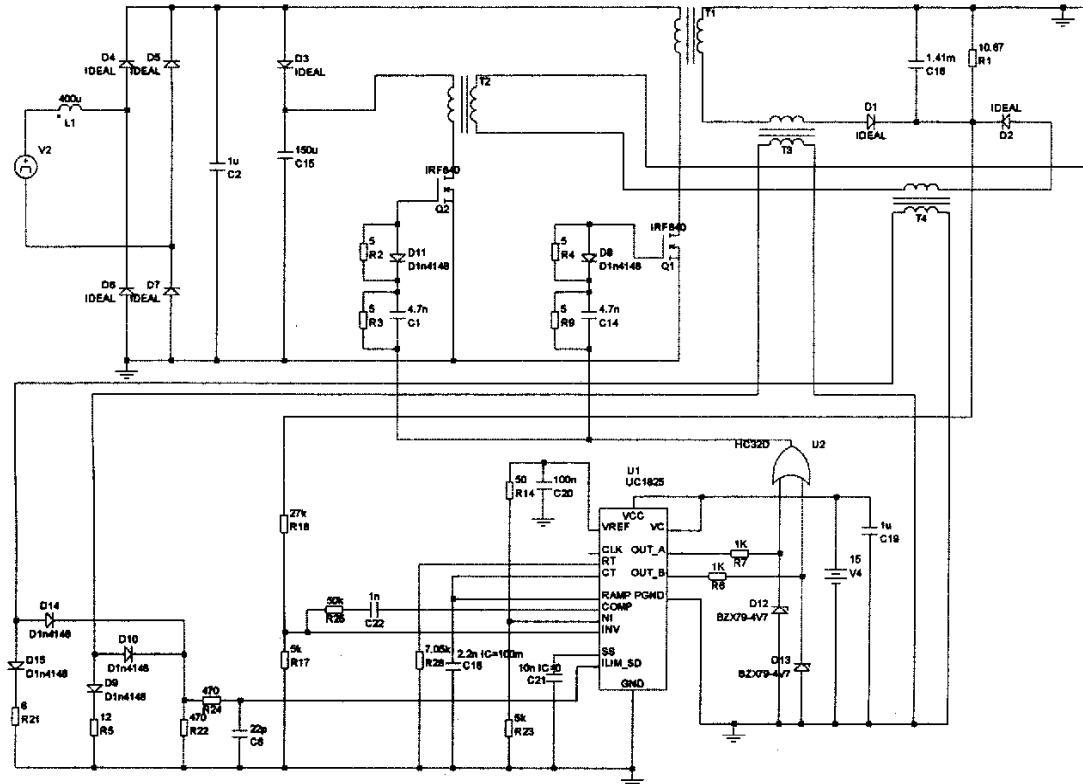

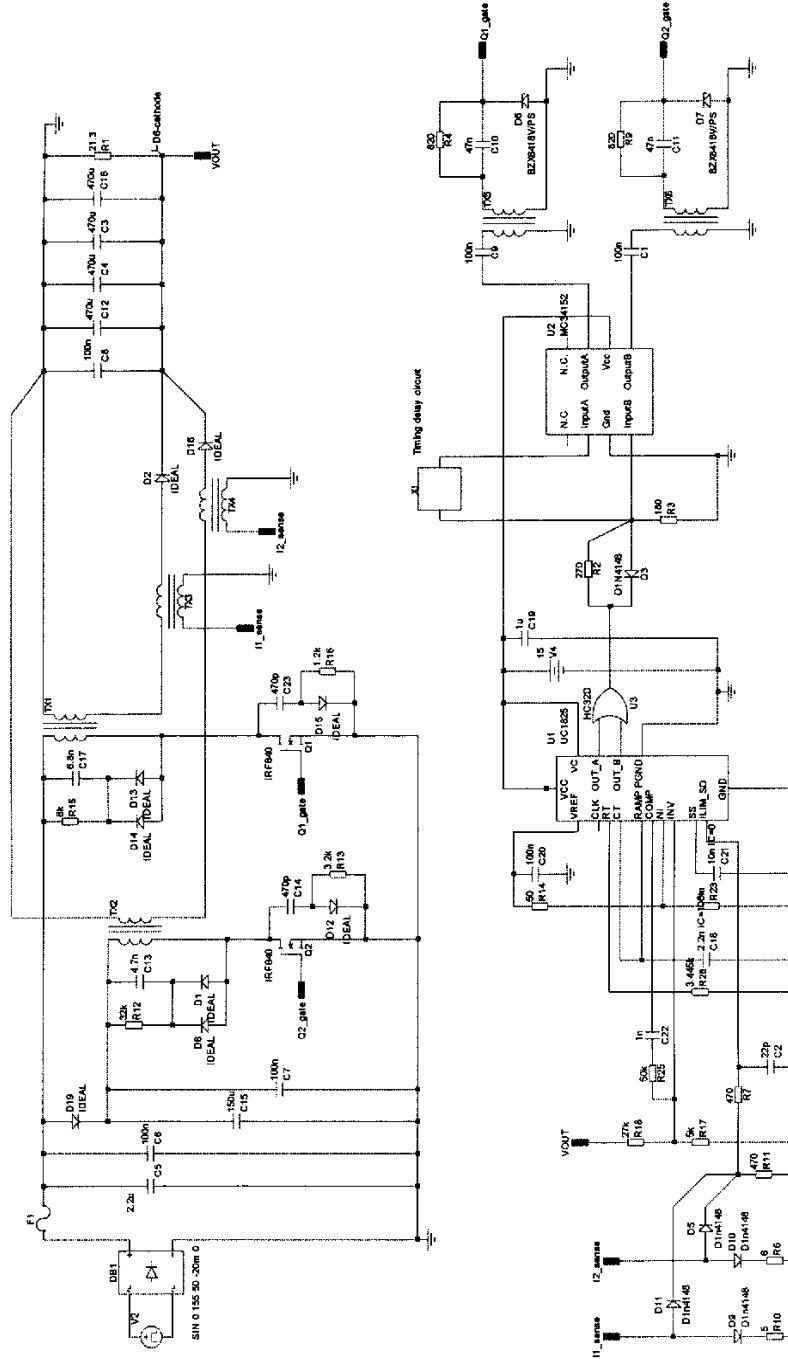

仿真原理图如图 5-1 所示。

在整流桥之后并联了一个小电容，这个小电容的作用是向变压器  $T_1$  提供高频电流。因为整流桥二极管是低频的，而  $T_1$  工作于高频状态，它不能从电网经整流桥二极管抽取高频电流。这个小电容的加入对输入电压波形不会产生很大的影响。另外仿真中采用理想二极管进行整流，无法得到输入电流的平均波形，所以在整流桥前面加入一个大电感，实际电路中这个电感是不需要的。

仿真中控制芯片采用 UC3825。UC3825 可以实现两路交错输出信号，每个信号的占空比不超过 50%。但是电路工作的过程中的要求占空比不断地周期性变化，可能需要突破 50%，因此 UC3825 不能满足要求。为了克服这个缺点，将 UC3825 的两路输出逻辑与，则占空比可以突破 50% 的限制。实际电路中采用的控制芯片是 UC3823。UC3823 与 UC3825 的内部结构功能基本相同。UC3823 只有一路输出信号，这个占空比信号可以从 0 到 100% 变化。

从 UC3825 逻辑与之后获得的占空比信号，同时控制开关管  $Q_1$  和  $Q_2$ 。即  $Q_1$  和  $Q_2$  同时开通和关断。这种工作状态的缺点是两个并联支路同时给副边提供能量，输出电压纹波较大。实际电路中采用交错控制，即将 UC3823 的输出信号处

理得到另外一路交错信号来控制另一个开关管。这样两个并联支路交错地给负载供电，有利于减小输出电压纹波，对减小电路的 EMI 也有好处。仿真中主要是看原边的电压电流情况，所以两个开关管仍然采用同一个控制信号，这不影响仿真效果。

电流互感器  $T_3$  和  $T_4$  串联在反激变换器的输出。 $T_3$  和  $T_4$  将感应到的电流信号经处理转换成电压信号送到控制芯片的电流限制端，起过流保护的作用。

图 5-1 仿真原理图

Fig.5-1 Simulation scheme

## 5.3 仿真项目和结果分析

### 5.3.1 仿真电路主要参数

仿真电路的参数规格如下

输入电压：85-135V

输出电压：32V

输出电流：3A

$T_1$ ：原边电感  $L_{T1}$  40u， $N_p$ ： $N_s = 1$ ：0.8

$T_2$ ：原边电感  $L_{T2}$  200u， $N_p$ ： $N_s = 1$ ：0.2

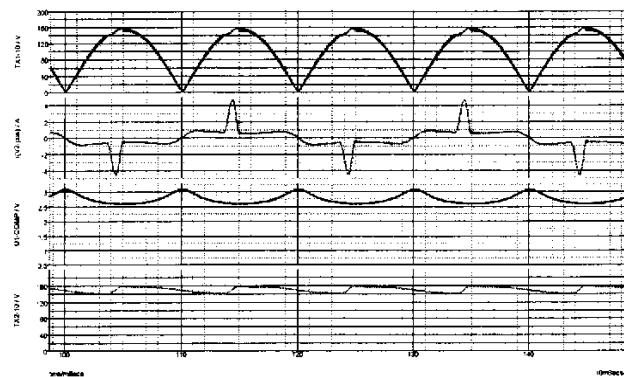

### 5.3.2 整流线电压, 线电流, 误差放大器输出电压, 储能电容电压

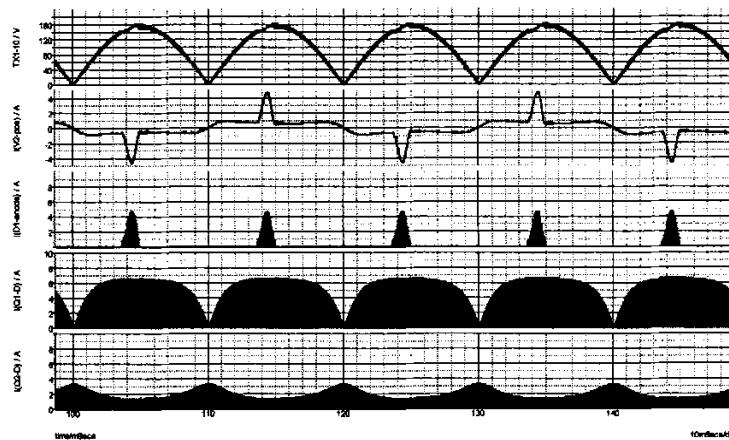

如图 5-2 所示, 从上到下依次是整流线电压、线电流、误差放大器输出电压(占空比)和储能电容电压。

可以看出, 整流线电压呈正弦半波脉动, 电流波形跟随输入电压变化, 但不是正弦形。误差放大器的输出电压是以一半的工频周期脉动变化的, 它和一个稳定电压值经比较器得到占空比信号, 因此占空比信号也呈周期性脉动变化。在一个工频半周期中, 占空比中间小, 两端大。中间储能电容的电压基本不变, 它在输入电压为峰值附近充电, 其他时间放电。

图 5-2 整流线电压, 线电流, 误差放大器输出(占空比)和储能电容电压。

Fig.5-2 Rectified line voltage, line current, error amplifier output (duty cycle) and voltage on the capacitor.

### 5.3.3 储能电容充电电流(即二极管 $D_3$ 电流), 开关管 $Q_1$ , $Q_2$ 电流

如图 5-3 所示, 从上到下依次是整流线电压、线电流、电容充电电流(即二极管  $D_3$  电流)、开关管  $Q_1$  和  $Q_2$  电流。

可以看出, 线电流是电容充电电流和  $Q_1$  电流的叠加。由于  $T_1$  支路高频地从小电容抽取电流, 导致输入电压给储能电容充电的电流波形也呈高频断续状态。从  $Q_1$  和  $Q_2$  的电流包络线可以看出, 在输入电压高时, 主要由  $T_1$  传递主要功率, 当输入电压低时, 主要由  $T_2$  承担主要功率, 当输入电压为零时,  $T_2$  承担全部输出功率。

图 5-3 整流线电压, 线电流, 二级管  $D_3$  电流, 开关管  $Q_1$  电流和开关管  $Q_2$  电流。

Fig.5-3 Rectified line voltage, line current, current of diode  $D_3$ , current of switch  $Q_1$  and  $Q_2$ .

### 5.3.4 中间储能电容 C 的取值对输入电流波形的影响

如图 5-4 所示, 从上至下分别是储能电容取  $50\mu F$ ,  $100\mu F$  和  $200\mu F$  时输入电流波形。

图 5-4 储能电容分别取  $50\mu F$ ,  $100\mu F$  和  $200\mu F$  时输入电流波形

Fig.5-4 Line current waveforms with a bulk capacitor of  $50\mu F$ ,  $100\mu F$  and  $200\mu F$

可见, 储能电容越大, 充电导通角越小, 输入电流的尖峰越大。从控制谐波的角度, 过大或过小的储能电容都是不合适的。

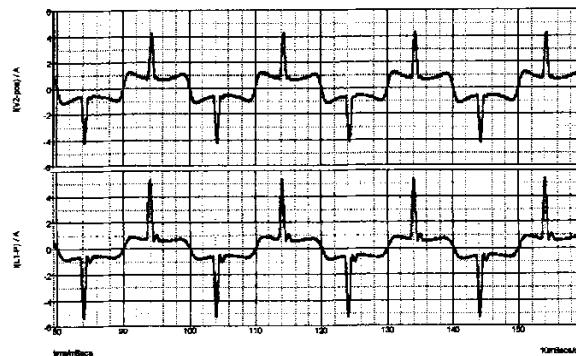

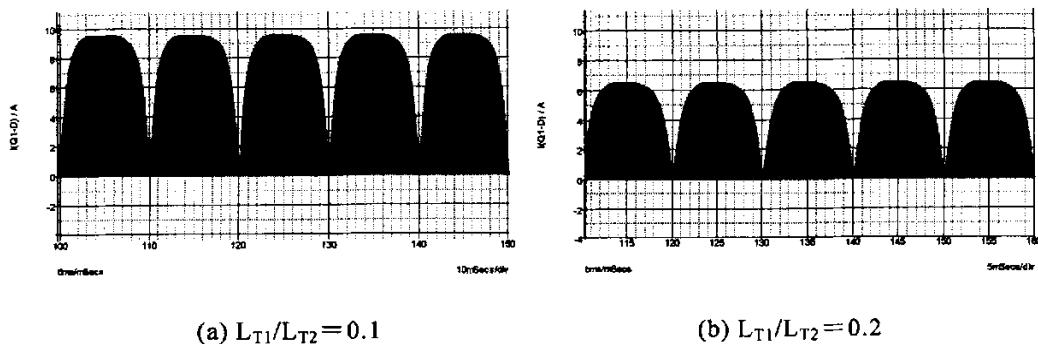

### 5.3.5 比值 $L_{T1}/L_{T2}$ 对输入电流波形的影响

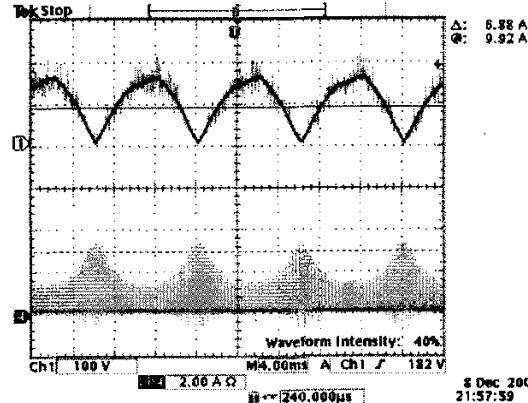

比值  $L_{T1}/L_{T2}$  为 0.1 和 0.2 时的输入电流波形如图 5-5 所示 (储能电容取  $150\mu F$ )。可以看出, 比值为 0.1 时电流波形更接近正弦形。

图 5-5 比值  $L_{T1}/L_{T2}$  为 0.1 (上) 和 0.2 (下) 时的输入电流波形Fig.5-5 Line current waveforms when  $L_{T1}/L_{T2}$  equals 0.1 (top) and 0.2 (bottom)

但是在  $L_{T1}/L_{T2}$  为 0.1 的情况下, 开关管  $Q_1$  的工作状态非常恶劣, 如图 5-6(a) 所示。从图 5-6(a) 可见,  $Q_1$  电流尖峰已经接近 10A, 这种情况下开关管  $Q_1$  的损耗将非常大。如果  $L_{T1}/L_{T2}$  为 0.2, 则开关管  $Q_1$  的工作条件大大改善, 峰值电流降至约 6A, 如图 5-6(b)。这对于提高变换效率具有重要意义。

(a)  $L_{T1}/L_{T2} = 0.1$ (b)  $L_{T1}/L_{T2} = 0.2$ 图 5-6  $L_{T1}/L_{T2}$  为不同值时  $Q_1$  的电流波形Fig.5-6 Line current of  $Q_1$  with different  $L_{T1}/L_{T2}$

以上仿真结果表明, 比值 = 0.1 时的功率分配更加合理, 输入电流更接近正弦形, 功率因数更高。但是如果设定比值 = 0.1, 则开关管  $Q_1$  的工作条件将非常恶劣。仿真表明, 此时的  $Q_1$  电流峰值约为 10A, 这对于提高变换器的工作效率是非常不利的。因此比值需要折衷考虑, 确定比值为 0.2 是比较合理的。此时两个并联支路的功率分配为 6: 4。

## 5.4 实验结果

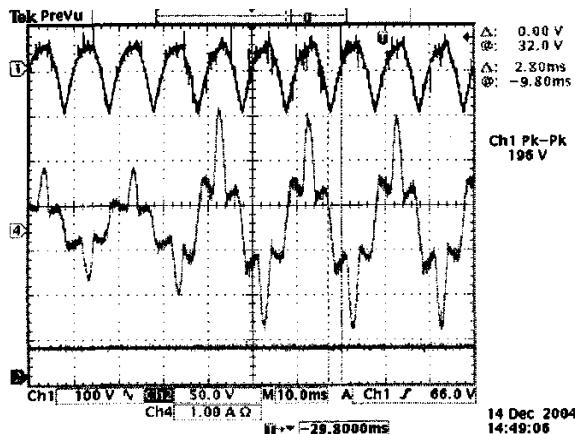

### 5.4.1 测量波形

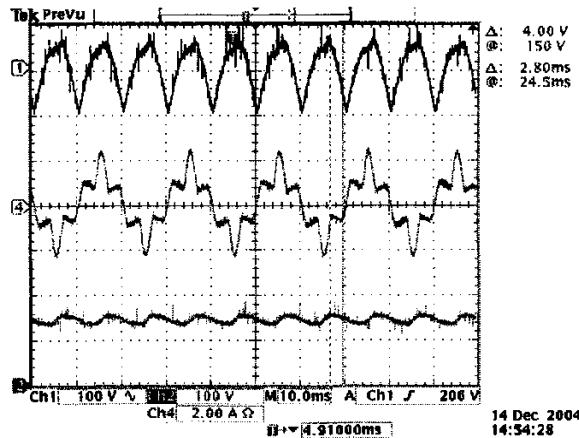

输入电流和中间储能电容电压波形如图 5-7 所示。对比图 5-2 的仿真结果, 可以看出, 试验波形符合理论分析, 和仿真结果吻合。

图 5-7 从上到下依次是输入电压, 输入电流和中间储能电压 (3A)。

Fig.5-7 Rectified line voltage, line current and bulk capacitor voltage (output current=3A)

二极管  $D_3$  电流如图 5-8 所示。对比图 5-3 的仿真结果, 可以看出, 试验波形符合理论分析, 和仿真结果吻合。

图 5-8 从上到下依次是输入电压, 二极管  $D_3$  电流和储能电容电压。

Fig.5-8 Rectified line voltage, charging current of capacitor and the voltage on the capacitor

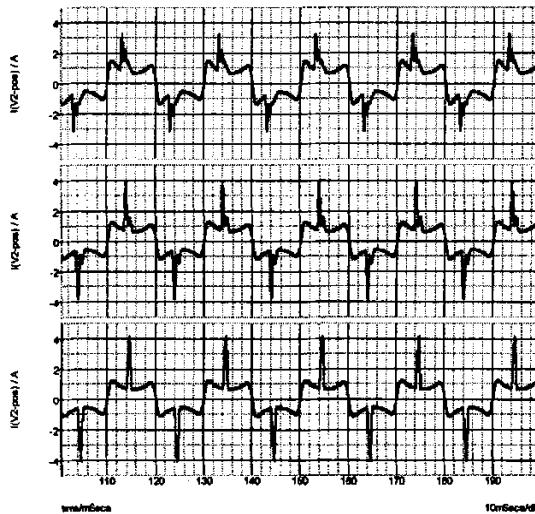

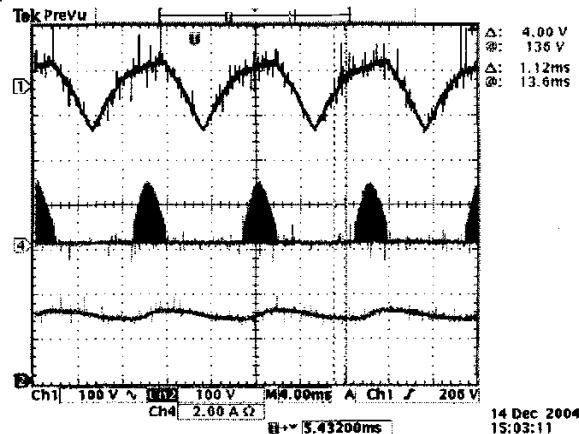

变压器  $T_1$  和  $T_2$  的电流波形 (即开关管  $Q_1$  和  $Q_2$  电流波形) 如图 5-9 和 5-10 所示。对比图 5-3 的仿真结果, 可以看出实验结果与仿真结果吻合。

$T_1$  电流工作在断续模式, 包络线随输入电压的变化而变化。在输入电压为零时,  $T_1$  电流也为零; 当输入电压为最大时,  $T_1$  电流也为最大。

$T_2$  电流工作在断续模式, 包络线随输入电压的变化而变化。在输入电压为零时,  $T_2$  电流为最大; 当输入电压为最大时,  $T_2$  电流最小

图 5-9 输入电压和  $T_1$  电流波形Fig.5-9 Rectified line voltage and  $T_1$  current图 5-10 输入电压,  $T_2$  电流波形Fig.5-10 Rectified line voltage and  $T_2$  current

负载变化的响应如图 5-11 所示。从上之下依次时输入整流电压, 输入电流和输出电压。当输出电流从 1.5A 跳变至 3A 时, 输入电流快速的调整, 输出电压稳定。实验证明这个电路具有快速响应的特性。

图 5-11 负载变化响应

Fig.5-11 Load response

#### 5.4.2 测试数据

表 5-1 是输入电压从 90V 变化至 135V, 负载 3A 时电路的各种参数记录。包括输入功率  $P_{in}$ , 输入电流  $I_{in}$ , 中间储能电容电压  $V_c$ , 功率因数 PF, 输出功率  $P_{out}$  等。根据输入功率和输出功率计算了变换器的效率  $\eta$ 。

表 5-2 是输入电压保持 110V, 负载从 0.5A 变化到 3A 电路的各种参数记录。包括输入功率  $P_{in}$ , 输入电流  $I_{in}$ , 中间储能电容电压  $V_c$ , 功率因数 PF, 输出功率  $P_{out}$  等。根据输入功率和输出功率计算了变换器的效率  $\eta$ 。

表 5-1 负载 3A, 输入电压从 90V 变化至 135V

| $V_{in}$  | 90     | 100    | 110    | 115    | 125    | 135    |

|-----------|--------|--------|--------|--------|--------|--------|

| $I_{in}$  | 1.4583 | 1.3203 | 1.2099 | 1.1643 | 1.0831 | 1.0146 |

| $P_{in}$  | 114.45 | 113.45 | 113.03 | 112.88 | 112.46 | 112.08 |

| $V_c$     | 115.7  | 130.6  | 145.3  | 152.7  | 167.2  | 181.7  |

| PF        | 0.873  | 0.863  | 0.851  | 0.844  | 0.832  | 0.819  |

| $V_{out}$ | 32.18  | 32.18  | 32.18  | 32.18  | 32.18  | 32.17  |

| $I_{out}$ | 3      | 3      | 3      | 3      | 3      | 3      |

| $P_{out}$ | 96.54  | 96.54  | 96.54  | 96.54  | 96.54  | 96.51  |

| 效率        | 84.35  | 85.09  | 85.41  | 85.52  | 85.84  | 86.11  |

表 5-2 输入电压 110V, 负载从 0.5A 变化到 3A

| $I_{out}$ | 0.5    | 1      | 1.5    | 2      | 2.5    | 3      |

|-----------|--------|--------|--------|--------|--------|--------|

| $V_{out}$ | 32.19  | 32.19  | 32.18  | 32.18  | 32.18  | 32.17  |

| $P_{out}$ | 16.065 | 32.19  | 48.27  | 64.36  | 80.45  | 96.51  |

| $I_{in}$  | 0.2553 | 0.4554 | 0.6462 | 0.8334 | 1.0224 | 1.2095 |

| $V_{in}$  | 109.98 | 109.98 | 109.97 | 109.96 | 109.91 | 109.93 |

| $P_{in}$  | 19.768 | 37.90  | 56.38  | 75.09  | 94.02  | 113.02 |

| PF        | 0.704  | 0.759  | 0.796  | 0.825  | 0.838  | 0.851  |

| 效率        | 81.42  | 84.93  | 85.62  | 85.71  | 85.57  | 85.39  |

| $V_c$     | 151.8  | 150.4  | 149.0  | 147.6  | 146.5  | 145.2  |

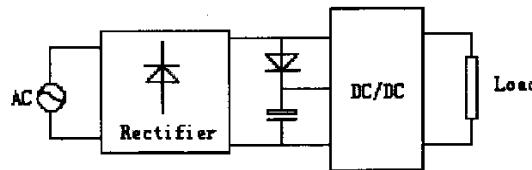

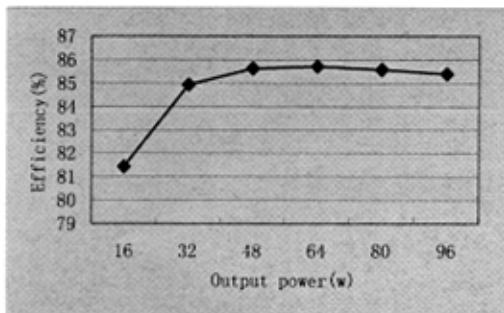

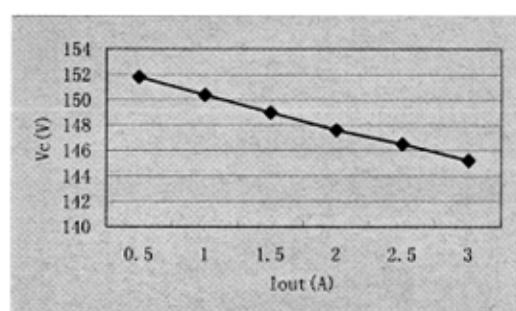

### 5.4.3 绘制相应的效率曲线, 储能电容电压曲线

根据表 5-2, 绘制了电路的效率曲线和储能电容电压曲线, 如图 5-12 和 5-13 所示。

图 5-12 效率曲线

Fig.5-12 Efficiency curve

图 5-13 储能电容电压曲线

Fig.5-13 Bulk capacitor voltage curve

理论分析表明，基于直接功率传递原理改进的单级并联双反激变换器对内部功率流向进行了优化，全部功率一次处理，可以获得比一般单级变换器高的效率。从 5-12 的效率曲线可以看出，当输出功率大于 30W 时，变换器的效率都在 85% 以上，满载时的效率是 85.39%，具有高效率的特点。

从电路的结构可知，储能电容上的电压将钳位在输入电压峰值。图 5-13 的储能电容电压曲线证明了这一点，储能电容电压始终没有超过输入电压峰值。随着输出电流（代表了输出功率）增加，储能电容上的电压下降。这是因为随着输出功率的增加，变压器  $T_2$  承担了更多的功率，储能电容电压纹波增大。

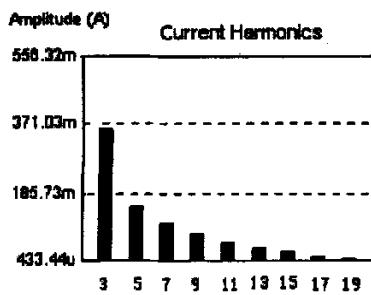

#### 5.4.4 谐波分析

理论分析表明，由于电流的特殊波形，这个变换器可以避开 IEC1000-3-2 的 Class D 标准，而只需要符合 Class A 标准。使用 HP AC source GUI 软件对输入电流谐波分析，分析结果如图 5-14 所示。由于 Class A 采用的是绝对值标准，这个变换器可以很容易地满足这个标准。

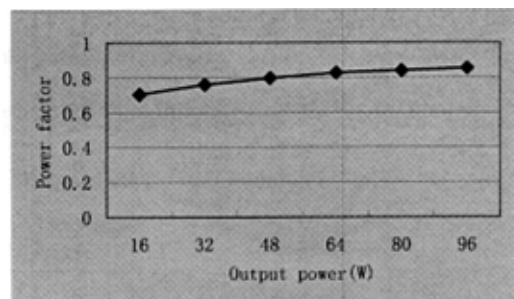

图 5-15 是变换器的功率因数曲线。由于输入电流的特殊波形，这个变换器的功率因数不高，满载时的功率因数为 0.851。

图 5-14 谐波分析

Fig.5-14 Harmonic analysis

图 5-15 功率因数曲线

Fig.5-15 Power factor curve

## 5.5 本章小结

本章简单介绍了仿真软件 SIMetrix/SIMPLIS，并用这个软件对电路进行仿真，采集了输入电压，输入电流，中间储能电容电压，电容充电电流， $T_1$  支路电流， $T_2$  支路电流和误差放大器输出电压等关键波形，说明了电路性能的特点，然后对这些仿真波形进行试验验证。实验结果和理论分析和仿真结果吻合。根据实验数据，对储能电容、效率、谐波、功率因数等参数作了分析。

## 结论与展望

### 1 本文所做的工作

为了抑制电器输入电流谐波，使电器符合相关的谐波限制标准，有源功率因数校正技术正在被广泛应用。在传统的 AC/DC 变换器中，为了达到高功率因数和稳定的输出电压两个目的，通常采用两级变换模式，即 AC/DC+DC/DC 结构。单级 PFC AC/DC 变换器将 AC/DC 级和 DC/DC 两级合成一级，利用 AC/DC 变换器工作于不连续电流模式时的自动功率因数校正功能，仅仅对输出电压进行调节。由于电路结构简单，成本降低，功率一次处理，效率提高。

本文研究了基于直接功率传递原理的单级并联双反激 AC/DC 变换器。为了降低中间储能电容电压，提高单级 PFC AC/DC 变换器的工作效率，引入直接功率传递原理，对单级 PFC AC/DC 变换器的拓扑进行了改进，对其中一种单级并联双反激 AC/DC 变换器进行了详细的设计和验证。

具体的包括以下几个方面：

1. 分析了单级变换器中间电容电压升高的原因。单级变换器由于中间储能电压不受调节，在输入电压升高或者重载的情况下，有可能储能电容电压升高的问题。第二章从功率平衡，变换器的工作模式等方面深入的剖析了这个问题的实质。

2. 中间电容电压的升高从根本上说是由于输入功率和输出功率的不平衡引起的，因此解决问题就需要从改善功率流向入手，从而引入直接功率传递原理。在这个理论的指导下对单级变换器进行改进，给出三个典型的拓扑。这些拓扑都有效地解决了中间电容电压升高的问题。

3. 在三个基于直接功率传递原理该改进地拓扑中，选取单级并联双反激 AC/DC 变换器作进一步研究。这个变换器具有成本低，体积小和效率高的优点，储能电容电压被钳位在输入电压的峰值。在这个变换器的基础上作进一步的改进，对改进的拓扑进行了仿真分析和实验分析。仿真和实验的结果证实了理论的预期。

### 2 进一步的研究设想

如上所述，单级并联双反激 AC/DC 变换器具有一些显著的优点，不过依然存在一些问题有待解决。

1. 变压器利用率较低。在这个变换器中，使用了两个变压器，不利于成本

的降低。另外每个变压器不是恒功率运行，承担的功率呈周期性变化，造成变压器的利用率较低。为了克服这个问题，可以考虑两个并联变压器使用同一个磁芯。

2. 采用其他一些拓扑获得更好的电流波形。本文研究的单级变换器输入电流并不呈正弦形，这是由电路结构决定的，不可能在这个电路的基础上改进去修正电流波形进而控制谐波含量。为了获得更好的电流波形，可以优化电路结构，或者采用更复杂的控制。不过单级 PFC AC/DC 变换器采用太复杂的控制就失去了它简单的特点。在文献[15]中，采用一个类似的电路结构，仅仅在控制上稍加简单的改进，取得很好的效果。

3. 单级 PFC AC/DC 变换器的建模问题。如果可以建立单级 PFC AC/DC 变换器的数学模型，就可以指导对变换器进行优化。但是单级 PFC AC/DC 变换器不同与一般的 DC/DC 变换器。后者的输入和输出的都是恒定的，容易建立起输出和输入之间的函数关系。但是 PFC 电路的输入却是不断变化的，这给建模带来很大的困难。目前的研究成果仅限于对特定的电路进行简单的建模[34~40]。

## 参考文献

1. 严百平, 刘建, 程红丽. 不连续导电模式高功率因数开关电源. 第一版. 科学出版社. 2000: 1-9

2. 张卫平. 绿色电源—现代电能变换技术及应用. 第一版. 科学出版社. 2001: 1-4; 23-31

3. P.C.Todd.UC3854 controlled power factor correction circuit design. Unitrode Application Note.1998

4. Manjing Xie. Digital control for power factor correction. Master degree thesis of the Virginia Polytechnic Institute and State University, June 2003, Blacksburg, Virginia

5. Ya-Tsung Feng, Gow-long Tsai, Ying-Yu Tzou. Digital control of a single-stage single-switch flyback PFC AC/DC converter with fast dynamic response. PESC 2001.2001:1251-1256

6. M.Fu, Q.Chen. A DSP based controller for power factor correction (PFC) in a rectifier circuit. APEC 2001.2001:144-149

7. K.De Gusseme, D.M.Van de Sype, J.A.A.Melkebeek. Design issues for digital control of boost power factor correction converters. ISIE 2002. 2002:731-736

8. Sangsun Kim, Dr. P. Enjeti. Digital control of switching power supply- power factor correction stage. Power Electronics and Power Quality Laboratory, Department of Electrical Engineering, Texas A&M University

9. J.Zhou, Z.Lu, Z.Lin, Y.Ren, Z.Qian, Y. Wang. Novel sampling algorithm for DSP controlled 2KW PFC converter. Power Electronics, IEEE Transactions on 2001.2001:217-222

10. David M. Van de Sype. Digital control of boost power factor preregulators: sampling.2nd FTW PHD Symposium, Gent, Belgium, Dec. 12, 2001.page 75

11. Lazaro, A.; Barrado, A.; Pleite, J.; Olias, E. New power factor correction AC/DC converter with reduced storage capacitor voltage. IECON 02 [Industrial Electronics Society, IEEE 2002 28th Annual Conference of the], Volume: 1, 5-8 Nov. 2002 Pages: 353 - 358 vol.1

12. Jiang, Y.; Lee, F.C.; Hua, G; Tang, W. A novel single-phase power factor correction scheme. APEC 1993. Conference Proceedings 1993. Eighth Annual , 7-11 March 1993 Pages:287 – 292

13. Garcia, O.; Cobos, J.A.; Alou, P.; Prieto, R.; Uceda, J. A simple single-switch single-stage AC/DC converter with fast output voltage regulation. *Power Electronics, IEEE Transactions on*, Volume: 17, Issue: 2, March 2002 Pages: 163 – 171

14. Qun Zhao; Lee, F.C.; Jinrong Qian. Single-switch parallel power factor correction AC/DC converters with inherent load current feedback. *APEC 2002. Seventeenth Annual IEEE*, Volume: 1, 10-14 March 2002 Pages: 270 - 276 vol.1

15. Lu, D.D.C.; Cheng, D.K.W.; Lee, Y.S. Single-stage AC-DC power-factor-corrected voltage regulator with reduced intermediate bus voltage stress. *Electric Power Applications, IEE Proceedings-*, Volume: 150, Issue: 5, 9 Sept. 2003 Pages: 506 – 514

16. Weihong Qiu, Weikai Wu, Shiguo Luo Peter Kornetzky and Issa Batarseh. Practical design considerations of a single-stage single-switch parallel PFC converter for universal voltage applications. *2002 IEEE PEDS*

17. Shiguo Luo; Huai Wei; Guangyong Zhu; Batarseh, I. Several schemes of alleviating bus voltage stress in single stage power factor correction converters. *PEDS 1999. Proceedings of the IEEE 1999 International Conference on*, Volume: 2 , 27-29 July 1999 Pages:921 - 926 vol.2

18. Jinrong Qian; Qun Zhao; Lee, F.C. Single-stage single-switch power-factor-correction AC/DC converters with DC-bus voltage feedback for universal line applications. *Power Electronics, IEEE Transactions on*, Volume: 13, Issue: 6, Nov. 1998 Pages: 1079 – 1088

19. Wenkai Wu; Weihong Qiu; Rustom, K.; Shiguo Luo; Batarseh, I. Universal input single-stage PFC AC/DC converter with reduced DC-bus voltage stress. *PESC 2002. 2002 IEEE 33rd Annual*, Volume: 3 , 23-27 June 2002 Pages:1351 - 1356 vol.3

20. Qun Zhao; Lee, F.C.; Fu-sheng Tsai. Voltage and current stress reduction in single-stage power factor correction AC/DC converters with bulk capacitor voltage feedback. *Power Electronics, IEEE Transactions on*, Volume: 17 , Issue: 4 , July 2002 Pages:477 – 484

21. O. García, C. Fernández, J.A. Cobos, J. Uceda. Universal line voltage single-stage AC/DC converter. *2002 IEEE*

22. O. García, C. Fernández, R.Prieto, J.A. Cobos, J. Uceda. Design trade-offs of bi-flyback and bi-forward AC/DC converters to comply low frequency harmonic regulation. *2000 IEEE*

23. Shiguo Luo; Weihong Qiu; Wenkai Wu; Batarseh, I. Flyboost power factor correction cell and its applications in single-stage AC-DC converters. PESC 2002. 2002 IEEE 33rd Annual, Volume: 3, 23-27 June 2002 Pages: 1375 - 1380 vol.3

24. 刘小光, 尹华杰. 应用直接功率传递原理改进的单级 PFC 拓扑及其直流母线电压应力分析. 电气应用 (原电工技术杂志) 2005. 1: 68-72

25. 许化民. 单级功率因数校正技术. 南京航空航天大学博士学位论文. 2001, 5: P16-17; P19-P21

26. High speed PWM controller UC1823/2823/3823. Texas instruments datasheet

27. High speed dual MOSFET drivers MC33152/34152. On semiconductor datasheet

28. Precision timers NE555/SA555/SE555. Texas instruments datasheet

29. 荀殿栋, 程宗汇. 实用数字电路设计手册. 电子工业出版社, 1994 年第一版: 190-193; 615-616

30. 张占松, 蔡宣三. 开关电源的原理与设计. 电子工业出版社. 第一版. 1998: P152-206

31. 电子变压器专业委员会编. 电子变压器手册. 第一版. 辽宁科学出版社. 1998: P381-397

32. Switching power supply design. Abraham I. Pressmen. New York ; McGraw-Hill, c1998: 105-113

33. 刘小光, 尹华杰. 不连续模式反激变换器的基本原理和电路设计. 电源世界. 2004.1.1: P17-P19

34. 张卫平, 吴兆麟, 赵徐森, 龚绍文. 功率因数校正器的三频分析法. 电子学报, Nov. 1997

35. 张卫平, 吴兆麟, 李洁. 开关变换器建模方法综述. 浙江大学学报(自然科学版), Mar, 1999

36. 王燕, 夏仁平, 吴昕. 基于系统建模法的 PFC 电压环仿真模型. 电力电子技术, 1999 年第 1 期

37. Guangyong Zhu, Huai Wei, Peter Kornetzky, Issa Batarseh. Dynamic modeling of a single-switch power factor correction circuit. 1998 IEEE

38. T.H.Chen, W.L.Lin, C.W.Liaw. Dynamic modeling and controller design of flyback converter. IEEE transactions on aerospace and electronic systems vol.35, No.4 October 1999

39. Kin-Siu Fung, Wing-Hung Ki and Philip K.T. Mok. Analysis and measurement of DCM power factor correctors. 1999 IEEE

40. Tsai-Fu Wu, Yu-Kai Chen. Analysis and Design of an Isolated Single-Stage Converter Achieving Power-Factor Correction and Fast Regulation. 1999 IEEE

41. Yiqing Zhao. Single phase power factor correction circuit with wide output voltage range. Thesis submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering. 1998

42. Vlad Grigore. Topological issues in single-phase power factor correction. Dissertation for the degree of Doctor of Science in Technology. Helsinki University of Technology (Espoo, Finland), 2001

43. P.Tenti and G.Spiazzi. Harmonic Limiting Standards and Power Factor Correction Techniques. 6th European Conference on Power Electronics and Applications - EPE '95

## 攻读学位期间发表的与学位论文内容相关的学术论文

在学期间已发表（包括已接受待发表）的论文，以及已投稿、或已成文打算投稿、或拟成文投稿的论文情况（只填写与学位论文内容相关的部分）：

| 序号 | 作者（全体作者，按顺序排列） | 题 目                                | 发表或投稿刊物名称、级别      | 发表的卷期、年月、页码        | 相当于学位论文的哪一部分（章、节） | 被索引收录情况 |

|----|----------------|------------------------------------|-------------------|--------------------|-------------------|---------|

| 1  | 刘小光，尹华杰        | 功率因数校正的数字控制方法                      | 电源技术应用            | 2004/2<br>P85-P89  | 第一章               |         |

| 2  | 刘小光，尹华杰        | 数字控制 PFC 几个设计事项的探讨                 | 电工技术杂志            | 2004/08<br>P91-P94 | 第一章               |         |

| 3  | 刘小光，尹华杰        | 不连续模式反激变换器的基本原理和电路设计               | 电源世界              | 2004/11<br>P17-P19 | 第四章               |         |

| 4  | 刘小光，尹华杰        | 应用直接功率传递原理改进的单级 PFC 拓扑及其直流母线电压应力分析 | 电气应用<br>(原电工技术杂志) | 2005/01<br>P68-P72 | 第二章               |         |

| 5  |                |                                    |                   |                    |                   |         |

| 6  |                |                                    |                   |                    |                   |         |

## 致 谢

本论文的工作是在导师尹华杰副教授的悉心指导下顺利完成的。在攻读硕士学位期间，尹老师非常关心我的学习和生活。当我在学业上遇到困难的时候，尹老师总是不厌其烦地给予帮助和指导，甚至花费自己的宝贵时间查阅相关的资料提供给我参考，令我倍受感动。他宽广坚实的专业知识，丰富的实践经验，忘我的工作热诚，和孜孜不倦的育人态度，让我受益菲浅。从论文的选题、研究方案的制定，实验电路的设计制作，直到论文的写作和最后定稿，都倾注了尹老师大量的心血。值此论文付梓之际，特向我的导师致以最诚挚的谢意和最崇高的敬意！

在学习和研究过程中，雅达电子有限公司安排了数次专业的培训和实习并提供了良好的硬件制作条件，让我的研究课题可以顺利进行。雅达电子有限公司香港设计部郑永宁先生、Laurence Mcgarry 先生和中国设计部李伟博士一直关注着我的毕业设计进度并提出具体的建议和解答，帮助我克服了许多困难，在此向他们表示深深的谢意。

感谢电力学院领导和电力电子教研室的各位老师对于我各方面的帮助和支持。感谢张波老师，谢运祥老师，王志强老师，杨苹老师，梁冠安老师的诸多指导和帮助。

在电路硬件制作阶段，得到了西班牙 Univ. Politecnica de Madrid 的 Oscar Gacia 先生的热心帮助。虽然只是几封 E-mail 的来往，但是 Oscar 先生严谨的学术态度和丰富的行业经验让我深感敬佩。

感谢庞永强、李意、李金鹏、王浩、陈少屏、梁少毅、钟小芬、李乔、周治强、李广全、王磊等师兄师姐们对我的热心帮助。感谢蔡昌文、王智昊、虞龙、邓衍平、王亚林、王经明、胡明星、武志贤、陈保艳，李虹、梁锦桃等同班同学的支持和鼓励。

深深地感谢我的父母和家人在我的成长道路上对我的关怀和鼓励。感谢一直以来关心和支持我的亲人和朋友。

最后，向评审本论文及参加论文答辩的专家和老师们致以崇高的谢意！

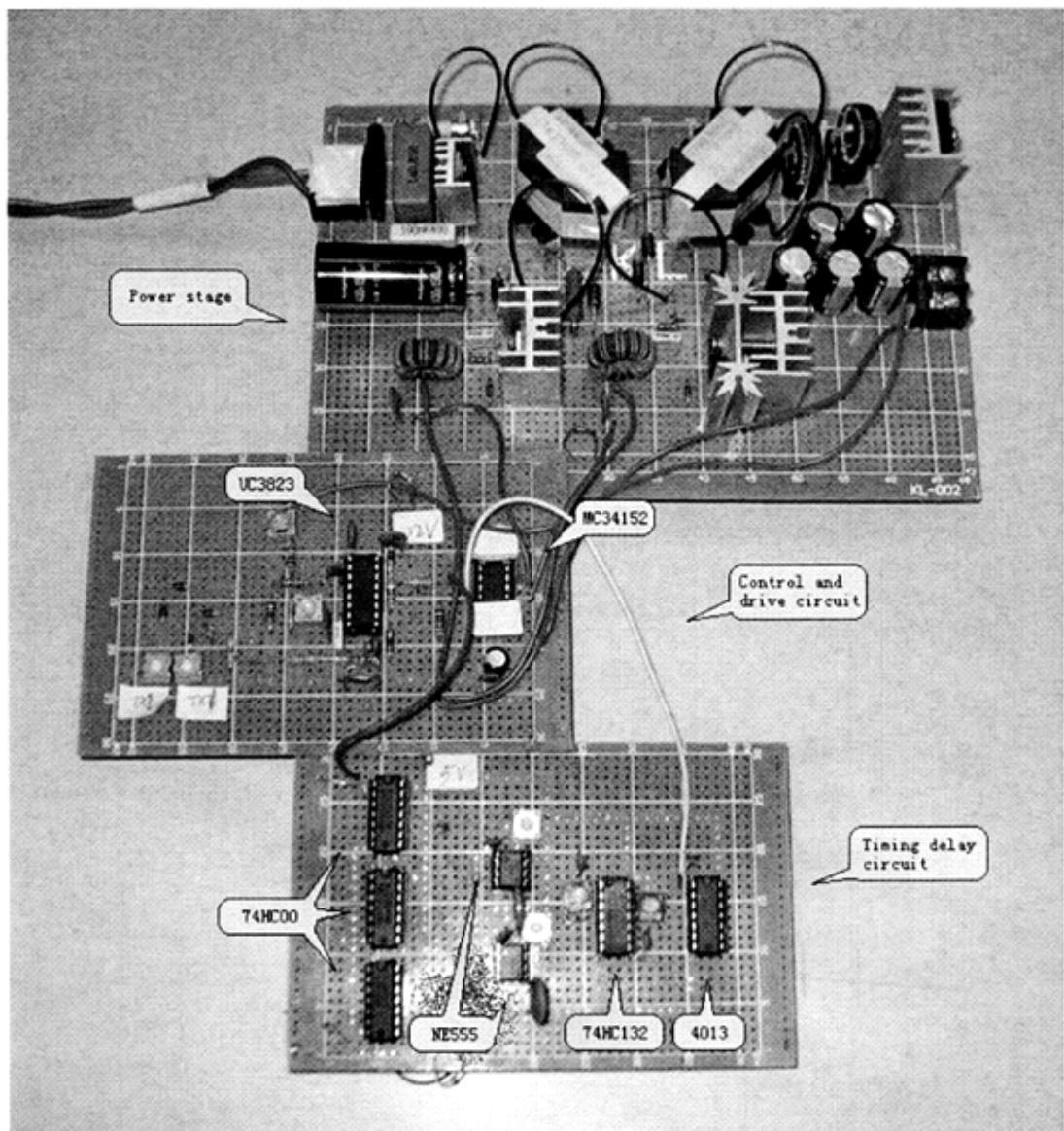

## 附录 1: 实验样机图

## 附录 2：电路全图

Title: single-edge parallel bidirectional

AC/DC converter

Version: 6

Date: 2025/5/13?

Drawn By: Raymond Liu