## 摘要

宽覆盖频率合成器有着广泛的应用，在雷达模拟器的信号源、干扰源以及超宽带跳频系统中都有很多应用。迄今为止，宽覆盖频率源的一个亟待解决的问题是宽覆盖条件下平衡好杂散、相噪以及功率平坦度等各项指标之间的关系。当前的频率合成技术的一个大的趋势是结合 DDS+PLL 的复合频率合成方式。本系统由于设计的需要，没有引入 DDS 作为环路的激励，设计的重点在于锁相环的宽覆盖的恒定环路带宽问题，基于这个设计理念的提出一种经典的频率设计方案，双锁相环切换加倍频模式，这样的设计可以使单个分系统的频率覆盖降低，降低了设计的难度。超宽覆盖频率源的设计是当代电子系统的一个关键技术。

本文首先对雷达模拟器进行了简单的介绍，然后详细分析了这类模拟器常用的频率合成技术的基本原理及其特点，并分析整个系统的相噪和杂散指标。其次，本文根据课题提出的要求，采用双锁相环切换加倍频的方案完成了对该宽覆盖雷达模拟器干扰源频率合成器系统方案的设计，然后设计并实现该频率源，从而验证了方案的可行性。

在本文中，采用的双锁相环切换加倍频方案以简洁有效的方式实现了课题所要求的频率合成器。测试结果表明本文的设计满足了系统在频谱纯度（相噪和杂散）、输出功率等关键技术指标上的要求：在 3~16GHz 频段范围内，全频段输出信号步进 20MHz 时，相噪均在 -83dBc/Hz @10kHz 以下，杂散在 -60dBc 以下，输出功率在 10dBm 以上。

最后，针对本次设计中的不足之处，本文提出了一些改进建议。文中所采用的一些设计方法及改进建议，为实现高性能的超宽覆盖小步进频率合成器提供了一个有效的方法，有一定的借鉴价值。

**关键词：** 频率合成器，宽覆盖，环路带宽，等效鉴相增益，等效压控增益

## ABSTRACT

Wide frequency-coverage synthesizer is popularly used in many domains, for example, it is can be found in Radar simulation system , such as its signal source and interference source. One disturbing problem in Wide frequency-coverage synthesizer is to make balance between its great variety of requirements, e.g. spurious level, phase noise level and output power flatness, in the present electronic system. Indeed, the complex frequency synthesizer, DDS+PLL, is considered as a main trend in correlative system. As the necessity of practical design, DDS is not implemented as a reference source to stimulate PLL. Because of it, invariable loop bandwidth is emphasized in such a PLL under the condition of wide frequency-coverage. A classical frequency synthesizer designing pattern, dual-PLL-switching, is proposed on the foundation of this theory. The benefit of this pattern makes the frequency-coverage of single PLL sub-system smaller in order to lower the difficulty of designing.

In the dissertation, Radar simulation system is briefly introduced .Then the basic frequency synthesizer designing principle and it characteristics are in presentation and compared in detail. The spurious level and phase noise level in whole frequency system are analyzed in step. At the coming chapters of this dissertation, dual-PLL-switching plus frequency multiplier is implemented in this wide frequency-coverage frequency synthesizer for interference source in Rader simulation system, according to the index of this program. It provides a powerful demonstration with the feasibility of this scheme.

In this thesis, dual-PLL-switching plus frequency multiplier provides a brief but efficient mean to realize the required frequency synthesizer. The results through practical test show a conclusion that the system is completely fit for the requirements especially on the key index, i.e. within its bandwidth of 3~16GHz, when the frequency step is 20MHz, the phase noise level is less than -83dBc/Hz @ 10kHz, the spurious level is below -60dBc and the output power is above 10dBm.

In the final chapter, aiming at the deficiency of this design, some suggestion is proposed. Some certain designing methods and suggestion in this design also offer an

---

## ABSTRACT

---

efficient method for designing an ultra-wide frequency-coverage and fine frequency step synthesizer with good performances, meanwhile, it is also valuable for reference .

**Keywords:** frequency synthesizer, wide frequency-coverage, loop bandwidth, equivalent phase detector gain, equivalent VCO gain

## 图目录

|                                        |    |

|----------------------------------------|----|

| 图 2-2 实测的 100MHz 晶体振荡器相噪图.....         | 8  |

| 图 2-3 受杂散影响的载波信号.....                  | 10 |

| 图 2-4 基本锁相环原理框图.....                   | 11 |

| 图 2-5 理想积分环路开环函数幅相特性图.....             | 13 |

| 图 2-6 分数分频锁相环结构.....                   | 17 |

| 图 3-1 DDS 激励 PLL 方案.....               | 23 |

| 图 3-2 内插混频式 DDS/PLL 方案.....            | 23 |

| 图 3-3 环外混频式 DDS/PLL 方案.....            | 23 |

| 图 3-4 DDS+直接频率合成方案.....                | 25 |

| 图 3-5 锁相环等效噪声模型.....                   | 27 |

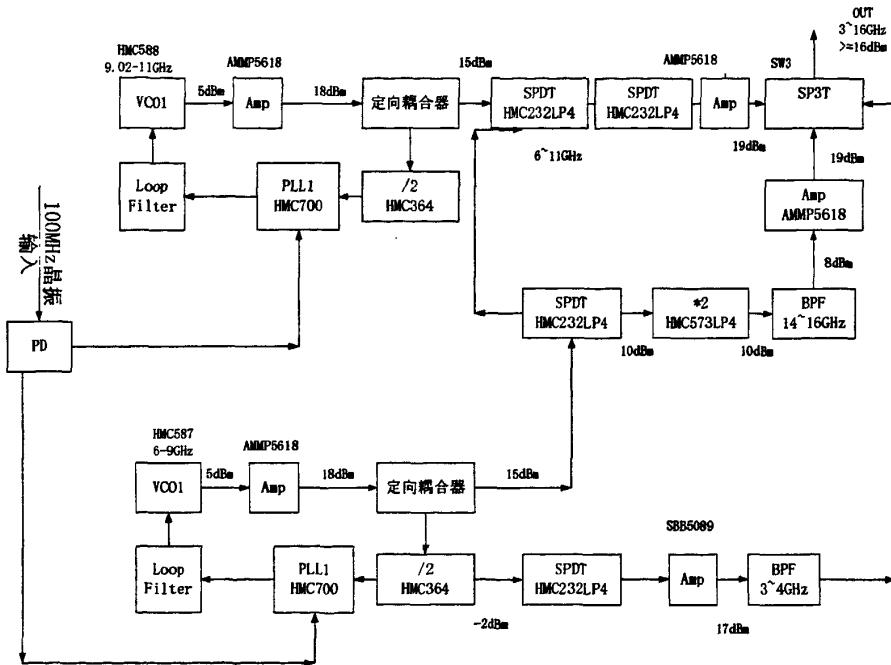

| 图 4-1 系统方案设计图.....                     | 33 |

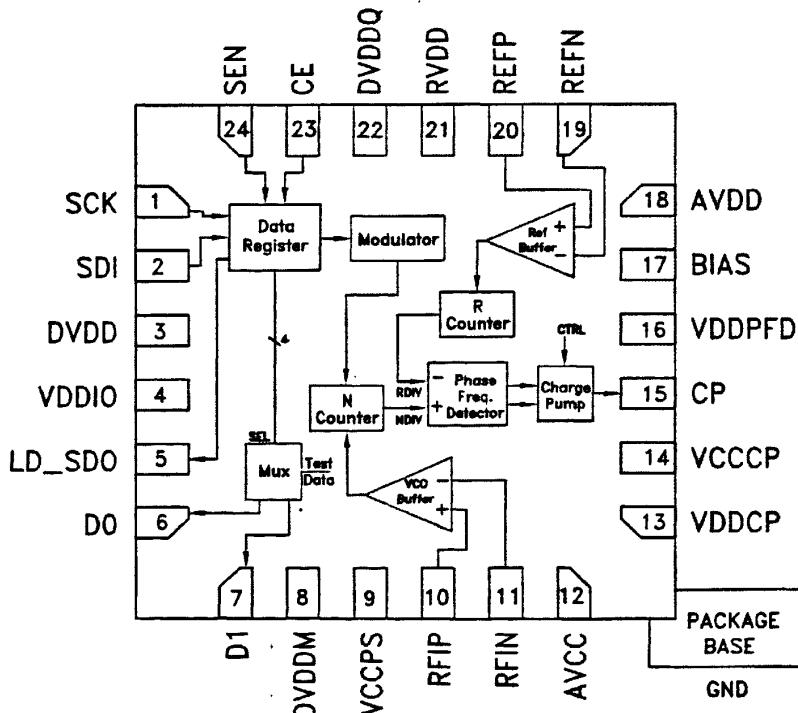

| 图 4-2 HMC700 的内部结构图.....               | 34 |

| 图 4-3 HMC700 小数分频引入的杂散图 .....          | 36 |

| 图 4-4 HMC700 为核心的锁相环电路 .....           | 37 |

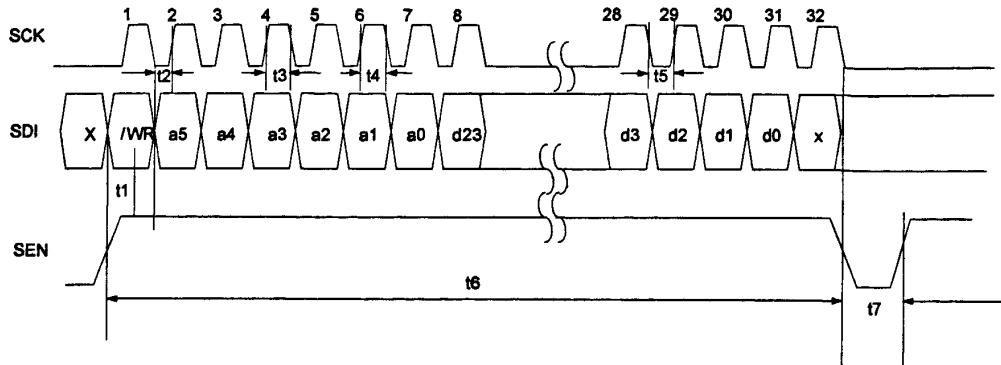

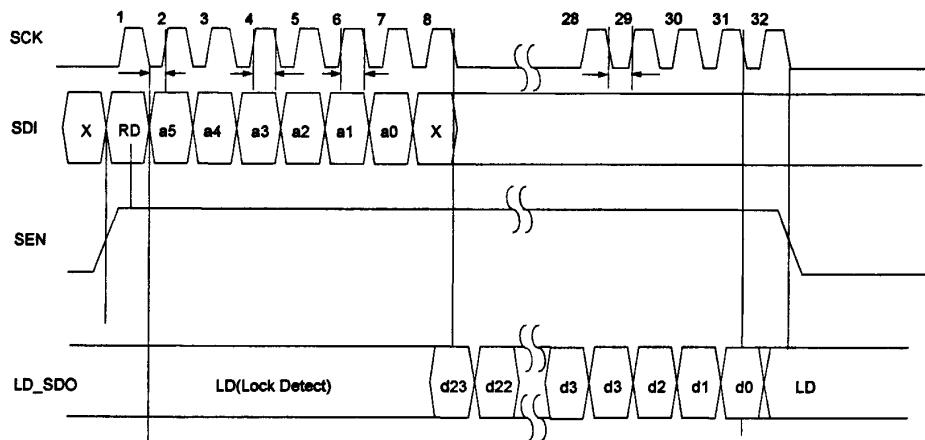

| 图 4-5 HMC700 串口时序——写串口操作.....          | 38 |

| 图 4-6 HMC700 串口时序——读串口操作.....          | 38 |

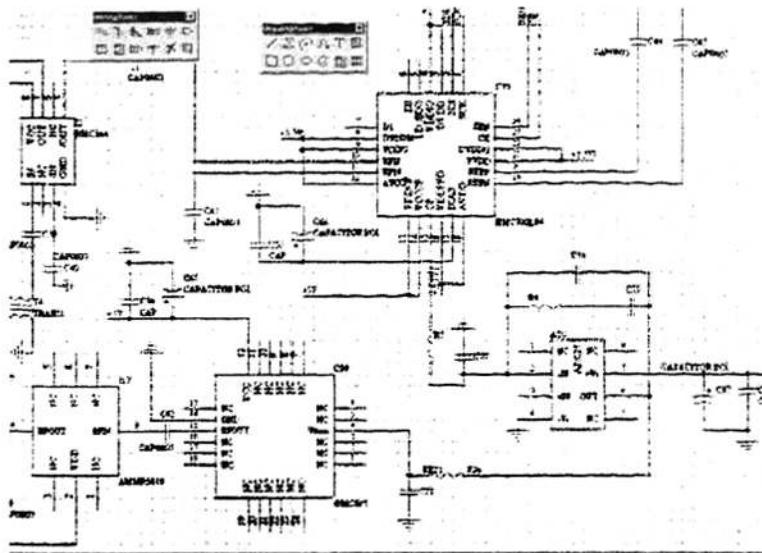

| 图 4-7 6~9GHz 环路原理图 .....               | 39 |

| 图 4-8 牺牲相噪平滑度，在 10KHz 处达到较好的相噪指标 ..... | 40 |

| 图 4-9 综合各方面的因素，得到较好的综合指标 .....         | 41 |

| 图 4-10 6~9GHz 环路 .....                 | 42 |

| 图 4-11 9~11GHz 环路 .....                | 42 |

| 图 4-12 输出端口多路选择器 .....                 | 44 |

| 图 4-13 MA4AGSW3 外围电路图 .....            | 44 |

| 图 4-14 系统的输出功率简图 .....                 | 45 |

| 图 4-15 C8051F360 电路原理图 .....           | 46 |

| 图 4-16 单片机程序流程图 .....                  | 46 |

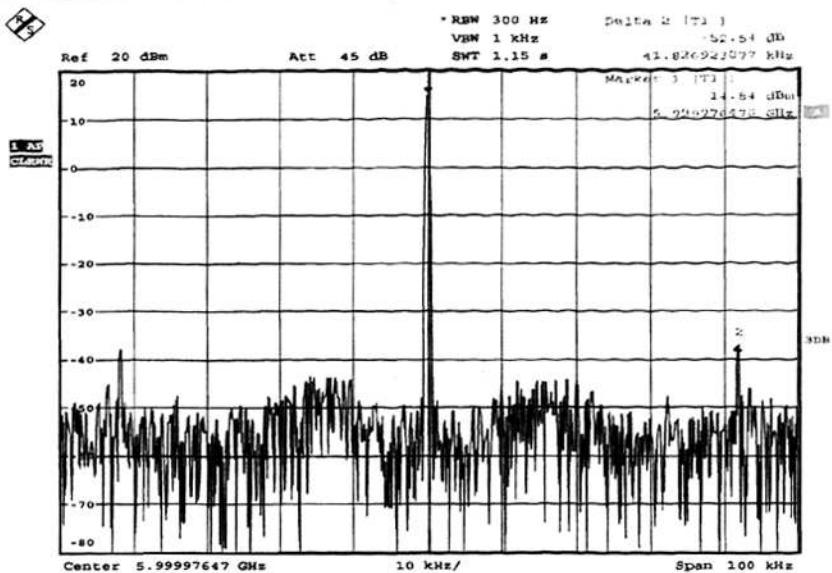

| 图 4-17 MAX660 引入的电源纹波，频率为 41KHz .....  | 47 |

| 图 4-18 MAX660 的外围电路图 .....             | 48 |

## 图目录

---

|                                                     |    |

|-----------------------------------------------------|----|

| 图 4-19 系统的近端杂散效果图 .....                             | 48 |

| 图 5-1 上腔体结构图 .....                                  | 49 |

| 图 5-2 下腔体结构图 .....                                  | 50 |

| 图 5-3 上腔体照片 .....                                   | 50 |

| 图 5-4 输出为 3GHz 时的相噪曲线 .....                         | 52 |

| 图 5-5 输出为 3.9GHz 时的相噪曲线 .....                       | 52 |

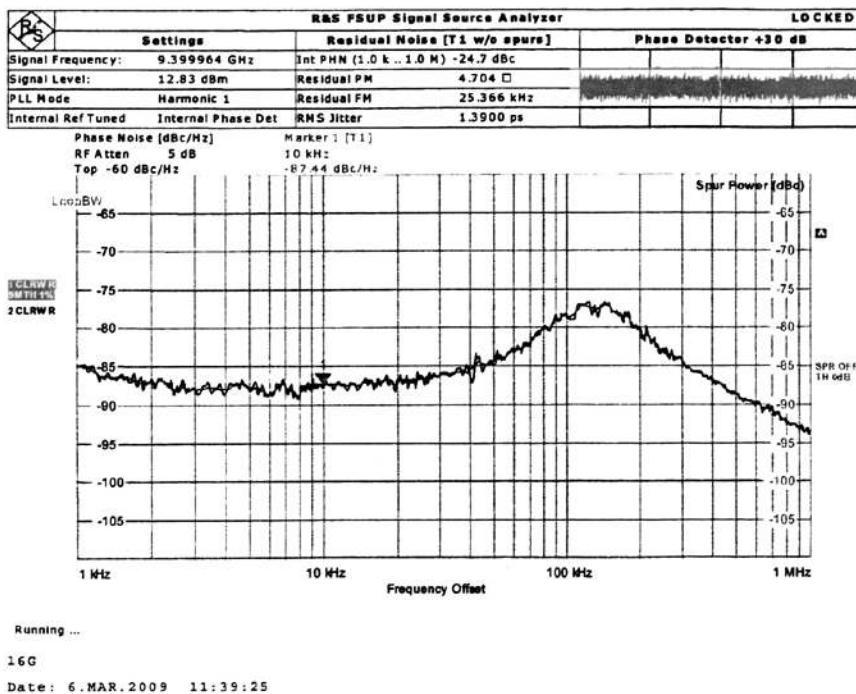

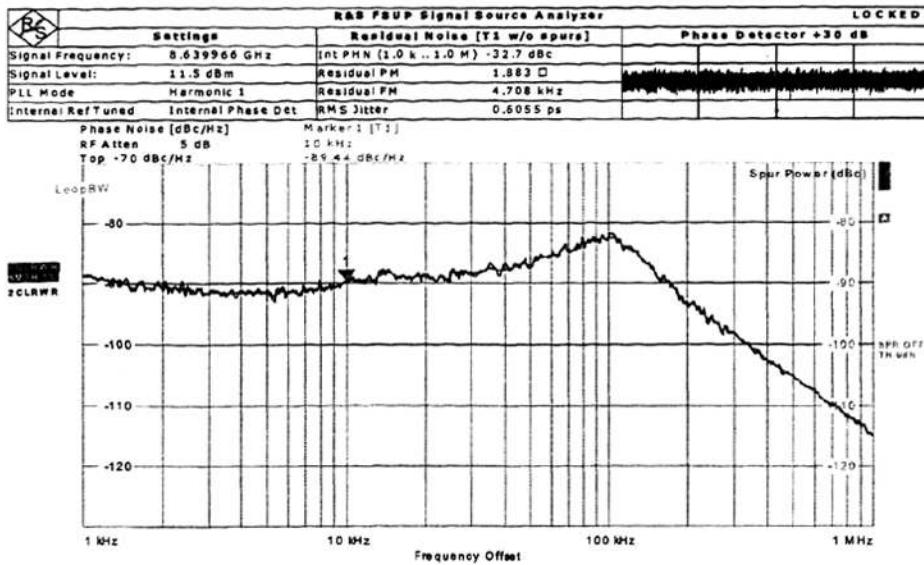

| 图 5-6 输出为 8.64GHz 时的相噪曲线 .....                      | 53 |

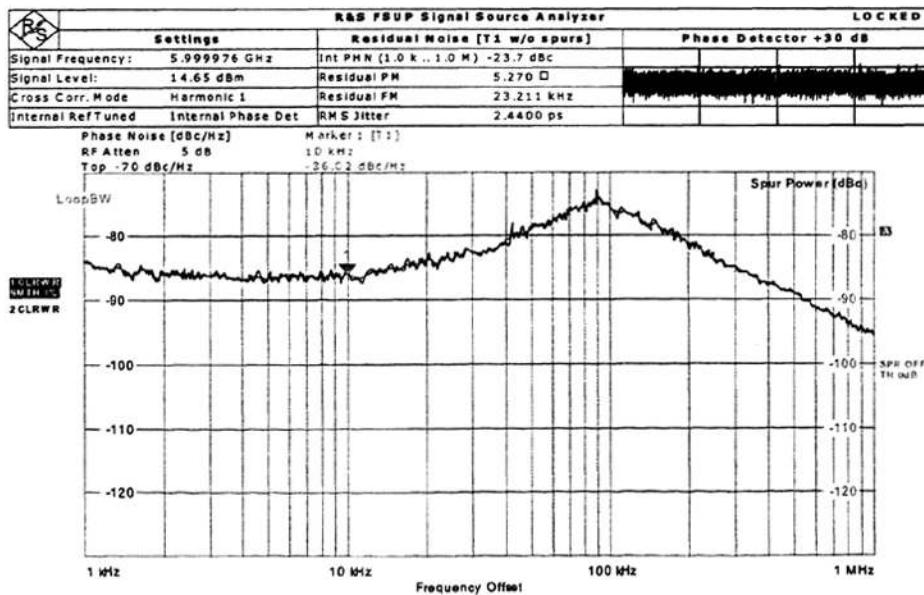

| 图 5-7 输出为 6GHz 时的相噪曲线 .....                         | 53 |

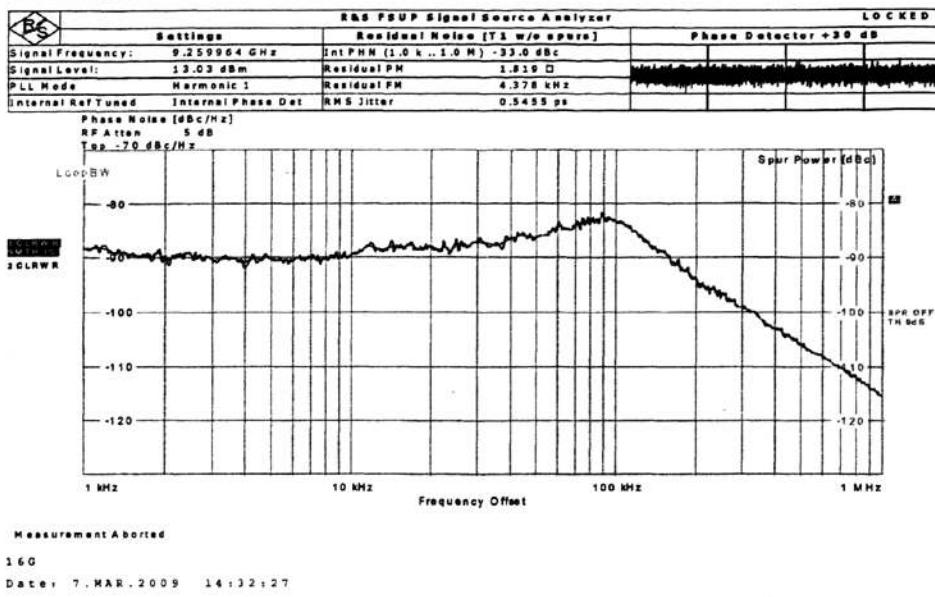

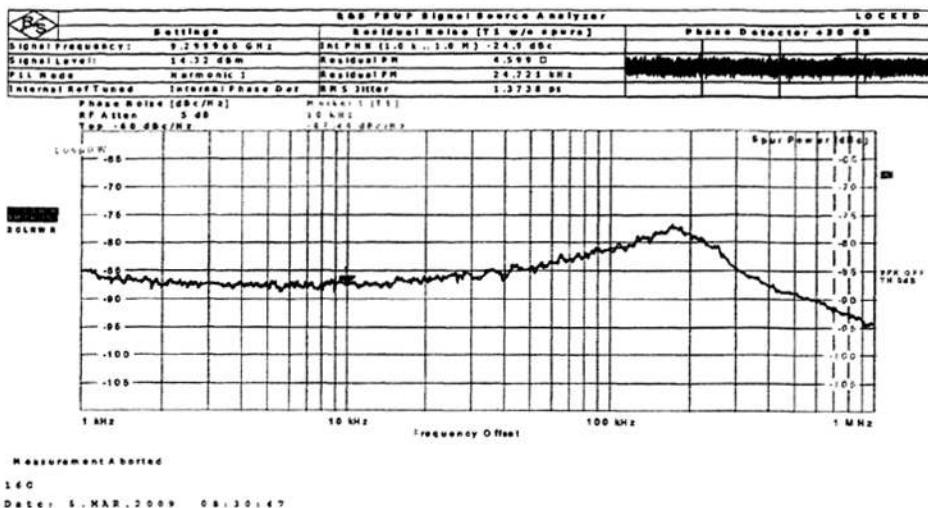

| 图 5-8 输出为 9.26GHz 时的相噪曲线 .....                      | 54 |

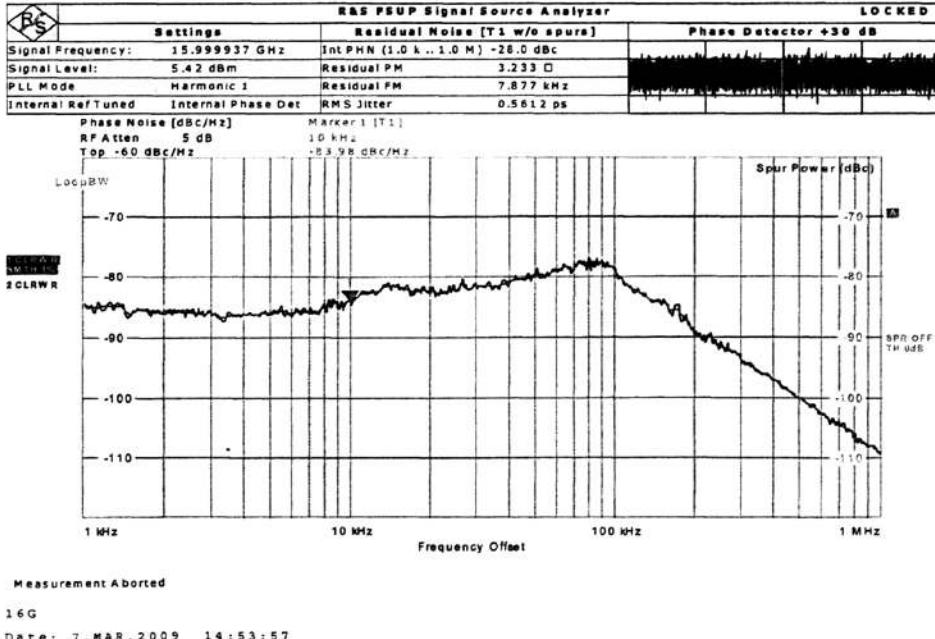

| 图 5-9 输出为 16GHz 时的相噪曲线 .....                        | 54 |

| 图 5-10 系统的远端杂散图 .....                               | 55 |

| 图 5-11 系统的近端杂散图 .....                               | 55 |

| 图 5-12 用信号源分析仪 FSUP-26 以测相噪的传统方式测试@10kHz 的相噪 .....  | 57 |

| 图 5-13 对图 5-12 中的信号用 FSUP-26 以传统的方式测@10KHz 相噪 ..... | 57 |

| 图 5-14 用同一台 FSUP-26 使用它自带的相噪测试功能绘制相噪曲线 .....        | 58 |

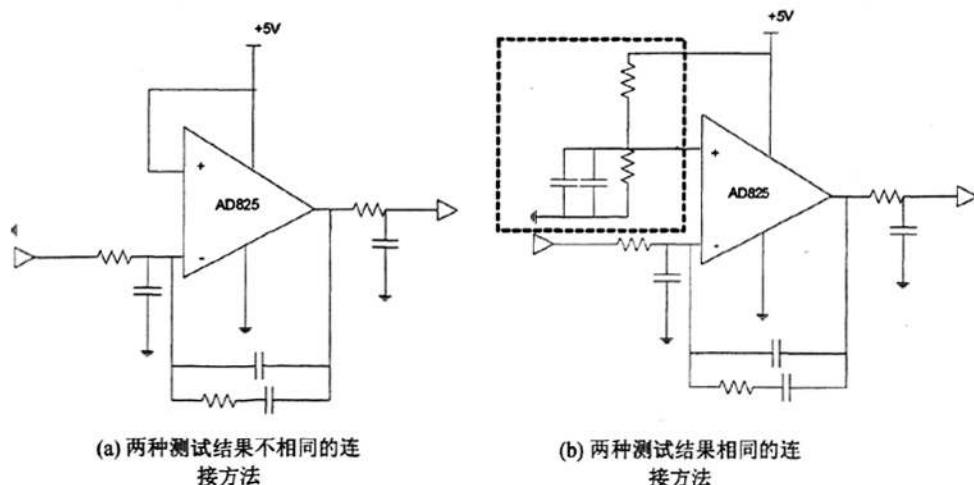

| 图 5-15 AD825 的连接关系 .....                            | 58 |

表目录

|                                    |    |

|------------------------------------|----|

| 表 2-1 相位裕量与阻尼系数的数值关系.....          | 14 |

| 表 2-2 整数分频锁相环与分数分频锁相环的比较 .....     | 19 |

| 表 3-1 HMC700 与 ADF4106 各项指标对比..... | 31 |

| 表 4-1 微带电路 10GHz 直线结构输出损耗 .....    | 43 |

## 独 创 性 声 明

本人声明所呈交的学位论文是本人在导师指导下进行的研究工作及取得的研究成果。据我所知，除了文中特别加以标注和致谢的地方外，论文中不包含其他人已经发表或撰写过的研究成果，也不包含为获得电子科技大学或其它教育机构的学位或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示谢意。

签名: 赖益 日期: 2010年6月3日

## 论 文 使 用 授 权

本学位论文作者完全了解电子科技大学有关保留、使用学位论文的规定，有权保留并向国家有关部门或机构送交论文的复印件和磁盘，允许论文被查阅和借阅。本人授权电子科技大学可以将学位论文的全部或部分内容编入有关数据库进行检索，可以采用影印、缩印或扫描等复制手段保存、汇编学位论文。

(保密的学位论文在解密后应遵守此规定)

签名: 赖益 导师签名: 蔡光生

日期: 2010年6月3日

# 第一章 引言

20世纪初，雷达的基本概念形成，用于对远距离目标进行无线探测、定位、识别等等，在二战和战后都是军队最重要的技术装备。雷达应用非常的广泛，比如飞机导航、预警等等，是目前为止最有效的探测设备之一，不仅能作为近程的跟踪成像，还可以作为远程的遥感遥测。它在军事领域及民用领域有着不可或缺的作用。比如，雷达对空中目标的探测；在气象预报、地质资源勘探勘测、航空交通管理、甚至于当前很热的反恐安全等都有着重要的应用。雷达的具体结构多种多样，从探测手段上说有连续波调频雷达、脉冲多普勒雷达<sup>[1]</sup>、相控阵雷达、SAR、ISAR 等等。其基本的构成主要如下：发射机、发射天线、接收机、接收天线、数字信号处理系统以及终端和伺服系统等辅助设备。发展到今天，现代雷达在干扰与抗干扰，侦测与反侦测等方面有了很多新的突破，比如捷变频技术、脉冲压缩技术、相控阵技术、SAR 等等都使得雷达系统越来越复杂。作为研究雷达技术的一个重要手段，雷达模拟技术越来越重要，这样的技术不仅可以降低研究的成本，也便于研究各个分系统的性能。

## 1.1 雷达模拟器简介及发展状况

近年来，电子技术有了飞速的发展，大量新型雷达涌现，当今先进的电子技术手段，比如捷变频技术、脉冲压缩技术、抗干扰技术、光学跟踪测量技术等都得到了应用。但是，由于雷达本身是很复杂的系统而且造价昂贵，实际装备数量也很有限，无论是对于研究雷达技术还是作为装备单位的训练来说都是昂贵的。雷达模拟器结合了仿真技术与雷达技术，对于雷达技术的研究有着很重要的作用。

雷达模拟技术在国外很早就有广泛的应用，有很多相关的产品。比如 MalibuResearch 公司开发的用于 AN/TPQ-36 迫击炮火控脉冲雷达的雷达环境模拟器。该系统能产生这类雷达测试所需要用到的各种信号，包括了数字、中频、射频多种形式，能模拟常见的几种扫描方式；系统同时还能模拟雷达的回波环境，比如各类噪声、目标、各类杂波与人为干扰等等；除此之外支持线性调频技术/非线性调频技术，QPSK 等几种波形编码方式，也支持连续波调频模式。同时，HP 公司的 X 波段雷达动目标信号 MTI 模拟器，能输出 9~11GHz 的射频信号，可以同

时产生和支路、方位差支路和俯仰差支路三个通道的目标信号。我国雷达模拟技术的起步较晚，不过在近几年也有不错的发展，特别是在窄带毫米波模拟器方面。2000年，由中科大电子工程系研制出了一台雷达毫米波目标模拟器。该模拟器可以模拟线性调频连续波体制雷达的回波信号（35GHz，带宽>500MHz），回波动态范围为100dB，步进0.1dB。电子科技大学在近年来也研制出了一台高分辨率毫米波脉冲雷达信号模拟器，是中国首台3毫米高分辨力脉冲雷达信号模拟源。该模拟器由软件建模再由硬件产生波形，可模拟3毫米波雷达在多种环境下的回波信号、各类杂波以及噪声，在系统噪声、I、Q两路一致性方面都有很好的表现<sup>[2]</sup>。

## 1.2 频率合成技术简介

频率合成技术是将一个或多个高精度高稳定度的频率源（通常由晶体振荡器产生），经过加、减、乘、除的基本运算，产生系统所需要的一系列离散频率的频率产生技术，通常实际的通信系统或者雷达系统对新生成的信号有具体的参数和指标方面很苛刻的要求。频率合成技术为现代通信系统和设备，提供了良好的频率源，有很多用途：可用于调制时产生本振信号，或者是产生已调制信号。因而，电子系统频率源的性能，往往作为了现代电子系统的硬指标，在很大程度上决定了现代电子系统的性能，是现代电子系统性能的一个关键点，一个失败的频率源设计也是一个硬件系统的硬伤。在空间通信、雷达测量、卫星导航等先进的电子系统中，都是利用频率或相位信息完成信息传递和接收的功能，即便使用幅度信息，但还是要在高稳定频率源的前提下才能完成其核心功能，因而频率系统其实是起着电子系统心脏的作用<sup>[3]</sup>。随着近些年来微波和毫米波技术的发展，电子系统对其频率合成器的指标提出了更高的要求。目前的频综系统所用的频率合成技术可分为以下四种，分别是：直接频率合成技术（DS）、间接频率合成技术（即锁相环技术PLL）、直接数字式频率合成技术（DDS）和混合式频率合成技术。

直接频率合成技术是通过使用一个或多个基准源作为系统的参考源，经分频、混频、倍频等电路来产生更多的频率。所有频率一个基准源产生的系统是相干频率合成系统，否则为非相干系统。其优点是原理简单、跳频速度快、相噪低。缺点是结构复杂，因为在系统中为了得到很多的频率点，必须大量使用混频和倍频模块，又没有PLL等器件对信号进行处理，导致系统需要很多的抑制谐波或者交调的滤波器，因此杂散指标是直接频率合成技术比较难的一个问题，特别是宽覆盖系统条件下，直接频率合成技术意味着上100倍以上的体积和很多的器件去组

成原理简单但结构重复且复杂的系统，这样的系统虽然往往有相噪上的优势但因为结构太复杂，而不会单独使用。近年来随着声表面波（SAW）技术以及模拟芯片技术的发展，使得在毫米波频段的很多设计可以集成化，因而直接频率合成技术可以在高频段有更大的发展空间<sup>[3]</sup>。从变频时间上考虑，直接频率合成方案的变频速度最快，可以很容易实现捷变频。因为直接频率合成方案不带锁相环这类的负反馈系统，也不像 DDS 系统有复杂的数字系统，因此它的跳频时间主要由混频、倍频、滤波等部件的响应速率来决定，其中混频、倍频电路几乎不延迟信号（因为可以把混频与倍频电路看成是 4 到 5 级的门电路，这样的电路延时很小，主要的延时是来源于电路中的电抗器件，比如大电容等等），而一般的低阶滤波器的延时很小（高阶的慢波结构延时也应考虑），因此整个频率合成系统的跳频时间一般为  $0.5\mu\text{s}$  以下。在直接频率合成系统中，输出信号的近端相噪指标主要取决于参考源（一般为晶振）的指标，因而比较好，一般接近于理论值。在这类系统中有很多混频、倍频和分频电路，使得对杂散的抑制难度较大，通常会对频率进行合理的规划并且选择合适的滤波器来抑制系统的杂散。

间接频率合成技术，也称为锁相式频率合成技术，是利用锁相环的窄带捕获与跟踪特性将输出的频率锁定在所要求的频率上。使用间接频率合成技术的优点在于锁相环由于其自身的工作特性，是一个相位负反馈系统，系统的响应针对的是输入输出信号的相位而不是幅度。因而可以通过相位锁定这个动态过程建立起高稳态，滤波特性随着环路阶数的增加变得很强，能有效地抑制输出信号的远端杂散，有很好的选择性，门限性能好，由于引入了现代数字以及芯片技术，可以大量集成。因而可以省掉频率源系统中大量的抑制谐波或者交调的滤波器。其缺点在于很难兼顾输出信号的带宽、相应的频率分辨率以及信号相噪杂散和跳频时间等多方面的综合指标。锁相环根据鉴相器的类型来分，可分为传统的模拟环与数字环。在实际应用中，往往是在锁相环的基础上增加其他非线性器件（混频器、倍频器、分频器甚至 DDS）进行改进，构成复合结构，由此产生了混频锁相环，多环嵌套、双模分频频率合成器以及小数分频频率合成器<sup>[4]</sup>等结构，用来解决综合指标的问题。

上世纪 70 年代，微电子集成技术有了长足的发展，用硬件电路实现了一种新的频率合成器类型，即直接数字频率合成技术<sup>[5]</sup>。直接数字频率合成技术对正弦信号进行高密度数字采样存储，在每个时钟周期对相位累加器进行累加，然后根据累加器的值对该数字系统的正弦查找表进行寻址，得到相应的数字信号正弦抽

样值(离散的), 经过采保电路成为阶跃信号, 最后经后级的低通滤波器滤波平滑后, 滤除高阶信号, 得到需要的信号。作为新一代数字频率合成技术, 直接数字频率合成技术(DDS)具有超高的频谱分辨率、很短的跳频时间、比较宽的带宽(从低频可到 40%的激励频率)、输出信号具有相位连续性(可用于产生恒包络信号等复杂的调制信号)、可输出多种波形的信号(纯正弦信号、锯齿波、三角波、LFM 等)、可通过对数字器件进行控制编程(有复杂的 ROM 表以及数字控制部分)、灵活性高、成本低、复杂度小等优势, DDS 的主要性能很大程度上取决于数字端对相位截断技术的处理以及后级的 DAC 位数和非线性补偿技术。DDS 已经得到了广泛应用, 例如在雷达领域, 特别是具有捷变频要求的雷达往往采用这一技术。其他雷达, 例如脉冲压缩雷达这种体制, 为了减小脉宽, 增加距离灵敏度, 得到相位连续的线性调频信号, 也广泛应用这一技术。而有源相控阵雷达, 在后端往往要求对相位等进行调节以弥补前端数字移相器等器件带来的误差也广泛地应用这一技术, 至于波形发生器以及各种合成信号源更是以 DDS 技术为基础。但是直接数字频率合成技术的缺点也同样显著: 首先 DDS 采用的是全数字结构, 根据奈氏采样定律, 输出信号频率不会高过激励源的 1/2, 通常现在主流的 DDS 芯片一般只有 40%左右, 而且输出杂散由于 DAC 等器件的因素一般很大。目前市面上的 DDS 芯片能达到的最高输出频率为 1GHz 左右(国外私人留片能达 5GHz 以上)。以上缺点大大限制了 DDS 在微波射频领域的应用, 因而 DDS 只是在较低频率上出现, 射频前端很难看到 DDS 的应用, 因此如何在提高 DDS 的输出频率的同时抑制其相位截断等机制引入的杂散成为了业界 DDS 研究的热点和难点, 提出了许多种改进方案<sup>[6]</sup>。

将以上前三种技术结合在一起, 就形成了应用最为广泛的混合式频率合成技术。之前所述的 DS、PLL、DDS 三种频率合成技术其优缺点都很明显, 混合频率合成技术则可以扬长避短, 结合各种频率合成技术的优点, 并且在一定程度上可以弥补单一频率合成技术的不足, 从而在综合指标方面, 达到更好的合成效果。充分利用混合频率合成技术设计合理有效的频率合成器方案是现代频率合成器发展的方向, 也是当今频率源设计的难点所在。在本文第三章, 会对常用的几种混合频率合成方式进行分析, 比较几种方案的优劣, 便于方案的设计。

### 1.3 课题简介及意义

本课题来源于西安电子科大的某“雷达模拟系统”项目, 由本实验室和成都

亚光电子股份有限公司第三研究所共同负责雷达模拟器频率源的设计。项目对所设计频率合成器的各个重要指标提出了较高的要求，尤其是在频率覆盖范围、相噪、杂散、输出功率等指标方面，因而在雷达模拟器的研究领域有很强的应用价值，而且该频率源对小步进宽覆盖的频率源设计有很好的指导以及借鉴意义。本教研室承担了雷达模拟器干扰源的 3~16GHz 频率合成器的设计工作。

本频率合成器的输出频率范围为：3~4GHz, 6~11GHz, 14~16GHz，全频段输出信号步进 20MHz，是 8mm 波雷达信号模拟器的一部分，作为了该模拟器干扰源的激励源。本频率源由两个输出覆盖很宽的锁相环组成，这种相对简洁的设计，使系统很稳定，并且输出的各项指标都比较好。

全文的安排如下：

第一章介绍了本课题的背景和研究意义，并给出了雷达模拟器和频率合成技术的基本概念。

第二章对频率合成器的相位噪声以及杂散理论进行了阐述，对锁相环以及混频器（包含微波频段的倍频器）的相噪杂散指标进行了分析。

第三章结合常用的频率合成理论，分析了几种常用频率合成技术的优劣并阐述了本宽覆盖频率合成器所采用的方案和设计理念。对系统的相噪、杂散和功率等指标进行了理论分析与估算，指出了本设计的重点和难点，完成了系统方案的论述。

第四章对本系统的关键硬件电路和软件实现做了详细的介绍，并分析了许多在调试过程中出现的问题，比如环路调试问题、功率控制问题、控制系统实现等等，并总结了需要注意的设计方法，以便作为将来设计的参考。

第五章展示了系统的测试结果，对系统设计以及测试上的一些不足提出了改进意见，总结了相关的一些设计经验。

## 第二章 频率合成器系统相位噪声和杂散的分析

第一章所介绍的3种基本的频率合成方式，都必须基于一定的硬件平台来实现，这些器件比如晶体振荡器、DDS芯片、锁相环、混频器、倍频器等，它们各自的相噪和杂散性能对整个系统的最终输出信号来说，都有可能带来影响。所以，评价一个频率合成器的优劣性，首先要考虑的就是输出信号的相噪和杂散这两个关键的技术指标。本章主要对频率合成器的相噪和杂散理论进行阐述，为本文所涉及的方案设计提供有力的理论支撑，特别是针对系统中所用到的锁相环和微波混频器进行了杂散和相噪方面的分析。

### 2.1 相位噪声理论及基本性质

相位噪声是频率源的一项关键技术指标，它直接影响电子系统的性能和系统设计的成败，往往成为一个失败的系统设计的硬伤，有比较固定的估算和设计准则，也是系统指标中最难改善的指标。频率合成器作为发射信号和接收信号的本振，或是作为各种频率的基准源，在相位噪声方面的指标要求都是越来越高的。因而本章需要着重讨论的就是频率合成系统中的相噪理论。现在电子系统中的电子信息都以随机方式对信号的相位或者频率进行了调制。用以衡量这种噪声的指标是相位噪声。相位噪声，简称相噪，是表征信号源输出频率短期稳定度的最重要指标，是系统内各种噪声作用下产生的输出信号的相位起伏或频率起伏，表现为信号频率在一个平均值上下的随机波动。主要有以下3种类型：散粒噪声、热噪声和闪烁噪声。在理想状态下，正弦波信号可用下式表示<sup>[7]</sup>：

$$V(t) = A_o \sin 2\pi f_o t \quad (2-1)$$

$V(t)$ 表示的是信号在t时刻的瞬时幅度， $A_o$ 表示的信号的最大幅值， $f_o$ 表示的是信号的频率。信号的频谱如图2-1(a)所示。在实际的系统中，信号源内部是存在着各种形式的噪声的，而且还有来自外界信号的干扰，这些干扰信号和噪声的分量使得实际系统中的正弦波信号的输出发生了改变，可表示为如下形式：

$$V(t) = [(A_o + \varepsilon(t)) \sin(2\pi f_o t + \varphi(t))] \quad (2-2)$$

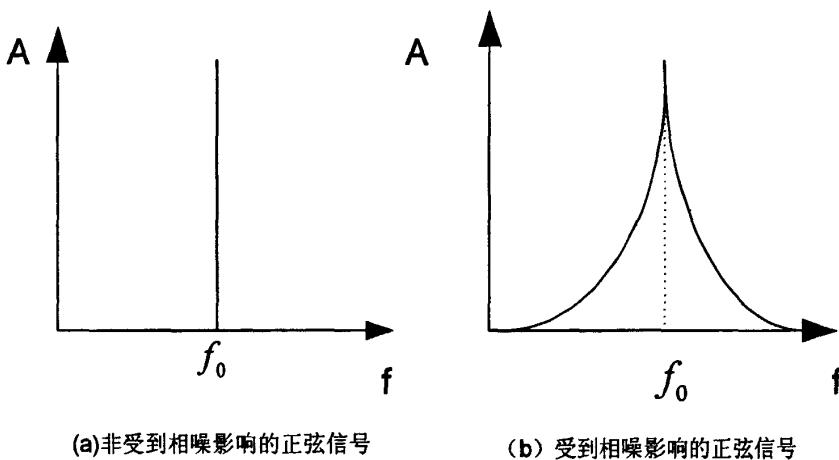

$\varepsilon(t)$  为信号的幅度上的噪声和干扰，称为调幅噪声； $\phi(t)$  为信号相位上的噪声和干扰，称之为相位噪声，对频率和相位是有着很大影响的。由于噪声的随机特性，所以相位噪声的表征是通过统计的方式来表示的，这里一般用功率谱密度来表示，即噪声的二阶统计量。相位噪声会使输出的信号波形发生畸变。在时域上，一般表现为信号的频率或相位在时间轴上的随机变化，在一定区域内随机抖动，在工程上可用阿伦方差等指标来衡量。在频域中，相位噪声对输出信号频率的影响如图 2-1(b) 所示，相位噪声叠加在了输出信号的两侧，形成了主信号的边带。它的存在，引起载波频谱的扩展，在近端主要表现为  $1/f$  噪声。

图2-1 信号理想状态和实际系统的频谱图

相位噪声在表示时，通常使用功率谱密度  $S_\phi(f)$  来描述，往往用分贝数 dBc@Hz 作为衡量大小的单位，由于是功率表征，所以取 10 乘对数，转换公式如下：

$$L(f)(dB) = 10 \lg S_\phi(f)[dB/Hz] \quad (2-3)$$

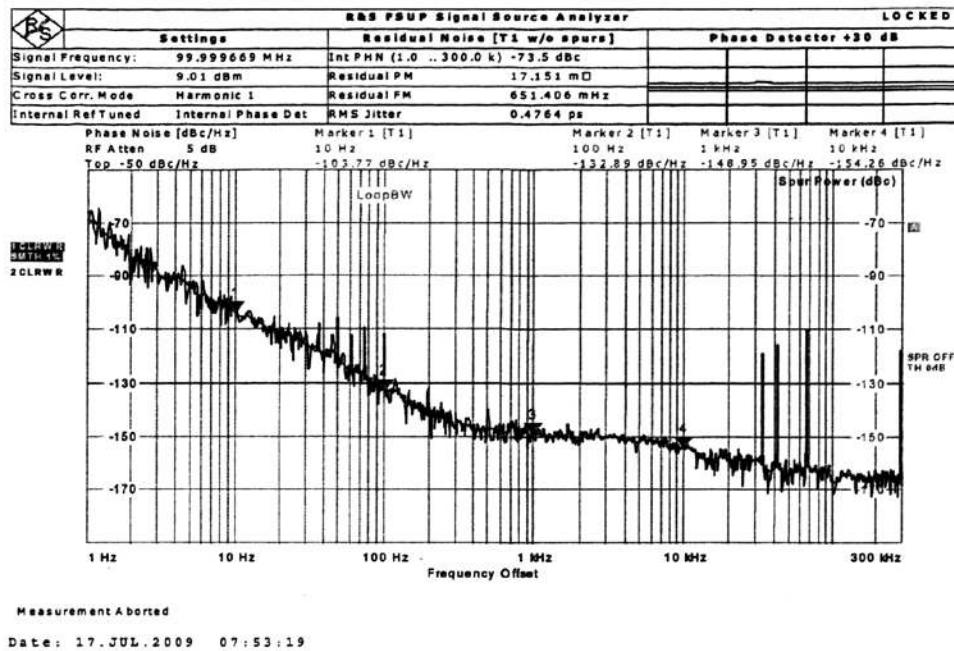

图2-2 实测的 100MHz 晶体振荡器相噪图

由上图可知，实际的高稳恒温晶振的相噪并不是一条单一的谱线，相位噪声实际上是扩展了主信号的频谱，构成了主信号两边的边带，在10kHz以外这类晶振的相噪就趋于稳定，不再有大的变化了。图中所示的晶体振荡器的相噪为-155dBc/Hz@10kHz。关于相噪的测试方法，在文中第五章会有相关的一些阐述，随着测试方法的不同，结果会有一定的差异，但这种差异最多不会超过3dB。

相位噪声有几个常用的性质，在系统设计的时候经常需要用这几个性质对系统的相位噪声指标进行估算，然后便于设计者选择合适的系统方案。相位噪声基本性质如下<sup>[8]</sup>:

### 1. 叠加性

假设系统信号  $A_a \cos[2\pi f_{01}t + \varphi_1(t)]$  和  $A_b \cos[2\pi f_{02}t + \varphi_2(t)]$  为混频器的两个输入信号，两输入信号不相关，则混频器的输出信号可表示为：

$$A_o = A_c \cos[2\pi(f_{01} \pm f_{02})t + \varphi_1(t) \pm \varphi_2(t)] \quad (2-4)$$

混频器输出信号的功率谱密度可表示为：

$$S_{\varphi(f)} = S_{\varphi_1(f)} + S_{\varphi_2(f)} \quad (2-5)$$

$$L(f)(dB) = 10 \lg S_\varphi(f) = 10 \lg (S_{\varphi_1(f)} + S_{\varphi_2(f)}) \quad (2-6)$$

由(2-6)可知最后的输出相噪表现为两者的叠加(功率谱密度的角度)。在实际系统中，往往影响混频器相噪的是相噪差的支路，即频率高的本振对混频器的相噪影响最大。

## 2. 比例性

当信号通过倍频器或分频器这类器件时，则对应的输出信号为<sup>[9]</sup>:

$$A_o = A_c \cos[2\pi N f_{01} t + N \varphi_1(t)] \quad (2-7)$$

式(2-7)中 $0 < N < 1$ 对应分频器， $N > 1$ 对应倍频器，可知倍频器对噪声的幅度增大 $N$ 倍，但是相位噪声的频率保持不变；分频器与之相似，是在原来噪声的振幅上缩小为以前的 $1/N$ ，由此可得到它的功率谱密度为：

$$S_{\varphi(f)} = N^2 S_{\varphi_1(f)} \quad (2-8)$$

$$L(f)(dB) = 10 \lg S_\varphi(f) = 10 \lg (S_{\varphi_1(f)}) + 20 \lg N \quad (2-9)$$

由式(2-8)(2-9)可知，在理想状态下，信号通过倍频器后相噪恶化 $20 \lg N$ ，通过分频器相噪得到改善 $20 \lg N$ 。在实际的系统中，分频器对相噪的改善，还要对比分频器的噪底才行，如果分频的噪底更低，则能改善 $20 \lg N$  dB，如果分频器的噪底较差，则以分频器的噪底为准。

## 2.2 杂散分析

为便于分析杂散的一些基本性质，以单频正弦波在相位上的干扰为例，令 $\varphi(t) = \varphi_m \cos(\omega_m t) \ll 1$ ， $\varphi(t)$ 表示的是相位上的干扰，

$$V(t) = V_0 \cos[2\pi\nu_0 t + \varphi(t)] \quad (2-10)$$

$$\begin{aligned} V(t) &\approx V_0 \cos(\mu_0 t) - V_0 \sin(\mu_0 t) \varphi_m \cos(\omega_m t) \\ &= V_0 \cos(\mu_0 t) - \frac{V_0 \varphi_m}{2} \{\sin[(\mu_0 + \omega_m)t] + \sin[(\mu_0 - \omega_m)t]\} \end{aligned} \quad (2-11)$$

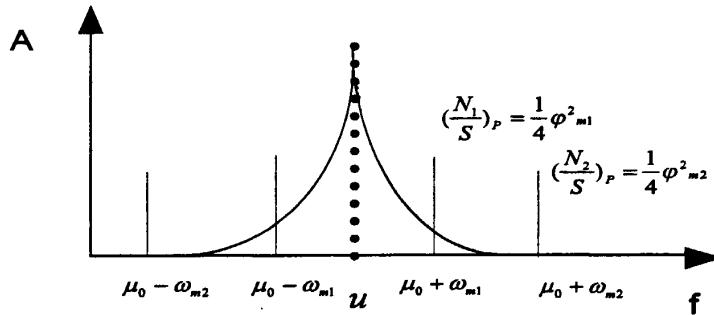

式(2-11)等号右边第一项表示的是载波，为有用的信号，后面二项为杂散调相信号，是对系统有害的信号。杂散对载波上下边带的干扰，出现在信号主峰两边的边带

上,且对称成对出现,在 $f = \mu_0 \pm \omega_m$ 处,信号杂散的平均功率 $P_{spur}$ 为: $\frac{1}{2}\left(\frac{V_0\varphi_m}{2}\right)^2$ ,

故杂散的相对功率可表示为:

$$L_c(f) = \frac{2P_{spur}}{P_s} = \frac{1}{2}\varphi_m^2 \quad (2-12)$$

图2-3 受杂散影响的载波信号

有以上分析可知,这样的杂散信号其实是调制在了载波主频相位上的干扰信号,有确定的位置及大小,一般来说可把杂散粗略的分为近端杂散以及远端杂散。如果信号同时受到多个寄生频率调制,则各个寄生频率造成的杂散的相对功率都要满足式(2-12)<sup>[10][11]</sup>,即其各自的特性具有独立性。一般来说,信号的杂散无论是经过混频器还是倍频器,其与信号主峰的相对位置都不会发生改变,即杂散的付氏频偏不会改变,但以上器件会引入新的干扰,即混频器引入的交调以及倍频器引入的高次谐波。对于锁相环来说,数字鉴相器引入的鉴相纹波是锁相环引入的最主要的杂散,在设计时,应引起足够的重视。

## 2.3 锁相环的工作原理及相噪杂散分析

随着集成电路的快速发展,锁相环已经成为现代电子系统中不可替代的一部分,有着广泛的应用,除了作为同步时钟外,还可以在射频模拟电路中作为本振和参考源。锁相环,从概念上讲,是一个相位反馈系统,因而包括了控制系统中常提到的线性控制系统(对传统环路的锁定状态)与非线性的控制系统(在环路的捕捉状态时,在环路中引入分频、倍频以及混频等非线性器件后,表现出新的非线性),所以,分析锁相环,一般来说是以反馈控制系统的方向来分析的,即以环路的稳定性以及捕获锁定过程的建立来分析环路的动态过程。本节重点是分析

环路的组成及基本工作原理、锁定过程以及的环路的稳定性和噪声。

### 2.3.1 锁相环的基本工作原理

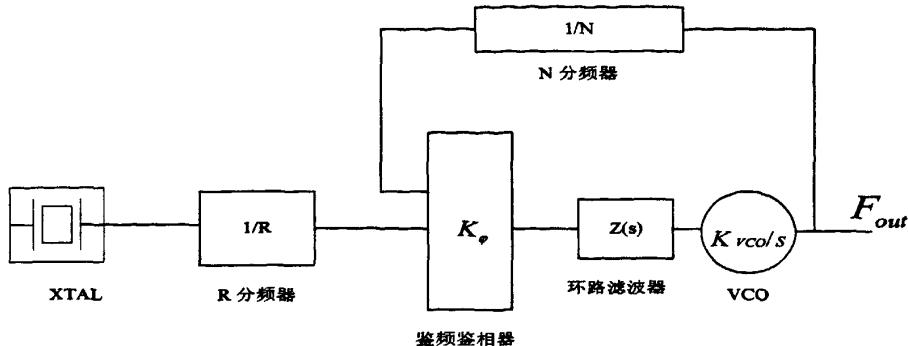

基本的锁相环结构如图 2-4 所示，锁相环由前置的 R 分频器、环路的 N 分频器、鉴相器、环路滤波器、VCO 等组成。

图2-4 基本锁相环原理框图

鉴相器（Phase Detector）用于检测出两个输入信号(参考端与反馈端)的相位差，现在一般为数字鉴相器+电荷泵结构。

环路滤波器（Loop Filter）是将鉴相器输出含有纹波的直流信号平均化，将此变换为交流成分少的直流信号的低通滤波器。环路滤波器除滤除纹波功能以外，还有一种重要作用，即决定稳定进行 PLL 环路控制的传输特性。环路滤波器可分为有源滤波器以及无源滤波器，而且是针对信号相位的滤波器

压控振荡器（VCO:Voltage Controlled Oscillator）是用于输入直流信号的电压去控制振荡频率，它是一种可变频率的振荡器<sup>[12]</sup>。

由图可知其最终的输出频率为

$$F_{out} = N * XTAL / R \quad (2-13)$$

### 2.3.2 PLL 跟踪和捕捉以及锁定过程

锁相环的两个基本的稳态是：锁定和失锁，在两个稳态之间的动态过程为跟踪与捕捉。这两个动态过程的分析有很大的差别。环路在跟踪状态时，由于环路的相位误差较小，通常是根据线性系统的特性来分析的，即假定环路的鉴相器是处在线性状态的，把环路方程线性化，即这时的跟踪特性为环路的线性动态特性。

对其开闭环的传递函数进行 Laplace 变换来分析瞬态响应和稳态响应。而环路进入捕捉过程时，有一个判断捕获与不捕获的门限，即能进入锁定的最大的频差也叫环路的捕捉带，这时环路动态方程是非线性常微分方程，很难求得它的解析解，只能在简化电路特性的基础上通过数值分析的方法求得它的近似解。环路锁定时，瞬时频差  $\Delta w_e$  为零，相位误差为常数(可能等于零，有可能不是零)，这个时候的相位误差被称为稳态相位误差  $\varphi_e(\infty)$ 。由环路的锁定状态方程  $K_d K_{vco} K_F(0) \sin \varphi_e(\infty) = \Delta w_i$  得：

$$\varphi_e(\infty) = \sin^{-1} \frac{\Delta w_i}{A_{\sum_0}} = \sin^{-1} \frac{\Delta w_i}{K_d K_{vco} K_F(0)} \quad (2-14)$$

$K_d K_{vco} K_F(0)$  是环路的直流增益， $\Delta w_i \leq K_d K_{vco} K_F(0)$ ，则直流增益越大，稳态相差越小。由环路原先的锁定状态，慢慢改变输入频差  $\Delta w_i$ ，然后锁相环通过跟踪过程保持它锁定的输入，这时的最大频差被称为锁相环的同步带。因此，直流增益大意味着同步带越大。提高直流增益可以通过在鉴相器与 VCO 之间加入直流放大器来实现，因此有源滤波的环路其同步带会高于无源滤波器的环路，从电荷泵的角度来分析，直流放大器增加了电荷泵对后级 VCO 电调端的驱动能力，当然这样对环路的其他指标的影响也是巨大的，比如有源滤波环路比无源滤波环路的相噪性能差，因为实际的直流运算放大器其实也是有一定的非线性特性的，再加上器件本身的热噪声，所以会恶化环路的相噪。环路带宽的优化设计有利于环路的锁定和其他性能，在这方面近年来，有很多这方面的研究，其基本点都是增加环路的捕获与跟踪性能<sup>[13][14]</sup>。

### 2.3.3 锁相环稳定性分析

锁相环是一个相位负反馈的系统，当它处于锁定状态时，如果在外界干扰、噪声等因素的作用下，能继续保持环路的平衡则环路是稳定的，稳定裕量是衡量环路能够承受多大干扰的量纲，包括了幅度裕量和相位裕量两个量。幅度裕量是在相移  $\phi = 0$  时，闭环系统变为不稳定的最小的附加增益，即幅度裕量为负值，数值越负，越稳定通常要求  $G_m \leq 20 \log |H_o(w_k)|$ ；相位裕量的定义是增益  $K = 1$  时，闭环系统变为不稳定的最小的附加相移，对于稳定的反馈系统， $\phi_m$  必须为正值， $\phi_m$  越大，表示系统越稳定，一般要求  $\phi_m \geq 45^\circ$ 。实际应用中，往往是用系统的开环函数的幅频特性和相频特性来得出增益和相位裕量的，并且可以在波特图中知道系统不稳定点所对应的频率点<sup>[15]</sup>，也可以通过对阻尼系数  $\xi$  的考虑来获得相应

的相位裕量的信息，因为阻尼系数  $\xi$  与相位裕量  $\phi$  是成正比关系的。以理想积分滤波器为例，可分析环路的稳定裕量，以及稳定裕量与其他环路参数的相互关系<sup>[16]</sup>。理想积分滤波器系统函数和对应的环路开环传递函数如公式(2-15)至(2-19)所示：

$$K_F(s) = \frac{1+s\tau_2}{s\tau_1} \quad (2-15)$$

$$w_n^2 = \frac{K_d K_0}{\tau_1} \quad (2-16)$$

$$\xi = \frac{\sqrt{K_d K_0} \tau_2}{2\sqrt{\tau_1}} \quad (2-17)$$

$$H_0(s) = \frac{K_d K_0}{\tau_1} \cdot \frac{1+s\tau_2}{s^2} = \frac{2\xi w_n s + w_n^2}{s^2} \quad (2-18)$$

$$\phi_{H_0} = -\pi + \tan^{-1} \Omega \tau_2 \quad (2-19)$$

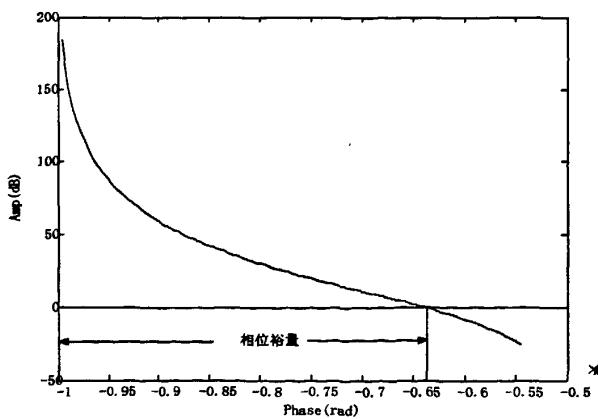

图 2-5 是一个理想积分环路开环函数幅相特性图，由图可知该环路的相位增益为 113 度。在实际设计时，因为相位裕量是正比于阻尼系数  $\xi$  的，所以一般的设计都会把  $\xi$  设计为 0.7 以上，这样就能保证环路的相位裕量 45 度以上，这样的环路系统就能获得比较稳定的性能。

图2-5 理想积分环路开环函数幅相特性图

相位裕量  $\phi$  与阻尼系数  $\xi$  的关系可如公式(2-20)与表 2-1 所示

$$\sec \phi - \tan \phi = \frac{1}{4 \cdot \xi^2} \quad (2-20)$$

表2-1 相位裕量与阻尼系数的数值关系

| 相位裕量 $\phi$ | 阻尼系数 $\xi$ |

|-------------|------------|

| 30°         | 0.6580     |

| 35°         | 0.6930     |

| 36.87°      | 0.7071     |

| 40°         | 0.7322     |

| 45°         | 0.7769     |

| 45°         | 0.8288     |

| 55°         | 0.8904     |

| 60°         | 0.9659     |

| 61.93°      | 1.0000     |

| 65°         | 1.0619     |

分析开环函数的相频特性：临界相位值越远离  $-\pi$ ，相位裕量则越大，稳定性越好；而环路增益时， $\xi$  值越大，瞬态响应的过冲量则越小，其实  $\xi$  越大意味着系统是有阻尼振荡，即刚开始的冲击能量会随着振荡时间的增长而逐渐衰退，最后趋于稳定，即这样的系统参数是有利于环路的稳定性的。有很多关于这方面的论文通过探讨具体的锁相环电路来研究环路的稳定性问题，因为环路的结构确实多种多样，许多特性不能一概而论<sup>[17]</sup>，为了方便分析，可以借助于 ADS 等工具，不过这类工具只能对锁相环的同步过程进行分析，捕获过程的分析往往不是很准确。环路带宽对环路输出的频谱纯度影响其实很大，环路带宽越小，则环路的通带越小，即环路滤波特性的拐点越近，比如高增益二阶环，按拐点之前-6dB/倍频程，拐点之后-12dB/倍频程计算，可知其所对应的频谱纯度也越好。因此增加稳定裕量的同时，应使环路带宽不增加，也就是说  $\tau_2$  增大时，应该同时适当减小环路增益或是  $\tau_1$ 。不然的话，稳定裕量的增加将带来的是环路频谱纯度恶化这样不可忍受的结果。有许多关于锁相环作为低抖动时钟源的应用，这些应用都是考虑到了环路（无论是数字的，还是模拟的）在作为源时的稳定性<sup>[18]</sup>。

### 2.3.4 锁相环噪声性能

在实际工程应用中，应该注意的是环路的各个部件都会引入新的噪声，噪声

的类型如前所述，其中包括来源于参考信号的输入噪声  $N_r$ 、环路部件产生的热噪声以及压控振荡器控制端所感应的寄生干扰等，锁相环的噪声有很多种，比如鉴相器噪声  $N_{PD}$ 、环路滤波器噪声  $N_{LP}$ 、VCO 内部噪声  $N_v$  等，在后面第三章还要对宽覆盖系统相噪进行详细分析。在实际应用中，除了考虑器件的自身的噪声性能外，还应注意环路各部分的基底噪声对环路性能的影响，这样的影响是有别于理想模型的<sup>[19]</sup>。锁相环的具体特性不同，相应的环路中各类噪声对环路的影响也有很大的不同。当锁相环用于锁相鉴频或者载波时，需要重视的是输入加性噪声和调制噪声对锁相环输出信噪比的影响；当锁相环用于频率合成器时，往往环路的输入参考信号都是频谱纯度很高的信号源，比如高稳的晶体振荡器，因而要对 VCO 的内部噪声和鉴相器电荷泵的信号泄漏这类影响着重考虑。噪声与干扰具有随机性，因而环路的动态方程也是一个非线性随机微分方程，不能用传统的解析计算的方式得到准确解，常常对环路的噪声性进行的是统计分析或者近似分析的方法。一般来说，为了便于数学上的分析，总是假定噪声及干扰源是统计独立的，应用叠加原理，可分别求出各噪声与干扰对环路的响应，再进行求和叠加得到总的噪声响应。对于低相噪的频率合成系统，业内做了很多很独到的分析，对锁相环的经典模型也分析得比较透彻，虽然基于不同的半导体技术，但得到的结论还是比较相近的，特别是业内最常用于锁相环技术的 CMOS 工艺，环路模型的建立更是考虑到了最新的工艺能力<sup>[20] [21] [22]</sup>以及相应的新的环路结构，比如当前最常用的是小数分频数字环路。还需要注意的是本论文所提到的公式都是功率计算，应以 dB 作为单位计算。

锁相环的输出相噪可表示为：

$$L_o(f) = L_L |H(f)|^2 + L_H |H_e(f)|^2 \quad (2-21)$$

$L_L$ 、 $L_H$  分别表示的是环路总的低通型相噪和总的高通型相噪， $H(f)$ 、 $H_e(f)$  是环路的闭环传递函数和相位误差传递函数，由公式(2-21)看出锁相环近端相噪主要由各环路参数决定，而锁相环的远端相噪则受 VCO 的影响。实际上，可把锁相环看作是一个倍频器（当然这里只是简单的近似，实际上要考虑影响很多），输出相噪则至少是输入信号相噪的  $k^2$  倍，变换为相噪，即相噪恶化  $20\log k$  dB， $k$  是锁相环环路总的分频数<sup>[23]</sup>，这是一般的环路理论上估计的最低相噪。环路带宽的设计是锁相环设计的一个关键，它其实是开环传递函数（幅度相位函数）幅度为 1 时所对应的频率。当只考虑输入参考信号和压控振荡器的相位

噪声而忽视鉴相器的噪声时,从式(2-21)可以看出,这个条件下是希望锁相环环路带宽越低越好;但是如果要过滤压控振荡器的相位噪声,因为这类噪声影响的是锁相环的远端,这时的设计要求锁相环环路带宽越宽越好。综合考虑环路带宽的两面性,从设计的角度上来说,一般是在上述两条噪声源谱密度曲线的交汇点附近确定环路带宽<sup>[21][22]</sup>(当然还有其他的考虑,此处为了便于分析环路带宽的问题,暂时忽略其他因素的影响,比如环路滤波器带来的影响)。此外,由前面的阐述可知,环路带宽还影响环路的捕捉时间以及稳定性。环路带宽越大,捕捉时间越短,稳定裕量越大。综上所述,环路带宽的设计是个折衷考虑的过程,是对捕捉时间、稳定裕量、输出频谱纯度等环路的主要性能的平衡设计的过程。另外,为了减小鉴相频率以及其谐波对环路的输出频谱纯度的影响,通常情况下的锁相环环路带宽小于鉴相频率的十分之一。但是在锁相环的输出端仍然有泄漏的鉴相纹波,产生的原因多为线路间的耦合,表现为锁相环的输出在频谱的两端存在对称的频率为鉴相频率的杂散信号<sup>[24]</sup>。

VCO 的电调端通过输入的电压对输出的频率进行控制,实际上也是对 VCO 的输出相位的控制,假设 VCO 的控制端存在一单频的干扰信号,

$k \sin(2\pi f_c t)$ ,

$|k| << 1$ ,

$f_c$  是锁相环的鉴相频率。环路锁定以后,则压控振荡器的控制端信号为

$V_c(t) = V_0 + k \sin(2\pi f_c t)$ , 那么 VCO 输出频率为:

$f_o = f_n + A V_c(t)$ , 其中

$f_n$  被称为压控振荡器的自然谐振频率。由以上可推导出压控振荡器的输出信号为:

$$\sin[2\pi(f_n + V_0 A)t + Ak \sin(2\pi f_c t)] \quad (2-22)$$

其中  $|Ak \sin(2\pi f_c t)| << 1$ , 由前面的分析可知,(2-22)的频谱中会存在  $f_n + V_0 A \pm f_c$  的杂散信号,即为鉴相纹波。通常情况下,环路的有源滤波器为 2 阶滤波器,这样的滤波器实际上对鉴相纹波这类强耦合信号而言,滤波能力是有限的,因而通常会在有源滤波器的前后增加滤波器,通常为一阶 RC 低通,相当于增加了环路滤波器的级数,故可以把鉴相纹波抑制在较低电平。对于纹波的分析有很多方法,常用的仿真是基于具体电路以及具体半导体技术来研究的,这样的研究在近些年主要是基于 CP\_PLL (电荷泵) 的分析<sup>[25]</sup>,数字环技术相对于模拟环在跟踪锁定能力方面有着不可比拟的优势,当然 CP\_PLL 的纹波泄露一直以来都是锁相环芯片设计者很头疼的问题,具体的用于抑制纹波的芯片设计相关技术不是本文的重点,就不再详细阐述,对于此类技术的分析,可参看文献 25

## 2.4 分数分频锁相环技术

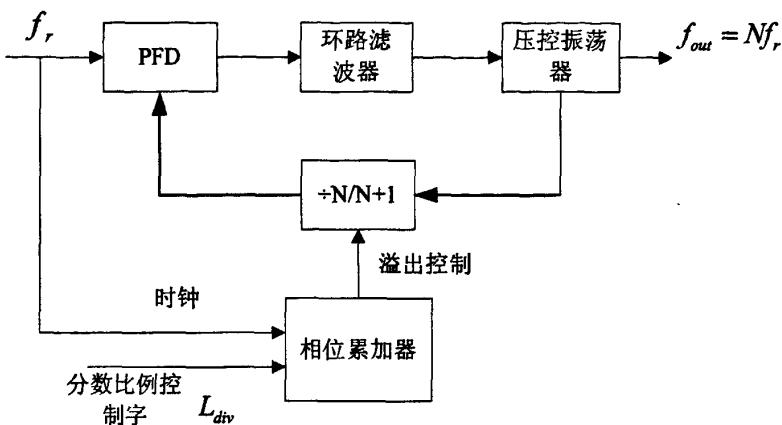

在整数 N 分频锁相环中, 输出频率只能是鉴相频率的整数倍,  $F_{out} = N * F_{ref} / R$ , 这便限定了整数分频锁相环输出信号的频谱分辨率, 因为整数分频锁相环的步进必然是  $F_{step} = F_{ref} / R$ 。在传统的整数锁相环的基础上, 可在环路中引入分数分频器, 产生了分数分频锁相环, 其结构如图 2-6 所示。由图可知, 与传统的锁相环相比, 分数分频器的实现一般来说是用吞没脉冲的方式, 即分频器的分频比可以在两个整数 N 和 N+1 之间变化。

图2-6 分数分频锁相环结构 (双模分频器)

一般来说分数分频锁相环中, 相位累加器的控制时钟是引的参考时钟。相位累加器在每个时钟周期将其分频比控制字  $L_{div}$  累加。在累加器溢出之前, 双模分频器 N/N+1 的分频比是 N, 当累加器的输出溢出后, 双模分频器的分频比则变换为 N+1。取平均值后, 分频器的分频比就变为 N 到 N+1 之间的一个分数。设累加器的长度为  $L_{acc}$ , 每  $L_{acc}$  个周期, 累加器溢出  $L_{div}$  次。即在  $L_{acc}$  个时钟周期内, 分频器的分频比为  $L_{div}$  次 N+1; 其他周期内, 分频比都为 N。可得平均分频比  $N_{avg}$

$$N_{avg} L_{acc} = N \cdot (L_{acc} - L_{div}) + (N + 1) \cdot L_{div} \quad (2-23)$$

$$N_{avg} = N + \frac{L_{div}}{L_{acc}} \quad (2-24)$$

分数分频器使得在锁相环鉴相频率即整数频率步进不变的前提下, 能输出更小的频率步进。分数分频锁相环频率合成器可以在保证环路稳定性的同时拥有更

高的参考频率。由前面的阐述可知，分数分频比其实是通过求均值来获得的，分频比在  $N$  与  $N+1$  间变化，输出频率也在  $N \times f_r$  和  $(N+1) \times f_r$  间变化，所以从微观上分析，分数分频锁相环其实不同于整数分频锁相环，整数分频锁相环是一种稳态的锁定，而分数分频锁相环其实是在两个接近的锁定状态下摆动的亚稳态。因而，这种周期性的摆动会产生新的杂散。并且这个杂散的主峰通常会落入环路滤波的通带之内，所以它的功率很大。另外一种分数分频锁相环合成器采用的是 Sigma-Delta 技术，通过随机的选择  $N/N+1$  的分频比例，来实现分数分频。可以把图 2-6 中的  $N/N+1$  结构看作是一个一阶的 Sigma-Delta 结构，只是在其中要引入随机的置数装置。通过 Sigma-Delta 的技术阐述可知，随着 Sigma-Delta 阶数的增高，则伪噪声性表现得越好，即系统能降低分数分频带来的杂散。但阶数的增高也使系统的稳态的建立过程较长，在 Sigma-Delta 中，计数器一般不用链式结构，因为这样会增加计数的反应周期，取而代之的是多模分频器，此外为了使分数分频带来的相位失配错误降低，在现代的 IC 技术中引入了数字信号处理的方式进行改善，一个主导的思想是在多模分频器中引入相位内插等数字信号处理的技术来使固有的多模分频器杂散随机化，此类技术是将来在 IC 方面一个很好的发展方向<sup>[26]</sup>。

## 2.5 整数分频锁相环与分数分频锁相环的比较

在实际的许多电子系统中，如果采用整数分频锁相环，则系统信道间隔  $f_{ch}$  很小，因为锁相环鉴相频率  $f_r = f_{ch}$ ，由前面的论述可知，锁相环鉴相频率太低，会影响锁相环的稳定和性能指标，例如： $f_r$  会限制环路的带宽，窄的环路带宽会限制锁相环的频率切换速度，严重影响变频时间。而在分数分频锁相环中，输出频率是输入参考频率的分数倍，所以  $f_r$  可以远大于  $f_{ch}$ 。大的  $f_r$  意味着宽的环路带宽，因而可以实现捷变频等关键技术。即从一般的原则上来讲，选择整数分频是为了获得杂散方面的指标，而分数分频则是为了获得高的环路带宽，即高的跟踪锁定能力，更好的相噪指标。但是分数分频锁相环的最大问题是，传统的周期运行的双模分频器会产生分数杂散（当然有其他技术可以进一步抑制分数分频带来的杂散），在前一节已经做了充分的讨论了。目前常用的许多减少分数杂散的方法有相位插入、相位随机抖动、 $\Delta-\Sigma$  调制等，当然这些方法大都是用信号处理的方式来补偿模拟输出<sup>[27][28]</sup>，即利用置数的伪随机特性来降低某个强杂散的技术。

对于两者的区别可如表所示。

表2-2 整数分频锁相环与分数分频锁相环的比较

|       | 整数分频锁相环      | 分数分频锁相环 |

|-------|--------------|---------|

| 分频器类型 | 整数           | 分数      |

| 频率步进  | 较大           | 较小      |

| 相噪指标  | 较差（由于分频比的原因） | 较好      |

| 杂散指标  | 较好           | 较差      |

## 2.6 混频器相噪与杂散特性

在现代电子系统中，一般来说要把带有信息的低频信号调制到高频信号上去，是利用混频器来实现的，更特别的是，在 X 波段以上的倍频器，大多是通过混频器的相干混频取输出实现的（一般不采用把放大器推饱和取谐波的方式，因为这种方式在高频段往往是不稳定的），故有必要说明一下混频器基本的特性，以便于说明高频段信号调制的一些基本概念。在射频模拟电路中，通常是利用二极管，三阶管的非线性特性，来产生多个频率分量。混频器就是多个二极管或者三极管利用管子自身的非线性特性，来实现信号的乘法即频率的加减法，由此可知其他微波射频类器件的参数含义。当前混频器在高频段，比如 V 波段或者 W 波段多采用 HEMT 管或者 PHEMT 管，平衡模式或者非平衡模式都有各自的应用领域 [29][30]。对混频器而言，参与混频的两路信号为互不相关的信号时，由前面的讨论可知，混频器的输出相噪的功率谱密度为参与变频的两路信号的相噪功率谱密度之和，因而可以对系统频谱纯度进行初步的估计， $L$  为相噪的功率谱密度， $f$  为相对频偏<sup>[29]</sup>：

$$L_c(f) = L_{c1}(f) + L_{c2}(f) \quad (2-25)$$

即变频会带来系统相噪的恶化。实际应用过程中，对混频输出相噪的影响最大的是相噪较差的支路<sup>[31]</sup>。

常用的非线性器件有二极管、场效应管（FET）和双极性晶体管（BJT）。混频器在线性时变工作时，要求射频输入是小信号，本振输入是大信号。与 FET、BJT 相比，二极管不需要偏置，低功耗，开关速度快，常用于混频电路。FET 是平方律特性器件，由构成的混频器产生的无用频率成分较少。混频器的常用电路结构是：单平衡混频器和双平衡混频器<sup>[32]</sup>。混频器有很多衡量指标，比如变频损耗、噪声系数、线性度、互调失真（IMD）、本振激励电平、端口隔离度、直流失

调、功耗。而一般在设计中最为关心的是变频损耗、噪声系数、线性度以及端口隔离度。混频器的变频损耗根据不同的混频器结构会有很大的差异。在混频器中，产生 IIP<sub>3</sub> 的原因是信号具有多载波特性，如果在射频的输入端有多个载波信号混合，那么这些信号经过混频器这类非线性器件，就会产生很多交调分量。如果两个载波  $f_{IF1}, f_{IF2}$  相隔较近，根据交调理论，三阶交调  $f_{IP3\_1}, f_{IP3\_2}$  会在  $f_{IF1}$  与  $f_{IF2}$  之间，很难滤除，具体公式如下：

$$f_{IP3\_1} = 2f_{IF1} - f_{IF2} \quad (2-26)$$

$$f_{IP3\_2} = 2f_{IF2} - f_{IF1} \quad (2-27)$$

假设混频器是工作在线性区间，则射频输入每增加 1dB，三阶交调就增加 3dB。设输出有用信号功率  $P_o$  与三阶交调信号功率  $OutIP3$  偏差为 A(dBm)，那么：从理论上讲，只要经过  $A/(3-1) = A/2dBm$ ，输出的三阶交调功率就与需要信号的功率相同，这时对应的输入功率就是  $IIP3_{in}$ ，故得出：

$$IIP3_{in} = P_{in} + A/2 \quad (2-28)$$

在实际的电子系统中，IIP3 超过了器件的 1dB 压缩点，已经在非线性区域，而且一般超出了器件的输入极限，故 IIP3 不是实际存在的，而是计算的估计值。对于不同的输入频率，混频器的三阶截点是不同的，即混频器的输入功率会有相应的频率特性，在不同的频率点上有各自的频率容限，与混频器的频率响应特性有关，不过一般情况下，工程上通过对 1dB 压缩点来粗略估计器件的三阶交调截点。一般来说三阶截点约为 1dB 压缩点 +9.6dB，即三阶截点比 1dB 压缩点高约 10dB 左右。

## 第三章 系统方案设计

上一章我们介绍了频率合成器相关的相噪和杂散理论，并分析了锁相环、混频器（微波倍频器）的相噪和杂散。本章我们先对常用的混合频率合成技术进行介绍，然后结合本系统的具体指标要求进行分析，通过对方案的关键技术指标（频率覆盖宽度、相噪、杂散、输出功率）进行分析，找出设计该宽覆盖频率合成器的难点，提出系统所采用的设计方案。

### 3.1 常用的混合频率合成方式

以下先分析几种常用的混合频率合成结构，以便于对比分析各种类型方案的优劣，通过对各种方案的取舍和修改，可以最终得到比较理想的系统方案。

#### 3.1.1 DDS+PLL 频率合成

由第一章的介绍可知，DDS 是全数字化的结构设计，具有分辨率高、频率转换时间短、相噪低等优点。同时 DDS 在输出频率低和输出杂散大方面的缺点也很突出。锁相环（PLL）是一个窄带的相位跟踪滤波器，输出信号的频率较高，因为锁相环本身可以看成是一个带反馈的倍频器，而且现在主流的 VCO 输出一般都能达到 X 波段，故而能有效地提升系统的输出频率，在 X 波段以上，一般是应用微带——管芯结构来推高频率，这有助于弥补 DDS 本身输出频率不够的缺陷，并且能够有效地抑制信号的杂散分量（因为对鉴相器来说是一个相位的低通系统），可以省掉大量的滤波器，有利于系统集成，对于输出频率多样的系统而言，锁相环的优势很大。但是锁相环是一个很折衷的系统，往往是在频率步进、频谱覆盖宽度、频率分辨率和频率转换时间等多方面的指标间去平衡，同时，在微小频率步进以及频率转换时间等方面不如直接数字频率合成。如前所述，锁相环是一个负反馈控制系统，这样的系统有一个稳态建立的过程，导致锁相环的变频速度较慢，往往达不到捷变频的要求。现在电子系统设计中，比较流行的趋势是结合各种不同器件的特点，形成复合系统，由此产生了 DDS+PLL 方案<sup>[33]</sup>。这种方案结合了直接数字频率合成和锁相环各自的性能优势，弥补了他们各自的不足，在性能上往往能取两者的折衷，既能保证一定的频谱纯度，在一定程度上改善 DDS 输出杂散大的弱点，同时由于 DDS 本身能保证系统的输出频率步进，故能

够推高锁相环自身的鉴相频率，意味着抬高了锁相环的环路带宽，则环路总的分频比就会变小，改善了环路的输出相噪，又能在变频时间上满足要求。这种方法在我国 90 年代中期就提出来了，只是当时的硬件技术条件还不够成熟，在加上系统设计方面仍没有形成有效的解决方案，因此当时的系统指标并不高<sup>[34]</sup>

实现 DDS+PLL 组合系统的方案主要有以下几种：环外混频频率合成、DDS 作参考源激励锁相环频率合成、PLL 内插 DDS 混频合成以及 PLL 内插 DDS 小数分频频率合成。以上几种方案中，环外混频的杂散指标一般因为 DDS 作为中频而使得杂散指标很差，没有充分发挥 PLL 与 DDS 各自的特点，参加混频的两路一路是 PLL 产生的本振信号，一路是 DDS 产生的中频信号，虽然 PLL 作为本振信号可以忽略步进等因素来推高鉴相频率，但是 DDS 支路的信号杂散很大，且很难滤除，参加混频，使杂散难以控制，因而应用环境较窄，这类方案的优势在于能灵活地控制两路信号的频率，使组合的混频信号的三阶交调能够得到很好的控制，在交调抑制方面能够达到较好的效果；PLL 内插 DDS 混频合成与 PLL 内插 DDS 小数分频合成在系统的可调节性上较差，即硬件设计完成后，由于混频两路的输入频率的组合方案会变少，因而需要在方案设计阶段对三阶交调等强的干扰信号准确的估计，不然这类混频环结构有可能会因为干扰信号，输出频率被牵引到干扰信号的频率上，还有这类方案并没有充分发挥 DDS 与 PLL 各自在频谱纯度上的优势，软调整的能力较差，应用也比较特殊。因此，只对常用的 DDS 激励 PLL 方案进行分析。

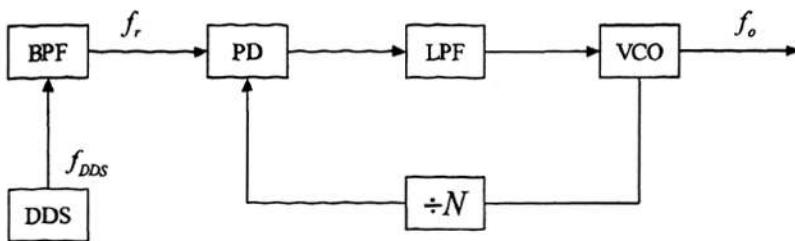

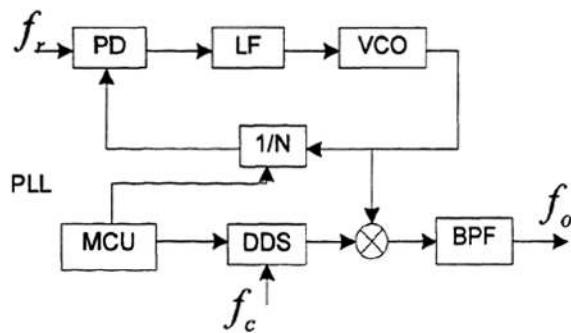

DDS 激励 PLL 方案的结构如图 3-1 所示<sup>[35]</sup>。DDS 的输出信号经过带通滤波器，滤除一部分远端杂散以后，然后作为锁相环的参考源去激励环路中的鉴相器，作为鉴相器的参考信号，被环路的预分频器分频后作为环路的鉴相信号。锁相环在这类方案中起到的是倍频的作用，将 DDS 的输出信号推到更高的频率。由前面的分析可知，DDS 具有高分辨率特点，产生的频率步进非常小，因此通过对 DDS 的程序控制，对输出频率进行细调，以达到微小步进的设计要求。

图3-1 DDS 激励 PLL 方案

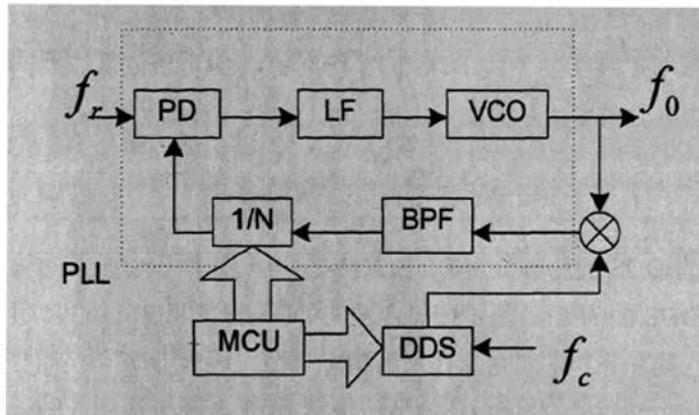

图3-2 内插混频式 DDS/PLL 方案

图3-3 环外混频式 DDS/PLL 方案

这种方案充分利用了 DDS 的高分辨率的特点，从而在理论上保证这类频率合成系统的小步进性能；也利用了锁相环的窄带跟踪滤波特性，能够有效地抑制锁相环通带外的杂散，降低输出的远端杂散水平，在近端杂散方面，可以利用 DDS 与 PLL 各自的软件调节能力，把 DDS 引入的相位截断杂散、PLL 小数分频带来的杂散、还有通常情况下的电源纹波等杂散，移到环路的带外变为环路的远端杂

散，得到很好的抑制。在跳频时间方面，由于 DDS 频率转换时间远小于 PLL 的锁定时间，因而这类方案主要考虑锁相环的锁定时间作为衡量系统变频时间的标准，其中由于 DDS 解决了步进方面的问题，所以锁相环的环路带宽可以加宽，因而这种方案在锁定时间方面会优于只用锁相环的方案。

当环路锁定时，DDS+PLL 系统的输出频率可表示为：

$$f_o = Nf_r = Nf_{DDS} = \frac{NK \cdot f_c}{2^A} = K \cdot \Delta f \quad (3-1)$$

上式中，K 为频率控制字， $f_c$  为 DDS 的系统时钟，A 为相位累加器的位数，因此输出信号的频率分辨率为：

$$\Delta f = \frac{N \cdot f_c}{2^A} = N \cdot \Delta f_{DDS} \quad (3-2)$$

式中  $\Delta f_{DDS}$  为 DDS 的频率分辨率。由式(3-2) 可知该频率合成器的输出频率的分辨率是单一 DDS 的 N 倍。通过选择合适的 DDS 带宽和 PLL 的 R 值、N 值，以实现频率的连续和完整的覆盖。在杂散指标方面，因为 DDS 的杂散指标较差，如果 DDS 输出信号的杂散在锁相环的环路带宽内，则会因为锁相环的倍频作用放大  $20 \log_{10} N$  倍。其偏离主频的位置不会变化，因此杂散指标将会恶化，且得不到很好的抑制。如果 DDS 的输出杂散位于环路带宽之外，则会受到环路滤波器的抑制，从而输出信号的杂散得到改善。在这样的理论基础上，建立起的 DDS+PLL 三重调节理论，在这样的结构中得到了灵活的应用<sup>[36]</sup>。即同时从数字控制电路端调节 DDS 的输出频率、锁相环的前置 R 分频器、还有环路中的 N 分频器，即可使系统的综合指标得到优化。

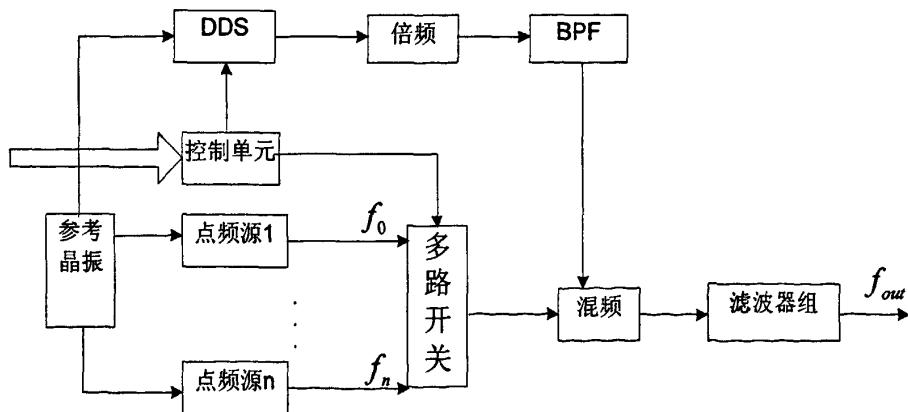

### 3.1.2 直接频率合成+DDS

在前面的讨论中可以发现，直接频率合成技术存在着频率分辨率低、结构复杂等缺点，它的优点是输出频率较高，近端相噪指标好以及最短的跳频时间。另一方面，DDS 的分辨率高。因此，结合 DDS 和直接频率合成技术，可以发挥两者各自的性能优势，用直接频率合成技术来弥补 DDS 输出频率低的缺陷，用 DDS 的高分辨率来弥补直接频率合成技术频率分辨率低（频率步进小）的问题。从跳频时间来说，这类系统的跳频时间主要取决于 DDS（如果其他支路的信号没有很强的慢波结构的话）。DDS 的跳频时间主要由数字系统以及 DAC 的内部电容决定，DDS 的控制部分时间一般为 0.1μs 量级；在系统的其他部分，混频器、分频器、

倍频器由于只是普通的模拟器件，延迟主要来源于电抗器件；滤波器的延时要看滤波器的类型，如果是慢波结构，则延时相对较大。这类方案（考虑最多的是三次变频方案）的跳频时间一般不超过  $1\mu s$ ，以达到雷达所要求的捷变频。在这一节中，我们对两种常用的 DDS+直接频率合成的方案进行分析。如果利用跳频时间很短的倍频器代替了频率转化时间较长的锁相环，就能缩短跳频时间，由此产生了 DDS+倍频的方案，这种方案的缺点在于设计的灵活性太差，如果对 DDS 的杂散估计不足的话，就会有很大的设计硬伤。可使用恰当的带通滤波器对 DDS 的杂散进行滤波，但是 DDS 的杂散一般距离输出信号的频率主峰较近，因此对滤波器的设计指标要求往往很高，特别是对滤波器在近端的矩形系数要求高，从而实现同时具有高输出频率和捷变频功能的频率合成器。

这类系统的方案原理图如图 3-4 所示<sup>[37]</sup>。由图可知，本方案电路主要由晶振、DDS、滤波器组、倍频器、混频器、开关以及控制电路单元等组成。方案中，用 DDS 来实现小步进功能，而频率源 1~n 往往通过对参考源晶振的倍频来实现大频率步进。频率源 1~n 的倍频可以用倍频链实现，也可以用锁相环来实现或者通过混频实现，通常来说都可以达到较好的杂散指标和近端相噪指标；然后将信号选通与 DDS 经倍频后得到的信号进行混频，再通过滤波器组来抑制带外杂散后，得到需要的信号。这类方案的设计理念是以 DDS 产生小步进的中频信号，而点频源阵列产生大步进的高频信号或者是本振信号，再通过混频的方式把 DDS 产生的中频信号调制到高频上去，获得高频的小步进信号。

图3-4 DDS+直接频率合成方案

一般来说，混频器的相噪主要取决于相噪较差的那路信号，通常来说输出频率较高的频率源由于其倍频倍数较大，N 越大，则相噪恶化系数  $20\log_{10} N$  就越大，

故最终输出信号的相噪由频率较高的点频源的相噪指标决定，所以对频率最高的点频源一般是用高稳定恒温晶振作参考源，再通过倍频链得到最接近理论相噪的信号。就杂散而言，该系统的杂散主要来源于三部分：DDS 的杂散、倍频后的谐波、混频器的交调。DDS 的杂散因为经过了倍频电路，所以需要在倍频后考虑对它的抑制，也是就说 DDS+倍频后再滤波，对滤波器的矩形系数要求更高<sup>[38]</sup>；混频器的交调的抑制主要还是要考虑频率规划，因为在高频段，三阶交调离信号过近的话会使滤波器的实现难度增加，以至于很难滤除。

除此之外，近年来 DDS 阵列技术也方兴未艾，但这类技术的理论工作还未完备，实际系统的实现仍有很多问题，对此就不再多阐述<sup>[39]</sup>。

对以上几个系统的跳频时间进行分析，直接频率合成+DDS 技术的跳频时间主要由 DDS 的跳频时间与滤波器的延迟决定，与直接频率合成技术相比稍慢，可以到  $1\mu\text{s}$  左右，相对于 DDS+PLL 的方案，由于引入了锁相环这类负反馈系统，稳态建立的过程就快很多。DDS+直接频率合成技术能同时实现输出较高频率的信号以及小频率步进，但与 DDS+PLL 相比的缺点就是设计的弹性很小，设计出来的系统也还是比较复杂，直接频率合成+DDS 的优势在于较快的跳频时间。对宽覆盖系统而言，DDS+直接频率合成技术这样的结构是很不合适的，因为宽覆盖就意味着复杂的点频源结构，这样的系统支路会很多，实现复杂而且弹性很小。

### 3.2 系统指标要求

本课题来源于西安电子科大的某“雷达模拟系统”项目，其中本教研室和成都亚光电子股份有限公司负责雷达模拟器频率合成器的设计。项目于 2009 年 4 月底完成，历时半年，最终完成了宽覆盖、低相噪、低杂散雷达模拟器干扰源频率合成器的设计以及软硬件实现，各项指标均达到要求。

以下是该宽覆盖频综的具体技术指标要求。

#### 3.2.1 输入信号

恒温晶振 100MHz 输出，相噪-150dBc/Hz@10kHz

#### 3.2.2 输出信号

输出频率范围：3~4GHz, 6~11GHz, 14~16GHz

输出信号步进 20MHz,

相噪均在-80dBc/Hz @10kHz 以下,

杂散在-60dBc 以下,

输出功率在 10dBm 以上

工作温度: -40°C~+85°C。

### 3.3 方案分析

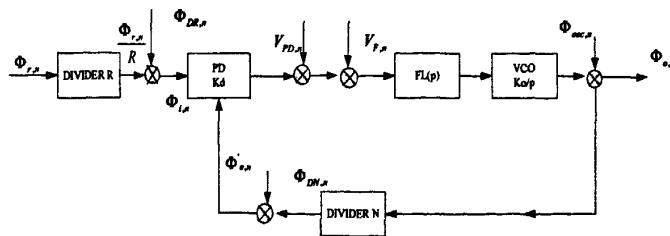

频率合成器方案的设计主要通过合理地选择频谱规划方案，利用现有的放大器、混频器、倍频器、分频器、滤波器、PLL 芯片等器件来达到系统的指标要求。通过对各项指标的分析，可知要在这么宽的频带内达到全频段输出信号步进 20MHz 时，相噪均在-80dBc/Hz @10kHz 以下，杂散在-60dBc 以下，输出功率在 10dBm 以上这样的技术指标，而且有体积尺寸等外围的限制，就决定了本设计不可能使用直接频率合成的设计，因为直接合成意味着设计出来的合成器体积很大 [40][41]；并且如果采用 DDS 的方案，往往意味着小步进，但相噪以及杂散方面的指标往往很差，综上考虑，对于在如此宽的频带内要达到以上指标，应采用 PLL 的方式，然而单一的 PLL 芯片，或者更准确地说，PD 芯片以及 VCO 芯片很难覆盖如此宽的频带。所以综合考虑要用到至少 2~3 个锁相环才能达到设计的要求。在此需要引入锁相环的噪声模型进行分析[42][43]。

图3-5 锁相环等效噪声模型

为便于分析锁相环环路的噪声性能，建立如下模型，如图 3-5 所示： $\Phi_{r,n}$  为输入参考源的噪声， $\Phi_{DR,n}$  为预分频器引入的噪声， $V_{PD,n}$ 、 $V_{F,n}$ 、 $\Phi_{osc,n}$  分别为鉴相器、环路滤波器、VCO 引入的噪声， $\Phi_{DN,n}$  为环路 N 分频器引入的噪声。根据随机过程理论，输出的相位噪声可最终表示为<sup>[44][45]</sup>：

$$\Phi_{O,n} = [\Phi_{r,n} \frac{N}{R} + (\Phi_{DR,n} + \Phi_{DN,n} + \frac{V_{PD,n} + V_{F,n}}{K_d})N] \bullet H'(s) + \Phi_{osc,n}[1 - H'(s)] \quad (3-3)$$

$$H'(s) = \frac{\frac{F_L(s)F_M(s)K_dK_o}{Ns}}{1 + \frac{F_L(s)F_M(s)K_dK_o}{Ns}} \quad (3-4)$$

由以上的分析可知，压控振荡器 VCO 主要决定环路远端相噪（带外），锁相环的其他部分决定环路近端相噪（带内），而最后输出的相位噪声为两者的综合表现。因为在 PLL 中鉴相器的反馈回路分频器（N 分频器）的工作频率最高，故而对系统最终相噪的影响也最大，所以从理论上去估算实际系统的相噪指标时，往往首先考虑的是环路中分频器的噪底。此外，环路带宽的公式为：

$$K = \frac{K_\phi K_f K_{VCO}}{N} = K_\phi K_f K'_{VCO} = K'_\phi K_f K_{VCO} \quad (3-5)$$

其中  $K'_{VCO} = K_{VCO}/N$ ，即为等效 VCO 压控增益； $K'_\phi = K_\phi/N$ ，为等效鉴相增益。设计宽覆盖频率源系统，从  $K'_\phi$  的角度比从  $K'_{VCO}$  的角度考虑要方便很多，因为我们实际的系统往往  $K_{VCO}$  随频率的变化规律比较固定，而且可以实际测得，因而可以看成是一个已知的高次函数曲线，而在设计时，往往环路的  $K_\phi$  和 N 都是可变的（对现在的大多数锁相环芯片而已，这两者都是可以软件设置的，不需要改变硬件系统），因而只要使  $K'_\phi$  变化能补偿  $K_{VCO}$  的非线性，即可获得恒定的环路带宽以及稳定的性能。如前所述，环路带宽决定了环路的很多特性，比如锁定时间、环路的稳定性等等。对于宽覆盖的频率合成器来说，由于频率覆盖范围内的 N 值变化很大等原因，带来  $K'_{VCO}$  的非线性，使环路带宽 K 变化剧烈<sup>[46]</sup>，故要保证环路带宽的恒定，就应有同样变化范围的  $K_\phi$  去补偿 N 的变化，这是基于宽覆盖频率源设计的理论基础。

## 3.4 方案设计

### 3.4.1 设计原则

由上面的规划与噪声模型可知，该方案的难点在于输出频率的高端，即 16GHz 的信号时，鉴相频率很低，造成输出的相噪指标会比较紧张，根据前面的

相噪理论，这样的相噪恶化是不可避免的，故而需要选用噪底较好的鉴相器。对比各类锁相环芯片，特别是当前主流的锁相环芯片，可以得知，Hittite 公司推出的 HMC700 与 ADI 公司的 ADF41xx 系列芯片相比，噪底更好。在 HMC700 里，不但集成了 R、N 分频器，且变化范围很大，同时，该鉴相器芯片的电荷泵电流可以程序控制，从 0.5mA 到 2mA，电荷泵噪声也达-145dBc/Hz@20kHz，而且预分频器工作频率高达 8GHz，噪底低至-155dBc/Hz。该芯片鉴相频率可高达 105MHz，并且支持小数分频<sup>[47]</sup>。在系统输出 16GHz 时，本系统选用了鉴相频率为 5MHz 整数分频的方案，舍弃了更高鉴相频率下小数分频的方案（比如 100MHz 鉴相频率的小数分频方案），主要原因在于 HMC700 在小数分频条件下，虽然随着鉴相频率的提高会带来相噪方面的好处，比如两种方案相比理论上会有 26dB 相噪方面的改善，但要在全频段内控制杂散在-60dBc 以下很难（特别是小数分频器带来的带内杂散很难抑制）。5MHz 鉴相，16GHz 输出时输出相噪（在 10kHz 的地方）理论计算为

$$\begin{aligned} \text{PhaseNoise(inband)} &= \text{PhaseNoiseFloor} + 20 \log |N| \\ &= -(155 - 20 \lg 3200) = -(155 - 70) = -85(\text{dBc/Hz}) \end{aligned} \quad (3-6)$$

另外，由公式（3-6）及前面的分析知，由宽覆盖引起的环路带宽不恒定问题是很严重的，比如在相同的鉴相频率下，每覆盖  $m$  个倍频程，即  $N$  也会有  $m$  倍的变化范围，相应的要求  $K_p$  要有更大的变化范围。然而  $K_p$  的变化范围是很受硬件限制的。因此必须要有一种相应的设计理念去解决这样的问题，一种比较好的解决方案就是用可变的鉴相频率去鉴相。因为对一个实际的硬件平台而言， $K_{vco}$ ， $K_f$  都已经固定，而  $K_p$  和  $N$  却往往是可以调整的，特别是系统有设计裕量的情况下， $N$  往往可以做很大的调整，比如在较低的频率点上，可以改低鉴相频率使  $N$  变大，从而使  $N$  的变化范围小于  $K_p$  的变化范围。再有就是选择  $K_p$  变化范围很大的芯片。本系统  $K_p$  变化范围比较大（HMC700 最低鉴相电流为 500μA，最高为 2mA），因此两者可结合起来考虑。可以使鉴相增益能补偿  $K'_{vco}$  的非线性带来的影响，从而在宽覆盖条件下，使环路带宽  $K$  保持基本恒定，使全部频点都达到所预期的指标要求<sup>[24]</sup>。

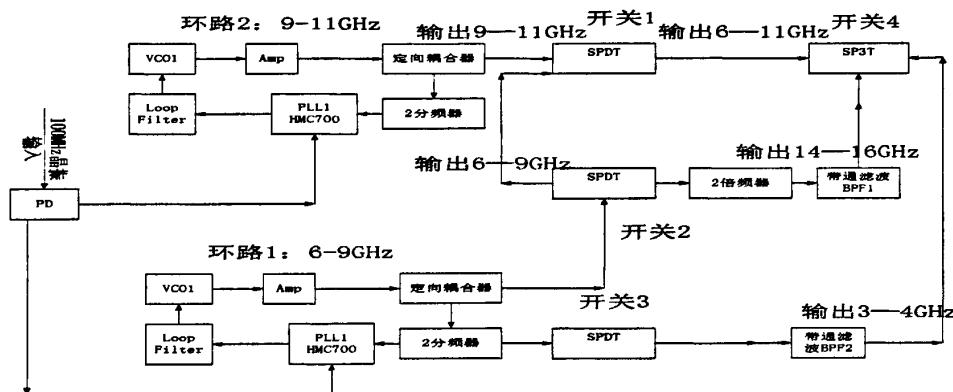

### 3.4.2 系统方案

由上文可知，该项目采用多环切换外加倍频的方案是较为合理的选择。由于在跳频时间上要求较低，所以选择 PLL，可以通过环路的硬软调节来实现在宽频

带上的指标，这对于直接频率合成来说，是很难的，而如果在系统中引入 DDS 的话，在如此宽的频段内是很难兼顾相噪与杂散的指标的。即便已经选择了多环切换外加倍频的方案仍然还有很多地方需要考虑：（1）合理的制定频率方案使所用的环路最少，一方面可以减少系统的复杂度，另一方面合理的规划也可以使系统达到更好的指标，充分发挥现有芯片的性能，完成设计的要求；（2）在实际设计时，对于相噪的考虑应是首要的目标，因为相噪指标往往是由方案阶段就限制了的，很多时候无法通过后期的调试来改善，因为相噪的恶化很大程度上取决于倍频的次数；（3）杂散的考虑，这也是一个很难周全的因素，因为杂散指标是在全频段的，在如此宽的频带内，要所有频点都能满足这样的指标其实是很难的，因为体积的限制使单个环路覆盖的范围很大，因而在设计时往往顾此失彼<sup>[48]</sup>；（4）对于射频电路而言最重要的是各部分的隔离，对于 S 波段以上的信号而言，串扰是很严重的，因而隔离也是很重要的；（5）系统稳定性问题也是一个频综需要关注的问题。最终的系统方案如图所示。

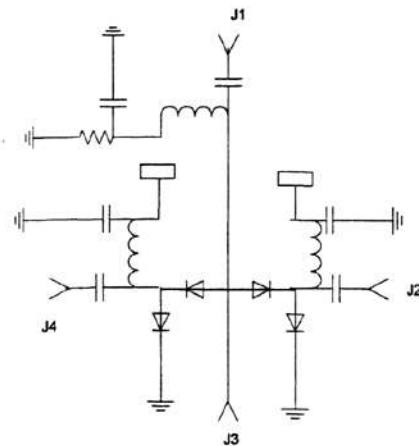

图3-6 本系统的基本结构图

可见，该方案主要由两个输出频率范围分别为 6~9GHz 的环路 1 和 9~11GHz 的环路 2 组成。具体的频率范围切换关系如下：

- 1、输出 3~4GHz、步进 20MHz 信号时，选择环路 1 工作，以 20MHz 鉴相，选通开关 3，关闭开关 1、2，开关 4 向右接通；

- 2、输出 6~9GHz、步进 20MHz 的信号时，选择环路 1 工作，以 10MHz 鉴相，开关 2 向左接通，开关 1 向下接通，关闭开关 3，开关 4 向左接通；

- 3、输出 9~11GHz、步进 20MHz 的信号时，选择环路 2 工作，以 10MHz 鉴

相，同时开关 1 向上接通，关闭开关 2、3，开关 4 向左接通；

4、输出 14~16GHz、步进 20MHz 的信号时，选择环路 1 工作，以 5MHz 鉴相，开关 2 向右接通，关闭开关 1、3，开关 4 向下接通。

### 3.4.3 系统相位噪声和杂散分析

#### 1. 频综系统的相噪指标分析

本设计用到的是恒温控制式高稳定度晶振（OCXO），频率为 100MHz，相噪指标为：-146dBc/Hz@1KHz；-150 dBc/Hz@10KHz。根据相位噪声理论，5MHz 鉴相，16GHz 输出时输出相噪（在 10kHz 的地方）理论计算为

$$\begin{aligned} \text{PhaseNoise}(inband) &= \text{PhaseNoiseFloor} + 20\log|N| \\ &= -(155 - 20\lg 3200) = -(155 - 70) = -85(\text{dBc/Hz}) \end{aligned} \quad (3-7)$$

信号经倍频器后，在 16GHz 输出的时候相位噪声要恶化 70dB，即最后输出的理论值为-85dBc 略好于系统的设计要求，但这样的实现是一种理论的计算，还要考虑的是实际器件可能附加的噪声，这样的叠加有可能在实际的系统测试时使指标达不到要求。

而实际设计时由于芯片的局限必然使相噪的恶化会超出预期。所以选择合适的锁相环芯片是很必要的。在本系统中我们选择的是最新的 HMC 700 锁相芯片。各方面数据显示，Hittite 公司推出的 HMC700 与 ADI 公司的 ADF41xx 系列相比，噪底更好。HMC700 不但集成了 R、N 分频器，电荷泵电流可以程序控制，而且预分频器工作频率高达 8GHz，噪底低至-155dBc/Hz。该芯片鉴相频率可高达 105MHz，并且支持分数分频。该芯片的具体数据与 ADF41xx 系列的对比如下表 [49]。

表3-1 HMC700 与 ADF4106 各项指标对比

|          | HMC700        | ADF4106                  |

|----------|---------------|--------------------------|

| RF 端输入频率 | 0.1~9GHz      | 0.5~6GHz                 |

| 参考端输入频率  | 100KHz~225MHz | 20MHz~250MHz             |

| N 分频范围   | 36~65535      | 8/9, 16/17, 32/33, 64/65 |

| 双模分频器, 按 $N=BP+A$ 计算 |              |                                      |

|----------------------|--------------|--------------------------------------|

| R 分频                 | 14 位 R 分频器   | 14 位 R 分频器                           |

| 鉴相器噪底                | 优于-155dBc/Hz | 随鉴相频率的变化而变化, 按实际的测试结果来看应低于-155dBc/Hz |

由上表可知, 由于 ADF4106 的分频比还有噪底方面的劣势, 是不满足我们实际的需要的。要在全频段把杂散都做好, 往往就需要牺牲部分的相噪指标, 因而对于 ADF4106 这类鉴相芯片而言, 设计的弹性很小, 往往使最终实际系统的测试达不到预想的要求。故在设计时, 在相噪上留有足够的裕量是很必要的。这样的设计也使我们最终的系统调试有很大的弹性。

## 2. 频综系统的杂散指标分析

该系统方案的杂散主要来自于以下几个方面, 一、鉴相纹波, 因为采用的是锁相环电路, 所以对鉴相纹波的抑制是很必要的, 由于输出频带很宽使得环路特性在频率的高端与低端的差别很大, 所以单一环路能覆盖的频率范围有限, 使得环路滤波器对鉴相纹波的抑制在高端与低端时不能同时兼顾。二、DC~DC 电源的纹波, 由于外部电源只提供了 15V 的电压, 而在系统中需要的电源的种类很多, 不仅有 15V 以下的正电, 还有-6V 这样的负电, 因而在系统中引入了负电变换的芯片, 比如 MAX660, 这样必然会引入 MAX660 的工作频率信号, 耦合在负电回路, 甚至串扰在正电回路中, 对于锁相环而言, 输出的高频信号必然耦合上了这样的近端杂散, 而且很难抑制。三、由于系统没有引入任何的混频器, 只有倍频链, 对于需求方而言, 在频带内的高次谐波这样的信号, 也是需要考虑的, 虽然一般不会考虑成杂散, 但是对于雷达模拟器而言, 这样的干扰也是必须抑制掉的, 这直接影响了模拟器的性能<sup>[50]</sup>。

当然除去以上的杂散以外, 还有路与路之间的隔离, 往往是采用开关子系统电源这样的方式, 这类杂散是比较容易滤除掉的。综上所述的杂散信号, 最影响工作性能指标的还是第一类这样的杂散, 这是一个宽覆盖的频率合成器要达到相噪与杂散指标的障碍。所以在下文, 会继续阐述这类杂散的抑制问题。

当然, 分数分频引入的杂散的规律性相对较小, 一般而言, 会应用多重调节的理论, 使这类杂散移出锁相环的通带, 可得到很好的抑制, 由于实际调试的原因, 使分数分频的方案最终被本项目舍弃, 所以此就不再多阐述。在后面还会提到, 在调试过程中舍弃分数分频的过程。

## 第四章 系统的硬件和软件实现

### 4.1 系统具体设计方案

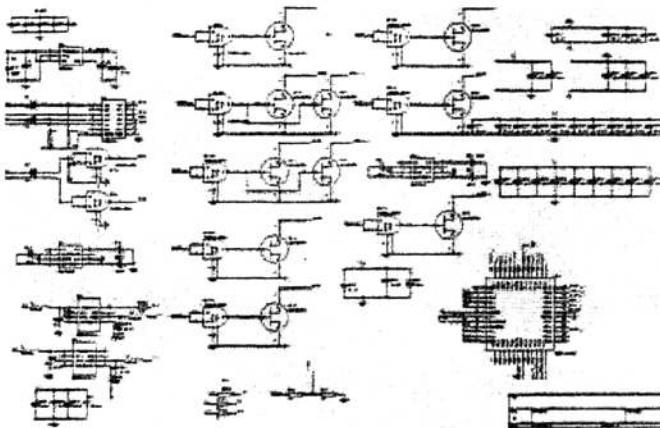

上一章我们确定了该宽覆盖频率合成器的方案，本章主要介绍该方案的具体软硬件实现，并介绍系统关键模块的设计以及调试过程，如图 4-1 所示。

图4-1 系统方案设计图

### 4.2 锁相环本振的实现

#### 4.2.1 锁相芯片的选择

因为锁相环可以看作倍频器，输出相噪从理论上说为输入参考信号相噪的  $N^2$  倍，即相噪恶化  $20\log N$  dB，N 为环路总的分频数，因而可以以锁相环鉴相器的基底噪声与输入信号噪声比对取差者，再减去由于倍频作用的恶化量即可从理论上大概估计 PLL 输出的近端相位噪声。当然这是理论上的估计，实际上这种估计是很难达到的，即实际的系统很难做到这样的理想状态，往往都会比理论估计值坏

3~10dB，除此之外，往往对于锁相环相噪恶化的公式还有几种，在这里做简单的介绍，比如ADI公司的锁相芯片常采用的就是，

$$\text{PhaseNoise}(\text{in\_band}) = PN1\text{Hz} + 20 \log N + 10 \log F_{\text{comp}} \quad (4-1)$$

这个公式通常要考虑鉴相器的鉴相频率，当然针对不同的鉴相器类型，估计值往往会有很大的出入；另外还有一种常用的估计相噪的公式引入了电荷泵膝点的考虑，

$$PN1\text{Hz}(K_\phi) = PN1\text{Hz} + 20 \log |1 + K_{\text{phi}}K_{\text{knee}} / K_\phi| \quad (4-2)$$

无论用以上哪种公式去估计 PLL 的相噪，其最终的结果其实都不会好于通常的把锁相环当成倍频器来估计相噪的结果。因而在这个系统中，我们以第一个公式作为最终的理论值，再在估计中引入修正因子，往往估计值与实际的系统最终指标相差不远。

HMC700 的芯片内部结构如图 4-2 所示

图4-2 HMC700 的内部结构图

由上图可知其结构跟以前的锁相芯片有一定的差别，主要在于 N 分频器部分，比以前的鉴相芯片更灵活。

由于第三章的分析，本系统选用 HMC700 来作为鉴相芯片，其主要的指标可参看第三章与 ADF4106 对比的数据，当然在此值得注意的是：PLL 的杂散性能如前面所述主要受鉴相纹波与电源纹波的影响，这是两类很不同的杂散，通常来说，鉴相纹波属于带外杂散，因为通常情况下，为了有效的抑制鉴相纹波，都会把锁相环的带宽设置为低于鉴相频率 3%，因为这样才可以使通常的 2 阶环路在带外-6dB/倍频程的特性下，得到很好的抑制，这也是本系统的一个难点之一，因为对于宽覆盖的锁相系统而言，由于覆盖了几个倍频程，使得环路特性在频率的高端与低端的差异性很大，如所示

$$K = K_\phi K_f K_{vco} / N = K_\phi K_f K'_{vco} = K'_\phi K_f K_{vco} \quad (4-3)$$

其中  $K'_{vco} = K_{vco} / N$ ，即为等效 VCO 压控增益； $K'_\phi = K_\phi / N$ ，为等效鉴相增益。在宽覆盖设计时，从  $K'_\phi$  的角度，比从  $K'_{vco}$  的角度考虑要方便很多，因为我们实际的系统往往  $K_{vco}$  随频率的变化规律比较固定，而且可以实际测得，所以在宽幅盖的设计时，往往  $K_\phi$  和 N 都是可变的，只要使  $K'_\phi$  变化能补偿  $K_{vco}$  的非线性，即可获得恒定的环路带宽以及稳定的性能。环路带宽决定环路的很多特性，比如锁定时间、环路的稳定性等等。对于宽覆盖的频率合成器来说，由于频率覆盖范围内的 N 值变化很大等原因，带来  $K'_{vco}$  的非线性，使环路带宽 K 变化剧烈。

所以鉴相频率相对环路带宽来说越高，则鉴相纹波越容易抑制，但是高的鉴相频率影响 PLL 输出的最小步进和环路带宽，通常情况下，环路带宽小于鉴相频率的十分之一。

在整数分频 PLL 中，鉴相频率等同于环路输出的最小步进。故鉴相频率需要在环路输出最小步进、鉴相纹波的滤除以及环路带宽等多方面考虑下确定。而对于分数分频来说就比较灵活了。在分数分频中，鉴相纹波由于可以取更大的值，因而可以做得很好，主要的问题集中在分数分频引入的杂散上，这样的杂散往往在带内，很难抑制，因而在考虑分数分频时要尽量地使分数分频引入的杂散落在带外，从而使这类杂散得到很好的抑制。

16G

Date: 6.MAR.2009 20:30:42

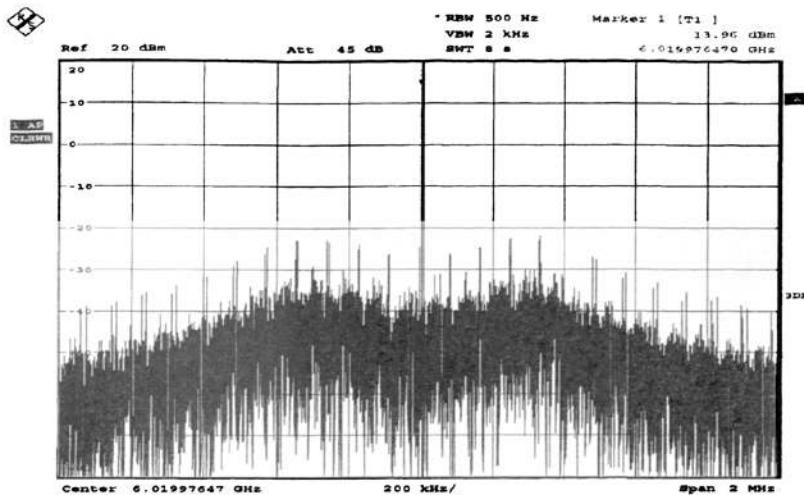

图4-3 HMC700 小数分频引入的杂散图

如上图所示，为了在频率的高端，比如 15.98GHz 这样的频率，以 100MHz 鉴相，得到低于-80dBc/Hz @10kHz 的指标，根据公式，

$$f_{VCO} = f_{xtal}N_{int}/R + f_{xtal}N_{frac}/(R \cdot 2^{24}) = f_{int} + f_{frac} \quad (4-4)$$

可知，这时是有分数部分，由于 HMC700 自身的一些硬件局限，使得分数分频的杂散很难抑制，如果此时去调整环路滤波的参数，又会剧烈恶化其他频点的指标。

#### 4.2.2 锁相环的设计

从硬件设计的原则来说，第一版设计往往都会尽量增加设计的裕量，使得在后期的调试时有更多的调整空间，根据设计的要求，我们把环路滤波器设计成一阶，即环路为二阶环，使得带外的相噪与杂散都能得到抑制。

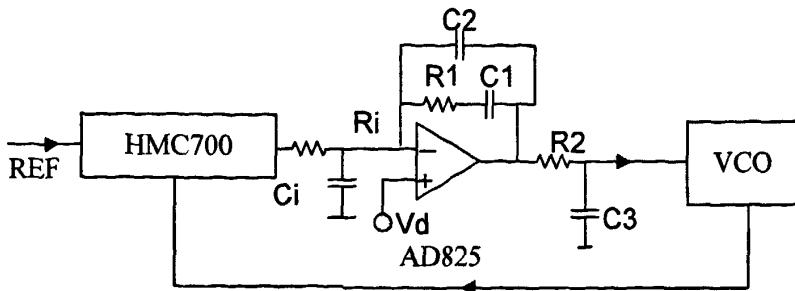

图4-4 HMC700为核心的锁相环电路

从 PLL 芯片的最大输入参考频率、参考频率分频后的鉴相频率、最大输入射频频率、分频比的灵活性、鉴相电流的可调性、噪声底限等方面考虑，Hittie 公司的 PLL 芯片 HMC700 是较为理想的选择。输入参考时钟为 100MHz；环路滤波为有源滤波，采用运算放大器 AD825，以有效地驱动后级的 VCO。为了有效抑制鉴相纹波，AD825 前后增加一阶 RC 低通滤波器，这样最终的环路如图 4-4。

利用 PLL 设计工具 ADIsimPLL 进行仿真(取  $K_{vco} = 300MHz/V$ ，环路带宽  $K=100KHz$ ，鉴相电流  $I_p = 0.5mA$ ，环路分频比  $N=700$ ，阻尼系数  $\xi = 1.1$ )，可初步算得 C1、R1，然后可通过经验公式推算出后级的 C2、R2、C3，并且可通过适当对 Ci、Ri 的调节，进一步抑制带外杂散。

最终 6~9GHz 的环路参数为：

$$R1=3k\Omega, C1=2.7nF, R2=500\Omega, C2=500pF, C3=100pF, Ri=0\Omega, Ci=\infty$$

9~11GHz 的环路参数为：

$$R1=1.5k\Omega, C1=6nF, R2=300\Omega, C2=1nF, C3=100pF, Ri=0\Omega, Ci=\infty$$

### 4.2.3 锁相环的调试

为了保证环路正常锁定，就要求 HMC700 的工作状态和参数配置必须正确，如：

- ✓ HMC700 输入参考时钟为 100MHz，其对于 HMC700 的输入端功率不能太小(如果是 AC 耦合， $V_{pp}$  必须大于 700mV)，否则芯片将不能在正常工作；由于 HMC700 不像其他芯片提供参考电压引脚，芯片的工作状态只能通过其他方法得知，比如通过对寄存器 Reg 0Dh GPO\_SPI\_RDIV

Register 的设置，检测管脚 D0、D1 来获得相关信息。在这里，需要注意的是，输入控制信号的时序关系必须严格满足 HMC700 控制的电路的要求，如下图所示

图4-5 HMC700 串口时序——写串口操作

图4-6 HMC700 串口时序——读串口操作

4 个送数周期的配合，必须严格满足实际的要求，并且从数字逻辑电路的角度来说，对 HMC700 的寄存器置数；还需要和置数的单片机同步，由于本系统对功耗以及系统内抑制干扰的要求，对两个环路的供电是交替供电的，因而对 HMC700 的外围电路，要求不应有大电容的存在，因为会使 HMC700 上电变慢，可能导致对 HMC700 的前几个置数周期失效，影响置数。但是由于 HMC700 的外围供电电路大电容的去除，使得 HMC700 输入端的电源纹波等通过电源线耦合的杂散很难滤除。

图4-7 6~9GHz 环路原理图

✓ 关于电荷泵极性的选择，有以下几条：

- A、 电荷泵的极性为正：环路滤波器为无源滤波器，VCO 的控制灵敏度为正（即，随着控制电压的升高，输出频率增大）。

- B、 电荷泵的极性为负：1、环路滤波器为有源滤波器，并且放大环节为反相放大；VCO 的控制灵敏度为正。2、环路滤波器为无源滤波器，VCO 的控制灵敏度为负。3、PLL 分频应用，滤波器为无源型。即参考信号直接 RF 反馈分频输入端，VCO 反馈到参考输入的情况。

由于运算放大器 AD825 为反向输入导致运放前后电压极性相反，为保证锁定过程中正确的频率牵引方向，必须对 HMC700 电荷泵的极性参数配置为负。

✓ HMC700 的分频器由于不是传统的 N/N+1 模式，这种非吞脉冲程序分频器就不会受到  $N_{MIN}=P^2-P$  的限制，当然这样的分频器还是有它的分频下限的  $N_{MIN}=32$ （整数模式时）； $N_{MIN}=36$ （分数模式时）。

环路的调试过程可分为两种，一种为硬调试，使环路各芯片的工作正常，然后在频率高端，调整环路滤波器的参数使环路在预定状态下锁定；另一种为软调试，在环路初步锁定的条件下，调整环路芯片的寄存器参数，同步调节环路参数，比如电荷泵鉴相电流，N 和 R 的分频比等，使得环路参数发生改变，进而可以使环路达到所预想的状态。

在调试过程中这两种方式，其实是交替进行的，因为在 C 波段以上，电路的分布参数是不可忽视的，同时电容电感等分立元件也有相应的频率特性，这在电路设计时是不可忽略的，再加上分立元件有自身的浮动值，即电特性的个体差异性，使纯粹按数值设计的电路不一定会满足实际的需求，因此软调整在一定程度上能弥补这一差异性，使得硬件的缺陷得到修正。

另外，频率合成器是一个综合的系统，它所反映的性能也应该是一个综合的指标，单个指标是要服从于整体性能的。比如，在本系统中，如果只是考虑 -80dBc/Hz@10kHz 的指标，则可能会损失整体性能。

图4-8 牺牲相噪平滑度，在10KHz处达到较好的相噪指标

如图 4-8 所示，虽然在 10kHz 的地方，获得了不错的指标，但是是以牺牲  $\xi$  为代价的，在拐点处有隆起，使整体性能下降。

图4-9 综合各方面的因素，得到较好的综合指标

如图 4-9 所示，可稍微牺牲一下在 10KHz 处的相噪性能，即可使输出的相噪曲线变得比较平滑，使相噪方面的性能更合理。

### 4.3 输出功率控制

由于在系统中没有专门的功率控制模块，因此，在功率方面的指标是要求输出 10dBm 以上，对于宽覆盖系统来说，实现比较平坦的输出功率有很大的难度，原因在于，对于这样的系统而言，对不同的频率，其分布参数是有很大差别的，虽然在系统中充分考虑了这一点，把输出分开成几路，使各路相对频率范围变小，使得功率的平坦度，难度降低。具体的分系统电路如图 4-10、4-11 所示

图4-10 6-9GHz 环路

图4-11 9-11GHz 环路

对于系统而言，两个环路的功率分开控制，特别是高频段。比如 Ku 波段，长的输出线路必然会使电路的损耗增加，由于从功率控制端到最后的接口端，是很长的微带电路，对于 Ku 波段这样的信号来讲，超过  $n\lambda$  ( $n \geq 5$ )，再加上由于输出支路不一定是直线，可能由于腔体结构以及空间的限制，使输出支路出现拐角，从微带电路的角度来说，这样的结构对一个宽覆盖系统来说是很难做到匹配的。

在设计输出电路之前，对 10GHz 以上的系统，用 ADS 以及 HFSS 做了微带

电路的仿真，具体的统计数据如表 4-2。

表4-1 微带电路 10GHz 直线结构输出损耗（铜导线， $w = 0.78mm$ ，板材 roger4350）

| 输出线路长度                | 损耗 (loss) dB |

|-----------------------|--------------|

| $\frac{1}{4}\lambda$  | 0.05         |

| $\frac{3}{4}\lambda$  | 0.06         |

| $\frac{5}{4}\lambda$  | 0.08         |

| $\frac{7}{4}\lambda$  | 0.111        |

| $\frac{15}{4}\lambda$ | 0.25         |

因为本系统实际的覆盖有 3 个左右的倍频程，即便在实际设计时，出于对输出功率以及系统结构的考虑，把输出分路，但是其一路的覆盖也是比较宽的，对于微波电路来说，这样在输出的平坦度上是一个很大的问题，比如，本系统 6~9GHz 的环路也是覆盖了半个倍频程，从微带电路的角度上讲，这样的电路是很难做到全频匹配的，再加上实际系统中，电路的相互影响，以及腔体结构对周围电磁场的改变，使得实际的密封腔体的电磁场结构使本来的微带电路的电磁场改变为类似缝隙结构的电磁场，这样的系统使实际调试的最大困难在于：腔体密封与不密封的电磁特性差别很大。

由于 9~11GHz 的输出支路会经过一个很长很窄的腔体，这样的结构经过 HFSS 的仿真可以知道，在这个频段上是有很大的损耗的，再加上高频开关的耦合等问题，这样就会造成输出的功率不够，为了增加输出的功率，在 9~11GHz 的输出支路增加了增益放大器 NBB-300，去驱动输出的信号，但这个频段上的放大器 NBB-300 的稳定区域比较窄，很容易就发生自激等现象。这个频段上的放大器的偏置电路一般来说都是用的绕线铜丝作为高频扼流圈，其感抗值很难做得很准确，再加上铜线自身的自感和电容特性等因素，使 NBB-300 的自激现象很严重，应引起足够的重视。

对于功率调节而言，一般是通过粘性重金属与介质块等来改变电路的分布特性，最后使信号达到匹配。从而获得较好的输出功率。虽然并没有增加输出信号的强度，但使输出端达到匹配，信号的输出功率达到最大，同时，也避免阻抗不匹配造成的强驻波烧毁相关芯片。

系统的设计往往在输出端的时候匹配最难，比如

图4-12 输出端口多路选择器

如图 4-12 所示，在本系统中最后的输出端口前是管芯 MA4AGSW3，由于腔体空间的限制，使几路输出信号在到达开关之前，并不是直路，而是有弯曲的，特别是左支路与上支路，靠得很近，相互耦合很强，使这两路的输出相互制约。右支路与输出通道也有同样的问题，特别是 MA4AGSW3 的外围是低频电路，有很多外围器件，比如外围的线绕电感等等，这样的电路与主信号通道的微带电路构成复合电路，对高频的输出影响很大。MA4AGSW3 的外围电路如图 4-13 所示 [51]。

图4-13 MA4AGSW3 外围电路图

由图 4-13 可知，这样混合电路比纯微带电路的电特性更为复杂，因而在输出

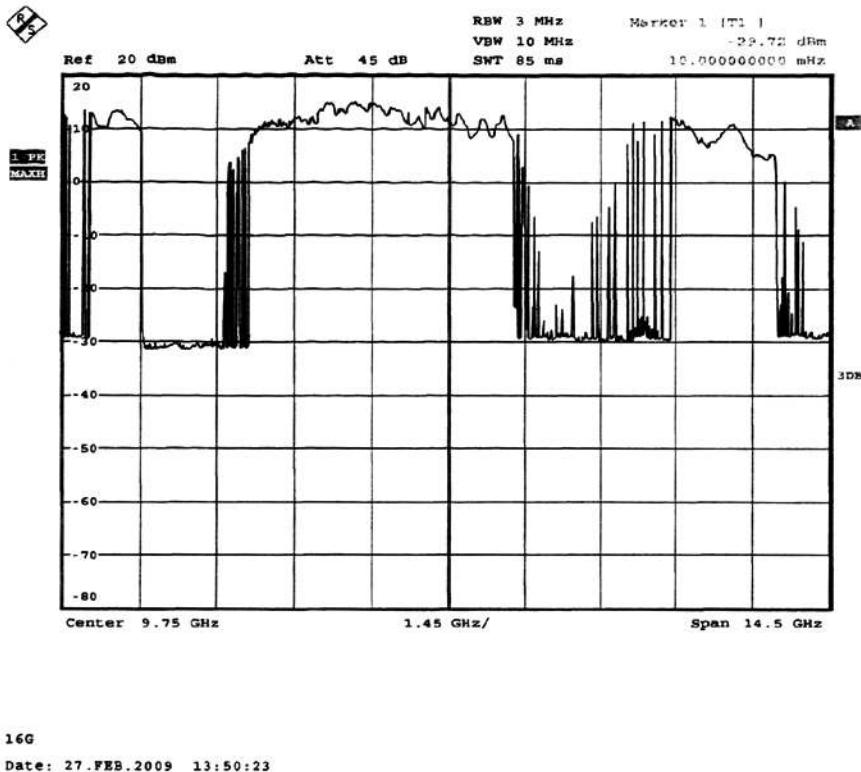

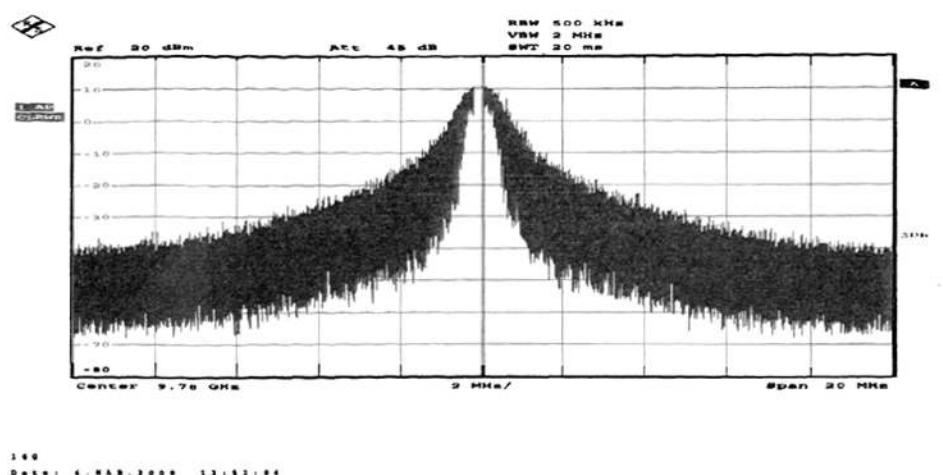

开关电路这一段，阻抗的匹配和驻波很难控制，比理论上的输出信号强度要弱 6dB 左右。在调试功率过程中，可以通过频谱仪对输出功率进行粗略的分析，如图 4-14 所示。

图4-14 系统的输出功率简图

图 4-14 所示，在频谱仪上，可以看出在 14~16GHz 的频段上，功率好像没有达到输出功率的要求，低于了 10dB 以下，主要是因为频谱仪不是功率探测仪器，对功率的探测不准确，再加上连接系统与仪器之间的线缆不是 Ku 波段上的线缆，损耗很大，通过矢网对该电缆的测量可知，其损耗达到了 -4dB 左右，并且在频谱仪所示功率不足的频段，用 Agilent 的功率计进行测试，结果为 10dBm 以上，达到了实际的输出要求。

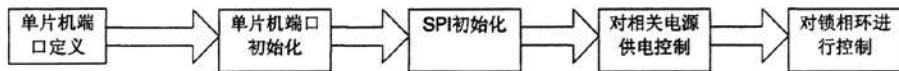

#### 4.4 控制系统的实现

在本系统中，控制电路采用的是单片机控制，芯片为 C8051F360，该单片机在系统中的主要作用是

- 1、对 HMC700 的寄存器置数，使锁相环工作在不同的频段上。

- 2、对系统各部分的电源进行控制，降低各部分之间的干扰。

- 3、对输出开关进行控制，达到多路选通的目的。

单片机 C8051F360 的电路结构如图所示

图4-15 C8051F360 电路原理图

单片机程序的流程图如图 4-16 所示。

图4-16 单片机程序流程图

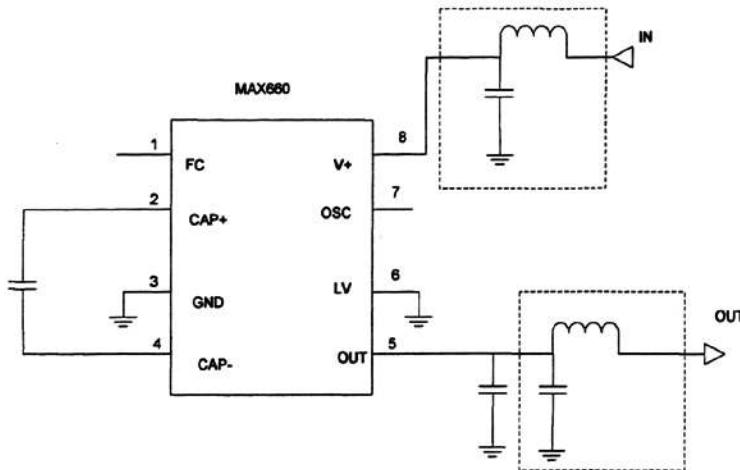

在频率源系统中，设计控制芯片的外围电路需要注意与受控部分的电路相配合，比如，使单片机控制的上腔体环路芯片的供电路径最短。有很多在设计时需要注意的小细节，这里就不多赘述。需要特别说明的是，由于外部只提供+15V的电源，而系统中有很多需要负电的器件，使得在单片机控制板上，需要引入DC-DC电源，这类电源的工作是开关模式进行的，所以必然引入电源纹波，在本系统中，一个比较典型的应用就是 MAX660 的对正负电源的转换，由于 MAX660 的存在，其工作频率经过实际的测试，为 40KHz 左右，由于电源是强信号，MAX660 的工作电流达 100mA 左右，其电压为 5V，相对 10dBm 的射频输出而言，这样的干扰是很强的。同时，40KHz 这样的信号的频率很低，根据模拟滤波器一般的设计原则，要达到 -60dB 的抑制，则意味在滤波器中要引入大电容大电感，因而对于电源纹波的滤除是很难的，MAX660 引入的电源纹波如图 4-17 所示。

16G

Date: 6.MAR.2009 20:36:09

图4-17 MAX660 引入的电源纹波，频率为 41KHz

对于 MAX660 的纹波的滤波，除了考虑在输出端滤除以外，还应考虑在输入端进行滤波，因为 MAX660 工作在 40KHz 这样很低的频率上，很容易耦合串扰成为干扰信号，因而在 datasheet 推荐的电路以外，对 MAX660 的外围电路进行了修改，在前后的输入输出都加入了一级的 LC 滤波，如图 4-18 所示。

图4-18 MAX660 的外围电路图（虚线部分为抑制 40KHz 的电源纹波添加的一级 LC 滤波器）

经过反复的调试，为了防止电源纹波的泄漏，还在底部电源板的其他关键控制点上添加了许多谐振频率在 40KHz 左右的一阶 LC 滤波器，才使得最终的输出把电源纹波抑制在了 -60dBc 以下。这类近端杂散如图所示。

图4-19 系统的近端杂散效果图

如图 4-19 所示，电源纹波可以通过在关键处滤波得到很好的抑制，达到了 -60dBc 以下，满足了设计的要求。

## 第五章 结果分析与项目总结

在上一章中，对3~16GHz宽覆盖频率源各部分的设计以及在调试中遇到的问题进行了详细的说明和分析，并且也找出了相应的解决方案。本章对系统的测试结果进行展示，并加以分析说明。

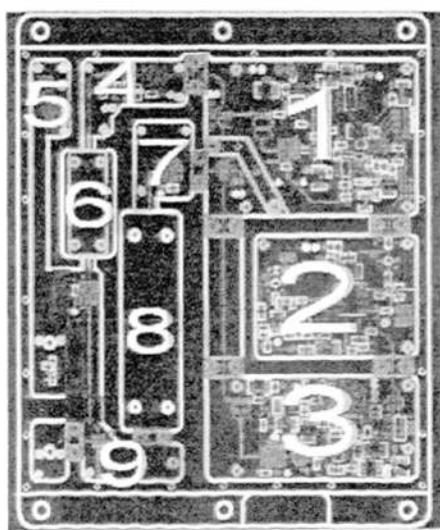

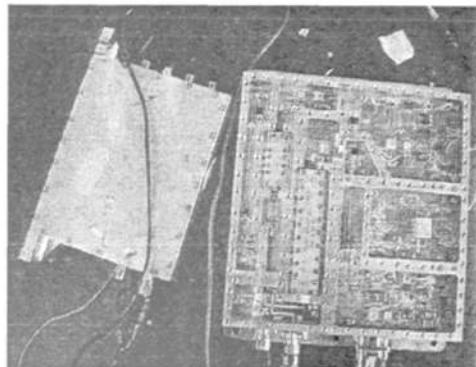

### 5.1 系统结构与实物

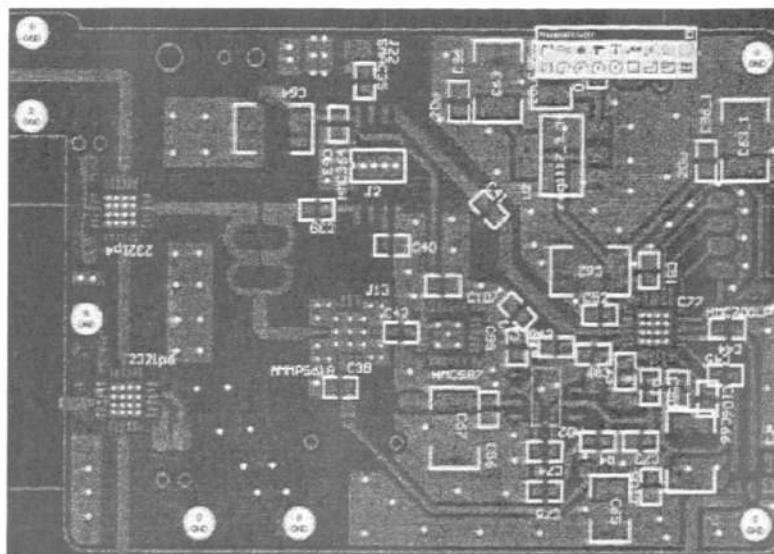

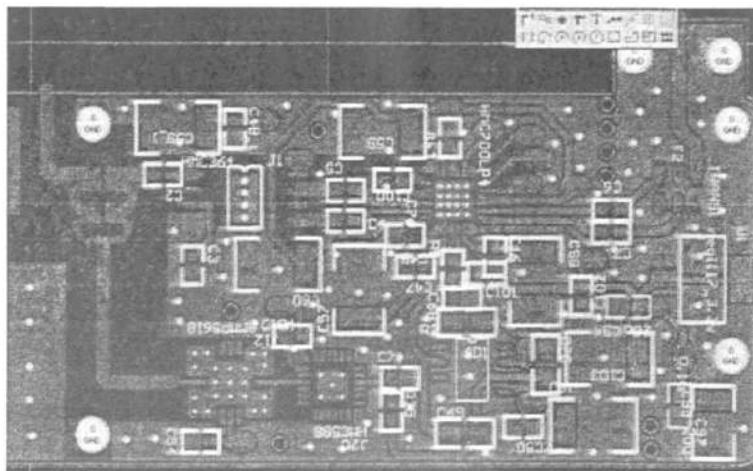

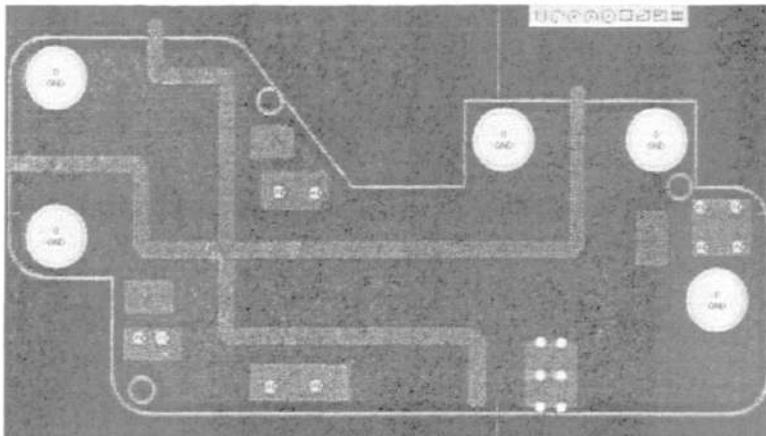

本频率源系统的实际尺寸为 $135 \times 139 \times 29\text{mm}^3$ ，系统腔体分为上腔体与下腔体：上腔体主要是射频部分，包括了两个锁相环，以及相应的倍频器、滤波器以及输出开关等等；下腔体主要是单片机等控制部分，以及相关的电源变换部分。从腔体设计以及相应的结构设计来说，主要是注意不相关信号的隔离，只有这样才能减少模块之间信号的串扰，为了加强腔体密封，一般的军品设计会有气密性以及水密性等要求，而本设计没有这方面的需求。为了更好的满足对不相关信号的隔离，除了腔体的严密性要做好以外，还追加了铺金属箔纸的设计，以及相应频率的吸波材料的设计。其上下腔体结构图如5-1、5-2、5-3所示。

图5-1 上腔体结构图

图5-2 下腔体结构图

图5-3 上腔体照片

如图 5-1 以及 5-3 所示，上腔体为微波射频电路，包括了两个锁相环等电路，为了保证 Ku 波段电路的电磁特性，对关键部分，比如 3dB 混合功分电路等都用 ADS 进行了相应的电磁仿真。图所示编号为 1 的部分是 6~9GHz 环路，右中第 2 部分为外部激励晶振 100MHz 的分路电路，为各部分提供激励信号，右下第 3 部分为 9~11GHz 环路。

图 5-1 中第 5 部分为 3~4GHz 输出通路，是从第 1 部分的 6~9GHz 的环路中引出的，经过了一根屏蔽电缆从下腔体经过，在第 5 部分经过 SNA386 等电路以后在第 9 部分通过多路开关选通输出。第 7 部分为放大器，对第 1 部分的 6~9GHz 以及第 3 部分的 9~11GHz 的信号进行功率调整，再经过第 8 部分的 6~11GHz 的介质滤波器，到达第 9 部分的开关，再选通输出。第 4 部分为倍频电路，把 7~8GHz

的信号通过倍频器，得到 14~16GHz 的信号，再通过第 6 部分的滤波器，经过放大以后，最后到第 9 部分选通。

这样的设计最大程度地避免了各部分信号间的耦合，特别是宽覆盖系统中，低端信号的高次谐波也在带内，通过对腔体的分腔设计，使谐波、电源工作频率、耦合信号等的干扰变小。

## 5.2 系统测试及结果

系统测试用到的仪器有：1、Rohde& Schwarz 公司的信号源分析仪 FSUP-26，主要用于测试相噪曲线与杂散；2、HP 公司的功率计 437B 主要用于输出信号功率的测量；3、HP 示波器 infiniium、Tektronix 示波器 TDS2022B，主要用于单片机与外界通信的测试，以及单片机对 HMC700 寄存器工作时序的测试。

本系统的测试根据指标的要求主要体现在以下几个方面

输出频率范围为：3~4GHz, 6~11GHz, 14~16GHz

输出信号步进 20MHz

相噪均在 -80dBc/Hz @10kHz 以下，

杂散在 -60dBc 以下，

输出功率在 10dBm 以上

根据设计指标的要求，对各项指标进行严格的测试，由于输出范围以及步进这两项很好检验，就不在此说明。

### 5.2.1 系统的相噪指标测试

相噪指标的测试图如下

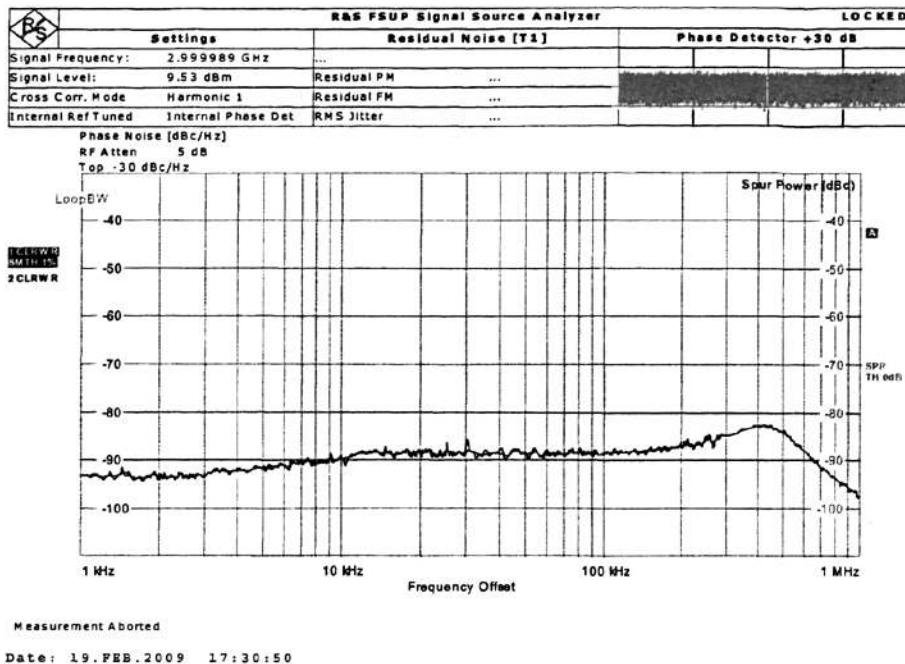

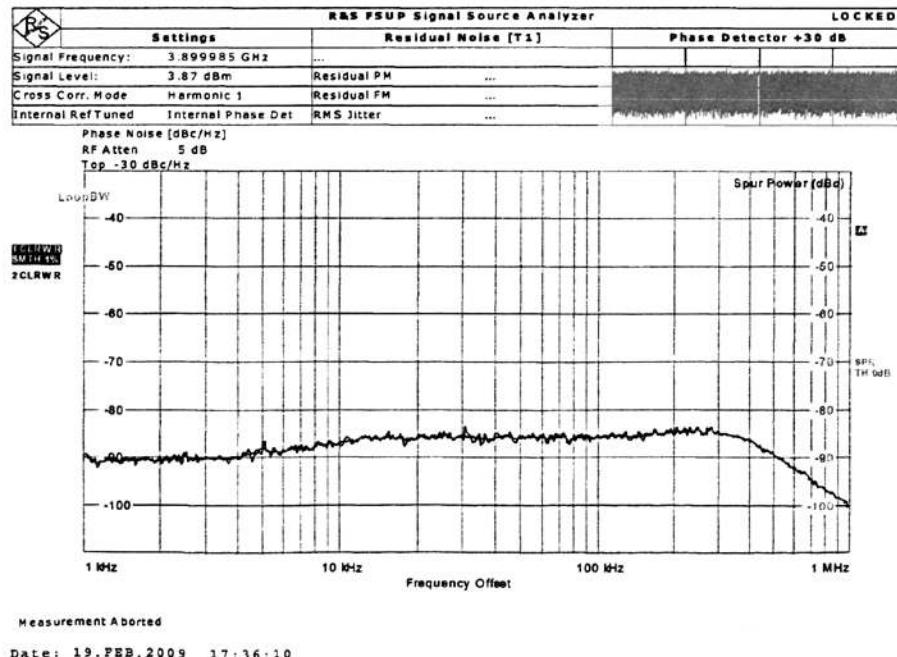

图5.4 输出为 3GHz 时的相噪曲线

图5.5 输出为 3.9GHz 时的相噪曲线

Measurement Aborted

16G

Date: 7.MAR.2009 14:30:53

图5-6 输出为 8.64GHz 时的相噪曲线

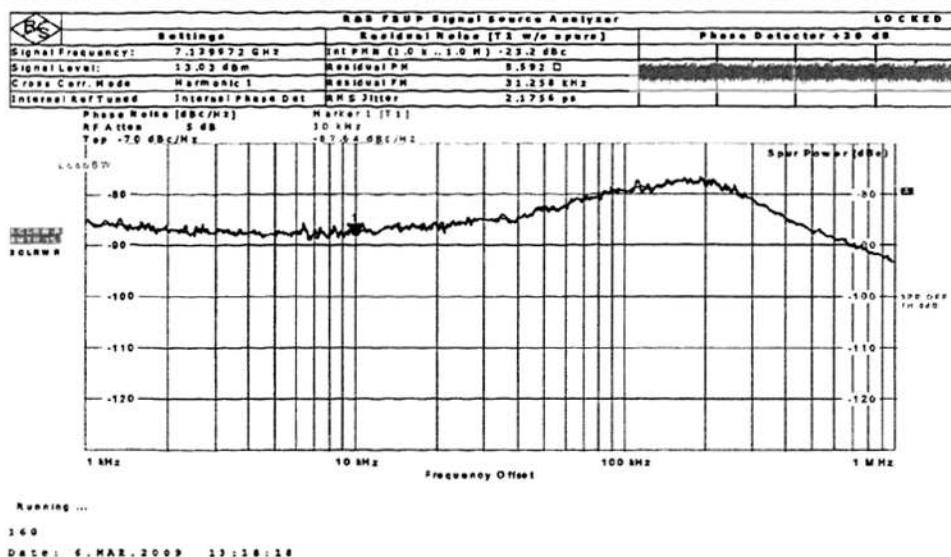

Running ...

16G

Date: 6.MAR.2009 13:12:10

图5-7 输出为 6GHz 时的相噪曲线

图5-8 输出为 9.26GHz 时的相噪曲线

图5-9 输出为 16GHz 时的相噪曲线

综合以上各图可知，系统的相噪特性均低于-83dBc/Hz@10kHz，满足了低于-80dBc/Hz@10kHz 的指标要求。

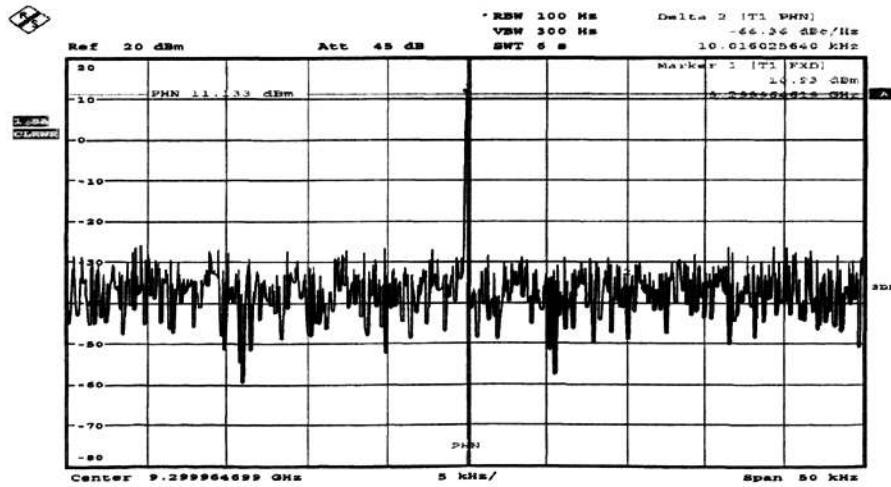

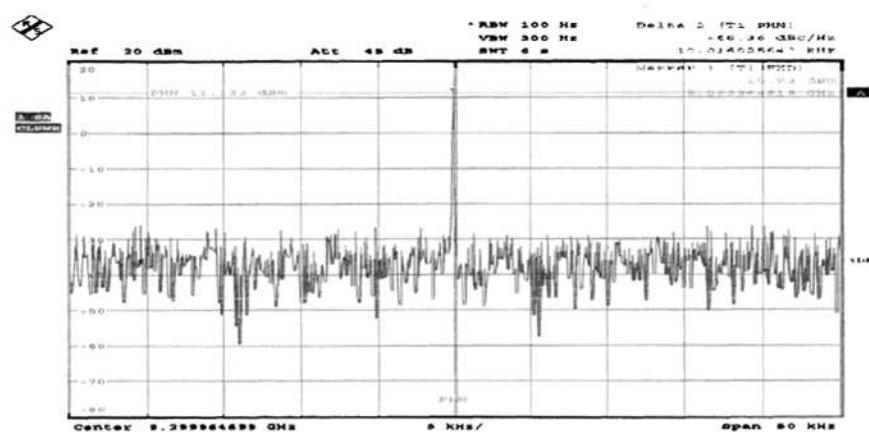

### 5.2.2 系统的杂散指标测试

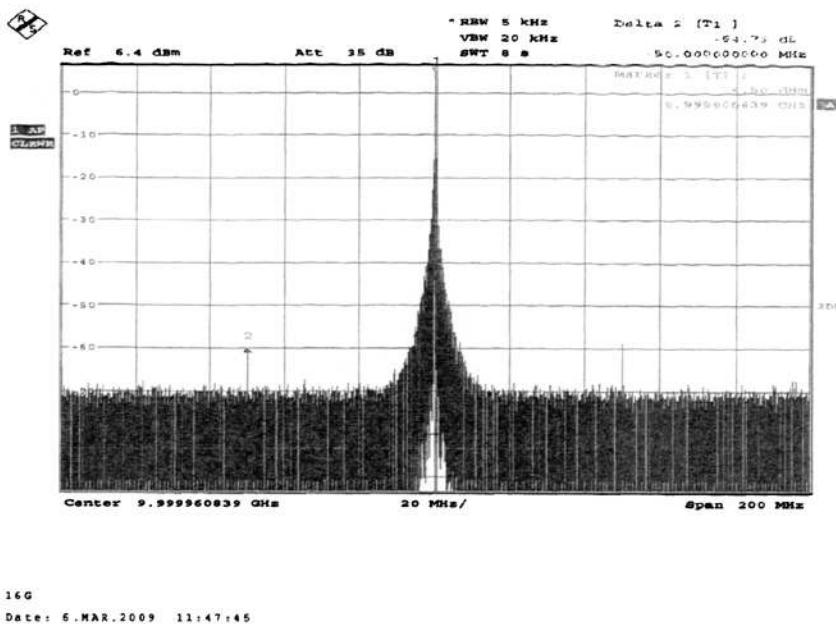

图5-10 系统的远端杂散图

图5-11 系统的近端杂散图

由上图可知系统最终有效的抑制了各类杂散，近端的电源纹波——各类电源工频干扰低于-62dBc，以及远端的鉴相纹波低于-64dBc，并且通带内的各类谐波，都得到了有效的抑制。因而系统完全满足了杂散低于-60dBc 的指标要求。

### 5.2.3 系统的功率指标测试

系统的功率指标已经在前面 4.3 节的功率调节部分做了详尽的阐述，最终的结果完全满足指标的要求，即输出功率高于 10dBm。

## 5.3 测试结果分析与改进

在本文中，详细地介绍了一种设计宽幅盖频率合成器的研制方法。测试的结果显示，这样的设计是满足系统的指标要求的，实际的测试也说明这样的设计在相噪与杂散方面比指标的要求还要好，但设计的过程中也遇到了各种各样的问题。比如前面所提到的功率问题，在宽覆盖系统中，这样的问题尤为突出，因为作为在 Ku 波段的宽覆盖系统而言，终端电路很难在几个倍频程内做到匹配。所以功率的动态范围就比较大，为 10dBm~15dBm 之间，由于指标在输出功率平坦度上的要求不高，这使得本系统中没有引入相应的宽带的功率控制模块，比如宽带的对数放大器或者类似的功率控制器件，如低频段的 AGC 芯片或者高频段上的可控衰减器，由于本系统只是作为雷达模拟器干扰源的一部分，因此，并没有引入相应的功率控制模块及与之相应的数字控制模块，在此就不再讨论相关问题了。

从测试结果来说，很值得注意的一点是，在调试过程中，同一系统用不同仪器或者方式测出的相噪指标出现了不一致的现象，虽然从测试的角度上说，应以最优指标为准，但至少说明了系统中还有不完善的地方，需要去发现且解决。比如本系统的相噪测试问题就是一个很好的例子。

180

Date: 4-MAR-2009 13:52:44

图5-12 用信号源分析仪 FSUP-26 以测相噪的传统方式测试@10kHz 的相噪

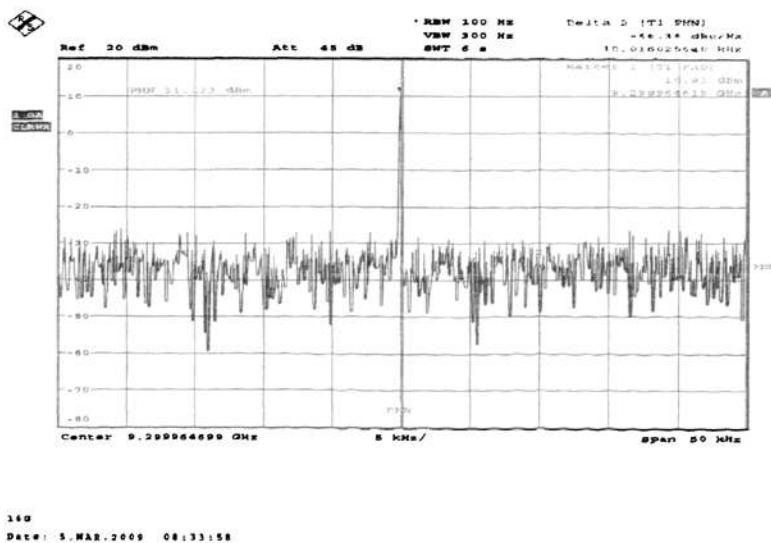

180

Date: 5-MAR-2009 08:33:58

图5-13 对图 5-12 中的信号用 FSUP-26 以传统的方式测@10KHz 相噪

图5-14 用同一台FSUP-26使用它自带的相噪测试功能绘制相噪曲线

对比图 5-13 与图 5-14 可知,用同一台仪器——信号分析仪 FSUP-26 以传统方式和相噪估计的方式,所测得的相噪有 10dB 左右的差别。这说明了系统中还有其他问题,使得测试出现这种差异。经过反复的测试与调试,发现问题在于环路中运算放大器的 AD825 的正端输入电平上。系统中所用的 AD825 的连接关系如图 5-15 所示。

图5-15 AD825的连接关系(虚线部分为添加的偏置电压部分,使相噪达到-80dBc/Hz@10kHz以下)

如图 5-15 (a) 中直接把 AD825 的正端接 5V，用两种方式得到不同的测试结果，在图 (b) 中加上了虚线部分的连接图以后，两种不同的测试方式的结果是一致的。两种连接方式的不同在于：AD825 作为运放来说，是差动放大电路，+端接 5V，使+、-两端的压差过高。对于 AD825 前级的 HMC700 中的电荷泵来说，这样的压差，往往超出了电荷泵自身的驱动能力，使电荷泵的驱动能力饱和，这样就引入了新的干扰，这个干扰因为与电荷泵的驱动能力有关，因而就会在 VCO 的电调端体现出来，最终影响了锁相环的输出。这个电压因为附加了这样的干扰，锁相环在输出时就会附加有相关的干扰，这样的干扰对于 FSUP-26 的相噪检测功能来说是不可见的，根据相噪检测的基本原理，FSUP-26 的相噪检测会中和掉这样的相关干扰，而只是检测随机特性的噪声；而按传统的检测方式，是在频谱仪上对一段时间上采集到的样本取平均，对于均值非 0 的干扰而言，是不会被中和掉的，因而出现了同一仪器用两种检测方式去测同一系统得到差异较大的不同结果的现象。

系统中对高次谐波的滤除也是一个很难的问题，对于宽覆盖系统而言，低端的 2 次，3 次甚至 4 次谐波都是在系统滤波器的通带内的，虽然通过信号分路的方式可以在一定程度上抑制低端谐波的串扰。但是对于频率的高端而言，特别是 X 波段以上的信号，为了保证功率，往往会在输出之前加放大器与滤波器，但是这样的结构在 X 波段这样的频段上会出现新的问题。因为有宽覆盖的要求，这样的滤波器因为宽的通带与体积限制，往往采用介质滤波器，对带外的抑制是有限的，因而强的高次谐波信号在滤波器抑制带的远端很难抑制到-60dBc 以下。

此外，由于腔体的密封性等问题，还有电路板间的飞线等等，往往会泄漏信号，这样的泄漏在系统中是很致命的，影响指标的实现，特别是低频信号，是通过电源线耦合到其他部分的，相互间的隔离也很难，应引起足够的重视。

## 5.4 项目总结

在本文中，着重阐述了关于宽覆盖频率源在相位噪声与杂散等关键技术指标方面实现的方法以及需要重视的问题，本设计为雷达模拟器的整机性能提供了保障，可作为雷达模拟器干扰源的关键部件。

从文中的阐述可以看到，该系统的方案上有以下特点：

1. 尽量地简化设计，充分发挥方案规划上的优势，使其结构简单，从一定程

度上减少了故障率。比如方案的选择上，可以用双环倍频切换的方案，也可以用双环嵌套加混频的方案，最终的选择要考虑很多的因素，比如后期调试的简便。比如由于指标上没有变频时间这些指标上的要求，因此在设计过程中没有采用 FPGA 去作为控制系统，而应用了单片机作为控制，使设计简易化，也便于后期的调试。

2. 对单个环路的设计尽量地扩展它设计上的弹性，尽量增加设计的裕量，设计上的灵活性是建立在新器件的应用上的，作为 08 年 Hititte 推出的最新的鉴相器芯片 HMC700，在设计中充分发挥它的性能上的优势，使设计变得有裕量，在后期的调试中，也证明了只有在方案阶段留有足够的设计裕量，才能有效的解决后期调试时出现的许多新问题。

3. 方案上的规划，特别是对频率合成器来说，频谱的规划，是设计的一个关键点，应充分考虑单个环路的性能，以及各类杂散、高次谐波等的滤除。

4. 方案设计应以需求的腔体结构为基础，充分发挥腔体空间，使分腔分版设计达到最优。

从系统的指标上考虑，系统的设计仍有很大的潜力可挖，比如功率设计，在前期分腔设计时并未考虑到几路信号到最终开关的宽带匹配，以及减少输出之间的耦合，造成后期调试功率时遇到比较大的困难。在设计单个环路的时候，对模拟电与数字电的隔离仍存在问题，在这方面如果有充分的隔离，相噪指标可以有更大的改善。

## 第六章 结论

对于任何的频率合成器而言，频率合成器的相噪与杂散水平是最重要的指标。而宽覆盖的频率合成技术，在空间、功耗等条件的约束下，使得单个分系统所要覆盖的频率范围变大，因而环路分频比会在频率的高端与低端有着剧烈的变化，不恒定的环路带宽是在宽覆盖下很特殊的一个问题，也是本文讨论的重点。在文中还对这样的宽覆盖系统中一个重要的指标——功率做了讨论，在宽覆盖的频率合成器中，输出功率以及其平坦度也是设计的一个难点，需要在前期方案的规划设计时就有细致的考虑，后期的调试与补救是很难从根本上解决问题的。

本系统在满足指标的同时尽量追求设计的简单化，并且在设计时兼顾了后期的调试工作，是一个比较合理的设计理念。

本系统的很多设计理念结合了很多前人的经典设计，在恒定环路带宽的理论方面有了一些新的理解和应用。实践表明这样的设计符合理论上的推算，证明了相关联的一些理论的正确性。在此系统的基础上，可以考虑在锁相环的激励端引入 DDS，实现小步进的频率源，该系统对设计超宽覆盖小步进频率合成器具有较强的指导意义和借鉴价值。

## 致谢

在课题完成之际，首先向长期以来指导我、关心我的导师蔡竟业教授表示深深的感谢！一直以来，学生很崇敬蔡老师细致严谨的科研作风和中庸谦和的处世态度。三年来，在老师的指导下，学生从微波射频的门外汉到今天能够独立承担设计任务，是老师不倦教诲的结果。还记得老师给学生上的第一堂课，反复提到做频率源与做人的相关之处——恪守中庸。很多很深奥的做事做人的道理，从老师口中娓娓道来，却变得浅显易懂。今天毕业论文写到此处，不禁有很多感触，老师谆谆教诲如在耳畔。文不厌繁，寥寥数笔岂能尽诉学生对老师的敬意？

衷心感谢教研室杨远望老师、刘镰斧老师、邵振海老师在课题研究阶段以及硕士学习期间对我的指导和帮助，三位老师丰富的工程经验以及平易近人的态度给我留下了深刻的印象。想杨老师已出国深造，希望学生的感谢能够传到大洋的彼岸，在此，祝老师一路平安。

衷心感谢教研室王文钦老师同时也是我尊敬的王师兄，在论文写作方面对我的指导和宝贵建议，王老师严谨的作风和亲和力，是我一生的榜样。

还要特别感谢的是成都亚光电子股份有限公司三所所长夏蓉、彭晓师傅和蒋孙冬师傅在项目设计和调试过程中给予的大力支持；衷心感谢郭杰亮、朱宁、李瑜师兄和曾秋林师姐在研究生期间对我的无私帮助；感谢教研室宦敏、钟恋、王洪英、周水平等同学在学习和生活中的帮助和关心，特别是在我人生最黑暗的时候，对我不懈的鼓励和支持。

还要深深地感谢养育我多年的母亲，是我坚强而善良的母亲的教诲，才使我能够冲破重重困难，完成我的研究生学业！

最后非常感谢参加答辩的老师，是因为您的辛勤工作使我三年的学习与努力得到承认。

## 参考文献

- [1] 向敬成. 雷达系统. 电子工业出版社, 2001, 77-79, 112-115

- [2] 田佳.雷达模拟器的研究与设计: [硕士学位论文].大连: 大连海事大学, 2008, 1-7

- [3] Kostulski, T., Reisenfeld, S. Ka band Propagation Experiments on the Australian Low-Earth Orbit Microsatellite. Communications Theory Workshop, 2005. Proceedings. 6th Australian, Feb 2005:102-106

- [4] Young Wan Kim and Jae Du Yu. 8mmPhase Noise Model of Single Loop Frequency Synthesizer, 2008 Phase Noise Model of Single Loop Frequency Synthesizer, March 2008, 54(1):112-119

- [5] Brandon, David. DDS design. Reed Business Information, May 2004, 49(10):71-84

- [6] Zhou, Jianming. A new method of spur reduction in phase truncation for DDS. Institute of Electronics Information and Communication Eng.Nov 2008,5(21):915-920

- [7] 陈邦媛. 射频通信电路. 北京:科学出版社, 2002, 139-154

- [8] Kim, Young Wan (IEEE), Yu, Jae Du . Phase noise model of single loop frequency synthesizer. IEEE Transactions on Broadcasting. March 2008, 54 (1): 112-119

- [9] Breitbarth, Jason. Additive (residual) phase noise measurement of amplifiers, frequency dividers and frequency multipliers. Microwave Journal. June 2008, 51 (6): 66-82

- [10] 张有正, 陈尚勤, 周正中. 频率合成技术. 北京: 人民邮电出版社, 1984, 19-399

- [11] 蔡竟业. 电子系统的射频和天线讲义. 成都: 电子科大, 2007

- [12] 远坂俊昭, 何希才译.锁相环 (PLL) 电路设计与应用.北京: 科学出版社, 2006, 1~17

- [13] Lian, Ping (University of Calgary, Canada); Lachapelle, Gérard; Ma, Changlin. Improving Tracking Performance of PLL in High Dynamics Applications. Proceedings of the Institute of Navigation, National Technical Meeting.2005: 1042-1052 .

- [14] Kyoungho Woo; Yong Liu; Eunsoo Nam; Donhee Ham. Fast-Lock Hybrid PLL Combining Fractional- N and Integer-N Modes of Differing Bandwidths. Solid-State Circuits.2008,43(2):379-389

- [15] Huber, L, Irving, B.T,Jovanovic, M.M. Review and Stability Analysis of PLL-Based Interleaving Control of DCM/CCM Boundary Boost PFC Converters. IEEE TRANSACTIONS ON POWER ELECTRONICS.August 2009,24(8):1992-1999

- [16] Luís Guilherme Barbosa Rolim, Member, IEEE, Diogo Rodrigues da Costa, Jr., and Maurício Arede, Member, IEEE. Analysis and Software Implementation of a RobustSynchronizing PLL Circuit Based on the pq Theory. *IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS*.Dec 2006,53(6):1919-1926

- [17] Minoru Kamata and Takashi Shono. Third-Order Phase-Locked Loops Using Dual Loops Inserting an Active Filter in the Second Loop with Improved Stability. *Electronics and Communications in Japan*.2001, Part3,84(6):273-282

- [18] Bae, Yong-Cheol. A mixed PLL/DLL architecture for low jitter clock generation. *IEEE International Symposium on Circuits and Systems*.2004, 4: 788-791

- [19] Woogeun Rhee, Keith A. Jenkins, John Liobe, and Herschel Ainspan. Experimental Analysis of Substrate Noise Effect on PLL Performance. *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS*.July 2008 55(7):638-642

- [20] Jun Ma, Mike Li, and Mark Marlett. A New Measurement and Analysis Method for A Third Order Phase Locked Loop (PLL) Transfer Function. *INTERNATIONAL TEST CONFERENCE*.2005

- [21] Seiichi Saito, Tetsuro Kate. PLL Noise Reduction Circuit to Stabilize the Disturbed Clock Pulse Due to Noise. *IEEE International Symposium on Electromagnetic Compatibility*, 1998:1004-1009

- [22] Xinhua He; Robert Newcomb; Martin Peckerar; Weixin Kong. Design and modelling of a low phase noise pll frequency synthesizer. *Solid-State and Integrated Circuit Technology*, 2006. ICSICT '06. 8th International Conference.2006:1571-1573

- [23] Djen. Fraction-N PLL Provides fastest, low noise synthesis, *Microwave & RF* 1994,33(5):95

- [24] Dean Banerjee. *PLL Performance, Simulation, and Design* 3rd Edition.2003

- [25] MARTIN JOHN BURBIDGE. Detection and Evaluation of Deterministic Jitter Causes in CP-PLL's Due to Macro Level Faults and Pre-Detection Using Simple Methods. *JOURNAL OF ELECTRONIC TESTING: Theory and Applications*.2005:267-281

- [26] Ching-Yuan Yang, Member, IEEE, Chih-Hsiang Chang, Student Member, IEEE, and Wen-Ger Wong. A  $\Delta - \Sigma$  PLL-Based Spread-Spectrum ClockGenerator With a Ditherless Fractional Topology. *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS*.Jan.2009,56(1):51-59

- [27] Kyoungho Woo, Student Member, IEEE, Yong Liu, Member, IEEE, Eunsoo Nam, Member, IEEE, and Donhee Ham, Member, IEEE. Fast-Lock Hybrid PLL Combining Fractional-N and Integer-N Modes of Differing Bandwidths. *IEEE JOURNAL OF SOLID-STATE CIRCUITS*.Feb 2008,

- [28] Ching-Lung Ti, Yao-Hong Liu and Tsung-Hsien Lin. A 2.4-GHz Fractional-N PLL with a PFD/CP Linearization and an Improved CP Circuit.2008 IEEE:1728-1731

- [29] Brad R. Jackson, and Carlos E. Saavedra. A Dual-Band Self-Oscillating Mixer for C-band and X-band Applications. *IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES*.Feb 2010,58(2):318-323.

- [30] Sushil Kumar, Julie Kessler & Henrik Morkner. 6-24 GHz Mixer Using 0.25 $\mu$ m Enhancement Mode PHEMT Technology in a Low Cost Chip Scale Package. *Proceedings of the 3rd European Microwave Integrated Circuits Conference*.Oct 2008:238-241

- [31] Haihong Ma & Xiaohong Tang. Design of 3 mm Band Hopping Frequency Synthesizer. *Int J Infrared Milli Waves*.2008,29:704-711

- [32] Radha Setty, Daxiong Ji and Harvey Kaylie. Figure of Merit of Mixer Intermod Performance(AN-00-001). *Mini-Circuits*, 2005

- [33] Tao Wu & Xiaohong Tang & Fei Xiao. Design of a W-band Stepped-frequency Synthesizer with Fast Frequency Switching. *Infrared Milli Terahz Waves*.2009, 30: 826-834

- [34] 杨国渝, 粟显义. 采用 DDS+PLL 技术实现 S 波段频率合成的一种方法. *电子科技大学学报*.1994.4

- [35] 宋庆华, 徐正芳. DDS+PLL 宽带频率合成器的设计与实现, *半导体技术*, 2008, 33 (8) : 734-736

- [36] Wengqin Wang,Jingye Cai.An Approach of Developing High Performance Millimeter-wave Frequency Synthesizer.*Infrared Milli Waves*.2006,27:931-940

- [37] 徐锐敏, 延波, 李积微. “小型 Ka 频段锁相倍频源”, *电子科技大学学报*, 2001, 30 (6) : 555-558

- [38] 李衍忠, 蔡英杰, 向敬成. DDS 谱质分析及其杂散抑制研究综述. *现代雷达*. 2000, (8), 33~38

- [39] 刘光辉, 唐小宏. DDS 阵列频率源技术研究. *电子科技大学学报*.2004,33(4):341-344

- [40] 陈大海,邓贤进,张 健, 宽带频率合成器设计及应用. 电子测量与仪器学报,2008,22(1):94-98

- [41] 王莉军,刘光祜 4~8 GHz 宽带频率合成器的设计.现代电子技术, 2008,1:66-70.

- [42] 杨远望, 蔡竟业, 任威, 徐锐敏. X~Ku 波段宽覆盖捷变频频率合成器研制. 电子科技大学学报,2007,36(4):709-712

- [43] 蔡竟业,袁文,王文钦,等.一种高分辨率低杂散频率合成器的研制.电子科技大学学报,2005,34(6):1009-1012.

- [44] TSANG K F,YUAN C M. Phase noise measurement of free-running microwave oscillators at 5.8 GHz using 1/3-subharmonic injection locking.IEEE Microwave and Wireless Components Letters,2005,15(4):217-219

- [45] Young Wan Kim and Jae Du Yu. Phase Noise Model of Single Loop Frequency Synthesizer[C]. IEEE TRANSACTIONS ON BROADCASTING,2008,54(1),112-119.

- [46] Cai J Y, Yang Y S, Yang Y W, Liu L F, Zhu X Y. High Performance Waveform Generator Design for Full-Coherent Millimeter Radar[C Proc. of 2007 Int. Workshop on Signal Design and its Applications in Communications, Chengdu, Sept. 2007,378-382.

- [47] HMC700LP4 / 700LP4E Datasheet. Hittite Microwave Corporation 2008

- [48] 赖 益,蔡竟业,杨远望,宦 敏. 3~16GHz 宽覆盖频率合成器的研制.电讯技术.2009, 11.49(11):85-89

- [49] ADF4106 Datasheet.Analog Devices Corporation.2001

- [50] MAX660 Datasheet.Maxim Corporation.

- [51] MA4AGSW3 Datasheet.Macom Corporaton.

## 攻读硕士学位期间的研究成果

参与项目：

1. 完成了基于 SAW 测相系统的设计。

2. 完成了 S~Ku 波段频综器的设计。

3. 参与了 Ka 波段收发系统（T/R 组件）科研项目。

发表论文：

[1] 赖益, 蔡竟业, 杨远望, 宦敏. 3~16GHz 宽覆盖频率合成器的研制. 电讯技术.

2009 Vol.49 No.11: 85-89