# 基于 IMT-Advanced 收发系统的 数字预失真硬件平台设计

## 摘要

本文基于 IMT-Advanced 收发系统，设计并实现了提供数字预失真功能的硬件平台。该平台可以实现传输信号的线性放大，从而提高信号的传输质量，降低误码。

文章首先对 IMT-Advanced 系统的研究现状、标准进展及技术特点进行了介绍。针对数字预失真技术的原理，引出本文所研究的数字预失真硬件平台的工作原理以及设计思路。该硬件系统可将功率放大器送出的信号耦合一部分到处理模块与基带发送来的高速数字信号进行预失真运算，从而弥补由宽带功放非线性给系统带来的影响。

其次，基于此系统工作原理、技术指标要求及冗余设计等原则，对硬件平台的主要芯片进行分析与选型，同时完成 FPGA、ADC、DAC、存储模块、时钟模块、接口模块、电源管理等模块的电路设计。

再次，本文对以上的电路进行高速 PCB 版图分析与设计。为保证信号和电源的完整性，需要对硬件的走线、过孔、电源等方面进行研究与设计，从而保证电路板的工作可靠性。

最后，本课题对数字预失真硬件平台进行功能模块调试并分析整理调试结果。该测试结果表明电源模块能够给出符合要求的电压；核心处理模块 FPGA 工作正常；生成 DDR2 的 IP 核可以读取出正确的时序信息；AD9627 可以采集给定频率的信号；时钟模块可以提供相应频率的时钟信号。这些调试结果为系统的进一步开发和完善奠定了良好基础。由于本文仅涉及数字预失真硬件平台的整体设计、芯片选型及电路设计与调试，因此关于预失真算法的分析则在本论文的研究范围之外。

**关键词：**IMT-Advanced    数字预失真    高速 PCB    FPGA

高速 ADC/DAC    IP 核

# Design of Digital Pre-Distortion Hardware Platform Based on IMT-Advanced Transceiver System

## Abstract

Based on the IMT-Advanced transceiver system, the hardware platform is designed and implemented in this thesis, which is able to provide the function of digital pre-distortion. The transmitted signal can be amplified linearly in this platform, thus the system performance is enhanced in terms of nice signal transmission and low bit error ratio.

First, the current research status, standards evolution and technical features are introduced in this thesis. According to the theory of digital pre-distortion, the working theory and design methodology of this digital pre-distortion hardware platform are illustrated in detail. In this hardware system, part of the transmitted signal can be coupled with the original high speed base band signal to perform the calculation of pre-distortion in order to mitigate the influence of the non-linear signal amplification in the original broadband power amplifier.

Second, the main chips for the system is analyzed and chosen based on the system working theory, technical requirements and the redundancy principal in this project. Meanwhile, the circuit designs of FPGA, ADC, DAC, storage module, clock module, interface module and power management module are proposed in association with the previous analysis.

Third, the relative high speed PCB board is analyzed and designed. To guarantee the integrity of signal and power, the layout, through-holes and power in the hardware should be designed carefully to provide the high working reliability of the circuit board.

Finally, the function modules in this digital pre-distortion hardware platform are debugged and relative results are organized. It demonstrates that the power module is able to provide the qualified voltage; central processing FPGA works well; the generated DDR2 IP Core can read the correct information of time sequence; the samples can be got from

AD9627 for the given frequency; and the clock module can provide various corresponding frequencies. The results show that the system design is capable of laying a strong foundation for the further development. However, what we concern about in this thesis is the system architecture design, chip selection, circuit design and debugging, thus the analysis on the pre-distortion algorithm is beyond the research scope of this thesis.

**KEY WORDS:** IMT-Advanced digital pre-distortion high speed PCB FPGA high speed ADC/DAC IP core

## 目 录

|                                 |    |

|---------------------------------|----|

| <b>第一章 绪论</b> .....             | 1  |

| 1.1 课题研究背景 .....                | 1  |

| 1.2 国内外研究现状 .....               | 2  |

| 1.2.1 IMT-Advanced 研究现状.....    | 2  |

| 1.2.2 IMT-Advanced 标准进展.....    | 2  |

| 1.2.3 预失真技术研究及硬件发展现状 .....      | 3  |

| 1.3 论文主要工作 .....                | 5  |

| 1.4 论文结构安排 .....                | 6  |

| <b>第二章 数字预失真技术与硬件需求</b> .....   | 7  |

| 2.1 数字预失真平台设计前提 .....           | 7  |

| 2.2 数字预失真技术及其基本原理 .....         | 8  |

| 2.3 数字预失真技术的硬件实现原理 .....        | 9  |

| 2.4 硬件系统难点及关键问题 .....           | 10 |

| 2.5 本章小结 .....                  | 11 |

| <b>第三章 系统方案及原理图设计</b> .....     | 12 |

| 3.1 系统硬件原理框图 .....              | 12 |

| 3.2 系统硬件框图 .....                | 14 |

| 3.3 硬件平台器件选型及评估 .....           | 15 |

| 3.3.1 FPGA 选型与原理图设计 .....       | 15 |

| 3.3.2 AD/DA 选型与原理图设计 .....      | 19 |

| 3.3.3 存储器选型与原理图设计 .....         | 22 |

| 3.3.4 时钟分配器选型与原理图设计 .....       | 24 |

| 3.3.5 USB 芯片选型与原理图设计 .....      | 25 |

| 3.3.6 电源管理选型分析 .....            | 26 |

| 3.4 本章小节 .....                  | 28 |

| <b>第四章 PCB 设计与信号完整性分析</b> ..... | 29 |

| 4.1 PCB 设计 .....                | 29 |

| 4.1.1 PCB 布局 .....              | 29 |

| 4.1.2 PCB 分层 .....              | 31 |

| 4.1.3 布线 .....                  | 32 |

| 4.1.4 硬件实物图 .....               | 34 |

| 4.2 信号完整性分析 .....               | 35 |

| 4.2.1 接地 .....                  | 35 |

| 4.2.2 滤波 .....                  | 37 |

| 4.2.3 屏蔽 .....                  | 41 |

| 4.3 本章小节 .....                  | 42 |

| <b>第五章 系统功能模块调试</b> .....       | 43 |

| 5.1 系统模块 .....                  | 43 |

| 5.2 模块调试 .....                  | 44 |

| 5.2.1 电源模块调试 .....              | 44 |

| 5.2.2 FPGA 调试 .....             | 45 |

| 5.2.3 低速 AD 调试 .....            | 46 |

|                        |    |

|------------------------|----|

| 5.2.4 DDR2 读写仿真.....   | 48 |

| 5.2.5 USB 读写方式配置 ..... | 53 |

| 5.3 本章小节 .....         | 55 |

| 第六章 结论.....            | 56 |

| 6.1 论文工作总结 .....       | 56 |

| 6.2 工作展望 .....         | 56 |

| 致 谢.....               | 58 |

| 参考文献:.....             | 59 |

| 硕士期间发表论文.....          | 62 |

| 附录.....                | 63 |

# 第一章 绪论

## 1.1 课题研究背景

作为现代先进的通信技术，第三代移动通信技术（3G）已在世界上很多国家和地区进入了市场运营阶段。相对于以前的通信技术，其可以为各种高宽带的多媒体业务提供 QoS 保障，如数据的高速传输（传输速率高达 2Mbit/s）、视频图像的高分辨率，低时延及时延抖动等。

但是，虽然 3G 系统能提供 2Mb/s 的带宽，此带宽是共享式的。当多个用户同时接入小区时，平均用户的有效带宽远低于 2Mb/s。因此在高节点密度小区，小区的服务无法满足某些多媒体业务的需求。然而，第四代移动通信技术（4G）可提供的数据传输速率将高达 100Mb/s<sup>[1]</sup>，甚至更高，因此 4G 可以支持从低速语音业务到高速多媒体的业务，甚至为更高 QoS 需求的流媒体业务提供服务。

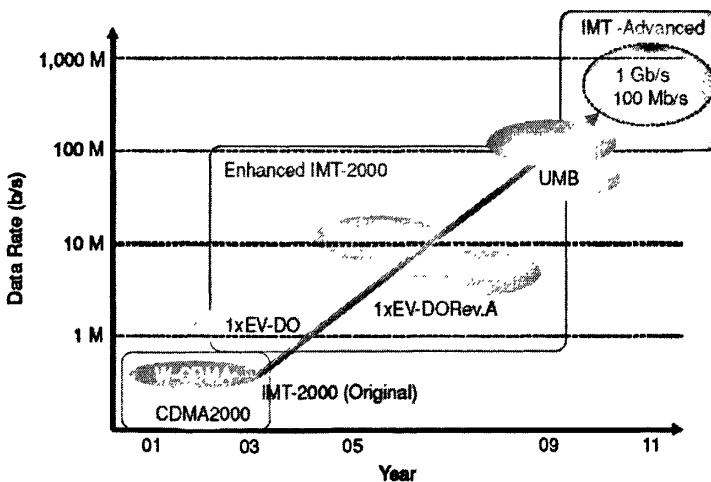

ITU-R 将 4G 技术命名为 IMT-Advanced，并对其通信速率等相关指标进行了明确的规定。IMT-Advanced 技术需要实现更高的数据率和更大的系统容量，目标峰值速率为：1) 低速移动、热点覆盖场景下，速率在 1Gbit/s 以上；2) 高速移动、广域覆盖场景下，速率在 100Mbit/s<sup>[2]</sup>以上。

在 IMT-Advanced 通信系统中，对功率放大器的带宽要求非常高，但同时功放的非线性会给信号带来失真，从而影响系统的正常工作。因此，需要采用预失真技术来对功放的非线性进行补偿，从而使得功放可以在系统规定的带宽范围内正常工作。数字预失真技术是解决 IMT-Advanced 系统中由功放非线性带来系统通行质量下降这一问题的重要技术<sup>[3]</sup>。

由于射频前端的带宽增大，并且在多天线系统中要求多通道并行工作，所以数字预失真系统的硬件平台需具备较大的带宽和较高的处理速率，同时对于多通道系统的 ADC、DAC 等性能指标要求较高，这就给系统硬件体系架构设计带来一定困难。而系统中芯片的高时钟频率，又给硬件设计带来信号完整性等相关问题。

基于上述关键技术问题，综合关键设计因素，本文提出并设计一个硬件功能平台。该平台为 IMT-Advanced 通信系统的数字预失真功能提供硬件支持，同时

关键芯片、模块的选型亦基于实现系统的基本要求进行。本文仅对 IMT-Advanced 通信系统的硬件设计及其相应模块的调试过程进行研究与讨论，对预失真算法的对比与分析则在本课题的讨论范围之外。

## 1.2 国内外研究现状

### 1.2.1 IMT-Advanced 研究现状

目前的各标准化组织正在开展针对 IMT-Advanced 的预研。3GPP2 在加紧进行空中接口演进（AIE）标准化的同时，设立了先进技术演进（ATE）项目，开始针对 IMT-Advanced 提案进行研究<sup>[4]</sup>。IEEE 在 2006 年 12 月终于批准了 802.16m 的立项申请（PAR），此项目在 IEEE 802.16e（WiMAX 技术）的基础上开发满足 IMT-Advanced 需求的技术方案。相对而言，3GPP 并没有明确展开针对 IMT-Advanced 的工作，但其长期演进（LTE）技术已经具有部分 4G 技术的特征<sup>[5]</sup>。

IMT-Advanced 候选技术评估 2008 年 10 月 ITU-RWP 5D 第三次会议起草完成了 IMT-Advanced 空中接口技术评估方法（ITU-R M.2135）和候选技术提案提交模板（ITU-R M.2133），用以指导后续 IMT-Advanced 候选技术提案的提交、评估和技术建议的起草。

从当前的国际发展形式来看，各国的研究工作均已进入系统设计、评估、实验的实质阶段，甚至已经开始“预标准化”。相对而言，我国的研究和标准化仍有大量工作需要加紧推进。我国在“十五”期间通过以高校为主的 FuTURE 计划，对相关关键技术进行了广泛的研究，取得了令人瞩目的成果。2006 年 11 月，FuTURE 演示系统在上海成功进行了测试，验证了 OFDM、GMC、MIMO 等 4G 关键技术，演示系统通过多媒体视频流验证了的宽带无线传输能力，在高速移动环境下可实现 100 Mbit/s 峰值速率，同时支持小区之间无缝切换。

### 1.2.2 IMT-Advanced 标准进展

2009 年 10 月 14 日至 21 日，国际电信联盟在德国德累斯顿举行 ITU-R WP5D 工作组第 6 次会议，征集 IMT-Advanced 候选技术。

国际电信联盟共收到来自中国、日本、韩国、欧洲标准化组织 3GPP 和北美标准化组织 IEEE 的共 6 项 4G 候选技术提案。3GPP 提交的 LTE-Advanced 技术了包括 FDD 和 TDD 模式；IEEE 提交的则是 802.16；中国提交的技术为 TD-LTE-Advanced。这些提案涵盖了 LTE-Advanced 和 802.16m 两种技术。在对这些技术提案进行总结后，国际电信联盟确定了 LTE-Advanced 和 802.16m 为 4G 国际标准候选技术。

根据 ITU 的计划，4G 通信系统提供商业服务不早于 2012 年。阿尔卡特、爱立信、诺基亚等通信巨头都组织了自己的 4G 研发团队；日本最大通信运营商 NTT DoCoMo 表示，该公司已成功完成第四代(4G)移动通信的传输实验；韩国三星称：三星电子计划从 2010 年开始，全面引进 4G 服务。图 2-1 所示为 IMT 系统的演进。

图 1-1 IMT 系统的演进<sup>[10]</sup>

### 1.2.3 预失真技术研究及硬件发展现状

#### 1. 预失真技术分类

预失真技术是一种广泛使用的射频功率放大器线性化技术，它分为射频预失真、中频预失真和基带预失真 3 种。根据预失真器信号处理的形式，又可以分为模拟预失真技术和数字预失真(DPD)技术<sup>[7]</sup>。

在预失真系统中，系统结构与实现方式对系统性能影响很大。根据处理方法的不同可将预失真分为模拟射频预失真，数字基带预失真，数字射频预失真三种，其中数字基带预失真得到的线性化效果最好。在具体实现方式方面，主要有表查

找 (LUT) 和多项式两种方式。将多项式和表查找相结合的方式，信号先经过多项式预失真，再通过表查找进一步修正，可以达到好的预失真效果。

## 2. 数字预失真的实现平台

对于数字预失真硬件平台的实现上，一般采用 FPGA 或 DSP 作为处理器进行预失真算法的实现，DSP 主要使用有 TI、AD、Motorola 等公司的产品；而 FPGA 主要使用 Altera、Xilinx、Actel、Lattice 等公司的产品。在处理高速率数据时，考虑到芯片的处理能力及可操作性，更多会选择 FPGA 作为处理器<sup>[13]</sup>。

与此同时，市场上也有独立的集成数字预失真微型模块，用以简化基站设计。凌力尔特公司 (Linear Technology Corporation) 推出宽带 RF 至数字接收器子系统 LTM9003，该器件以凌力尔特公司多年的信号链路设计经验为基础，采用易用的 11.25mm x 15mm 微型模块封装<sup>[8]</sup>，其含有一个高性能 12 位、250Msps 模数转换器 (ADC)，一个带通滤波器，中频 (IF) 放大器和一个高线性度 RF 下变频混频器。就无线基站用数字预失真实现功率放大器 (PA) 线性化而言，集成的微型模块接收器极大地节省了电路板空间和开发时间。

在原理上，面向 IMT-Advanced 系统的数字预失真技术与其在 3G 或 LTE 硬件设备上的应用是类似的，但由于 IMT-Advanced 系统带宽的原因使得其在实现的难度上会更大，例如记忆效应会更加严重，从而引入更多新的问题<sup>[13]</sup>。

目前为止，IMT-Advanced 系统的标准尚处在完善阶段，因此并没有成熟的商用系统推出，但相应的预失真技术已在不同的文献进行了研究。

文献<sup>[14]</sup>从预失真原理的角度介绍了数字预失真技术的特点和发展趋势，描述了从窄带到宽带信号的变化中系统所处理问题的重心的改变。并给出了在这个变化过程中几种相应的数字预失真实现的电路原理图，其中包括在基带适应性预失真架构等的 7 种预失真电路实现原理图。

文献<sup>[15]</sup>介绍了面向 IMT-Advanced 系统基站的数字预失真硬件实现原理，在 IMT-Advanced 系统中，3GPP 和其他标准化组织对其系统的带外抑制和功率泄露有比较高的要求，文中对 FF 和 DPD 两种预失真技术进行了比较。由于 IMT-Advanced 系统带宽高达 100MHz，如果使用数字预失真技术来实现宽带信号的失真补偿，则需要高速的 DAC，从而导致耗电量的加大。因此，必须找到耗电较小的 FPGA 来实现。如果有合适的低功耗 FPGA，则可以实现宽带数字预

失真。而系统性能也取决于放大器的最高工作效率。Doherty 放大器经常被作为主要功放，但是由于其在大功率工作时效率不高于 50%，因而 HRA 被提出来作为主放大器，它在 1.7G 频段的最高效率可达到 75%。本文文献展示并验证了一种以 HRA 作为主要放大器的预失真电路配置，工作在 2G 频段，带宽为 20MHz，文中对该预失真放大器的各项性能指标进行了分析。

LTE-A 作为 IMT-Advanced 系统的标准之一，文献[24]介绍了由 LTE 向其演进过程中的主要问题，其中对应用在 LTE-A 中的数字预失真技术及其相应的硬件平台研究现状进行了描述。

### 1.3 论文主要工作

本文的主要工作是基于课题需求，设计并实现为 IMT-Advanced 系统数字预失真运算提供硬件支持的功能平台。芯片、主处理器等的选型和原理图设计都是基于满足数字预失真功能要求进行的。但对预失真算法的分析与设计则在本课题的讨论范围之外。

本文所涉及的关键问题包括：

1. 针对 IMT-Advanced 系统的基本要求，考虑数字预失真算法对硬件平台本身性能指标的需求，完成硬件所需功能的芯片选型：包括 FPGA、AD、DA、存储器、时钟芯片等；

2. 针对多管脚 FPGA 的密集高速线布线问题，在保证信号质量的前提下，选择最优的 PCB 布局方案，完成多层、高速 PCB 板设计；

3. 硬件完成初期制板工作后，需要对各个模块进行调试和功能测试。因为各个模块能够独立正常工作是整个系统正常工作的前提。

针对上述问题，本文在对系统各个功能部分的性能要求进行了深入分析研究的基础上，进行设计与实现，最终完成预期目标。因此本论文的主要贡献体现在以下三个方面：

1. 在进行了大量调研和实验的基础上，优选了完成硬件平台的各个器件和芯片，最终完成数字预失真硬件平台的研发工作；

2. 在完成 PCB 的制板过程中，依据信号完整性分析的具体原则，考虑到高速数据线的布局优化、降低干扰等具体需求，在保证信号完整性要求的前提下完

成布板任务，并完成电路板的可靠性测试；

3. 针对项目中相关性能和指标的要求，完成 FPGA、AD/DA、存储模块、接口模块、电源模块等各个硬件部分的相应调试工作，并对调试过程中对所遇到问题依次进行处理。

## 1.4 论文结构安排

论文共分为六章，内容安排如下：

第一章主要介绍了论文的研究的背景和意义，分析了当前 IMT-Advanced 的国内外研究现状，并对本文的主要研究内容进行概述。

第二章首先简单介绍 IMT-Advanced 标准进展情况及其技术特点；其次，本章概述数字预失真技术及其基本原理，整理了数字预失真硬件平台在 IMT-Advanced 通信系统中的研究现状；最后针对项目要求对提出本硬件系统设计的难点和需要解决的主要问题。

第三章提出了硬件系统的设计方案，依据所要实现硬件平台的指标，给出相应芯片和器件的选型原则和过程，与此同时给出了功能模块相应的原理图设计方案。

第四章主要介绍了硬件平台的 PCB 和设计中遇到的问题。在考虑信号完整性的前提下，完成布局、分层、布线、电源设计等工作。

第五章主要针对各个功能模块进行调试，给出部分调试结果，同时介绍了在此过程中所用到的一些软件及其使用。

第六章对论文的主要内容和成果进行总结，并给出对今后工作的展望。

## 第二章 数字预失真技术与硬件需求

### 2.1 数字预失真平台设计前提

欲较好的进行数字预失真平台的设计，其前提是清楚 IMT-Advanced 的技术特点。IMT-Advanced 的技术特点即需要实现更高的数据率和更大的系统容量，目标峰值速率为：低速移动、热点覆盖场景下，速率在 1Gbit/s 以上；高速移动、广域覆盖场景下，速率在 100Mbit/s 以上。

在系统带宽方面，LTE-Advanced 提出了和 IMT-Advanced 相同的要求，即支持最大 100MHz 的带宽。由于如此宽的连续频谱很难找到，因此 LTE-Advanced 提出了对多频谱整合的需求。目前 LTE-Advanced 考虑的峰值速率（下行 4×4 天线，上行 2×4 天线）为下行 1Gb/s，上行 500MHz。

2008 年 6 月 WP5D 迪拜会议最终确定了 IMT-Advanced 在技术方案上的八个方面最小技术要求，其中包括小区频谱效率、峰值频谱效率、系统带宽、小区边缘频谱效率、时延、移动性和切换和 VoIP 容量等一系列参数。ITU 确定下行峰值频谱效率为 15bit/s，最大带宽为 40MHz，这意味着下行最大峰值速率在 600Mbit/s。在 2008 年 6 月召开的 ITU 会议上已经确定了 IMT-Advanced 最小技术要求。部分技术参数如表 2-1，表 2-2 所示<sup>[11]</sup>。

表 2-1 IMT-Advanced 小区平均频谱效率

| 小区平均频谱效率(bits/Hz/cell) | 下行 4×2MIMO | 上行 2×4MIMO |

|------------------------|------------|------------|

| 室内                     | 3          | 2.25       |

| 微小区                    | 2.6        | 1.8        |

| 宏小区                    | 2.2        | 1.4        |

| 高速                     | 1.1        | 0.7        |

表 2-2 IMT-Advanced 移动性

| 环境                  | Bits/s/Hz | 速度(km/h) |

|---------------------|-----------|----------|

| Indoor              | 1.0       | 10       |

| Microcellular       | 0.75      | 30       |

| Base Coverage Urban | 0.55      | 120      |

| High Speed          | 0.25      | 350      |

## 2.2 数字预失真技术及其基本原理

对于 IMT-Advanced 的各不同标准，其显著特点是高系统带宽需求，而当前相应功率放大器在规定带宽内的线性度指标很难满足要求，因此数字预失真技术被广泛使用，目的是在宽带通信系统中解决放大器的非线性问题。

数字预失真技术具有性能好，实现灵活，成本低等优点，可以有效提高发射机的效率。数字预失真又分为基带预失真，中频预失真和射频预失真等几种体制。而基带预失真避免了射频的复杂情况，便于进行数字信号处理，是本文研究的方向。

数字预失真技术是指在通信系统的基带部分完成信号预失真，达到线性化功率放大器的一种技术。由于基带信号的频率较低，容易控制和调整便于利用现代信号处理技术来处理，所以有很大优势。自适应预失真技术又分为基于查找表和基于多项式两种预失真技术。两种技术各有优点，基于查找表的预失真技术结构简单，在强非线性段，查询表预失真器的性能优于多项式预失真器，而在功放特性曲线比较陡的小信号段，多项式预失真器的性能优于查询表预失真器。

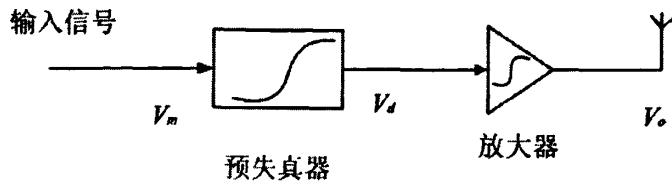

预失真系统可以通过各种各样的形式实现，但基本原理都是一样的。首先让输入信号通过一非线性器件即预失真器(其特征函数为  $F(\cdot)$ )，再送入非线性功率放大器(其特征函数为  $G(\cdot)$ )进行放大输出。调节预失真器参数使得预失真器非线性特性和功放非线性特性相反，从而使得两个非线性系统的级联表现为一线性系统。其数学描述为：

$$F(|V_m|) \cdot G(|V_d|) = K \quad \text{式(2-1)}$$

其中  $K$  为常数增益。预失真放大器的原理图如图 2-2 所示。

图 2-1 预失真原理图

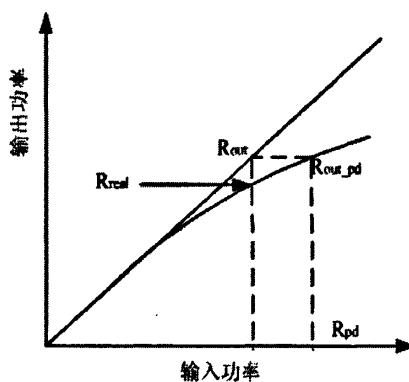

预失真器工作原理如图 2-3。设  $R_{in}$  为放大器输入信号的幅度， $R_{real}$  为相应

的输出信号的幅度，但理想的线性功放的输出信号幅度应为  $R_{out-pd}$ 。如果要使输出信号幅度为  $R_{out-pd}$ ，正确输入信号的幅度应为  $R_{pd}$ ，因而预失真器的作用就是把原来的输入信号幅度  $R_{in}$ ，调整为  $R_{pd}$ ，这样就能够把信号线性放大。相位预失真也可以通过类似的方法得到。从图 2-3 中可以看出，如果理想的输出幅度超过了放大器的饱和点太多，幅度  $R_p$  就不能够完全纠正它的非线性。只要不大于放大器的饱和电平，都可以通过预失真器校正。一旦超过了饱和电平，即使增加输入信号的幅度也不会带来输出功率的增加<sup>[12]</sup>。

图 2-2 预失真器工作原理

### 2.3 数字预失真技术的硬件实现原理

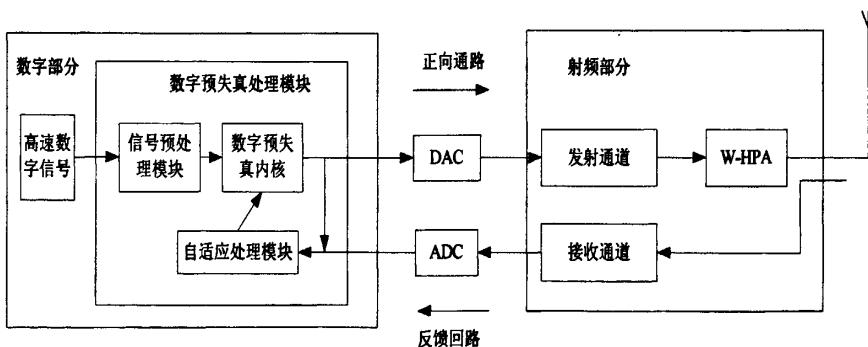

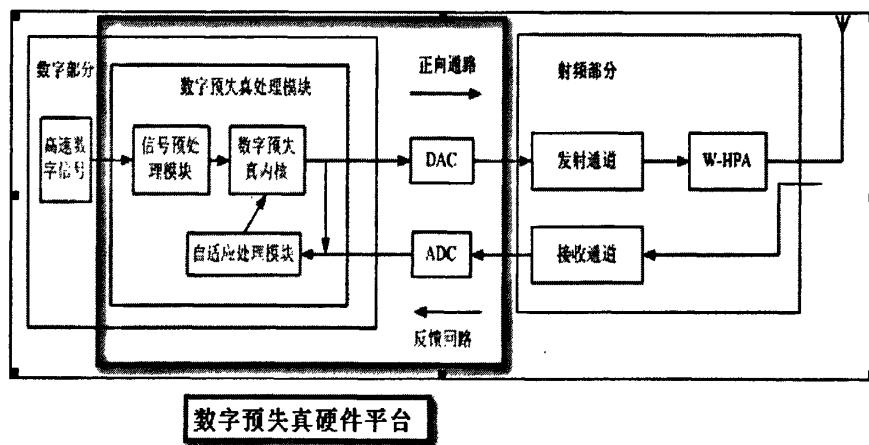

图 2-3 数字预失真系统硬件框图<sup>[16]</sup>

图 2-4 所示为数字预失真系统的硬件框图，其工作过程为：进入系统的基带信号通过数字预失真合成单元中的信号预处理模块后进入数字预失真内核。信号通过 DAC 进入射频发射通道，此时宽带射频信号经过宽带功率放大器进行发射。

与此同时，一部分信号通过接受通道耦合到预失真处理模块。经过 ADC 转换之后，反馈信号与正向通路的发射信号进行比较，得到差值。此时两路信号的差异是源于正向通路各个系统模块带来的非线性影响。数字预失真处理模块会根据相应的预失真算法进行数据处理，从而补偿系统的非线性对信号的影响。

在射频通道中，系统非线性的引入主要是来源于功放，因此从功放耦合到的信号通过反馈回路进入数字预失真处理模块来完成数字预失真算法。经过数字预失真处理后的数据再通过正向通路发送到射频部分，此时的射频信号由于已经记忆了宽带射频功率放大器的非线性参数，因此从功放发送出的宽带信号能够符合通信要求。

## 2.4 硬件系统难点及关键问题

本文所介绍的硬件系统是基于项目传输带宽不低于 100MHz 的要求，完成可应用于 IMT-Advanced 移动通信系统中数字预失真硬件支撑平台。基于项目的指标要求，本文中数字预失真部分具有如下难点：

### 1. 元器件选型

(1) ADC：根据项目要求，无线传输带宽不小于 100MHz，因此要求芯片的采样率要足够高。由于宽带功率放大器引入的非线性，使得 ADC 的工作方式需要使用高阶采样来完成。

在高阶采样中，业界普遍使用的是 3、5、7 阶采样等方式。此时系统对 ADC 的要求是：射频信号带宽为 100MHz，数字信号分成 I、Q 两路，每路各 50MHz，此时如果采用 3、5、7 阶采样，则相对应的采样速率至少分别为 300MHz、500MHz、和 700MHz，考虑到实际应用，还需要留出一定裕度。而如此高速率的 ADC 在实际应用中还很不成熟，因此 ADC 的选取及其相应电路设计成为一个难点。

(2) DAC：由于在实际应用中理想的功放并不存在，因此滤波器通常是采用升余弦滚降滤波器，此时假设滚降系数为 0.22，则可以计算出此时的发送速率约为 80MHz。与此同时，升余弦滤波需要进行插值算法，业界通用为 4、8 倍插值，如果采用 8 倍插值，则此时计算出 DAC 的转换速率要不小于 640MHz，如此高速率的 DAC 在实际电路中应用很少。

此外，根据对相关预失真算法的模拟，系统要求 DAC 的位数在 12 位以上

可以保证信号有比较好的精度。在转换速率和位数的要求下，DAC 的选型和电路设计也成为一个重点。

(3) 处理器：作为核心处理器，由于所支持的 AD、DA 性能参数都比较高，相对对核心处理器的处理速率、规模等要求都比较高。鉴于要完成对大带宽、高速率数据的数字预失真算法，系统对处理器的查找表、乘法器、存储器等资源的要求也比较高，也需要有丰富的接口资源，支持 DDR 等多种接口。

## 2. 硬件电路设计

本系统的大带宽使得硬件平台需要完成的数字信号处理速率很高，因而在电路设计上会带来相应的困难。由于系统具有多路高速数据信号，能否避免多路高速数字信号的相互干扰成为关键。同时由于系统涉及到的元器件比较多，最终完成的电路板必定是多层板，能否在保证信号完整性的前提下实现电路板的设计，也是本文需要解决的难题之一。

下面章节将详细介绍验证平台的关键芯片选型与原理图设计，由于文章的设计实现目标只限于数字预失真算法验证，并不过多考虑工程应用以及成本控制，所以在芯片选型上留有一定余量。

## 2.5 本章小结

本章首先简单介绍 IMT-Advanced 系统的标准进展状况及该系统的技术特点。之后概述数字预失真技术及其基本原理，说明数字预失真技术在 IMT-Advanced 系统中的意义和作用。最后针对项目要求对提出本硬件系统设计的难点和需要解决的主要问题。

### 第三章 系统方案及原理图设计

由图 2-3 所示的数字预失真系统硬件原理框图可知, 由数字预失真处理模块以及相应 DAC/ADC 共同组成的数字预失真硬件平台是该系统最核心的部分, 如图 3-1 所示。本文所设计的数字预失真硬件平台即位于系统图中方框所标示的位置。另外, 本硬件平台还设计有一个接收通道 ADC 模块, 由该通道发送来的信号并不需要完成数字预失真运算, 因此在平台设计中使用速率相对低的 ADC 来实现。根据项目所提出的指标要求, 本文将提供可对带宽 100MHz 信号实现数字预失真功能的硬件支撑平台, 但仅就硬件角度考虑设计与实现, 并不涉及具体的预失真算法实现。

图 3-1 数字预失真硬件平台

#### 3.1 系统硬件原理框图

本文使用 FPGA 作为核心处理芯片来完成对数字预失真算法的硬件支持, 高速数字信号与从高速 ADC 反馈回的信号在 FPGA 中实现数字预失真运算, 因此考虑到两路高速信号和相应预失真算法的复杂度, 必须使用运算速率和资源足够强大的 FPGA 作为主处理芯片。正向通路的高速 DAC 将处理好的信号送入发射通道, 反馈回路的高速 ADC 将从宽带功放中耦合回的信号送入数字预失真模块进行分析和运算。同时, 由于系统中各个功能芯片使用的时钟频率和电平不同, 需要有专用的时钟模块来提供所需的不同时钟频率和电平模式。考虑到要对

100MHz 带宽的信号实现数字预失真功能，正向通路 DAC 和反馈回路 ADC 工作频率至少在数百兆。因此，需要设计存储模块，用于在 FPGA 自带的存储器不能满足要求时，需要提供额外的大容量空间对数据进行缓存，从而将通过 AD 接收到的 IQ 数据传回 PC 以便做进一步的分析、处理。

对于接收系统，由于不需要完成数字预失真功能，在采样定理和冗余设计的原则下选择适合的 ADC，来实现信号接收。同时，需要设计相应的电源模块来满足硬件平台其他各个功能模块的电压需求。作为系统工作的原理图，电源模块暂不画出。

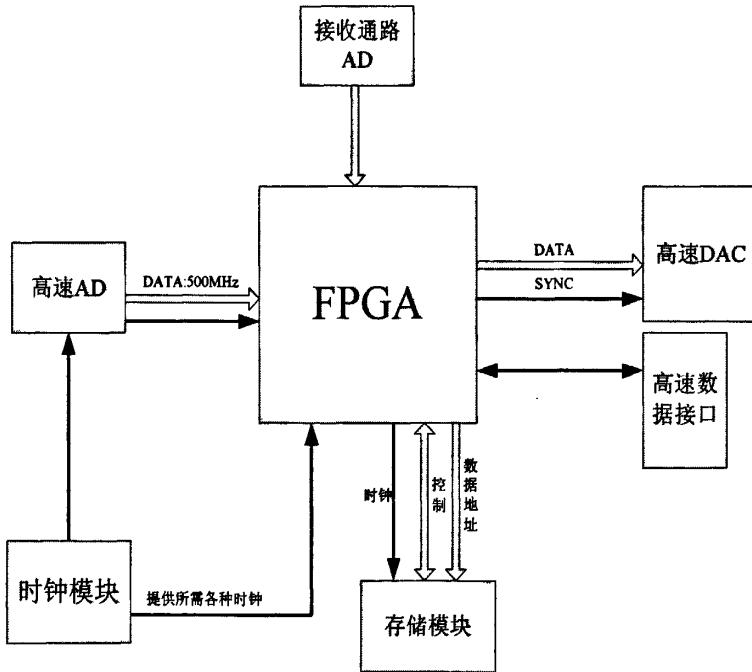

因此，本功能平台扩展为包括发射通道 ADC/DAC 模块、接收通道 ADC 模块、时钟模块、存储模块、高速接口模块、电源模块等的硬件平台，整体平台原理图如下图 3-2 所示：

图 3-2 数字预失真硬件平台原理框图

本文目标是完成一个功能强大、可扩展性强的数字基带硬件平台，并对其进行调试和分析，使得各个模块能够正常工作，满足对 100MHz 带宽信号实现数字预失真运算的硬件支持。功能强大是指系统可以实现对 100MHz 超大带宽信号实现数字预失真功能的硬件支持，可扩展性强是指本平台可以在后续研发过程中进行其他相应功能完善，例如 FPGA 中的高速数据模块可以在后期的开发过程中

进行配置和使用，与后端基带芯片进行数据通信。

本章将详细介绍各个模块的设计方案，从芯片的选型考虑入手，展开介绍各个硬件模块的设计和相关模块涉及到软件部分的工作。具体包括下述内容：

- 1) AD/DA 能与 FPGA 实现给定速率要求下的通信；

- 2) 实现并行 DDR2 存储器组对实时数据的存取；

- 3) 完成高速 AD/DA 接口的设计；

- 4) 完成 USB2.0 接口电路设计，提供硬件平台与 PC 机高速数据传输的支持；

- 5) 实现时钟电路设计，为各个功能芯片提供所需的精确时钟。

### 3.2 系统硬件框图

数字预失真硬件平台的核心为 FPGA，其实现整个数字预失真算法及射频前端器件的控制逻辑。FPGA 通过 USB 接口从 PC 机接收经过编码调制的 IQ 信号，并存储在存储器中，当处于发射状态时，FPGA 从存储器中读出数据，并从发射

图 3-3 系统硬件框图

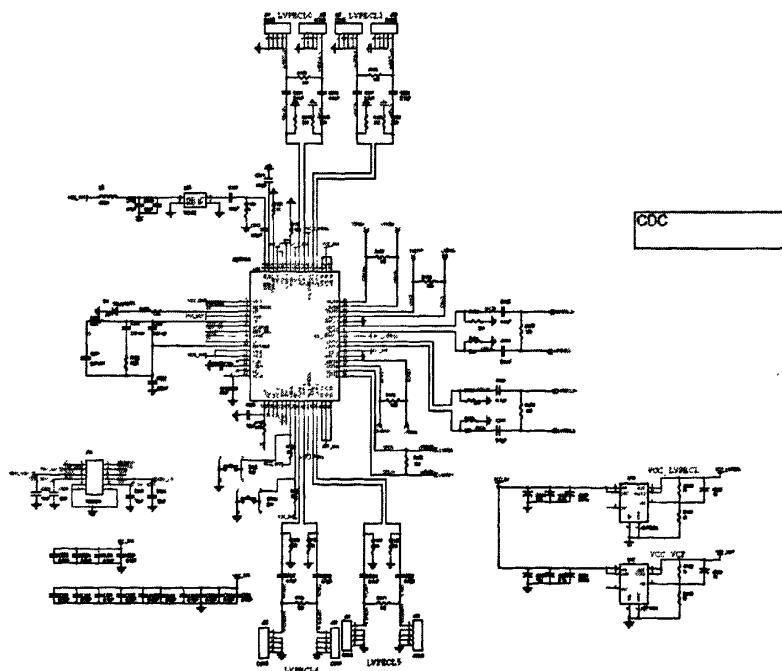

通道 DA 接口发出数据，从预失真接收通道接收的数据与发射数据通过预失真算法，并调整发射数据，改善功放非线性引起的失真。当处于接收状态时，FPGA 从接受通道 AD 接口读入接收信号 IQ 信号，并可以根据需要存储与存储器中或通过 USB 接口传输到 PC 机进行后续处理。另外硬件还包括控制接口，对射频前端器件比如 PLL，衰减器，射频开关，VGA 等进行控制；PROM，每次上电对 FPGA 进行配置；CDC，产生各种时钟，提供给 FPGA，DDR2，AD，DA 等工作时钟；电源管理器件，提供各种电平比如 0.9V，1.0V，1.8V，2.5V，3.3V 等满足各种器件的工作要求，具体的硬件结构如图 3-3 所示。

### 3.3 硬件平台器件选型及评估

对于本文所涉及到的面向 IMT-Advanced 系统的数字预失真功率放大器硬件平台，其所用到的器件包括高性能指标的 FPGA、ADC、DAC、FLASH、时钟等芯片，同时在选择好相应的器件后要考虑相互之间的兼容性问题。

在多层板层叠结构设计中，XC5VFX70T FPGA 芯片采用 BGA 封装，引脚数多达 1136。为了实现整个电路的布局布线，需要至少 10 层板，而且信号层，电源层和地层的位置分配直接关系到高速电路的信号完整性能否满足要求。

#### 3.3.1 FPGA 选型与原理图设计

对于 FPGA 选型来说，时钟频率是需要重点考虑的问题。由于 IMT-Advanced 系统要求支持到信号带宽 100M 以上，同时要支持如 16QAM、64QAM 等高阶的调制方式。因此，数字基带部分的比特率会达到 300Mbps 甚至更高。另外，由于平台需要为预失真算法提供支撑，而算法上需要通过升余弦滤波( $\alpha=0.22$ )、预失真器、插值等模块来实现。其中，插值部分可能需要进行 4 倍甚至 8 倍插值，从而得出 FPGA 的时钟速率至少要达到 400M 以上，接口速率则要支持 800Mbps 以上。同时，由于存在多条通路的并行 ADC、DAC 数字接口，要求 FPGA 的 I/O 口数量足够支持收、发以及预失真反馈通路的要求。

目前对于 FPGA 芯片主要有两大供应商，即 Xilinx 与 Altera 公司。关于这两家公司的芯片对比如表 3-1 所示。

表 3-1 Xilinx, Altera 公司 FPGA 芯片对比

| Xilinx            | Altera                  |

|-------------------|-------------------------|

| 体积更小              | 体积较大                    |

| 算术函数支持较好          | 算术函数支持不好                |

| 灵活的 I/O           | Flex 与 Apex 可实现快速双向 I/O |

| 编译时间较长            | 编译时间短                   |

| 工具复杂              | 工具简单                    |

| 功能强大              | 功能不够强大                  |

| 同时具有较大与较小的嵌入式 RAM | 没有较小的嵌入式 RAM            |

| 双端口 RAM           | RAM 有一个读一个写端口, 没有双端口    |

考虑到系统的通用性、高速率、高实时性以及未来可能的功能扩展, 本课题选择了 Xilinx 公司的 Virtex-5 系列 FPGA。Xilinx 主要有 Spartan 和 Virtex 两大系列 FPGA, 前者主要面向低成本的中低端应用, 后者主要面向高端应用<sup>[17]</sup>。

Virtex-5 系列 FPGA 第一个充分发挥了 65nm 工艺性能、密度和成本优势的 FPGA 系列产品, 与前一代 90nm 工艺 FPGA 相比, 速度平均提高 30%, 逻辑容量增加 65%。目前 Virtex-5 提供了四款不同配置的平台以满足用户不同的需求, 分别是 LX, LXT, SXT, FXT 系列。相比其他 FPGA, 其主要特点及优势如下:

- 1) 采用了 65nm 工艺, 速度等级更高, 功耗更低, ExpressFabric 架构使用了真正的 6 输入 LUT;

- 2) 增加了新型 PLL, 和原有的 DCM 模块组成了始终管理通道 CMT, 进一步增强了时钟驱动能力;

- 3) 片内集成了大量新型的 DSP 模块 DSP48E, 在 500MHz 时钟下可配置提供超过 190GMac 的 DSP 处理能力和 92Tbps 存储器带宽;

- 4) 集成了多个 RocketIO GTP 收发器, 数据传输速率从 500Mbps 到 6.5 Gbps 动态可配置, 支持 XAUI、SONET、Serial Rapid IO、PCI Express 1.1 和 2.0 等标准的各种应用;

- 5) 集成了多个三态以太网 MAC 和 PCI Express 端点模块, 便于实现接入以太网和 PCI Express 总线系统<sup>[18]</sup>。

综合考虑各方面因素, 在本课题最终选用了 LXT 系列的 XC5VFX70T 作为系统 FPGA 芯片, 它针对具有低功耗串行连接功能的高性能逻辑应用进行了优化, 不仅可以很好的完成本系统需要的接口和控制逻辑, 更因其片内集成的多个

RocketIO MGT 收发器模块，使其具备了良好的高速串行传输能力，完全满足高速实时信号处理系统的需要。

FPGA 作为硬件平台核心控制器件，其性能决定了整个硬件平台的最终性能，因此对其逻辑单元数量，DSP 模块，存储器容量，接口电平类型，接口传输速率都有较高的要求，尤其是数字预失真算法要在 FPGA 中实现，对 FPGA 的 DSP 模块和存储器容量有更高的要求，对于 FPGA 接口电平和速率，需要考虑兼容预失真通道 AD 及发射通道的 DA 的速率和电平，通过对 FPGA 性能，价格及实验室已有 FPGA 硬件平台的考虑，本系统采用 Xilinx 的 V5 系列 FPGA——XC5VFX70T 开发平台，其性能如表 3-2 所示。

表 3-2 XC5VFX70T 性能

| Slice | 逻辑单元   | 触发器        | 分布式 RAM | 块 RAM    | DCM                      |

|-------|--------|------------|---------|----------|--------------------------|

| 11200 | 71680  | 44800      | 820Kbit | 5328Kbit | 12                       |

| PLL   | DSP48E | PowerPC440 | GTX     | DDR2 速率  | LVDS 速率                  |

| 6     | 128    | 1          | 16      | 266MHz   | SDR: 645MHz<br>DDR: 1GHz |

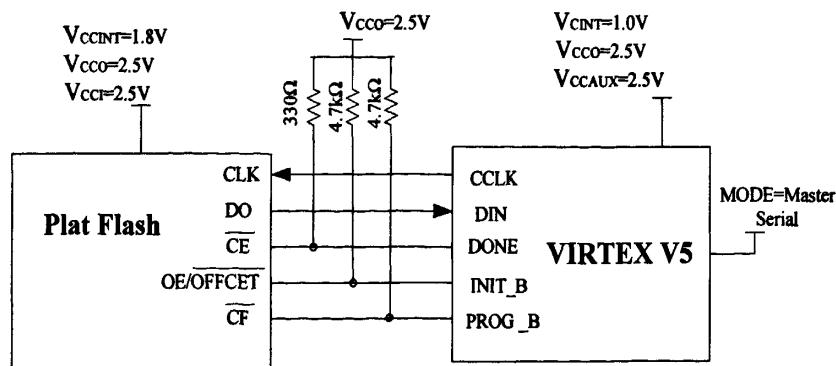

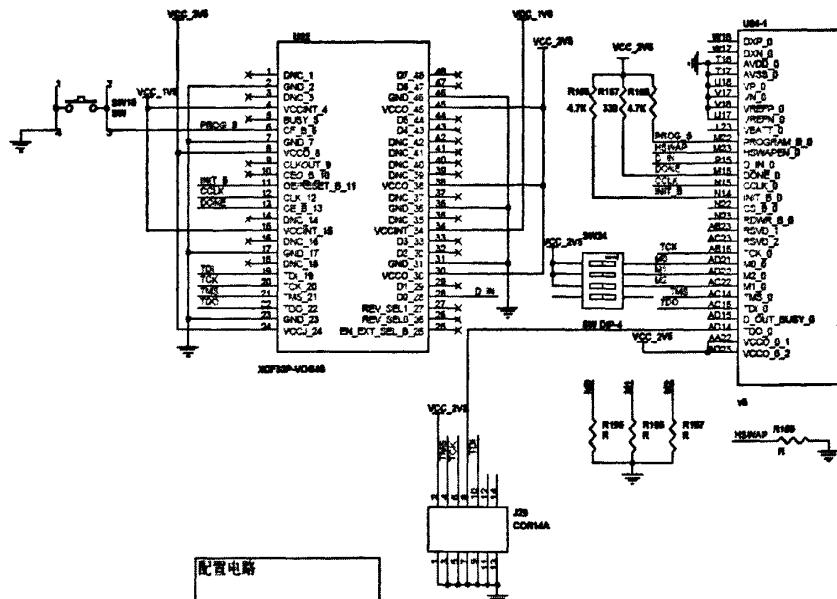

FPGA 配置电路设计：由于 FPGA 采用 SRAM 工艺，掉电后所有配置信息均丢失，因此需要外加配置芯片，以存储 FPGA 的配置信息，在每次上电时，重新配置 FPGA。配置电路分为多种模式，包括串行，并行，SPI Flash 等。由于本系统对配置速度没有要求，所以选用主动串行配置模式，FPGA 初始设置的原理图如图 3-4 所示。

图 3-4 FPGA 初始设置电路图

对于器件控制接口设计，由于使用 FPGA 作为控制核心模块，需要控制 TDD

电源开关的切换, LNA 工作状态, 衰减器衰减量, VGA 工作增益, PLL 工作频率以及 AD, DA 的工作参数等, 所有的 SPI 控制接口可以组成 SPI 总线, 以减少引脚连接数。

数字预失真算法可以有效地改善功率放大器的非线性, 优化系统的 ACLR。算法的具体实现通过在所选 FPGA 中处理发送通道输入和输出的数据, 得出发送通道非线性的多项式系数, 并根据这些系数补偿发送数据, 使整个通道达到线性化。

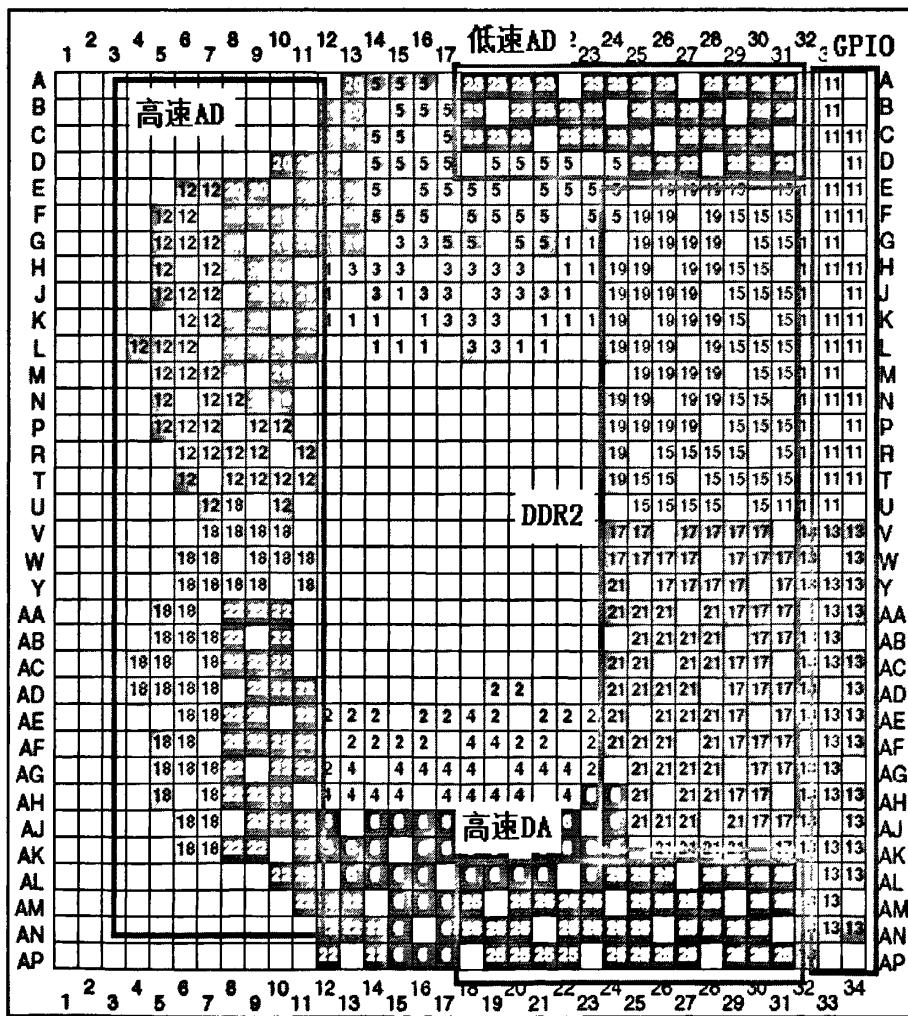

对于 XC5VFX70T, 它的 1136 个管脚分成 25 个 Bank, 其中各个 Bank 的分配如下图所示, 基于所布线性能的考虑, 优先考虑对高速、密集的芯片, 分配开阔管脚便于拉出线的 Bank。各个模块之间的连接关系如图 3-5 所示, 部分原理图详见附录 A。

图 3-5 XC5VFX70T 各个 bank 配置<sup>[19]</sup>

### 3.3.2 AD/DA 选型与原理图设计

AD 是用来将连续的模拟输入信号转换为离散的数字输出编码的一种接口转换电路。模数转换包括采样保持、量化编码等过程。采样就是将一个时间连续变化的模拟信号转换为时间上离散的采样信号。通过分析可以看到，采样信号的频率愈高，所取得信号经低通滤波器后能真实地复现输入信号，但为保证有合适的采样频率，它必须满足采样定理。

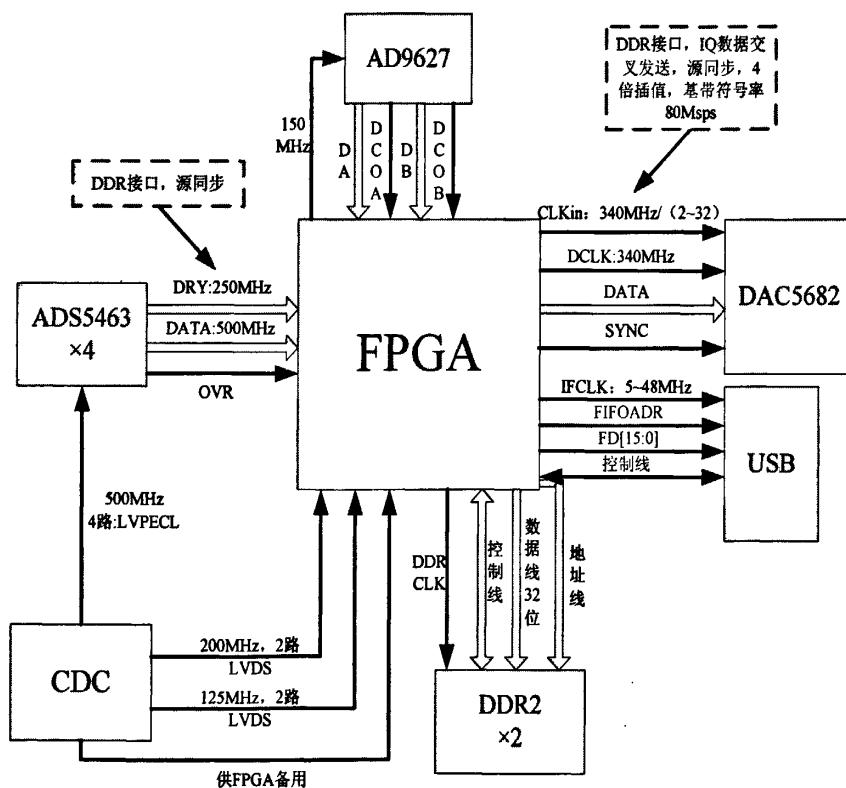

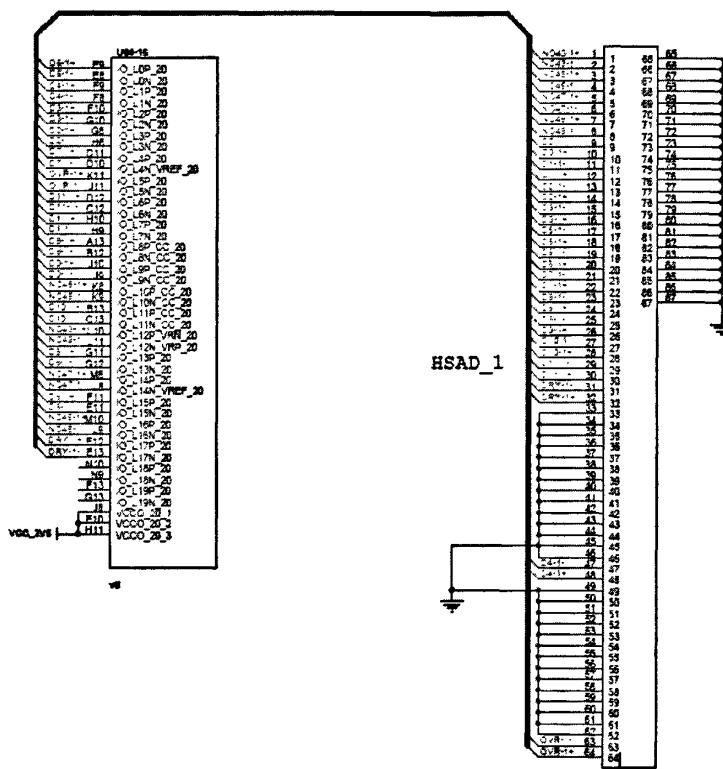

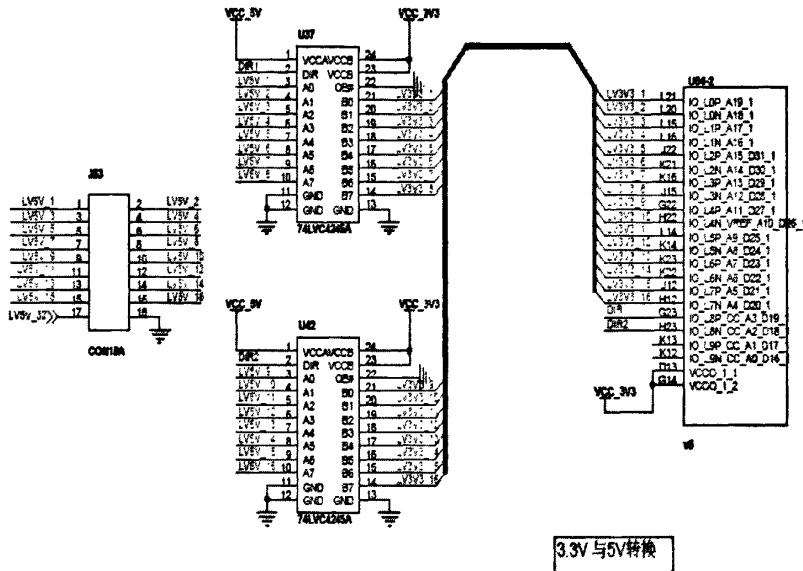

对于高速 AD/DA 接口设计，FPGA 作为后端数字处理模块，需要接收 ADS5463 和 AD9627 的数据，并将并行数据发送给 DAC5682，由于 ADS5463 和 DAC5682 和 FPGA 的数据传输速率最高可以达到 500MHz，即使是速率较低的 AD9627，也将达到 150MHz。因此 FPGA 与这些器件的接口需要注重信号完整性及走线的等长，以保证数据的正确接收。

下面即对具体的芯片选型进行讨论。

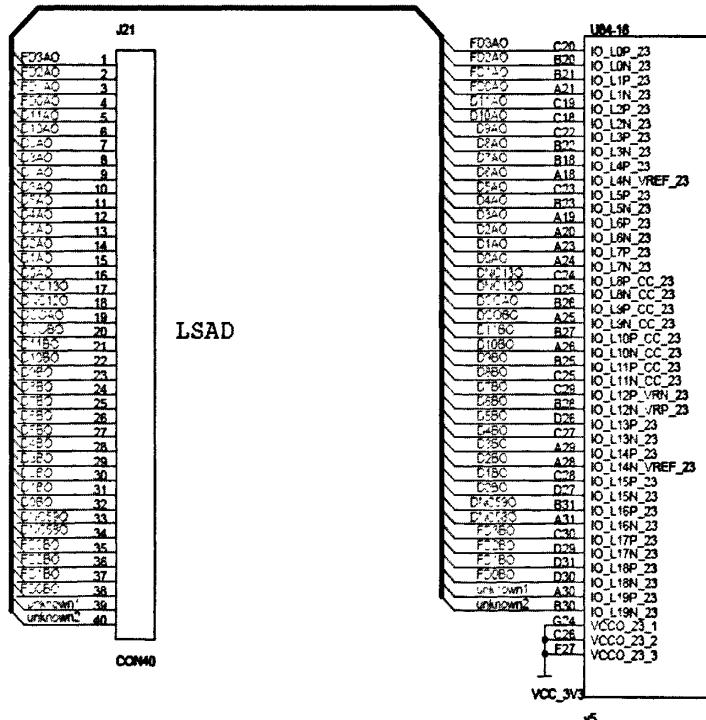

IQ 两路信号。根据奈奎斯特准则及所留的余量，选用 ADI 的 150Msps 的 12 位 AD 芯片——AD9627。12 位位宽可提供较大的动态范围，从而减轻前级 VGA 的动态范围压力。低速 AD9627 原理图如图 3-6 所示。

预失真通道 AD 由于需要采集非线性分量，按照采集 5 阶非线性计算，50MHz IQ 基带信号需要采集 250MHz 带宽，对 AD 的采样率至少要求为 500MSPS，更大采样率的 AD 对于器件选型及购买都存在较大问题，因此系统采用 TI 的 500Msps，12 位 AD 芯片——ADS5463。12 位位宽提供 IQ 信号较大的精度，满足预失真算法要求。

图 3-7 ADS5463 原理图

ADS5463 是 TI 公司推出的高速高性能 A/D 器件，具有精度高、转换速度快等特点，是当前 A/D 器件中超宽带信号采样的优选器件。其主要性能指标如表 3-3 所示。

表 3-3 ADS5463 的性能指标

|       |         |

|-------|---------|

| 位数    | 12      |

| 最高采样率 | 500Msps |

| SFDR  | 75dB    |

|        |      |

|--------|------|

| SNR    | 65dB |

| 最大工作带宽 | 2GHz |

| 功耗     | 2.2W |

该芯片模拟中频信号和时钟信号输入都采用差分形式，以增强 A/D 转换器的抗噪能力，转换后的数字输出为二进制补码，采用 LVDS 形式。芯片有数据输出指示信号 DRY，溢出标志 OVR 和基准电压  $V_{REF}$ 。

ADS5463 片上提供了采样保持电路和基准电压，使其能成为一个完整的 A/D 转换解决方案。ADS5463 内部采用二级子区式转换结构，这样既保证了转换的精度和速度又实现了较小的功耗和封装尺寸，高速 AD 原理图如图 3-7 所示。

图 3-8 DAC5682Z 原理图

## 2. DA

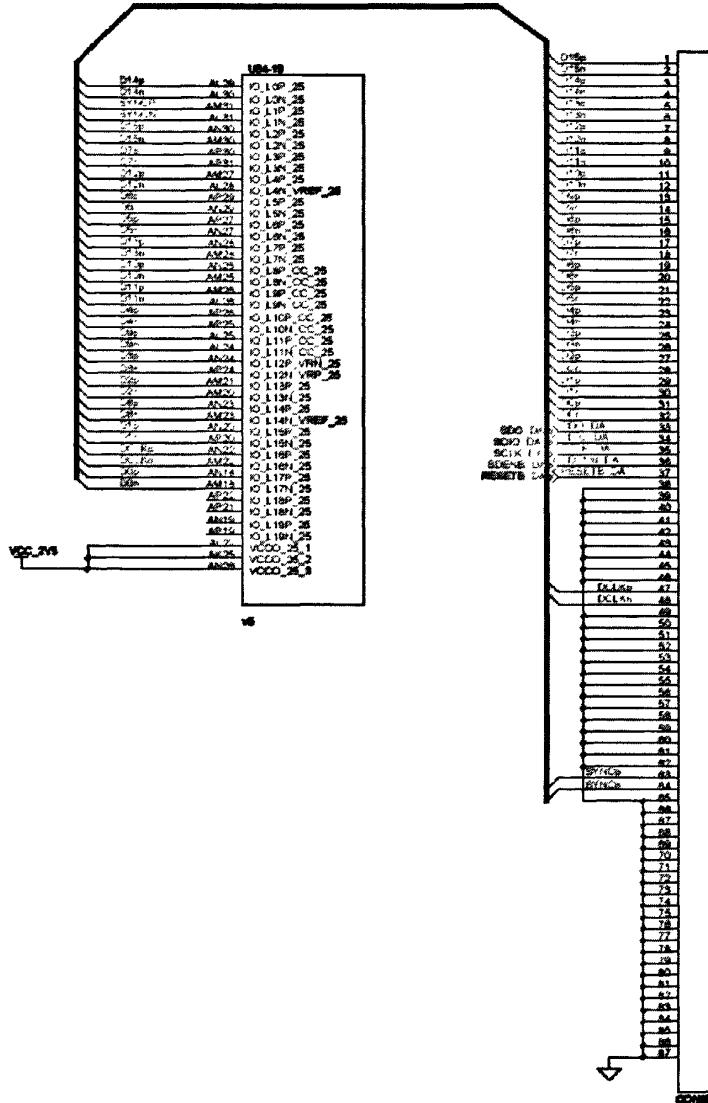

DA 将 FPGA 输出的 IQ 数字信号转变成 IQ 模拟基带信号，其转化速率由升余弦滤波插值倍速和滚降系数决定，本系统采用 8 倍插值，滚降系数采用 0.22，系统设计指标要求射频信号传输带宽 100MHz，因此基带数据码速率为

$$100\text{MHz} / (1+0.22) = 82\text{MHz} \quad \text{式(3-1)}$$

8 倍插值后速率为 656MHz，DA 的转化速率需要大于 656Msps。DA 的位数由升余弦滤波器的系数和数字预失真算法精度要求决定，理论上越大越好，鉴于实际器件选型，位数在 12~16 位均可接受。因此本系统选用的 DA 为 TI 的 16 位 DAC5682Z，转化速率为 1Gbps，满足系统要求。其原理图设计如图 3-8 所示。

### 3.3.3 存储器选型与原理图设计

#### 1. 存储器选型

DDR2 SDRAM 与上一代 DDR 内存技术标准最大的不同是：虽然同是采用了在时钟的上升/下降沿同时进行数据传输的基本方式，但 DDR2 内存却拥有两倍于上一代 DDR 内存预读取能力（即，4bit 数据预读取）。换句话说，DDR2 内存每个时钟能够以 4 倍外部总线的速度读/写数据，并且能够以内部控制总线 4 倍的速度运行<sup>[20]</sup>。

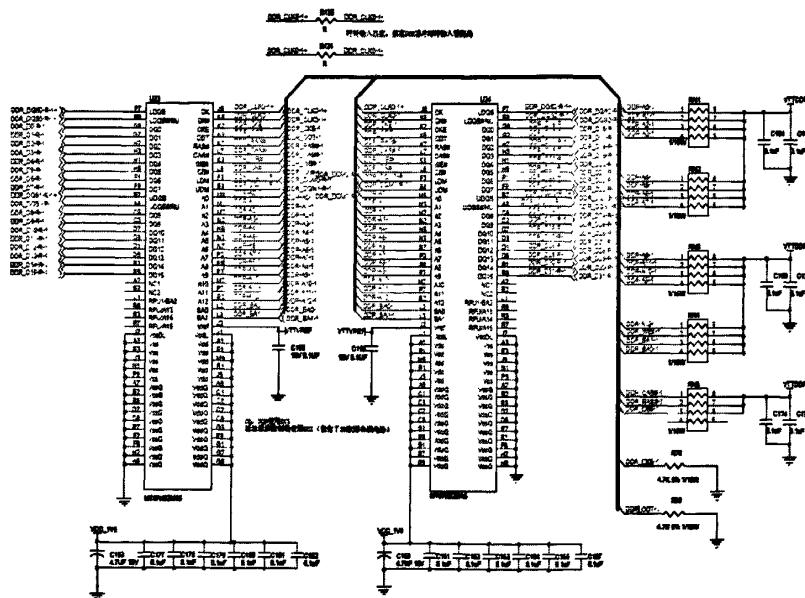

图 3-9 存储器连接原理图

存储器用于在 FPGA 自带的存储器不能满足要求时, 提供额外的大容量数据缓存空间。在发射或接收时, 可以从存储器中读取数据或将接收的数据写进存储器, 也可以在数字预失真算法执行过程中作为缓存, 存储大型的矩阵数据。由于预失真通道 AD 及发射通道 DA 的速率较高, 外接存储器为了能够实时读取和写入数据, 需要较高的工作速率, 配合当前存储器主流市场, 本系统选用 DDR2 存储器, Micro 的 MT47H32M16 内存芯片。其具有 512Mbit, 16 位数据线。为了降低内存芯片工作速率, 增大数据采集窗口, 放宽时序要求, 将两片内存组成 32 位数据总线, 由于系统会出现同时对存储器读取或写入数据状态, 为了提高吞吐率, 采用两套 32 位的存储系统, 即板子上使用 4 片内存芯片, 每两片组成 32 为存储器。

该芯片的具体参数为: 内存模组是 64 位位宽, 在缺省设置下, 每块内存芯片提供 8 位数据位宽, 容量为 64Mbytes, 即 512Mbit。内存模组使用共 8 个芯片, 共 512Mbytes 容量, 位宽为 64bits。这样每个芯片数据容量为 512Mbits, 4 个 logic bank, 每次给出数据的位宽为 8bits, 每个 logic bank 深度为 16K, 宽度为  $256 \times 32 = 8K$ 。这些都是存储量的描述, 至于带宽则为 533MB/s, 控制器给出的数据位宽为 8bits, 时钟频率为 266MHz,  $266 \times 2 \times 8 = 533\text{MB/s}$ 。芯片内部的工作时钟为  $266\text{MHz}/2 = 133\text{MHz}$ , 而数据位宽则扩大一倍, 即  $8 \times 2 = 16\text{bits}$ 。存储器的原理图如下图 3-9 所示。

## 2. 存储器接口设计

图 3-10 一套 DDR2 存储器连接图

对于 DDR 数据接收接口设计, ADS5463 输出的数据采用 DDR 模式, 即在

时钟的上升沿和下降沿都传输数据，以降低时钟频率，提高系统可靠性，因此，FPGA 与 ADS5463 的接口需要在软件上设置为 DDR 模式（采用 IDDR 原语），使其达到正确接收。

为了提供足够的空间以存储接收和发送的数据，算法运行中产生的中间数据等，需要外接存储器。对 DDR2 存储器的操作需要满足其标准规定的时序，包括初始化、读、写等时序。本系统采用 Xilinx 提供的 DDR2 接口 IP 核，以加速 DDR2 存储器接口的设计。

为了能够在发送数据的同时，实时的接受数据并进行预失真算法，本系统采用两套独立的 DDR2 存储器，同时为了降低 DDR2 工作速率，扩大数据采集窗口，采用两片 DDR2 芯片（每片 16 位数据位）组成 32 位数据总线，图 3-10 所示为由两片 DDR2 芯片连接组成的存储模块。

由于 DDR2 工作速率较高，考虑信号完整性，为了抑制反射，振铃等现象，需要在终端端接匹配电阻，不过 DDR2 芯片在 DQ, DQS, DM 等引脚上引入了芯片内部匹配终端（ODT）技术，可以省去外部的匹配电阻。DDR2 芯片采用的是 SSTL (STUB SERIES TERMINATED LOIGC) 18-II 电平，最好在所有的数据线，地址线和控制线上串联 22 欧姆~25 欧姆的电阻，同样这一选项可以在 FPGA 中设置，即使用 FPGA 引脚内部串联电阻从而省去外部串联电阻。

### 3.3.4 时钟分配器选型与原理图设计

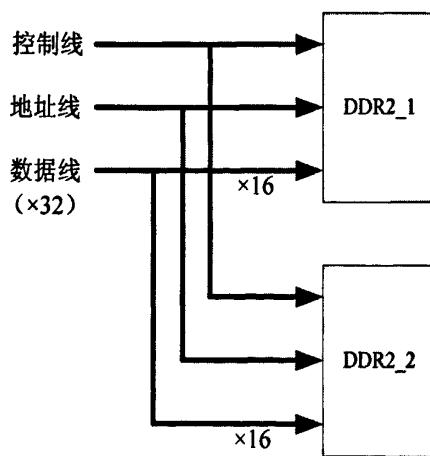

整个硬件平台需要提供多个时钟源以满足各芯片正常工作要求，即 500MHz (ADS5463), 200MHz (DDR2 IP 核), 125MHz (DDR2)。其他如 DA (AD9787), AD (AD9627), USB (CY7C68013) 等器件的时钟可以用 FPGA 的 DCM 和 PLL 产生。为了能够同时提供 500MHz, 200MHz, 125MHz 时钟，并且其输出电平与目标芯片时钟输入引脚电平兼容，本系统选用 ADI 的 AD9516-3。

该芯片的一些具体参数特点为：片上 VCO 调谐的频率达到 1.75G 到 2.25GHz；以一对差分或两根单端参考输入；具备自动参考监测能力；参考的基准频率达 250MHz<sup>[21]</sup>。

时钟分配器 CDC 用于产生 ADS5463 及 FPGA 正常工作所需的时钟资源，由于 ADS5463 所需时钟为 500MHz，大于 FPGA 自带 PLL 所能产生的最大频率，

因此必须使用外部 CDC 提供其工作时钟。在 FPGA 中实现的 DDR2 接口 IP 需要 200MHz 的数据采样窗口调节时钟和 125MHz 的系统操作时钟，该时钟需要有外部 CDC 提供。由于本系统有两套 DDR2 存储器系统，CDC 分别给每套 DDR2 存储器提供时钟，以方便操作。

本系统所选的 CDC 芯片 AD9516-3 提供 6 路 LVPECL 电平输出（每两路频率相同），4 路 LVDS/CMOS 电平输出（每两路频率相同），ADS5463 时钟使用 LVPECL 电平提供时性能较好。因此将 4 路 LVPECL 电平输出提供给 4 片 ADS5463，4 路 LVDS 输出提供给两套 DDR2 存储器所需时钟，余下两路 LVPECL 接入 FPGA 全局时钟引脚，作为备用时钟。时钟输出示意图如图 3-11 所示。

图 3-11 CDC 时钟分配网络

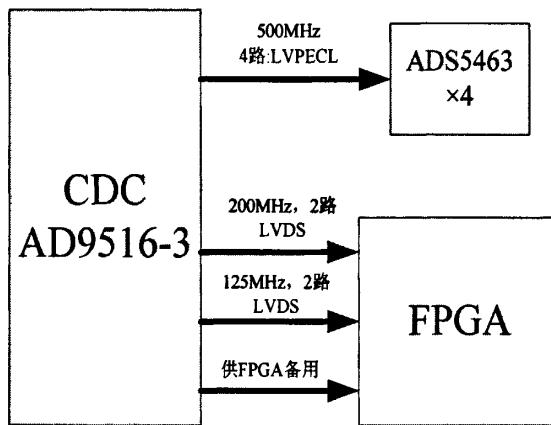

### 3.3.5 USB 芯片选型与原理图设计

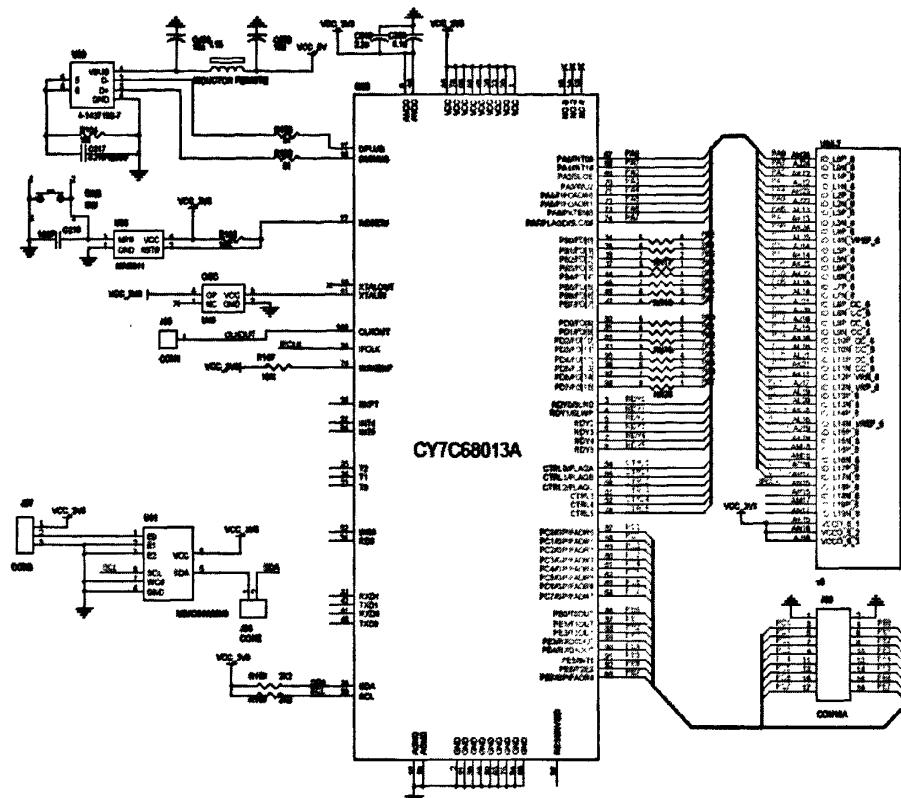

USB 电路负责对 PC 机和预失真硬件平台进行数据交互。PC 机通过 USB 电路将经过编码调制的 IQ 基带数据下载到 DDR2 内存芯片。FPGA 通过 AD 接收到的 IQ 数据也可以将数据通过 USB 传回 PC 以便做进一步的处理，为了匹配数据的接受和发射速率，要求 USB 传输具有较高的速率，USB1.1 12Mbit/s 的全速传输速率不能满足本系统的要求，而 USB2.0 最高速率可以支持到 480Mbit/s，能够满足系统要求。Cypress 的 EZ-USB FX2 系列芯片可以支持 USB2.0 协议，系统选用 CY7C68013-100 芯片。

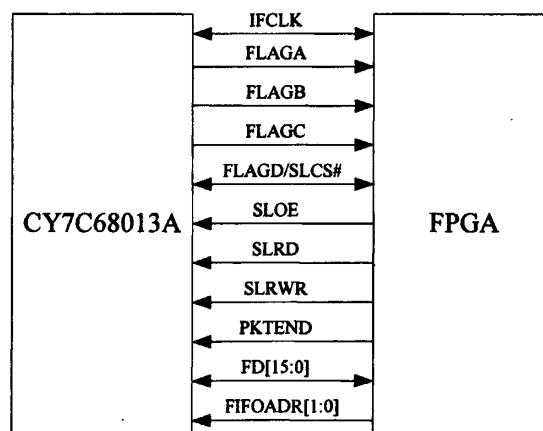

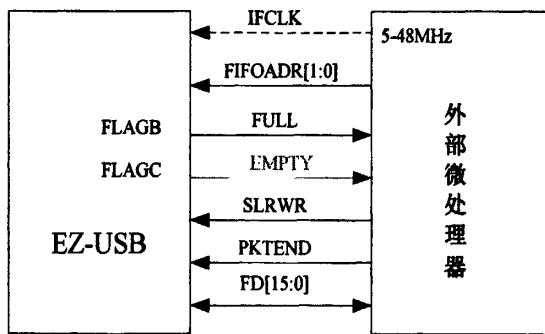

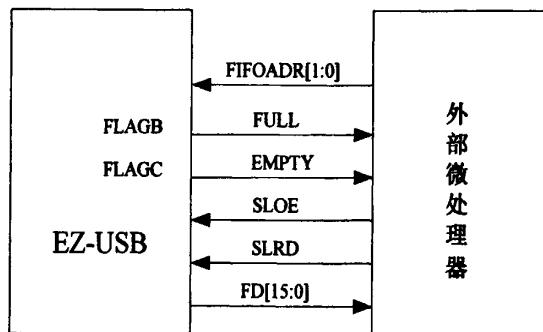

工作中 USB 芯片 CY7C68013A 处在 Slave 模式，FPGA 提供满足 Slave FIFO 要求的传输时序，做为 Slave FIFO 主控制器。Slave FIFO 的传输示意图如图 3-12 所示。

图 3-12 Slave FIFO 传输示意图<sup>[22]</sup>

在这种模式下，FX2 内嵌的 8051 固件的功能只是配置 Slave FIFO 相关的寄存器以及控制 FX2 何时工作在 Slave FIFO 模式下。一旦 8051 固件将相关的寄存器配置完毕，且使自身工作在 Slave FIFO 模式下后，FPGA 即可按照 Slave FIFO 的传输时序，高速与主机进行通讯，而在通讯过程中不需要 8051 固件的参与。

在 Slave FIFO 模式下，FPGA 和 CY7C68013A 的连接关系图如图 3-13 所示。

图 3-13 Slave FIFO 连接示意图

在该模式下，可以在主机和 FPGA 之间进行同步或异步的 Slave FIFO 读写操作，从而实现数据的交互。USB 接口的原理图如图 3-14 所示。

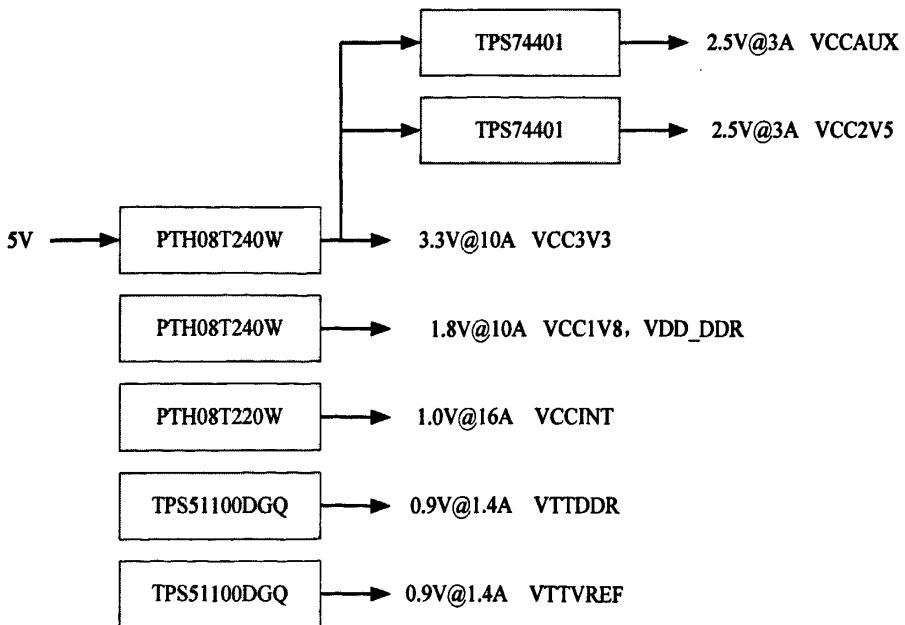

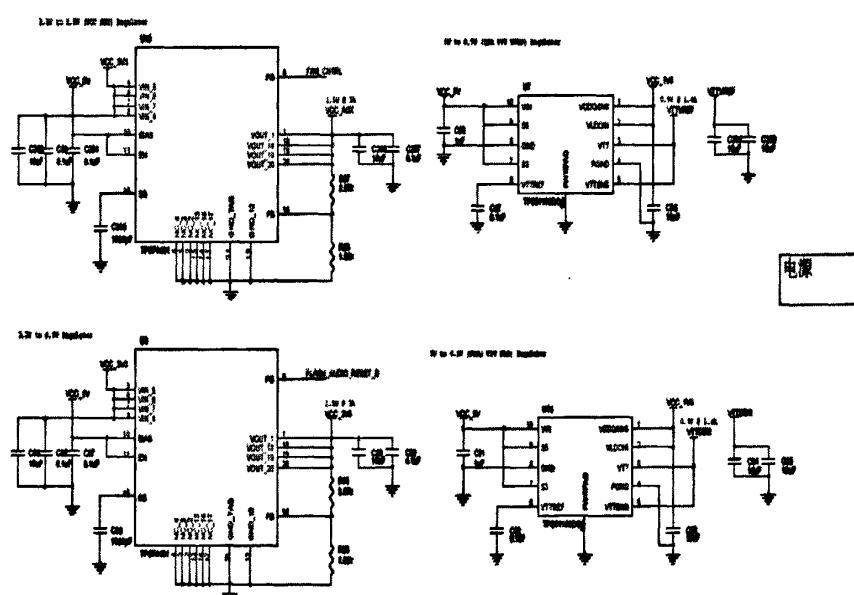

### 3.3.6 电源管理选型分析

预失真硬件平台作为高速数字电路，对于电源完整性提出了较高的要求，而且由于器件需要的电源电压类型较多（0.9V, 1.0V, 1.8V, 2.5V, 3.3V 等），本

系统采用 TI 的 FPGA 电源解决方案，使用其 PTH 及 TPS 系列电源模块及芯片。

图 3-14 USB 接口原理图

图 3-15 系统电源管理方案

整个数字处理模块正常工作所需的电源包括 3.3V (FPGA 的 LVTTI, LVCMOS 电平 bank 供电电压), 2.5V (VCC2V5: FPGA 的 LVDS 电平 bank 供电电压, VCCAUX: FPGA 辅助电源供电电压), 1.8V (FPGA 的 DDR2 接口 bank 供电电压, DDR2 芯片供电电压), 1.0V (FPGA 内核工作电压), 0.9V (VTTVREF: FPGA 的 DDR2 接口 bank 的参考电压; VTTDDR: DDR2 芯片终端上拉电压)。

考虑电压的同时, 还要确保电源芯片输出电流满足模块满负荷工作时所需的最大电流, 为了降低功耗, 还需要采用效率较高的 DC/DC 电源模块。本系统采用 TI 提供的 Virtex 5 FPGA 电源管理方案, 具体电源方案示意图如图 3-15 所示。

### 3.4 本章小节

本章提出了硬件系统的设计思路和相应设计方案, 依据所要实现硬件平台的指标, 给出相应的芯片和器件的选型原则和选型过程, 与此同时给出了以 FPGA 为核心的各个功能模块相应的原理图设计。在此过程中也简单阐述了所用芯片的工作原理。

## 第四章 PCB 设计与信号完整性分析

本章将主要介绍 PCB 电路板的设计与设计过程中信号完整性分析的相关内容。在原理图完成后导出，生成 PCB 的连接关系，此时需要注意如何对其进行结构的优化，需要考虑各个器件的位置安排，同时需要合理规划 PCB 板的层数，高速信号线的走线方式，信号完整性的分析等。

本文在 PCB 设计中的主要工作在于给出系统模块的布局、PCB 分层、相应高速差分线的布设原则以及在相应 PCB 制板过程中涉及到的保障信号完整性原则。

### 4.1 PCB 设计

用 OrCAD 完成原理图的绘制，实现各器件的电气连接，完成原理图导入，生成网表，布局布线，最后完成 PCB 的绘制。具体的 PCB 设计过程，本节的主要任务是给出系统的合理模块布局、确定 PCB 板所使用的层数、给出电源、地以及布线的设计原则，而具体的布线工作交由专业制版公司完成。下面即对 PCB 设计中重要问题进行详述。

#### 4.1.1 PCB 布局

布局是 PCB 布线前的工作，良好的布局对布线会带来很多便利，并且电路板布局是否合理对整板是否能达到预期的设计尤为重要。

布局时所有的元件均应布置在印制电路板的同一侧，即所有的功能模块均设计在 PCB 的 TOP 层，由于顶层元件过密，将一部分电容布设在底层。

按照信号的流向以及布线方便的原则安排各个功能电路模块的位置，实现以预失真功能的核心部件 FPGA 为中心来进行布局。元件的布局必须遵照便于布线和信号流通的原则，同时尽量使信号尽可能保持一致的方向。一般来说，信号的流向安排为从左到右或从上到下。在本课题中，以各个功能模块为单位来设计信号的流向，同时考虑到 ADC/DAC 模块单独调试，均设计了独立的 PCB 板。ADC/DAC 与主电路板是由 SMA 连接器来实现高速数据通信的，因此将相应的

SMA 接头应设计在板子的边缘，以利于与相应独立模块的连接。

考虑到 FPGA 在日后进行大量的数据运算，其相应发热量比较高，因此优先安排其位于利于散热的位置。如果在扩展设计中需要为 FPGA 设计独立外壳，可单独设置散热器或风扇，以降低温度，从而减少对邻近元件的影响。同时出于外围布线的考虑，使得 FPGA 对周围空间的要求比较大，这也恰与 FPGA 散热要求相一致<sup>[23]</sup>。

同时，由于主 PCB 板设计为 AD/DA 等功能模块预留了高速接口，因此需考虑板卡设计规范化，结合器件疏密和布线的难易程度，最终确定整个电路板的布局、层数以及尺寸。

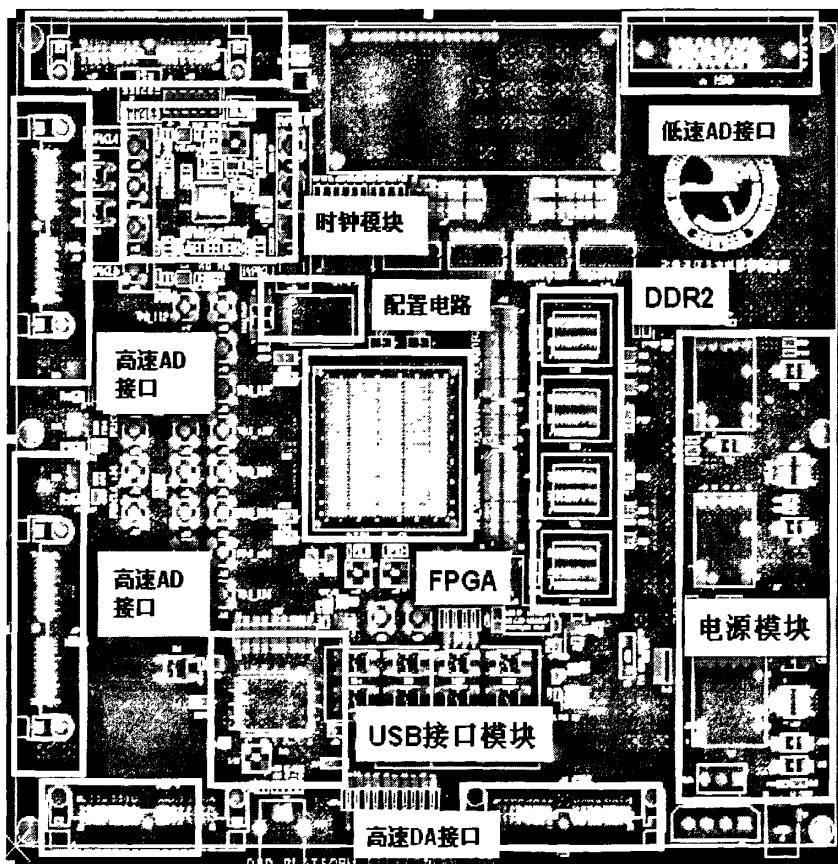

基于上述准则，本系统最终布局结果如下图 4-1 所示：

图 4-1 系统最终布局结果图

在图 4-1 中，以核心处理器 Xilinx V5 FPGA 为中心，对 PCB 进行整体布局。对 FPGA 进行初始化配置的硬件芯片位于离核心处理器比较近的位置。考虑到两组 32 位 DDR2 需要较多等长布线的原则，因此将存储器模块对称地布设在 FPGA 右边。电源模块作为一个整体，所预留的面积比较大，选择布设在整个板子的右

侧，同时相对于其他模块留出比较大的距离空间。而时钟芯片主要为 FPGA 和高速 ADC 模块提供时钟，因此选择将其就近布局在 FPGA 与高速 ADC SMA 接口之间。USB 接口模块主要提供 FPGA 与 PC 机之间的通信接口，因此将其布设在板子的下部，靠近 PCB 板的边缘。对于高速 ADC/DAC 以及低速 ADC 来说，由于只预留了接口，因此将相应的接头布局在板子的边缘。但是要注意，由于该部件在 PCB 布线中需要考虑多对差分线的布设，因此从 FPGA 的 I/O 接口 BANK 到相应的高速接口不能有过多的过孔以及器件，否则将给布线带来更大难度。

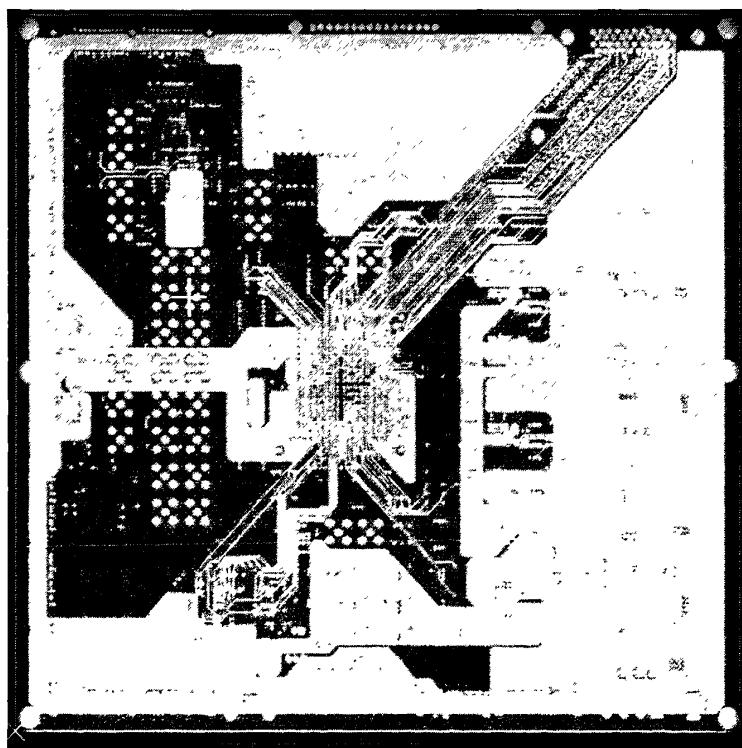

#### 4.1.2 PCB 分层

在本次设计多层电路板的时候，分层方面主要考虑两个问题：1)FPGA 的管脚是否能成功扇出；2)与信号层相邻的层是否有整层平板层，便于信号与之形成最短的回路。简单来说既要保证布线的方便，又要确保信号线之间的干扰要小。FPGA 信号线的使用决定了板卡需要的信号层数，然后与抗干扰性相结合，最终综合确定板卡总的层数<sup>[24]</sup>。最终 FPGA 板采用 FR4 板材，介电常数为 4.55，板卡共 10 层，其中内部信号层共 4 层，电源 2 层，地 2 层。板层设计如表 4-1 所示。板厚 1.6mm，大小为 203×224mm。

表 4-1 板卡分层情况

| MATERIAL | LAYER NAME      | THICKNESS |

|----------|-----------------|-----------|

| COPPER   | ARTWORK TOP     | 1.4 mil   |

| FR-4     | PREPREG         | 4.0 mil   |

| COPPER   | GROUND PLANE02  | 0.7 mil   |

| FR-4     | CORE            | 5.1 mil   |

| COPPER   | ARTWORK LAYER03 | 0.7 mil   |

| FR-4     | PREPREG         | 11.1 mil  |

| COPPER   | ARTWORK LAYER04 | 0.7 mil   |

| FR-4     | CORE            | 5.1 mil   |

| COPPER   | POWER PLANE05   | 0.1 mil   |

| FR-4     | PREPREG         | 4.0 mil   |

| COPPER   | GROUND PLANE06  | 0.7 mil   |

| FR-4     | CORE            | 5.1 mil   |

| COPPER   | ARTWORK LAYER07 | 0.7 mil   |

| FR-4     | PREPREG         | 11.1 mil  |

| COPPER   | ARTWORK LAYER08 | 0.7 mil   |

| FR-4     | PREPREG         | 5.1 mil   |

|        |                |         |

|--------|----------------|---------|

| COPPER | POWER PLANE09  | 0.7 mil |

| FR-4   | CORE           | 4.0 mil |

| COPPER | ARTWORK BOTTOM | 1.4 mil |

由于 3.3V 电源在板上很多器件都使用，所以把 L8 设计为 3.3V 电源层。L2 为可分割的平板层，把这个平板分割为 1.0V，1.8V，2.5V，5V 等这些电源共同使用。

#### 4.1.3 布线

在本次 PCB 布线过程中，由于使用到的芯片比较多，核心 FPGA 使用到的普通 I/O 接口多达数百个，同时存储模块 DDR2、以及高速 ADC/DAC、时钟等芯片的工作速率较高，需要在布线上特别注意。本文主要介绍根据布线要求所需要遵循基本的设计原则。对于高速信号线，有效地控制传输线的特征阻抗，是减小信号发射，抑制干扰的有效途径之一。

本次设计中单端线的阻抗需要设计到 50 欧姆，差分线阻抗为 100 欧姆。特征阻抗的大小同时决定了相应信号线的线宽。在考虑线宽的同时，线长应该尽量短，这样可以保证在信号传输过程中避免受到干扰的同时也减少对其他信号的干扰。

本次设计在遵循这些设计原则的前提下，对于特殊情况也必须考虑线距和线长等因素<sup>[30]</sup>（例如布线没有足够空间需要额外绕行蛇形线）。

例如第 3 层和第 8 层由于其上下电路层都是完整的地层，因而比较适合走敏感、重要的信号线的区域。而时钟线必须所有信号线分开以保证时钟的准确性，顶层和底层走微带线。

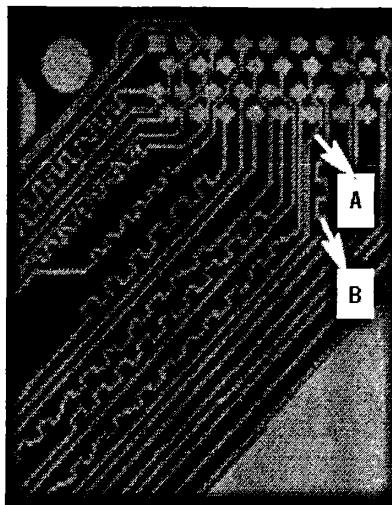

设计过程中，电源和地线处理是很重要的，它是整个电路板工作的基础。图 4-2 参照第三层信号层的 PCB 板，对布线原则进行介绍。

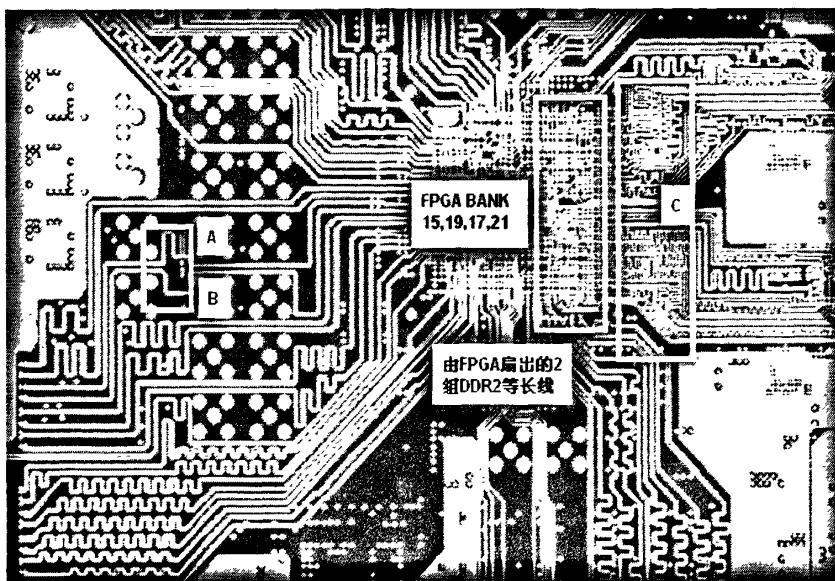

图 4-2 中的 A,B 所标示的信号线，由 FPGA 连接到高速 ADC 接口。由于高速 ADC 芯片的工作频率较大，理论上必须保证信号的等长布线，从而保证 12 位数据能够同时到达。但是由于各个管脚与 FPGA 相应 BANK 之间的相对位置不可能是完全对称，因此需要使用蛇形线来实现等长走线。同时为了保证信号的完整性，防止其他信号的干扰，选择采用差分布线。A、B 两条信号线为一对差分线。考虑到差分线的阻抗匹配原则，单根差分线阻抗为 50 欧姆，而一对差分

线为 100 欧姆，经相应软件计算信号线的宽度普遍采用 6mil。

图 4-2 L3 信号层布线局部图

对于 DDR2 来说，使用到 FPGA 的 I/O 接口 BANK 为 15、19、17 和 21，如图 4-2 中的 C 框所示的数据和地址线。作为两组并行的存储模块，必须保证 32 位数据能够同时到达，即需要保证 32 位数据线之间要做到等长布线，因此也需要用蛇形线来补偿距离。而对于地址线来说，地址信息也要保证同时到达，但数据线与地址线之间的相对长度则没有硬性规定。

对于高速同时要注意地线之间的长度不能超过波长的  $1/20$ ，同时采用多点接地法，如果太长则接地效果会比较差，即地与地之间会有电压差值出现。对于本课题，在空间允许的条件下，在多点接地的部分应尽量保证接地点有合理的密度，以保证接地良好。同时，接地线尽量加粗。因为如果接地线用很细的线条，则接地电位会随电流的变化而变化，从而降低抗噪性能。

在具体布线过程中，时钟线同样需要考虑等长的问题，也需要蛇形走线。但是由于时钟线（单根或一对差分线）本身比较少，因此对于时钟线的布线相对要容易一些。

整个板卡的布线工作量较大，且走线最密集的部分在 FPGA 引脚附近，因此 FPGA 引脚分配需要根据 PCB 走线实际情况进行调整。XC5VFX70T 的 1136 个引脚中，有 600 多个作为通用 I/O 口，布线时根据走线情况实时调整分配，而不必拘泥于原理图绘制时 pin 到 pin 的确定连接关系。但作为固定功能引脚是不能

重新分配的，即使走线比较困难也要通过加过孔、绕行等方法完成。

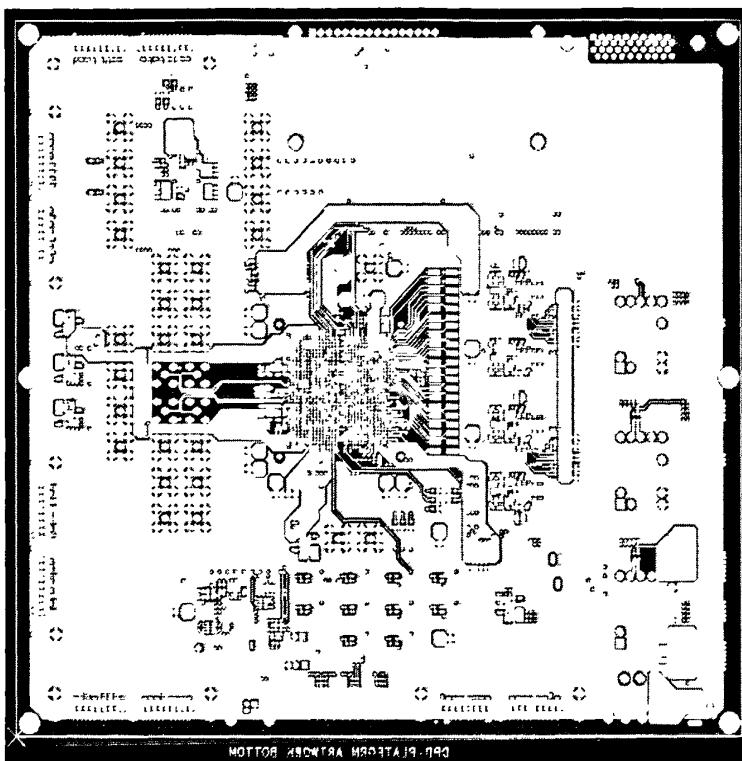

#### 4.1.4 硬件实物图

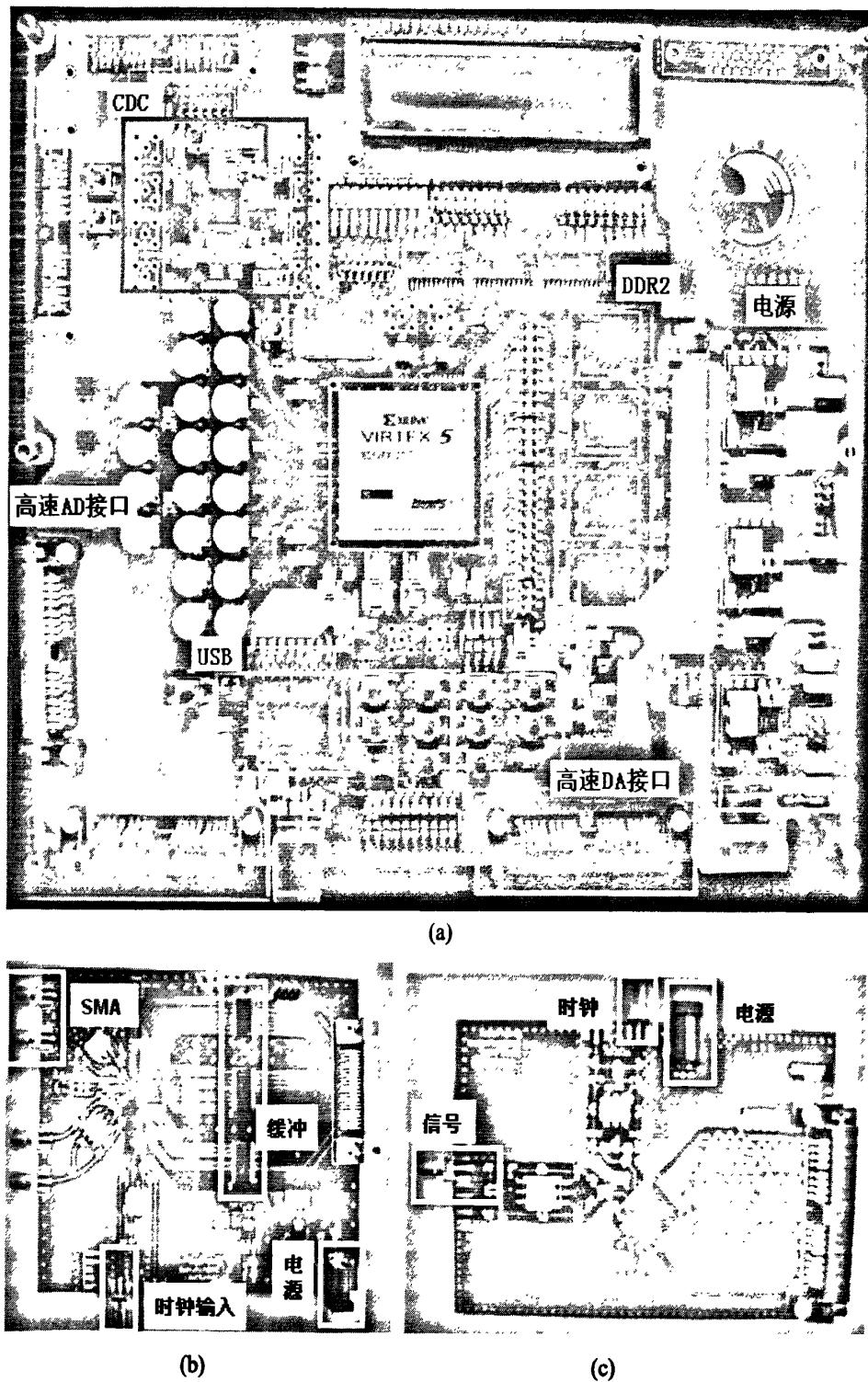

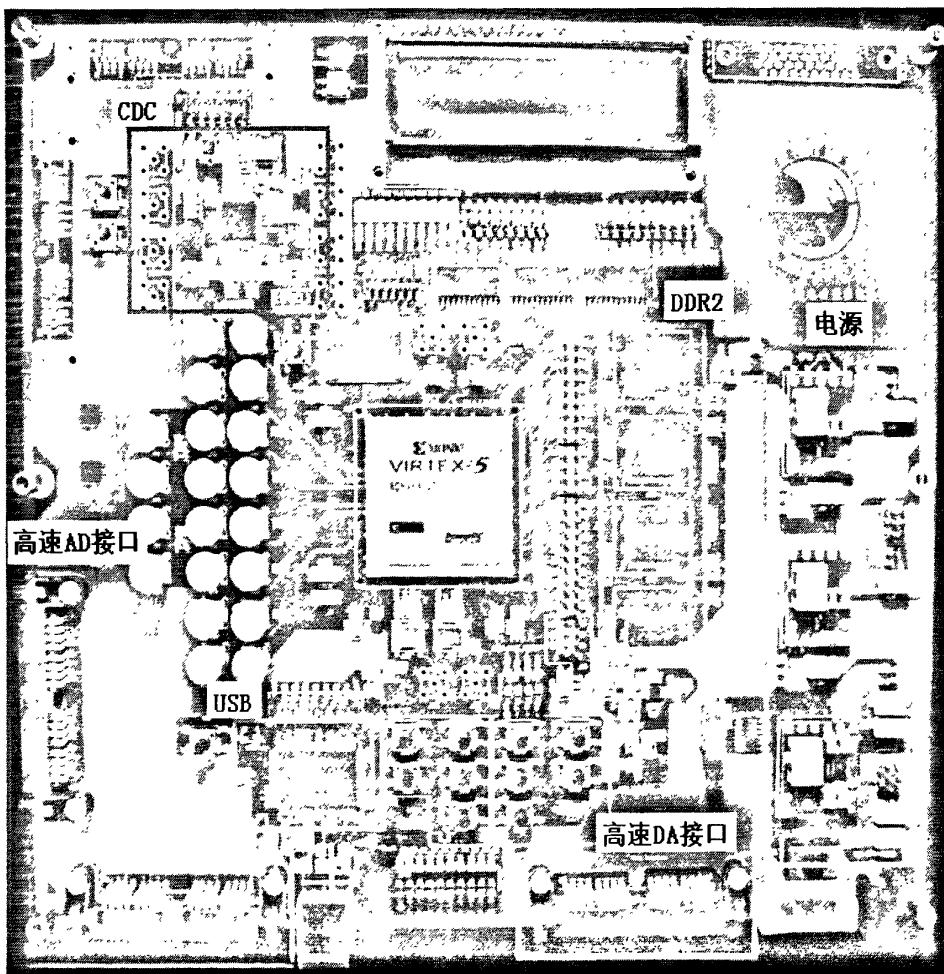

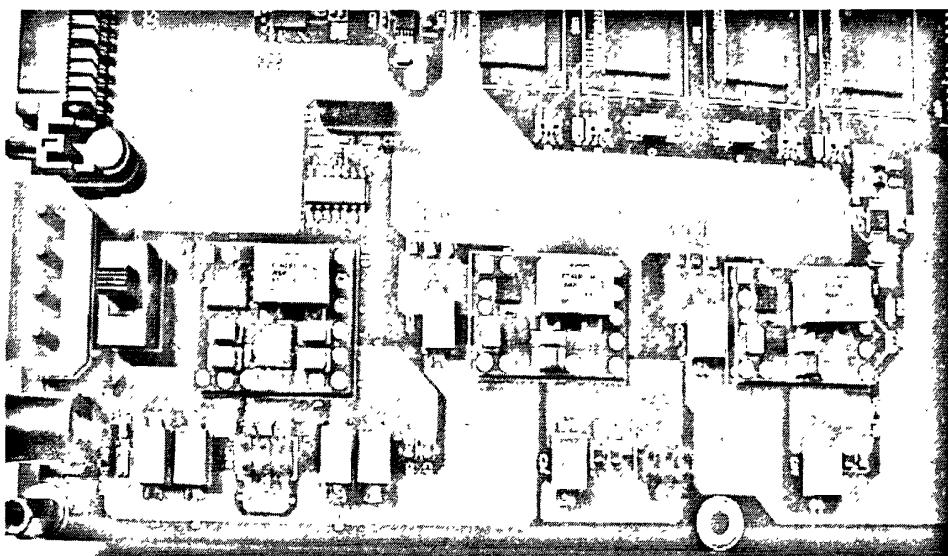

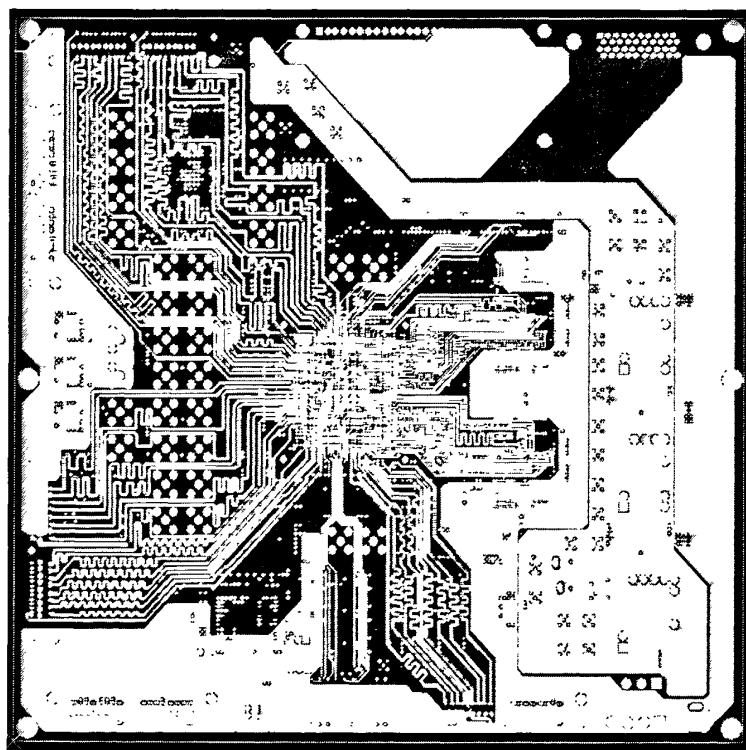

图 4-3 系统硬件实物图((a)预失真平台主电路板(b)AD9627 (c) ADS5463)

电路板制作完成后，先对 BGA 封装芯片进行焊接，之后完成电路其他部分，最后要检查关键信号线，看是否存在由于 BGA 焊接引发的短路、短路等情况<sup>[32]</sup>。在焊接过程中要坚持时钟和电源优先的原则，焊接与调试同步进行。数字处理平台包含 FPGA 板，高速 ADC 板，低速 ADC 板和 DAC 板。其中，高速 ADC 板、DAC 板与 FPGA 板之间采用高速差分连接器 Samtec QMS-032-01-SL-D-DP-RA，而低速 ADC 板与 FPGA 板之间采用 SCSI 连接器连接。图 4-3 是已经完成的硬件实物图部分。

如图 4-3 所示，所完成的硬件实物主要包括 3 个部分，(a)图为数字预失真主电路板，该板的各个主要功能模块如图 4-3 所示，其主要分为 FPGA、存储模块、电源、USB 接口模块、CDC 时钟模块等。为方便调试，将 ADC/DAC 分别制作相应的电路板，在系统整体调试和工作时，用相应的接插件进行连接。

(b)图为 AD9627 电路板。SMA 接口分别输入 I, Q 差分信号，150M 工作时钟由 FPGA 提供，缓冲芯片的功能是用来提高 AD 的驱动能力。

(c)图为 ADS5463 电路板，由射频端发送来的信号经过单路高速 AD 芯片转换为 12 位数字信号。

## 4.2 信号完整性分析

在本次高速系统的设计中，由于芯片工作频率很高，因此信号完整性问题需要作为一个重要问题进行处理。过孔、电源、差分信号布线等实际问题，都将关系到系统设计的成败。本节即进行信号完整性分析。

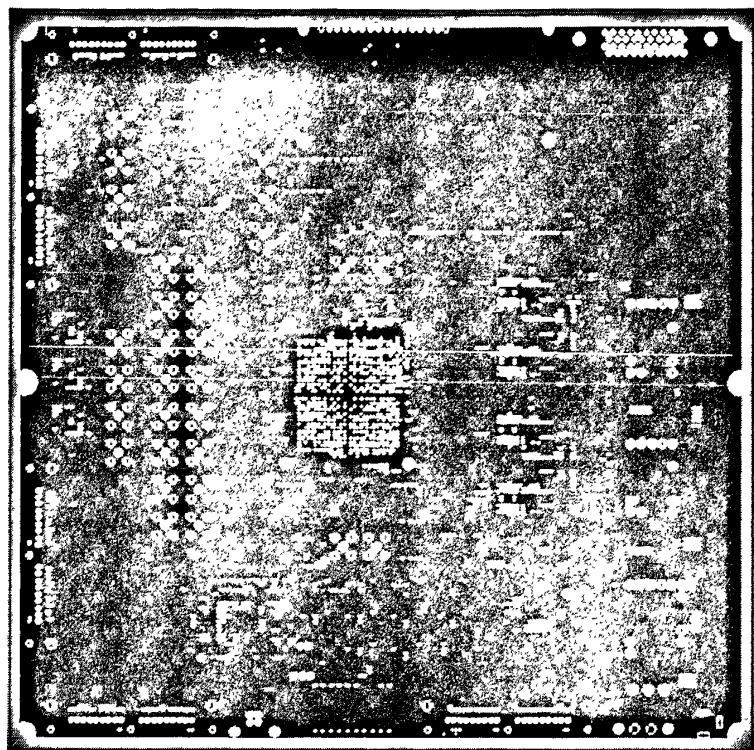

### 4.2.1 接地

在高速数字设计中，接地是否做的好直接关系到设计的成败。而接地主要由两个方式来实现，一是给出完整的地层，二是通过过孔。

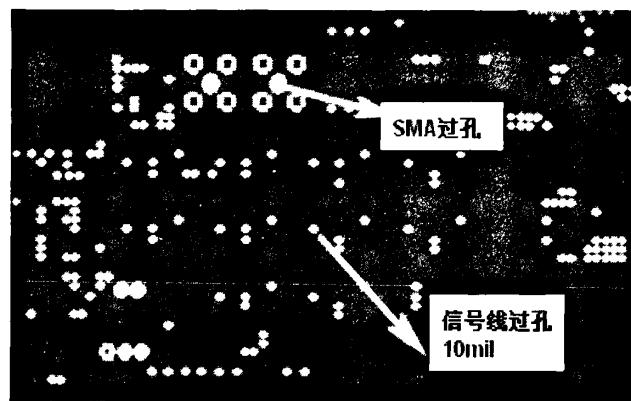

在本次硬件设计中，由于所使用到的很多芯片的工作频率比较高，如果过孔太大，这时高速信号上升时间将会变长，增加时延，因此在计算分布参数时，除了 PCB 线路以外，过孔问题也需要特别注意。因此在本次设计中，过孔也是需要考虑的重要因素<sup>[25]</sup>之一。

因为单位面积的布线和过孔较多，所以希望过孔越小越好，这样板上可以留

有更多的布线空间。此外，过孔越小，其自身的寄生电容也越小，更适合用于高速电路。但孔尺寸的减小同时带来了成本的增加，而且过孔的尺寸不可能无限制的减小。与此同时，如果过孔太小，则它带来的电感、电阻等参数会变大，使得信号不连续，会引起反射，综合考虑这些因素和信号线的线宽，设定信号线使用的过孔为 10mil。而对于其他类的特殊过孔，例如接插件等，需要按照实际尺寸测量。

下图是本 PCB 第二层地层上的过孔，考虑到 PCB 设计难度，本次设计都采用通孔。由下图 4-4 可见通孔的大小和密度不同，下文对过孔给 PCB 设计带来的寄生电容和寄生电感进行分析。

图 4-4 PCB 第二层地层局部

如图 4-4 所示，本次设计中的过孔主要分成如下两类，一是信号线的过孔，考虑到上文中提到的原则，设定为 10mil；二是设计中的接插件固定孔，例如 SMA，该过孔的尺寸是由具体部件的尺寸来决定的。

而从理论上分析，过孔在传输线上表现为阻抗出现不连续的断点，从而造成信号的反射。一般过孔的等效阻抗比传输线低 12%左右，对于差分线 50 欧姆的传输线在经过过孔时阻抗会减小 6 欧姆。但过孔阻抗不连续而造成的反射很小，其反射系数仅为： $(44-50)/(44+50)=0.06$ ，因此过孔产生的问题更多的集中于寄生电容和电感的影响。

同时，过孔本身存在着寄生的杂散电容，如果已知过孔在铺地层上的阻焊区直径为  $D_2$ ，过孔焊盘的直径为  $D_1$ ，PCB 板的厚度为  $T$ ，板基材介电常数为  $\epsilon$ ，则过孔的寄生电容大小近似于： $C=1.41\epsilon TD_1/(D_2-D_1)$ <sup>[26]</sup>。

过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间，降低了电路的速度。在本次设计中，厚度 60Mil，过孔焊盘直径为 15Mil（钻孔直径为 10Mils），阻焊区直径为 30Mil，则可以通过上述公式近似算出过孔的寄生电容是：

$$C=1.41*4.4*0.060*0.015/(0.030-0.015)=0.372\text{pF} \quad \text{式(4-1)}$$

这部分电容引起的上升时间变化量大致为：

$$T_{10-90}=2.2C(Z_0/2)=2.2*0.372*(50/2)=20.46\text{ps} \quad \text{式(4-2)}$$

从以上数值可知，一般单个过孔的寄生电容引起的上升延变缓的效用不是很明显，但是如果走线中多次使用过孔进行层间的切换，就会用到多个过孔，因此设计时要慎重考虑。实际操作中，可以通过增大过孔和铺铜区的距离（Anti-pad）或者减小焊盘的直径来减小寄生电容的影响。

过孔同时也存在着寄生电感，而在高速数字电路的设计中，过孔的寄生电感带来的危害往往大于寄生电容的影响。它的寄生串联电感会削弱旁路电容的贡献，减弱整个电源系统的滤波功用。下面的经验公式来简单地计算一个过孔近似的寄生电感：

$$L=5.08h[\ln(4h/d)+1] \quad \text{式(4-3)}$$

其中  $L$  指过孔的电感， $h$  是过孔的长度， $d$  是中心钻孔的直径。从式中可以看出，过孔的直径对电感的影响较小，而对电感影响最大的是过孔的长度。仍然采用上面的例子，可以计算出过孔的电感为：

$$L=5.08*0.060[\ln(4*0.060/0.010)+1]=1.218\text{nH} \quad \text{式(4-4)}$$

对于采样来说，假设信号上升时间是 1ns，那么其等效阻抗大小为：

$$XL=\pi L/T_{10-90}=3.83\Omega \quad \text{式(4-5)}$$

因此，这样的阻抗在有高频电流的通过已经不能够被忽略。特别要注意，旁路电容在连接电源层和地层的时候需要通过两个过孔，这样过孔的寄生电感会成倍增加。

#### 4.2.2 滤波

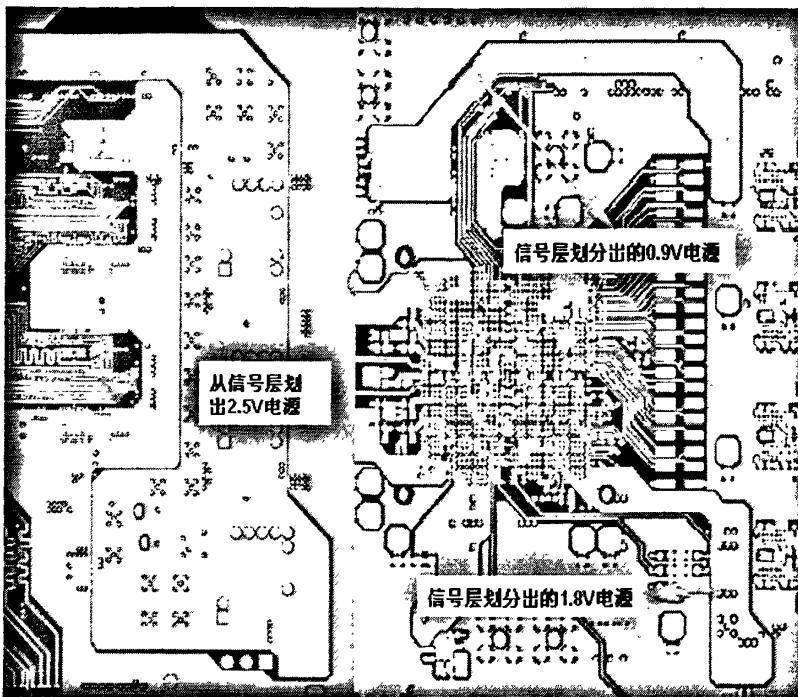

##### 1. 电源：

在 PCB 设计中，电源也是很重要的一部分。就本次设计而言，第 5 层与第 9 层被单独作为电源层。理论上来说，最好使用单独的平面来做电源层，但是由于设计中使用到的电源类型比较多，同时又不能每种电源都规定一个电源层，因

此在某些信号层也要根据要求，划分出一部分作为电源使用。

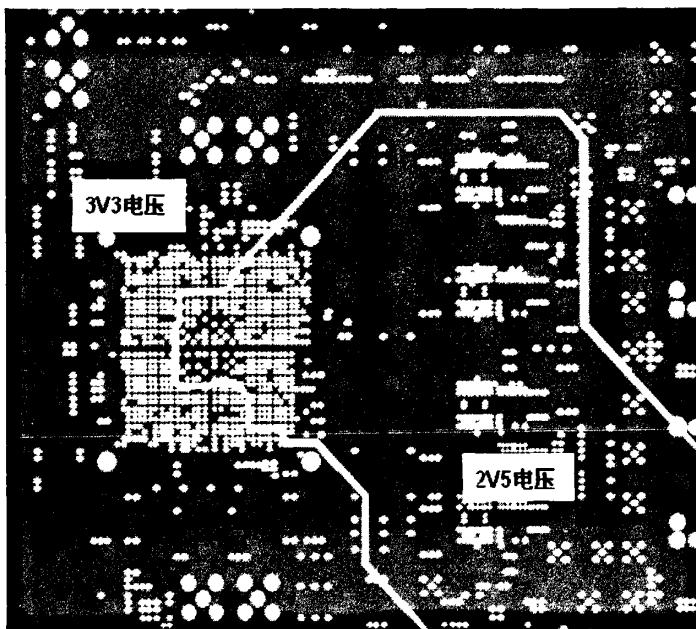

图 4-5 A. PCB 第 3 层电源划分 B. PCB 第 10 层电源划分

在本 PCB 设计中，由于功能模块比较多，因此用到的电源电压类型也比较丰富，包括 0.9V, 1.0V, 1.8V, 2.5V, 3.3V 等。在考虑信号完整性的前提下，电源也要保证完整性。因此如果条件允许，需尽可能多地使用整层敷铜作为电源层，这样首先可以保证表层器件需要接电源的时候可以通过直接打过孔来实现；其次可以使用整层电源可以为其邻层的信号线提供很好的参照，从而保证信号完整性。但考虑到多层板的成本等因素，电源层亦不宜过多，因此对于使用到最多的电压，例如 3.3V，可以使用一整层电源层，而对于使用到比较少的电压，可以考虑在一层上进行分割，即几个电压共用一个电源层。如本设计中的第 3 层与第 10 层信号层均画出一部分电源。但需要注意，同一层的两部分应该尽量保持一定的距离，以保证互相之间的独立性。

图 4-5 所示 A 图为第 3 层信号层划出的 2.5V 电源层，B 图为由第 10 层信号层划分出的电源。

图 4-6 为第九层电源层的分割情况。在该图中，对于该电源层，为能在同一层提供 3.3V 与 2.5V 电压，将其分成两部分来节约整块 PCB 的布板层数，但是

为保证电源完整性，划分出的电源须尽量实现平滑的过度。

同时，考虑到电源完整性的原则，尽可能地使得两部分电源不存在狭小的条状区间，因为只有电源平面足够大才能很好地保证电流的完整回流。如果单独划分出的电源太细的话，单位宽度流过的电流会过大，从而导致该电源铜面显示出的电感特性会比较明显，使得电源平面不能保证良好供电，进而影响硬件的正常工作。

图 4-6 第九层电源层的分割

## 2. 差分信号线：

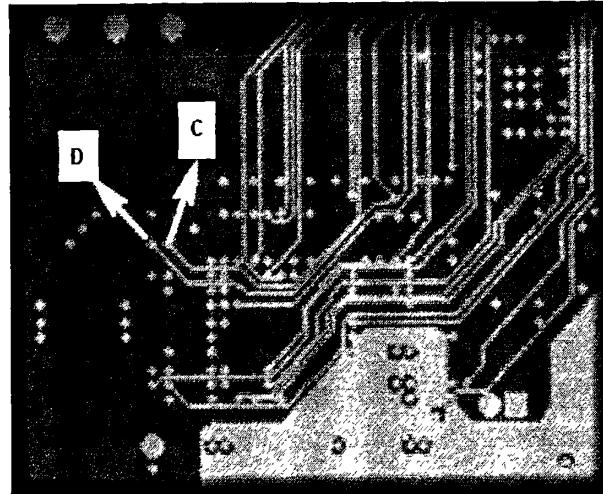

对于高速数据采集系统，电路的时钟信号和数据信号都大量地采用差分传输的技术。使用差分布线的原因是由于两路差分信号的电流回路不可能完全一致。这样就会产生一部分无法抵消的电流，即共模电流。共模电流会产生共模辐射，影响系统的电磁环境<sup>[27]</sup>。而在高速数字电路中，差分传输技术与单端传输技术相比具有电压浮动范围小、参考电平更好地控制、降低 EMI、不易受到串扰的影响、消耗功率少等诸多优点，因此在对高速信号布线中很多情况下考虑采用差分线，图 4-6 所示为第七层信号层的布线局部。

图 4-7 所示为从 FPGA 到 AD9627 接口部分的一对差分线，A 线和 B 线。由于相对 B 线来说 A 线从 FPGA 相应 I/O 口到焊盘的距离相对较长，因此在接入

到 B 线相连的焊盘之前，走差分线来使得两根信号线等长。因为如果不能保证信号线等长的话，当 B 线来的信号已经进入 FPGA 时，A 线的信号还没有到达，这是会导致 FPGA 所接收到的数字信号出现混乱，从而不能正常通信。

图 4-7 第七层信号层

在差分布线的具体操作中，为了防止产生较大的共模电流，差分信号进行布线的时候必须遵照如下原则<sup>[28]</sup>：

- 1) 理论上，两条信号线相互之间的长度差必须控制在信号上升沿时间的电气长度的 20% 以内，在实际布线中尽量保证信号线平行和等长，例如在图 4-7 所示的布线过程中，在使用 Cadence 进行线长的测量，时时保证线长两条线的长度一致，长度差不超过 50mil；

- 2) 差分信号的两条信号线在走线的时候，尽量保证在同一个布线层内，因为跨层布线会使得过孔增加额外的干扰，如图 4-7 所示，只要能够在一个布线层完成布线，尽量不将同一芯片的差分线布设在不同信号层；

- 3) 如果在同层信号线不能完成布线，则需要切换布线层，此时要求两条信号线在相同的位置通过过孔切换到另一个布线层，也就是说必须使得每一层的信号线都等长。如图 4-7 所示，C、D 两条信号线都是由 FPGA 到 ADS5463 接口的信号线，由于该层信号线无法在同一层完成布线，因此在 C、D 所示位置打孔在另外一个信号层完成信号线的布设。此时要注意，从 FPGA 相应 BANK 的 I/O 接口到 C、D 点的线长必须是相同长度的，同样要在 Cadence 布线中测量相应信号线的长度；

图 4-8 第七层信号层

为防止差分信号对邻近信号线的干扰，要求差分信号与邻近信号线的间距大于三倍的线宽，同时任意两对差分线也尽量保持距离，而同一对差分线的线宽则应当保持距离尽量小。

另外，还需要注意对差分信号传输线同样需要进行阻抗匹配。如果差分信号线的长度大于信号的电气长度，那么相同的阻抗匹配措施可以用于差分信号线上。但是对于一个纯粹的差分信号，可以在两条信号线之间端接一个电阻，同样可以起到阻抗匹配的作用，其中该电阻的阻值是传输线的特征阻抗。对于本设计，单线的特征阻抗为 50 欧姆，因而差分阻抗为 100 欧姆。

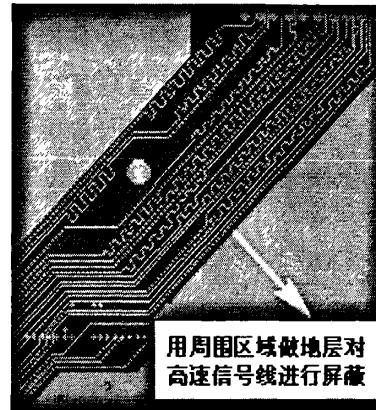

#### 4.2.3 屏蔽

对于高速电路设计来说，屏蔽也是非常重要的因素。因为如果屏蔽做的不好，各个高速信号线之间的干扰会比较大。因此经常考虑对重要的信号线采用单独的布线层进行走线，以取得较好的屏蔽效果。

在本课题中，高速数字信号的陡峭的上下沿会对其周围信号产生干扰，需要进行屏蔽。例如，如果屏蔽做得不好，本次设计中的 DDR2、时钟信号、数据和控制信息则不能有效到达，从而会影响存储和其他功能模块的正常工作。同时，考虑将接收通路和发射通路分开进行屏蔽，防止互相干扰。

如图 4-9 所示，由 FPGA 送往低速 ADC 的高速信号，采用将其周围区域设置为整个的地层的方式，对该信号线进行屏蔽。

除此之外，如果不能做到单独布线，则对比较重要的信号线进行隔离的同时，要在旁边加上“过孔屏蔽墙”，具体排列方式是：（1）两排过孔相互交错；（2）同一排过孔间距小于波长的  $1/20$ 。

图 4-9 用地层对高速信号线屏蔽

### 4.3 本章小节

本章主要针对在 PCB 设计过程中所遇到的各种实际问题进行详细描述，包括布局、分层策略以及布线方式等。对于线宽、过孔、电源、接地等方面，需要在考虑信号完整性的基础上进行设计。在具体的 PCB 设计中，主要分析了信号完整性原则在各个设计环节中的体现，给出了硬件平台实物。平台的整体布局、布线中的各种准则，以及考虑信号完整性原则等也体现了本课题的相应理论分析与实际操作。

## 第五章 系统功能模块调试

### 5.1 系统模块

对于硬件电路设计，在完成焊接工作后的调试极为重要。在此过程中，不仅需要调通电路，保证板子的各个组成部分正常工作，而且各模块的性能参数也需要加以验证。数字基带电路板各功能模块如图 5-1 所示。

图 5-1 数字基带平台各模块实物图

图 5-1 是本设计的主要硬件板图。其中主要包括核心处理器 FPGA、电源组件、两组 32 位 DDR2 SDRAM，USB 控制器、时钟以及 AD/DA 接口。

## 5.2 模块调试

下面对硬件平台的各个模块的调试工作分别作介绍。在实际的硬件开发过程中，硬件的调试工作非常重要，而且需要经验的积累。因此不仅要求熟悉各个硬件模块的原理和电路，同时要有较多实践经验。下面对如下几个模块的调试做详细介绍，其包括电源模块、FPGA、低速 AD 模块、存储模块、USB 接口模块，时钟模块以及高速 ADC、DAC 模块。

### 5.2.1 电源模块调试

图 5-2 电源模块部分

电源模块能否正常工作，直接决定了系统是否能够正常工作。图 5-2 是整个电路板的电源部分，参照上文中的原理图，对各个电压进行测试和调试，如果遇到有虚焊和连接错误的情况，需及时修证，以免影响到后端电路的正常工作。下表所展示的是在进行了调试之后的各个关键元件的电压值，其中只要偏差在合理范围之内，就可以给整块电路板正常供电。

表 5-1 电源模块调试结果

| 元件号 | 型号         | 理论值  | 实际测试值 |

|-----|------------|------|-------|

| U2  | PTH08T240W | 3.3V | 3.25V |

| U3  | PTH08T220W | 1.0V | 1.1V  |

|     |             |      |       |

|-----|-------------|------|-------|

| U5  | PTH08T240W  | 1.8V | 1.69V |

| U15 | TPS74401    | 2.5V | 2.3V  |

| U6  | TPS74401    | 2.5V | 2.35V |

| U7  | TPS51100DGQ | 0.9V | 0.9V  |

| U14 | TPS51100DGQ | 0.9V | 0.85V |

| U16 | ADP3334     | 2.5V | 2.5V  |

| U17 | ADP3334     | 2.5V | 2.43V |

## 5.2.2 FPGA 调试

### 1. 调试工具 ISE 简介

在 FPGA 调试过程中使用到 ISE 软件，现对其做简单介绍。

ISE 是由 Xilinx 所提供的集成综合开发环境的简称，其集成的工具可以完成整个 FPGA/CPLD 的开发及测试过程。

ISE 的主要特点是：

(1) ISE 是一个集成环境，可以完成整个 FPGA/CPLD 开发过程。它集成了许多著名的 FPGA/CPLD 设计工具，能够提供真正的与结构无关的设计环境和强有力逻辑综合能力；

(2) ISE 界面风格简洁流畅，易学易用。该界面秉承了可视化编程技术，界面根据设计流程而组织，整个设计过程只需要按照界面组织结构依次点击相应的按钮或选择相应的选项即可；

(3) ISE 有丰富的在线帮助信息，结合 Xilinx 公司的技术支持网站，一般设计过程中可能遇到的问题都能得到很好的解决；

(4) ISE 秉承了 Xilinx 设计软件强大的辅助功能。在编写代码时可以使用编写向导生成文件头和模块框架，也可以使用语言模板(LanguageTemplates)帮助编写代码。另外，ISE 的 CoreGenerator 工具可以方便的生成 IP 核(IP Core)与高效模块为用户所用，大大减少设计者的工作量，提高了设计效率和质量；

(5) ISE 可以与其他工业标准设计的输入、综合工具链接。设计者可以使用 ISE 自身集成的仿真工具进行仿真，也可以使用第三方的 EDA 工具来仿真。ISE 具有良好的数据互换性，支持 Synplify<sup>[29]</sup>等著名的综合软件。

## 2. FPGA 配置方式

Xilinx 为终端用户提供了配置 Virtex-5 FPGA 所需的灵活性。Virtex-5 FPGA 支持以下几种配置方式：主串行、从串行、主 SPI、主并行、从并行及主 BPI。其中，前三种配置方式又可总结为串行，后三种方式都是并行方式配置。配置中的“主”“从”都是以 FPGA 为中心的说法，因为配置时是将配置芯片中的数据导入到 FPGA。两个芯片之间需要同步时钟，如果这个配置时钟是从 FPGA 发到配置芯片以达到二者之间的同步，那么这种方式就叫“主”方式；反之，如果配置时，两者间同步时钟是从配置芯片发到 FPGA，那么这种就是“从”方式。对于配置方式的选择，当需要考虑引脚数目时，会涉及到“串”或者“并”的问题，而“主”“从”选择在本设计中都可以。

## 3. 硬件编程流程

本节介绍 ISE 软件中的硬件编程流程，详细的配置电路原理以及软件配置参数则不做具体讨论。

- (1) 生成编程文件在 ISE 中的操作非常简单，在过程管理区中双击 Generate Programming File 选项即可完成，生成的编程文件放在 ISE 工程目录下，是一个扩展名为.bit 的位流文件。

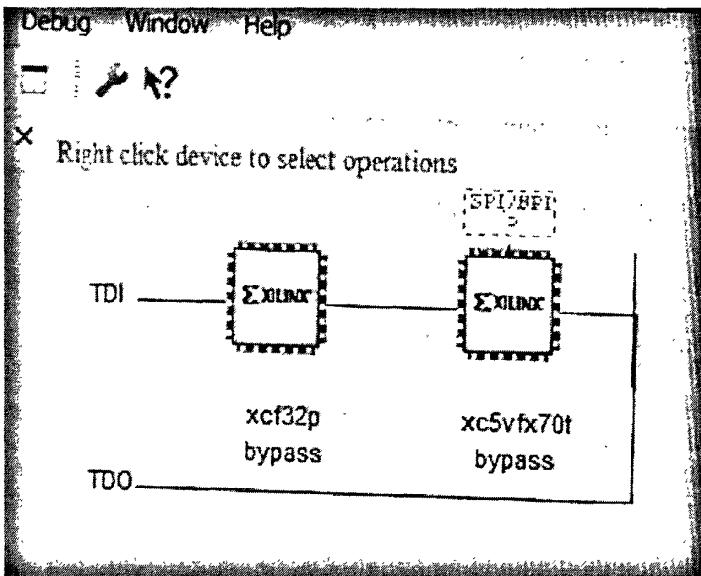

- (2) 完成下载。生成二进制比特文件并下载至芯片是 FPGA 设计的最后一步。双击过程管理区的 Generate Programming File 选项下的 Configure Device (iMPACT) 项，在弹出的 Configure Device 对话框中选取合适的下载方式，ISE 会自动连接 FPGA 设备。成功检测到设备后，会出现如图 5-3 所示的 iMPACT 的主界面。点击 Program 选项，就可以对 FPGA 设备进行硬件编程。配置成功后，会弹出配置成功的界面。

至此，就完成了一个完整的 FPGA 设计流程。ISE 的功能十分强大，以上介绍只是其中最基本的操作，更多的内容和操作<sup>[30]</sup>需要读者在大量的实际实践中来熟悉。

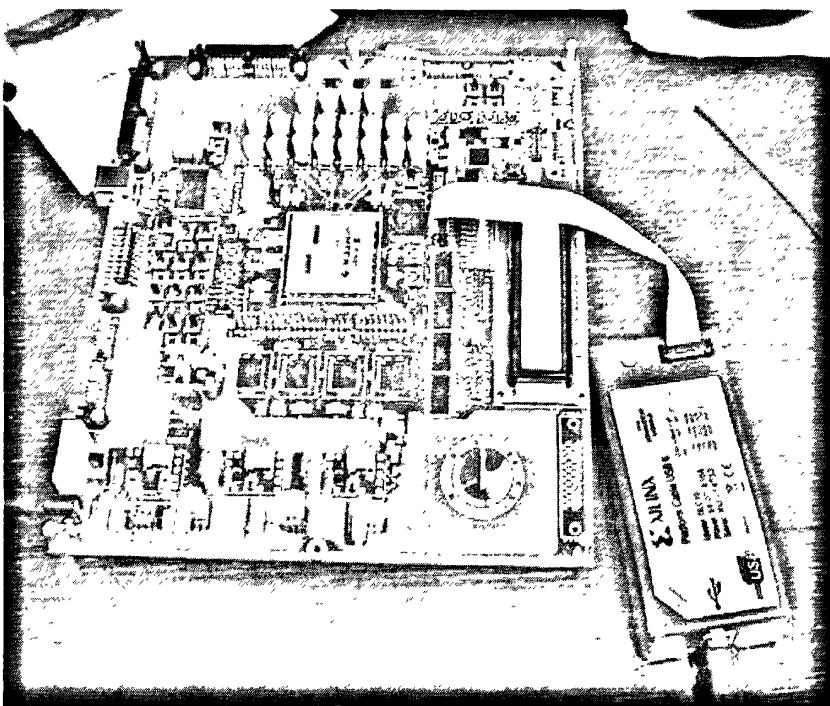

FPGA 的下载连接方式如图 5-3 及图 5-4 所示。

### 5.2.3 低速 AD 调试

对于低速 AD9627 的调试，使用的调试工具为信号源、示波器和频谱分析仪。

信号源用来提供所需要频率的输入信号，示波器用来测试输出信号波形，而逻辑分析仪则用来读取经过 AD 采样后的信号，对其进行分析。

图 5-3 电脑显示界面

图 5-4 连接方式

图 5-5 是当没有时钟输入时，信号源连接至 AD 的输入信号波形。选择输入信号频率 2M。对于更高频率的输入信号，原理是类似的。当时钟接入时，该波形图产生了一定的毛刺，这时需要对电路板设计过程中的信号完整性原则特别注

意，否则时钟输入会引入干扰。

图 5-5 AD 输入波形显示

图 5-6 测试结果图示

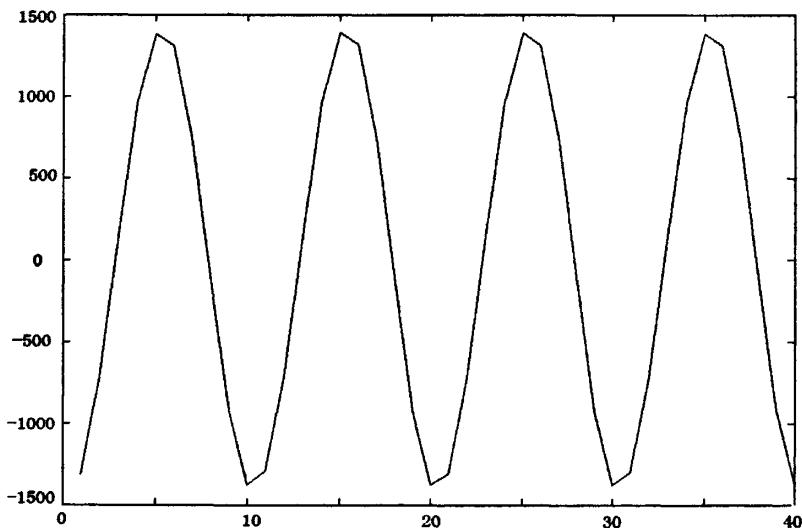

图 5-6 显示的是信号的采样结果，从 AD9627 的输出端采集 4 个周期（每周期采集 10 点）绘制而成的波形图。可以看出其波形在每个周期内基本与模拟信号波形相同，因此证明 AD 工作正常。

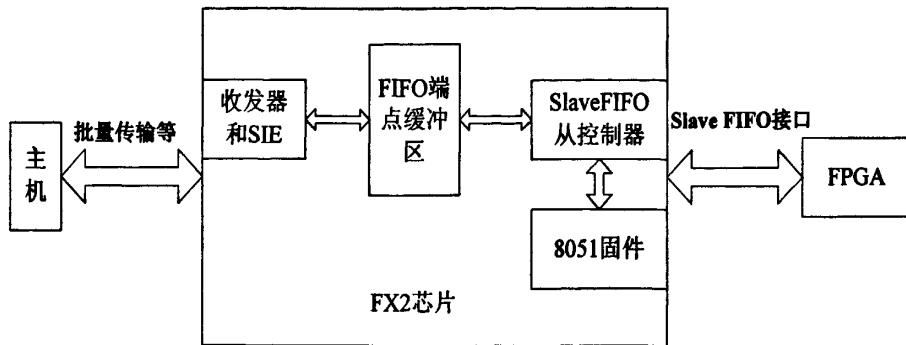

#### 5.2.4 DDR2 读写仿真

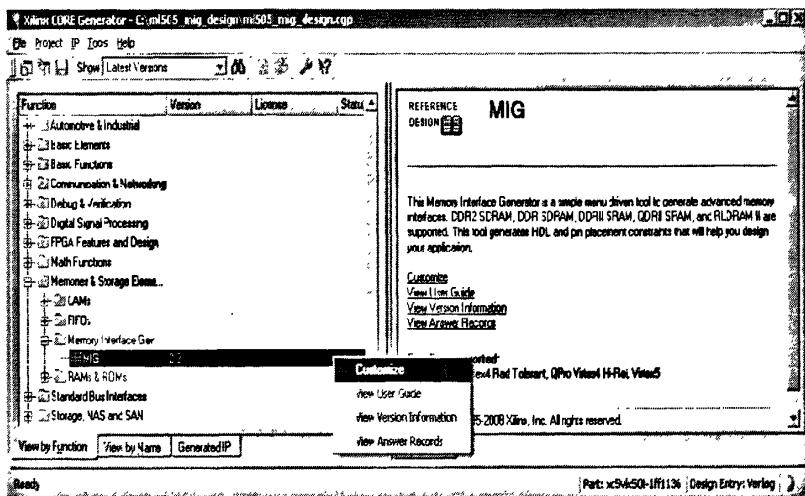

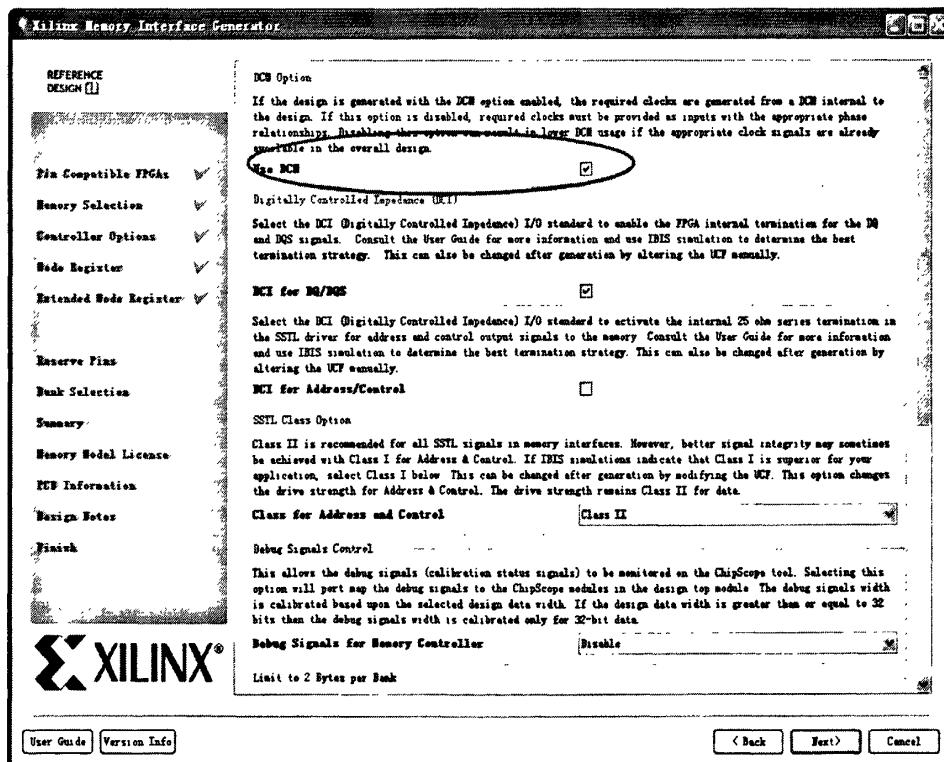

对于 DDR 控制器的实现来说, Xilinx 公司提供的 IP 核生成器 CORE Generator 中集成了存储器接口生成器 MIG 工具, 其可以直接生成 DDR2 控制器设计模块<sup>[31]</sup>。经过相应的修改可以应用到系统中, 从而大大缩短了系统的设计开发周期。MIG 界面如图 5-7 所示。

图 5-7 MIG 操作页面

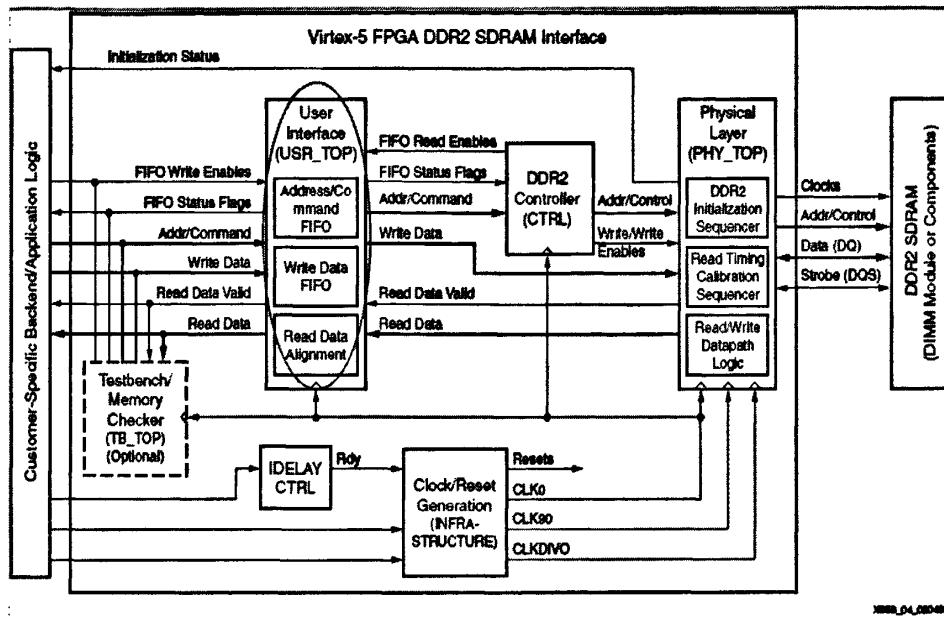

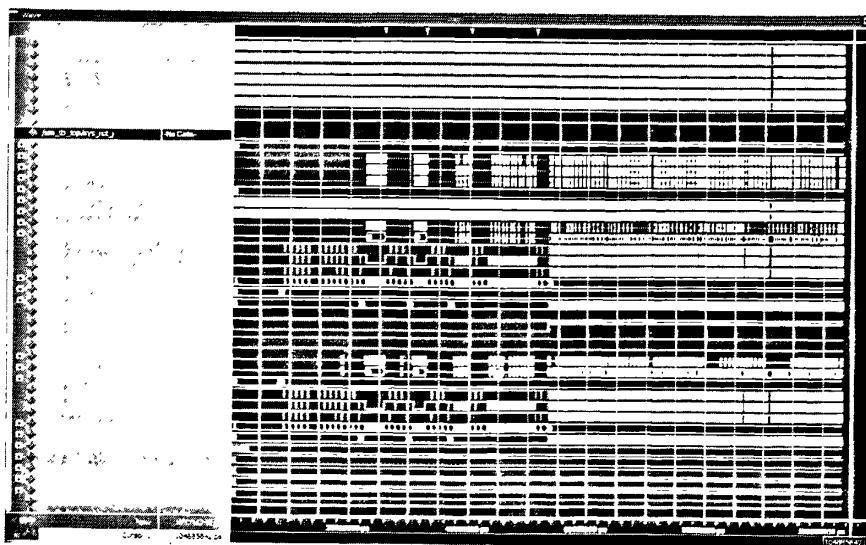

用户可以在 MIG 软件中根据所选用的存储器件型号选择相应的模板、总线宽度和速度级别, 并设置 CAS 延迟、突发长度、引脚分配等关键参数。而 MIG 即可生成控制器的 HDL 代码和约束文件。本系统以 MIG2.2 自动生成的测试模块为基础, 做相应的修改后用于本设计的硬件验证。控制器模块向 DDR2 存储器发出一系统的写入命令和读回命令, 同时在 FPGA 内部产生相应的数据和地址, 并对写入数据和读回数据进行比较, 通过比较信号(error)验证控制器的正确与否。当检测出读写信号相同时该信号为低电平。使用 Modelsim 工具对读/写指令进行时序仿真, 读写比较信号(error)在检测到读写数据相等时输出低电平。

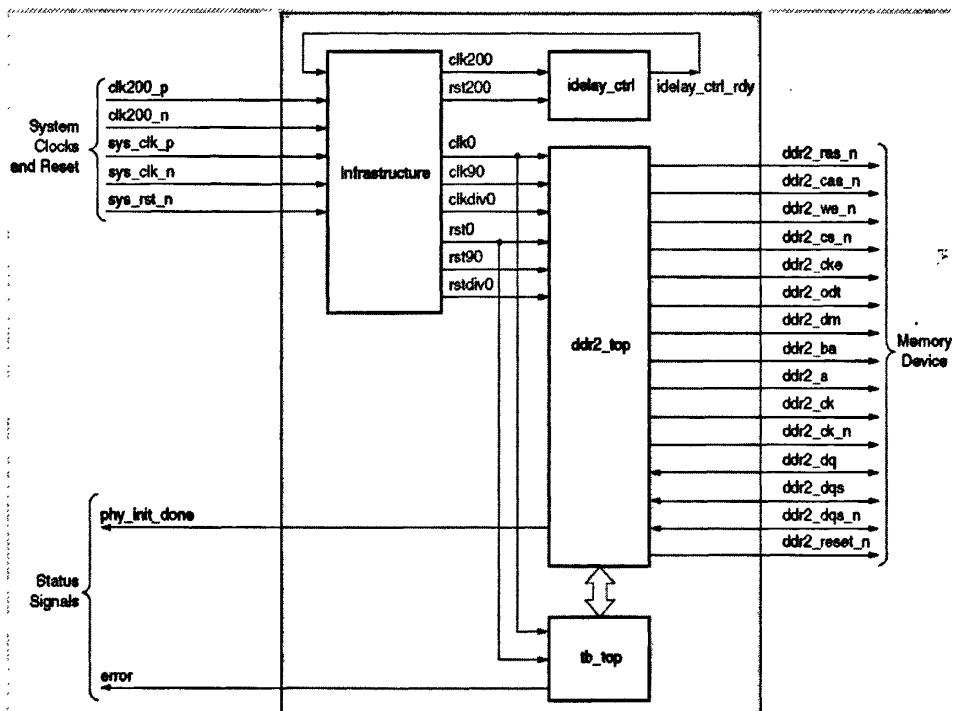

DDR2 控制器的整体结构如图 5-8 所示。其中输入的时钟可以使差分或者单端。如果选择差分, 则时钟接口为 sys\_clk\_p, sys\_clk\_n, clk\_200\_p, and clk\_200\_n; 而如果选择单端, 则时钟接口为 sys\_clk 和 idly\_clk\_200。

用户可以通过使用 DCM 来产生输入频率的移相, 分频等操作以满足 DDR2 控制器各个部分对时钟的需求。DCM 的配置如图 5-9 所示。

如果使用了 DCM, 则 MIG 最后会生成结构控制器, 如图 5-10 所示。其包含两种情况, 即包含 testbench 及不包含 testbench 的情况。

图 5-8 DDR2 控制器的整体结构图<sup>[32]</sup>

图 5-9 DCM 设置示意图

- (1) 包含 testbench: DDR2 控制器的用户接口都接到 testbench 上, 有 testbench 控制进行 DDR2 的读写等操作, 只通过引脚 phy\_init\_done

指示初始化已完成，error 引脚指示读写数据对比有无差错，在 MIG 生成文件的\example\_design\rtl 目录下包含了 testbench 文件及整个 DDR2 控制器模块源代码。

- (2) 不包含 testbench 的情况：DDR2 用户接口均接到 DDR2 控制器的最外端，有用户另外编写程序操作这些接口实现对 DDR2 的读写，方便讲 DDR2 控制器集成到整个系统工程中。在 MIG 生成文件的\user\_design\rtl 目录下包含了除 testbench 以外的 DDR2 控制器模块源代码。

图 5-10 DDR2 内部结构示意图<sup>[33]</sup>

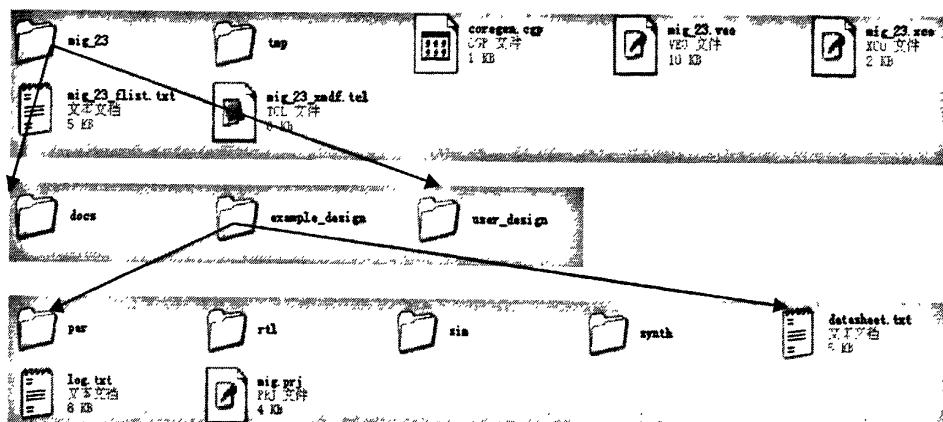

对于 MIG 生成的文件，MIG 中填写的 component name 为 mig\_23，则生成的目录位置如图 5-11 所示。

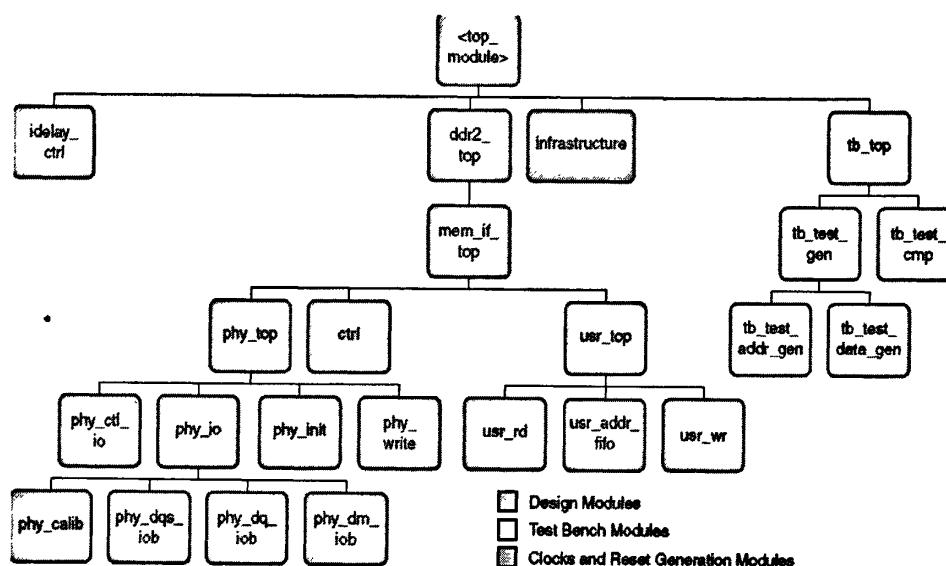

User\_design 和 Example\_design 基本内容一致，只是 Example\_design 包含了 testbench，而 user\_design 没有。rtl 文件夹包含了所有的源文件，整个结构如图 5-12 所示。其中<top\_module>即为 ddr2\_sram.v，而其他文件均加了 ddr2\_前缀。

在 par 文件夹下还生成了 ddr2\_sram.ucf 文件（用户约束文件），需要加到整个工程中。在 sim 文件夹生成了 ddr2\_model.v 文件，该文件即为所选器件的 verilog

图 5-11 MIG 所生成文件结构图

图 5-12 文件结构图

图 5-13 DDR2 读写仿真结果

语言描述，其可用于仿真。

图 5-13 所示是 DDR2 SDRAM 的读写时序结果。通过对该图分析可知，DDR2 SDRAM 时序正常，工作频率可以到达 266MHz，符合预期设计目标。

### 5.2.5 USB 读写方式配置

本次设计中的 USB 接口主要是为了能够将接收到的数据上传到 PC 上进行数据分析，以验证各模块通信数据的正确性。

USB 接口的数据传输模式分成不同种类，而在本文中使用典型的数据传输模式。EZ-USB FX2LP 的 Slave FIFO 模式主要用于 USB 数据的传输。按同步方式可以分为同步传输模式和异步传输模式；按数据传输的方向，可以分为 Slave FIFO 写和 Slave FIFO 读两种。这里需要主要的是，“读”和“写”都是从外部逻辑的角度来看的。下面分别进行介绍各种传输模式。

#### 1. 同步 Slave FIFO 写

图 5-14 同步 Slave FIFO 写接口

EZ-USB 和外部微处理器之间进行同步 Slave FIFO 写的典型接口。其中，同步时钟为 IFCLK 引脚，FD 为数据总线。外部微处理器控制 FIFOADR[1: 0] 引脚、SLWR 引脚和 PKTEND 引脚，同时可以读取 EZ-USB 的 FIFO FULL 和 EMPTY 标志，同步写接口的电路连接逻辑如图 5-14 所示。

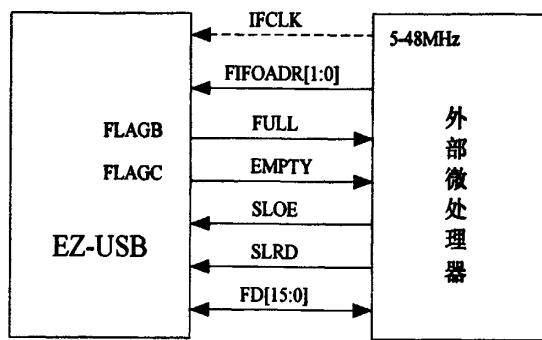

#### 2. 同步 Slave FIFO 读

EZ-USB 和外部微处理器之间进行同步 Slave FIFO 读的典型接口。其中，同步时钟为 IFCLK 引脚，FD 为数据总线。外部微处理器控制 FIFOADR[1: 0] 引脚、SLOE 引脚和 SLRD 引脚，同时可以读取 EZ-USB 的 FIFO FULL 和 EMPTY 标志，同步读接口的电路原理图如图 5-15 所示。

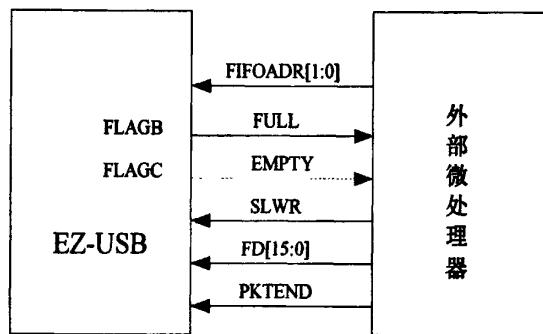

#### 3. 异步 Slave FIFO 写

图 5-15 同步 Slave FIFO 读接口

EZ-USB 和外部微处理器之间进行异步 Slave FIFO 写的典型接口。其中，数据写时钟由 SLWR 引脚来实现，FD 为数据总线。外部微处理器控制 FIFOADR[1:0]引脚和 PKTEND 引脚，同时可以读取 EZ-USB 的 FIFO FULL 和 EMPTY 标志。异步写接口的控制逻辑如图 5-16 所示。

图 5-16 异步 Slave FIFO 写接口

#### 4. 异步 Slave FIFO 读

EZ-USB 和外部微处理器之间进行异步 Slave FIFO 读的典型接口。其中，数据读时钟由 SLRD 引脚来实现，FD 为数据总线。外部微处理器控制 FIFOADR[1:0]引脚、SLOE 引脚和 SLRD 引脚，同时可以读取 EZ-USB 的 FIFO

图 5-17 异步 Slave FIFO 读接口

FULL 和 EMPTY 标志<sup>[39]</sup>，异步读接口的电路控制逻辑如图 5-17 所示。

本次 USB 接口设计主要考虑这两种读写方式。在电路连接正常的情况下，需要用软件实现不同的控制逻辑，从而决定使用何种读写方式，之后可以通过性能测试来判断两种读写方式的优劣，从而选择较为合适的方式进行配置<sup>[34]</sup>。对于此 USB 电路，经过电压测试可知，硬件电路工作正常。

### 5.3 本章小节

本章的主要内容是对所设计硬件平台的各个功能模块进行性能测试和电路调试工作，对调试过程中涉及到的相应软件进行了详细的介绍并给出调试结果。其中包括电源模块、FPGA、低速 AD 模块、存储模块、USB 接口模块等。经测试硬件接口及各模块工作正常。

## 第六章 结论

### 6.1 论文工作总结

本硕士论文主要完成了面向 IMT-Advanced 系统数字预失真硬件平台的设计和调试工作。其具体包括硬件平台的整体规划设计、芯片选型论证、电路原理图设计、PCB 高速板的设计、各个模块的调试等主要工作。

首先，在考虑到系统要求 100M 带宽的前提下，优选各个主要功能器件：1) ADC 选型。综合考虑采样定理及高阶采样的因素优选 ADS5463 作为高速 AD 芯片，而选取 AD9627 作为低速 AD 芯片；2) DAC 选型。依据转换速率、多倍插值、位数等具体要求优选 DAC5628 芯片；3) FPGA 选型。由于需要处理的数据量大、要求接口丰富，选择 Xilinx V5 作为主要处理芯片；4) 根据系统各个模块的工作要求，完成时钟、USB 等芯片的选型。本论文根据电路设计的一般原理和不同芯片的具体设计要求，完成各模块的原理图设计。

其次，本文对 PCB 版图进行设计。由于本文使用的 FPGA 管脚较多，需要对各个功能模块的布局进行优化。同时 AD、DA 需要用多对差分线进行布线，以完成高速信号的传输。在考虑到避免信号之间相互干扰的前提下完成了 PCB 分层以及高速信号线的布线工作。对于电路板的分层问题，在考虑电源、地层划分的前提下，最终选择采用 10 层板。同时在信号完整性分析相关理论的基础上，过孔、接地、电源、差分信号布线等问题进行了讨论。

最后，本论文完成硬件平台的整体设计及模块调试：1) 电源模块调试。测试输出电压基本满足系统要求；2) FPGA 配置调试。FPGA 可以正常工作；3) 低速 AD 的功能调试。测试结果表明该模块工作正常；4) 对 DDR2 进行了读写仿真。仿真结果显示存储模块工作正常，且满足系统的指标要求。

综上所述，本系统中各模块可正常工作，本论文所设计的基于 IMT-Advanced 收发系统的预失真硬件平台，其具有高速的处理性能、广泛的通用性和深度的可扩展性，并可较好地实现信号的线性放大，从而为高速、大容量通信双方提供可靠的物理层信号放大机制。

### 6.2 工作展望

近年来 IMT-Advanced 技术正进入一个高速发展的阶段，相对应的标准也在不断完善中，在今后必然会被广泛地应用于提供更大带宽的通信服务。因此，当

前在这个领域的研究工作具有十分重要的意义。本文初步比较完整地实现了一套基于 IMT-Advanced 系统的数字预失真硬件平台，今后可继续对其功能进行扩展及特性的提升。

首先，在 FPGA 方面可以通过编程实现更强的功能；

其次，更新关键芯片，提升系统整体性能；

最后，提高模块集成度，避免由接插件带来的信号传输质量损耗。

## 致 谢

谨将本文献给所有关心和帮助过我的老师、同学和朋友们！

首先衷心感谢我的导师唐碧华老师，她在我攻读硕士学位期间给予我悉心的指导和无微不至的关怀。导师严谨的治学态度、扎实的理论知识和实事求是的作风在学习、研究过程中给了我很大的启发和帮助，使我受益匪浅。在此，本人再次向唐碧华老师致以最诚挚的谢意！同时，还要感谢刘元安老师、吴帆老师、黎淑兰老师、袁东明老师、谢东亮老师，他们在我的研究生学习和生活中都给予了大量的帮助和指导，给了我许多的启迪。

感谢吴帆、李娜师姐，刘鑫师兄在研究生期间对我的指导和帮助，他们扎实的理论水平和认真的研究态度给我树立了学习的榜样。感谢马亮、楼健全、曹祥盈、白云飞、高龙飞等同学，他们给了我大力的帮助和支持，在和他们的共同学习和讨论中，使我获得的许多有意义的启发。感谢邓建廷、金景镇、曾山清、黄波等师弟们，他们给我的研究工作提供了许多的帮助。

最后，要感谢我的父母及家人，正是因为他们的关爱、支持和鼓励，使得我能够顺利完成学业。我将会不断提高自己，在日后的工作中取得更大的成绩。

## 参考文献:

- [1] Background on IMT-Advanced. Radiocommunication Study Groups. 7 March 2008.

- [2] Ahmet Sekercioglu Y, Ivanovich M, Yegin A. A survey of MAC based QoS implementations for WiMAX networks[J]. Computer Networks. 2009, 53(14): 2517-2536.

- [3] Dahlman E, Parkvall S. Background of 3G evolution [J]. 2007: 3-15.

- [4] CARL WIJTING, KLAUS DOPPLER,. KEY TECHNOLOGIES FOR IMT-ADVANCED MOBILE COMMUNICATION SYSTEMS. IEEE Wireless Communications • June 2009

- [5] Jangheon Kim, Junghwan Moon. INVESTIGATION ON WIDEBAND DIGITAL FEEDBACK PREDISTORTION TECHNIQUE FOR MOBILE WiMAX MULTICARRIER APPLICATIONS. MICROWAVE AND OPTICAL TECHNOLOGY LETTERS. No. 12, December 2008.

- [6] Yasunori Suzuki Shoichi Narahashi. Wideband and Hihg Efficiency Feed-Forward Linear Power Amplifier for Base Stations. NTT DOCOMO Technical Journal Vol.11 No.1

- [7] Gao X, Zhang J, Zhang P. Indoor channel characteristics based on wideband MIMO measurements at 5.25 GHz[J]. The Journal of China Universities of Posts and Telecommunications. 2008, 15(4): 46-50.

- [8] Lehr W H, Chapin J M. On the Convergence of Wired and Wireless Access Network Architectures[J]. Information Economics and Policy. , In Press, Accepted Manuscript.

- [9] Kumar A. Spectrum For WiMAX Networks [J]. 2008: 263-298.

- [10] Akira Hashimoto,Hitoshi Yoshino,and Hiroyuki Atarashi. Roadmap of IMT-Advanced Development. IEEE microwave magazine. August 2008.

- [11] Zaid A. Shamsan and Tharek Abd. Rahman. IMT-ADVANCED COEXISTENCE METHOD WITH FIXED SERVICES IN DIFFERENT GEOGRAPHICAL AREAS AT 3500 MHz. EUROCON IEEE.2009.

- [12] M. O'Droma. Developments in Predistortion and Feedforward Adaptive Power Amplifier Linearisers. IEEE computer society. 2009.3.

- [13] Jaehyok Yi, Youngoo Yang, Myungkyu P. Analog Predistortion Linearizer for High-Power RF Amplifiers[J]. IEEE Transanctions on Microwave Theory and

- Techniques. 2000, 48(12): 2709-2713.

- [14] Bacioccola A, Cicconetti C, Eklund C, et al. IEEE 802.16: History, status and future trends[J]. Computer Communications. 2010, 33(2): 113-123.

- [15] Lee S, Lee Y, Jeong Y. Fully-automated adaptive analog predistortion power amplifier in WCDMA applications[J]. 2005 European Microwave Conference. 2005, 2(1017-1022).

- [16] K. Jay Miyahara. IMT-Advanced - Objective and Challenges. IEEE Communications Magazine . June 2009.

- [17] Lee B G, Kwak J H, Kim K Y, et al. Technical innovation and 3.5 mobile phone generation: Lessons from Korea[J]. Telecommunications Policy. , 33(5-6): 296-308.

- [18] J K, Muhonen, Kavehrad M. Look-up Table Techniques for Adaptive Digital Predistortion:A Development and Comparison [J]. IEEE Transactions on Vehicular Technology. 2000, 49(5): 1995-2001.

- [19] 万屹. IMT-Advanced 技术研究进展[J]. 信息技术与标准化. 2007(Z1).

- [20] Suh B, Choi J, Kim J. Design and performance analysis of hierarchical location management strategies for wireless mobile communication systems[J]. Computer Communications. 2000, 23(5-6): 550-560.

- [21] Tharek Abd. Rahman, Intersystem Interference Scenarios between Fixed and IMT-Advanced Services in Different Terrestrial Regions, IEEE computer society,2009

- [22] M. O'Droma1, E. Bertran2 ; Developments in Predistortion and Feedforward Adaptive Power Amplifier Linearisers ; .European Gallium Arsenide and Other Semiconductor Application Symposium, GAAS 2005.

- [23] 丁念刚. 实时多通道数字接收系统硬件及其数字前端实现研究. 电子科技大学. 2009.4.

- [24] Stefan Parkvall, Erik Dahlman. LTE-Advanced – Evolving LTE towards IMT-Advanced. IEEE microwave magazine (S1527-3342). 2005, 6(3): 54-61.

- [25] Akira Hashimoto, Hitoshi Yoshino,. Roadmap of IMT-Advanced development. IEEE microwave magazine , August 2008.

- [26] 刘烨铭. 高速多板系统信号完整性建模与仿真技术研究. 国防科技大学. 2007.11.

- [27] Mugen Peng and Wenbo Wang,. Technologies and Standards for TD-SCDMA Evolutions to IMT-Advanced. IEEE Communications Magazine . December 2009

- [28] Virtex-5 FPGA Packaging and Pinout Specification. January 19, 2009.

- [29] Marc Defossez. Virtex-5 FPGA Interface for Fujitsu Digital-to-Analog Converters with LVDS Inputs. May 6, 2008

- [30] Virtex-5 FPGA Data Sheet:DC and Switching Characteristics. February 6, 2009 [31] 唐友喜, 易新平, 邵士海. 新一代移动通信系统——IMT-Advanced 的特征[J]. 电子科技大学学报. 2008(02).

- [31] Weng Chuen, Highly Efficient and Highly Linear RF Power Amplifiers, Thesis Delft University of Technology, 2009

- [32] Martinez R, He D. The Role of IEEE Standardization in Next-Generation Radio and Dynamic Spectrum Access Developments [J]. 2009: 743-775.

## 硕士期间发表论文

马云峰, 唐碧华, 吴帆, “通信中可以采用的视频采集方式及应用场景小结”,

科技论文在线, 2009 年 7 月。(已录用)

## 附录

### 附录 A：部分电路原理图

## 附录 B：部分 PCB 层

BOTTOM 层的布局和走线

信号层 (Layer4) 的走线

第二层地层

第三层信号层