## 摘要

光盘存储技术在信息社会中发挥着越来越重要的作用，PDIC（Photodetector Integrated Circuit）是光盘存储系统光学头的关键元件之一。与传统混合集成的PDIC相比，单片光电集成的PDIC具有低成本、高性能的优势，现已成为硅基光电集成（OEIC）研究的一个热点。虽然全球绝大部分光学头生产厂商都在中国大陆，但PDIC芯片都依靠进口。相比国外，国内对于该技术的研究还处在起步阶段，因此研究单片光电集成的PDIC对于打破国外垄断、提高我国DVD光学头产业的整体技术水平及核心竞争力具有一定的积极意义。

商业化的BCD（Bipolar CMOS DMOS）工艺比标准CMOS工艺多了一个N型埋层，N型外延层中杂质掺杂浓度较低，利用这一特点可以构建P<sup>+</sup>/N型外延层/N阱埋层（类似PIN）结构的光电探测器。因此，本文采用低成本的0.5μm BCD工艺研制了用于DVD机的单片集成PDIC，主要的工作内容如下：

1. 从低成本角度出发，利用BCD工艺埋层的BN<sup>+</sup>特点设计了与工艺完全兼容的适合650nm波长的P<sup>+</sup>/N-EPI/BN<sup>+</sup>光电探测器，并给出一个完整的等效电路模型。

2. 设计了基于互补式自偏置差分放大器（CSDA）结构的三级负反馈跨阻放大器。为了提高负载能力设计了一个两级运放作为单位增益缓冲器。采用Spectre软件对负反馈跨阻放大器进行了仿真设计。

3. 为了抑制电源扰动对跨阻放大器的性能影响，设计了一种低压线性稳压器（LDO）。仿真结果表明其输出电压可达4.36V，有较好的电源抑制比。

4. 采用Cadence软件完成单片集成PDIC的版图设计，并在无锡华润上华流片加工。版图面积约981×1982μm<sup>2</sup>。

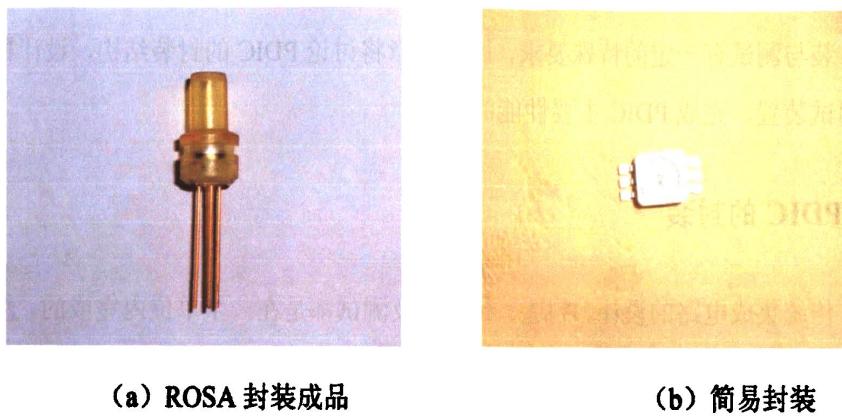

5. 根据实验室的测试条件对流片回来芯片进行了两种形式的封装，并做了具体的测试。测试结果：2.5V反向偏压下，PIN探测器结电容约为0.356PF，650nm波长的响应度约0.185A/W，PDIC中A~D部分的带宽65MHz左右，响应度为21.82 mV/μW~28.08mVu/μW；E、F部分的响应度为42.29mV/μW~47.31 mV/μW；输出失调电压均小于20 mV；功耗约130mw。所测指标均能达到设计要求。

本文在国内条件下采用低成本的标准BCD工艺自主完成了DVD光学头中

PDIC 的光电单片集成，研制过程中克服了 Si 基光电集成中的难题：

1. 成功解决 Si 基光电集成的难点---利用标准 BCD 工艺研制出高性能（高探测灵敏度，高传输速率）的 650nm 的硅基光探测器。

2. 自主建立了一种新的包含光电流、暗电流、结电容、并联和串联电阻、以及噪声特性在内的光电探测器完整的等效电路模型，实现 PD 与负反馈跨阻放大器(TIA, Transimpedance Amplifier)的协同设计。

3. 在电路设计中，充分考虑并解决了纵向结构的光探测器 PD 和横向结构电放大器 TIA 之间的结构、工艺兼容性问题；解决在光照下电子电路避免光信号干扰的问题。

**关键词：**单片集成 PDIC；PIN 光电探测器；跨阻放大器。

## Abstract

Optical data storage technologies are playing a more and more important role in modern information society. PDIC (Photodetector Integrated Circuit) is one of elements in optical pickup unit (OPU). Compared with hybrid integration, the monolithic integration of PDIC has advantages of low cost and high performance, which becomes a research hotspot of silicon-based OEIC. Most of OPU factories are in mainland China, but their PDIC chips all depend on importation. In present compared with abroad the studies of PDIC, those are still in start-up periods in our century. The research of monolithic PDIC will break the monopolization of oversea companies in this area, and improve the overall technical level and competitive energy of Chinese pickup industries.

The commercialized BCD (Bipolar CMOS DMOS) technology exists a N-type buried layer, by which P<sup>+</sup>/N-EPI/N buried layer structure of detectors with a similar characteristic of PIN photodetector can be realized. The doped concentration of N-type epitaxial layer is low. So this dissertation develops a monolithic PDIC for DVD machine by low cost BCD technology. Studies of this paper are listed as follows:

1. In order to get low cost PDIC, based on BN<sup>+</sup> layer of BCD technology the structure of P<sup>+</sup>/N-EPI/BN<sup>+</sup> for 650nm is designed. A whole circuit model of P<sup>+</sup>/N-EPI/BN<sup>+</sup> photodetector is established.

2. Based on CSDA three-stage negative feedback transimpedance amplifier (TIA) is designed. In order to improve load capacity, a buffer of unity gain amplifier composed of a two-stage amplifier is designed.

3. In order to suppress the power source perturbation to affect transimpedance amplifier's performance influence, a low dropout linear voltage regulator (LDO) is designed. Simulation results show that its output voltage reaches 4.36V and its PSRR is high.

4. With Cadence Virtuoso Layout Editor, the monolithic PDIC layout is completed, which area is about 981×1982 μm<sup>2</sup>.

5. Based on the condition of our own laboratory, two kinds of packaging structure are adopted. And the testing of PDIC is accomplished. Testing result show that at 2.5V reverse bias the capacitance of P<sup>+</sup>/N-EPI/BN<sup>+</sup> photodetector is about 0.356 PF, and its responsivity of 650nm is about 0.185A/W. The sensitivity of high-bandwidth part is from 21.82 to 28.08mV/μW, and that of high-gain part is from 42.29 to 47.31 mV/μW. The -3dB bandwidth of high-bandwidth part is about 65MHz. The output-offset voltage is less than 20mV. The power dissipation is about 130mW. Measured results meet design requirements.

A monolithic PDIC is designed based on low-cost standard BCD technology. Some difficulties of OEIC design are solved.

1. One of most difficult point about si-substrate OEIC is overcomed. Based on BCD technology, a high-peformance 650nm silicon-based photodiode is realized.

2. The full Spice equivalent circuit model of photodetector is established, which include photocurrent, dark current, junction capacitance, resistance and noise. The colla -borative design between PD and TIA is realized.

3. When IC designed, we considered fully and sovled the pobloem, which involves the structure and technology compatibility between vertical structure photodetector and horizontal structure TIA, and the signal interference caused by illumination.

**Keywords:** Monolithic PDIC; PIN Photodetector; Transimpedance Amplifier.

# 第一章 绪论

随着社会信息化的发展,光盘存储以其容量大、寿命长、成本低、复制速度快等显著优点已经成为现代社会信息存储的重要手段之一,而DVD (Digital Video Disc) 更是新一代数字视听技术和数字化信息存储设备的典型代表和潮流。它集计算机技术、光学记录技术和影视技术等为一体,其目的是满足人们对大存储容量、高性能的存储媒体的需求。PDIC (Photodiode Integrated Circuit) 是一种专门用于光盘存储系统光学读写头中的OEIC (Optoelectronic Integrated Circuit),是光学头的关键部件,信息检测都是通过PDIC来完成的。因此其品质优劣对光盘机的技术性能具有决定性的影响。

## 1.1 DVD 光学头技术概述

1982 年 Philips 公司发表红皮书确定了 CD 光盘的外观、尺寸、形状、信号的记录方式及相关产品的规格,从此光盘存储技术得到了飞速发展<sup>[1]</sup>。DVD 是为满足当人类社会大量信息的高密度存储要求,给人们以高品质视听享受而产生的一种新技术产品。1994 年 12 月 16 日,飞利浦公司和索尼公司公布了采用 MPEG-2 压缩标准的单面双层 12cm 高密度光盘 HDDC ( High Density Compact Disc) 的规范,使用 635nm 的激光器和数值孔径 0.52 的激光头。单面存储量提高到 3.7GB, 单面双层结构总容量达 7.4GB, 这也是第一次提出 DVD 技术规格<sup>[2]</sup>。1995 年 1 月 24 日,东芝、松下、先锋、日立、汤姆逊、美国音乐公司和米高梅影片公司等八大公司在洛杉矶共同宣布另一种具有竞争性超密度数字视盘 SDDVD (Super Dnesiyt Dihgal Vidoc Disc) 的规格使用 650nm 的激光器和数值孔径 0.6 的激光头,采用的是双层双面的存储结构,将两张厚度为 0.6mm 的信息盘片背靠背的粘接在一起,单面的容量为 5GB, 双面的容量达到 10GB<sup>[3]</sup>。

虽然红光 DVD 在存储的密度及读写速度方面和 CD 相比,已经有了长足的进步,然而业界依然没有放弃努力早已把目光投向蓝光技术。2002 年 2 月 19 以索尼、飞利浦和松下为核心联合日立、先锋、夏普、韩国三星、LG 及法国汤姆

逊共同发布了 0.9 版的 Blu-rayDisk (BD) 技术标准, 标志着蓝光光盘的诞生。蓝光 DVD 也是采用 MPEG-2 压缩标准, 单层蓝光 DVD 盘片的存储容量可达 27GB<sup>[4-6]</sup>。

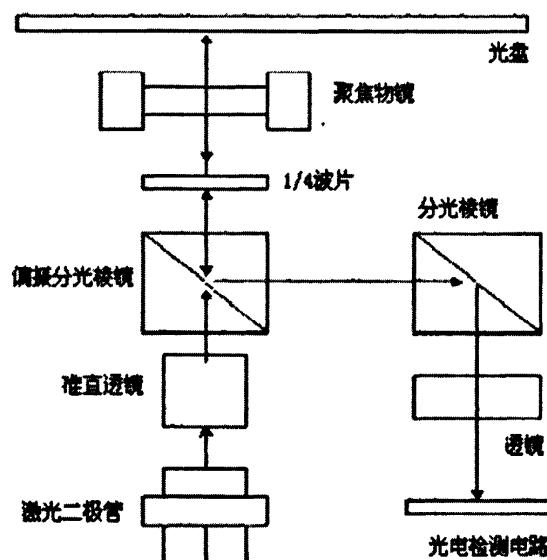

光盘存储技术, 是利用精细聚焦的激光束从模压而成的盘片上读取信息或进一步利用光对记录介质的物理或化学效应去改变介质的某些光学性能, 如对光的反射、吸收或相移等, 从而实现二值化数据的写入、读取与擦除。而光盘信息的读出和写入都要通过光学头来完成, 因此光学头是 DVD 光盘存储系统关键部分。光学头种类繁多, 读取不同的格式的光盘的光学头内部结构也各不相同, 不同公司生产的光学头也都有自己公司独特的结构。但主要还是由 DVD 激光二极管、光栅、光束分离元件、光电检测集成电路 (PDIC)、准直透镜及物镜等组成, 如图 1-1 所示。以下, 我们对光学头的各组成元件做简单的介绍<sup>[7][8]</sup>。

图 1-1 光学头示意图

(1) 激光二极管 (LD)。激光二极管是光学头的光源, CD 光学头用激光二极管的激光波长为 780nm, DVD 的为 650nm 或 635nm 而蓝光 DVD 为 405nm。激光光斑直径必须小于碟片的信迹之间的距离, 焦深范围必须小于信迹间距的 2 倍。否则, 即使寻迹伺服控制再好, 光斑始终落在信息中心, 由于光斑的边缘离相邻轨迹太近, 就会出现几帧同时读取的现象, 使画面周围有影坏现象。

(2) 准直透镜。准直透镜是一个平凸透镜, 作用是对激光束的发散角进行整形, 使发散光束通过透镜后可变为平行光束, 再进入物镜。

(3) 偏振分光棱镜和1/4波长。偏振分光棱镜和1/4波长组合成光束分离元件，所起的作用是避免射出光束与返回光束因共用光路而发生相互干涉并实现分离。

(4) 物镜。物镜是一种聚焦透镜，作用是把平行光束会聚于碟片的信息面上或是收集从光盘信号面上反射回来的光脉冲信号送入光电检测器。

(5) 光电检测电路 (PDIC)。光电检测电路基本作用是把从光盘信息层反射的光信号转换成电信号，是光头中的关键部件之一。以下章节将重点讲述这部分内容。

## 1.2 PDIC 的现状

随着信息社会的到来，作为尖端技术的微电子学领域，为了加快技术进步，不断的要求更多、更快、耗能更少的处理信息。在过去的发展中，电子器件逐渐小型化，处理速度高速化，而消耗电能越来越少。但是，随着技术要求日益提高，信息处理硬件的微细加工的极限开始显现出来，束缚了技术的日益发展。为了打破这种技术屏障，光电子技术成为首选。光电子技术将信息加在光波上，不断的开发光电信息处理技术<sup>[9]</sup>。

近年来出现的将光电器件与电子器件集成化的光电集成电路 (OEIC)，有效地缩小了器件的体积，大大减小了寄生效应的影响，提高了器件的性能和可靠性，并且大幅度地降低了批量生产的成本。光电集成的方式主要有两种即：混合集成和单片集成。混合集成是将各种光器件、电器件分别制在不同衬底上，然后通过焊接或其它连接方式组装起来，形成允许不同技术组合、不同衬底的光电混合集成模块。单片集成是将光电器件与微电子器件集成在同一片衬底上。相对于混合集成，单片集成具有以下优点<sup>[10]</sup>：

- (1) 器件间的互连线减小到最少，寄生参数得以减小，从而提高了器件的工作频率。

- (2) 由于减少了封装工序，易于大批量生产，大大降低器件生产成本和封装成本。

- (3) 单片集成 OEIC 还具有抗震动、整体性能好等优点。

而 PDIC 是一种专门用于光盘存储系统光学读写头中的 OEIC，是硅基 OEIC 研究的一个热点。单片集成硅基 PDIC 占据了光盘机光学读取头用光信号拾取部分的主流地位。

2001 年中国科学院半导体所梁恩主等人采用  $0.35\mu\text{m}$  CMOS 工艺研制了用于 DVD/VCD 的混合集成 PDIC，由六象限探测器阵列与电流模跨阻前置放大器采用键合技术组合而成，探测器的响应度可达  $0.370\text{A/W}$ ，暗电流可达  $0.16\text{nA}$ <sup>[11][12]</sup>。近年来，北京大学深圳研究生院集成微系统科学与工程重点实验室也有开展 PDIC 的研究<sup>[13][14]</sup>，但未见有测试结果报道。杭州士兰光电技术有限公司于 2005 年 8 月推出了 PDIC 产品 SM525<sup>[15]</sup>，该产品主要用于 CD 光盘机。09 年下半年又用该公司自己开发的 BiCMOS 工艺成功推出一款用于 DVD 的高性能 PDIC 芯片 SM626<sup>[16]</sup>，填补了国内 PDIC 的空白，如图 1-2 所示，但自定制工艺成本较高。2006 年本实验室卞剑涛博士采用低成本的 CMOS 工艺成功研制了用于 CD 光盘机的单片集成 PDIC，由六象限的  $\text{N}^+$ /N-Well/P-Sub 结构探测器阵列与跨阻前置放大器组合而成<sup>[17]</sup>。然而相比国外，国内对于 PDIC 的研究落后太多。

图 1-2 SM626 PDIC

国外的一些大型公司很早就对 PDIC 进行了大量的研究，而且技术都已经很成熟了，这些大公司包括松下、夏普、东芝、索尼、三星等。早期的产品主要采用双极型工艺<sup>[18-20]</sup>，而随着工艺技术发展 PDIC 一般采用 CMOS、BiCMOS 工<sup>[21-24]</sup>。根据各光学头制造厂家在不同的光路设计中采用的光学组件不同，光电探测器的几何图形也不一致，有四象限、六象限、八象限等等，但探测器的主流结构是 PIN

结构。而前置放大器主要利用负反馈跨阻型放大器 (Transimpedance Amplifier, TIA) 来实现。H.Zimmermann等人采用自定制CMOS或BiCMOS技术研制的PDIC，就光电探测器与前置放大电路部分提出了多种方案<sup>[25-27]</sup>。

表1.1为国外Si基PDIC光接收芯片的研究的简单对照。从表1.1可看出相比国内外内PDIC的研究落后很多还处于起步阶段。

表1.1 国内外PDIC的简单对照

|        | 参考文献<br>/产品型号          | 发表<br>时间  | 工 艺     | 主要指标                                                                                     | 适用<br>类型          |

|--------|------------------------|-----------|---------|------------------------------------------------------------------------------------------|-------------------|

| 国<br>内 | SM626A <sup>[15]</sup> | 2009<br>年 | BiCMOS  | 6PIN, 功耗 110mw, 650nm 响应度 28.5mV/ $\mu$ m, 宽为 8MHz                                       | DVD               |

|        | [17]                   | 2006<br>年 | CMOS    | 6N <sup>+</sup> /N-Well/P-Sub, 功耗约 50mw, 780 nm 响应度 31.17~42.47mV/uW                     | CD                |

|        | SM525A <sup>[16]</sup> | 2005<br>年 | Bipolar | 6PIN, 功耗 100mw, 780 nm 响应度 36 mV/ $\mu$ m, 带宽为 8MHz                                      | CD                |

|        | [11]                   | 2001<br>年 | CMOS    | 6PIN, 功耗约 200mw, 650nm、780nm 响应度分别为 33.4 mV/ $\mu$ W、11.9 mV/ $\mu$ W                    | VCD/<br>DVD       |

| 国<br>外 | [28]                   | 2009<br>年 | BiCMOS  | 405nm、5V 电压下响应度为 22mV/ $\mu$ W;<br>高频带宽 163MHz; 功耗 115mw                                 | HD-DVD/<br>DVD/CD |

|        | [24]                   | 2005<br>年 | BiCMOS  | 8PIN, 功耗 300mw, 650nm 相应度 100mV/ $\mu$ W, TIA 增益 130 $\Omega$ ~270K $\Omega$ , 带宽 260MHz | HD-DVD/<br>DVD/CD |

|        | [29]                   | 2003<br>年 | CMOS    | 4-背电极 PIN, 5V 供电功耗 53mw, 增益 24mV/ $\mu$ W, 带宽 147MHz                                     | DVD               |

|        | [30]                   | 2002<br>年 | BiCMOS  | 8-SP/BND/NW-PD, 5V 供电功耗 150 ~ 350mw, 带宽 250 MHz                                          | HD-DVD/<br>DVD/CD |

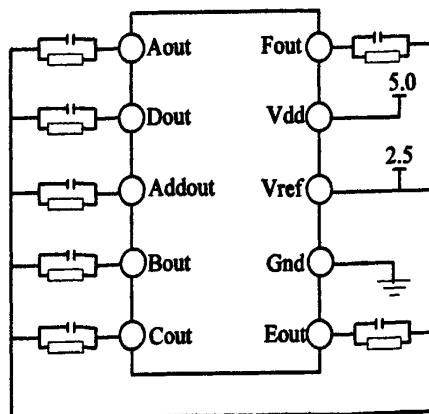

### 1.3 自制单片集成 PDIC 的设计

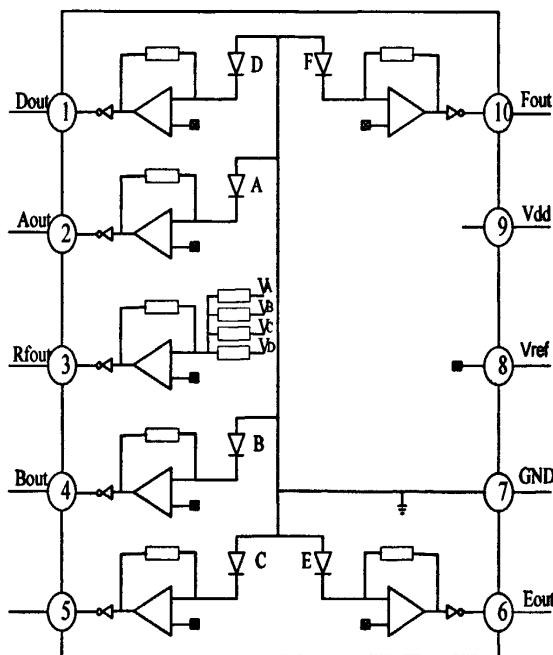

本文采用的是六象限光电探测器阵列的 PDIC，如图 1-3 所示。图中六个反偏连接的二极管分别表示光电探测器  $A \sim F$ 。其后紧跟着各光电探测器支路的电流-电压前置放大器。此外，还有求和运算放大器用于信号求和。 $A_{out} \sim F_{out}$  为各支路的电压输出； $V_{dd}$  和  $V_{ref}$  分别为电源电压和参考电压； $GND$  为信号地； $RF_{out}$  为读出射频信号，即  $RF_{out} = A_{out} + B_{out} + C_{out} + D_{out}$ 。

图 1-3 PDIC 示意图

#### 1.3.1 PDIC 的功能

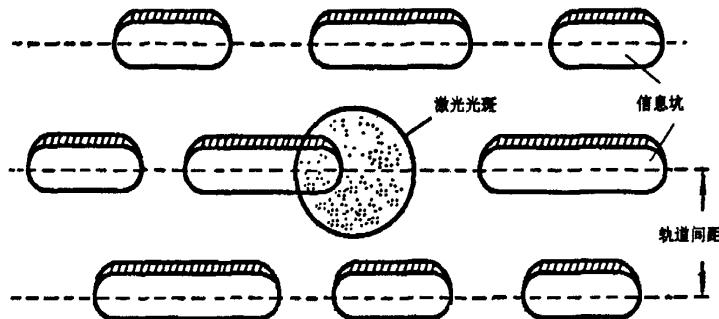

光盘是以沿螺旋形轨迹排列的不同长度的凹坑和间隔来表示信息内容的。对于DVD最小坑长 $0.4\mu m$ 、信息坑宽 $0.3\mu m$ 、螺旋轨迹间距 $0.74\mu m$ ，如图1-4所示。激光头从光盘上进行信息检测时，利用激光二极管发出的激光束经过一系列光学部件整形，包括光栅、准直透镜、反射镜、全息板、 $1/4$ 波长板、分光棱镜等，最后经物镜聚焦成极细的光束，垂直照射到光盘上，扫描高速旋转的光盘信息表面，反射光束沿一定的光路照射到光检测器PD (Photo Detector)上，从PD输出的强弱有别的信号经后续放大与处理后，获得记录在光盘上的“0”、“1”信息流，形

成RF(RadioFrequency)信号，经后端一系列处理后得到图像及声音信号<sup>[31-33]</sup>。

图1-4 DVD信息坑槽结构

PDIC 包含 PD (Photo Detector) 阵列和 IC (Integrated Circuit) 两部分，前端的光电探测器阵列把光信号转换成微弱的光电流信号；后端是前置放大电路，可把光电流信号转换成电压信号并放大到所需要的幅度。它是光盘存储系统光学头中的关键元件<sup>[11]</sup>。

PDIC 另外一个功能是提供聚焦误差 (FES) 和循迹误差信号 (TES)，以及光盘存储的射频信号 (RFS)<sup>[11]</sup>。实际工作中由于光盘的偏心，主轴电机轴的不同心度等原因，将引起盘片在旋转的过程中，沿盘片径向抖动；而且，由于信息纹是按螺旋方式存放的，这就意味着光盘在旋转的过程中，信息纹离盘中心的半径也在变化。为了可靠地从光盘上读取数据，使光束正好落在信息纹上，PDIC 检测光信号的同时还必须提供光束方向的聚焦误差信号 (Focus Error Signal, FES) 和在信息道上的循迹误差信号 (Tracking Error Signal, TES)。

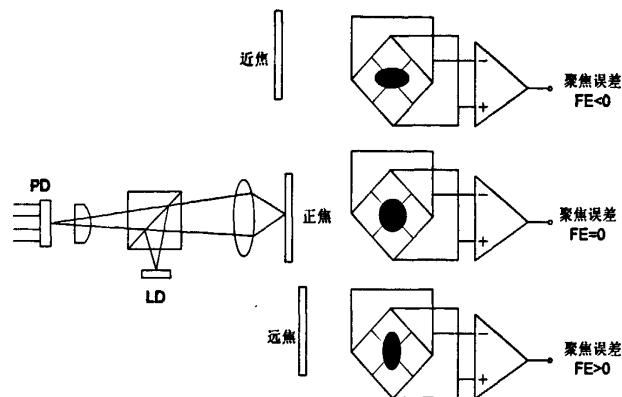

在 PDIC 中正常工作时，利用 A~D 四个光电探测器来实现 RF 信号的读取，为上述四个象限输出之和，即  $RF_{out} = A_{out} + B_{out} + C_{out} + D_{out}$ 。而聚焦误差信号 (FES) 检测方法有：像散法、刀口法、临界角法、富科棱镜法、光斑大小法等。像散法是最常用的聚焦误差检测方法。它是利用像散元件，把物镜离焦量的变化转变为不同方向光能的变化，经光电检测器得到误差信号。图 1-5 为像散法的原理示意图，四象限光检测器 PD 的位置必须很精确，以保证在正焦时反射光斑在 PD 上形成圆形，此时聚焦误差信 FE (Focus Error) 输出为零；在近焦点及远焦点情况下，PD 上的光斑形状发生变化变成椭圆<sup>[34][35]</sup>。

为了检测出光束在信息纹上的位置偏差，采用的寻迹误差信号检测方法有三

光束法、推挽法、衍射推挽法、相位差法、差动推挽法、波动法、外相差法等。

图 1-5 像散法原理示意图

在 DVD 中一般采用相位差分法 (Differential Phase Detection, DPD)。该方法检测 A~D 四个光电探测器中两组对角输出的相位差，光斑在信息纹上移动时，根据  $TES = \Delta\theta[(A+C)-(B+D)]$  的大小，检测出寻迹误差信号 TE，由此控制寻迹线圈驱动电流，达到正确寻迹的目的。

### 1.3.2 PDIC 的设计指标

根据现有的相关产品说明书<sup>[15][35][36]</sup>，确定了本文 PDIC 的相关的性能指标如表 1.2 和 1.3 所示：

表 1.2 PDIC 极限参数( $T_a=25^{\circ}\text{C}$ )

| 参数名称 | 符号               | 数值(室温) | 单位 |

|------|------------------|--------|----|

| 供电电压 | Vdd              | 6      | V  |

| 允许功耗 | Po               | 150    | mW |

| 工作温度 | T <sub>opt</sub> | -20~70 | °C |

| 储存温度 | T <sub>stg</sub> | -40~85 | °C |

表 1.3 PDIC 电气参数 ( $\lambda = 650\text{nm}$ ,  $R_L = 10k\Omega$ ,  $C_L = 10P$ )

| 参数名称 | 符号   | 测试条件 | Min. | Typ. | Max. | 单位 |

|------|------|------|------|------|------|----|

| 供电电压 | Vdd  | —    | 4.5  | 5    | 5.5  | V  |

| 参考电压 | Vref | —    | 2.4  | 2.5  | 2.6  | V  |

|        |               |                                     |     |     |     |            |

|--------|---------------|-------------------------------------|-----|-----|-----|------------|

| 输出电压   | $V_{OF}$      | A~D, $P_i=10\mu W$                  | 200 | 250 | 300 | $mV$       |

|        | $V_{OT}$      | E~F, $P_i=10\mu W$                  | 400 | 450 | 500 |            |

| 响应度    | $R_{e1}$      | A~D, $P_i=10\mu W$                  | 20  | 25  | 30  | $mV/\mu W$ |

|        | $R_{e2}$      | E~F, $P_i=10\mu W$                  | 40  | 45  | 50  |            |

| 输出失调电压 | $V_{off}$     | A~F, $P_i=0$                        | -20 | 0   | +20 | $mV$       |

| 最大输出电压 | $V_{O_{max}}$ | A~F, $P_i=100\mu W$                 | 4.0 | —   | —   | $V$        |

| 频率响应   | $f_c$         | A~D, $f=100KHz, -3dB$               | 20  | 35  | —   | $MHz$      |

|        |               | E~F, $f=100KHz, -3dB$               | 2   | 4   | —   |            |

| 输出噪声   | $V_n$         | $f=4MHz, RBW=30K, VBW=100Hz, P_i=0$ | —   | —   | -70 | $dBm$      |

### 1.3.3 单片集成 PDIC 研究意义

目前，国内生产的 DVD 产品，凭借低廉的生产成本，已在国际 DVD 市场占据了很大的市场份额。国际 DVD 市场的一半以上产品来自中国，为名副其实的世界 DVD 工厂。但是 DVD 产品中用到的关键技术主要由日本的索尼、东芝、NEC、松下以及荷兰的飞利浦等国外大公司所垄断，很多商用芯片绝大部分依赖进口，PDIC 更几乎还是空白。国内 DVD 生产商大部分利润用于缴纳核心技术的专利费，要摆脱这种窘境，PDIC 国产化很有必要。

虽然蓝光DVD已经慢慢占据DVD市场，但由于价格问题国内红光DVD还会继续存在。本文利用低成本的 $0.5\mu m$ BCD工艺研制单片集成的PDIC，对于PDIC芯片国产化，打破国外公司的垄断，具有重要的现实意义。对蓝光DVD的研究开发，也具有一定的指导作用。

同时 $650nm$ 光电探测器除了在DVD光盘应用外，其他方面还有着相当广泛的应用。比如： $650nm$ 塑料光纤通信中作为光接收探测器；用于 $650nm$ 激光器的光功率自动控制电路中的激光信号探测；可以用作条形码等的光学读取头；医疗方面，激光经皮肤照射静脉血液的治疗仪中也采用了 $650nm$ 光电探测器。因此，单片集成PDIC的研究对于这些方面的应用研究也有一定的参考作用。

## 1.4 本文主要内容

本文讨论了硅基单片集成PDIC检测芯片的研制。根据课题研究内容，本文的主要工作和其它章节的主要内容安排如下：

第二章：分析光电探测器的工作原理并设计与BCD工艺兼容的PIN光电探测器。

第三章：介绍各种前置放大器种类与结构，重点讨论负反馈跨阻放大器。设计和分析用于 PDIC 的跨阻放大器结构，在此基础上 Spctre 软件进行模拟仿真。

第四章：分析了 LDO 的工作原理，重点讨论了其核心模块的设计。

第五章：针对设计的光电集成电路进行版图设计，特别介绍了整个版图设计流程中需要注意的问题和设计技巧。

第六章：对流片回来的 OEIC 芯片进行简单的透明封装与 ROSA 封装，进行了各种测试。

第七章：总结本文的主要工作，展望本文工作成果的意义，并提出今后进一步的研究和完善的方向。

## 参考文献

- [1] 徐端颐. 光盘存储系统设计原理[M]. 北京: 国防工业出版社, 2000.

- [2] 骆志坚, 李旭鹏. DVD 简介[J]. 电声技术, 2002, 3:49-51.

- [3] 张善锋. DVD 聚焦控制和信号处理电路板的设计[D]. 大连: 大连理工大学, 2005.

- [4] 刘宪坤. 下一代 DVD 展望[J]. 电视技术, 2004, 12: 7-11.

- [5] Maeda T. Optical disk system using blue-violet laser[J]. Optieal Memory and Optical Data Storage Topical Meeting. 2002, 422-424.

- [6] Kobota T. HD DVD overview of next generation optical disc format[J]. IT to HD, 2004: 213-224.

- [7] Shibatoko T, Ohkubo S, Ide T et al. Optical head and optical disk technologies for HD DVD[J]. Comsumer Electronics, 2005: 11-12.

- [8] 卓辉立. DVD 激光头技术简介[J]. 山东电子, 2005, 3: 39-41.

- [9] 陈弘达. 微电子与光电子集成技术[M]. 北京: 电子工业出版社, 2008: 9-10.

- [10] 叶玉堂, 饶建珍等. 光学教程[M]. 北京: 清华大学出版社, 2005: 486-489.

- [11] 梁恩主, 郑婉华等. 新型 DVD/VCD 光学头用 PDIC 的研制[J]. 半导体光电, 2001, 22(5): 347-350.

- [12] 梁恩主. DVD 光学头用 PDIC 的研制与测试[D]. 北京: 中国科学院半导体研究所, 2001.

- [13] 胡海军, 李挥, 张政操等. 一种新型 DVD 激光读取头光电检测集成电路的研制[J]. 半导体光电, 2008, 29(6): 839-843.

- [14] 安杰, 邸雪松, 李挥等. 用于 PDIC 的跨阻放大器的优化设计[J]. 半导体光电, 2009, 30(5): 660-662.

- [15] 杭州士兰光电. SM625AXX[Z]. 2009.

- [16] 杭州士兰光电. SM525AXX[Z]. 2005.

- [17] 卞剑涛. 单片集成光盘信号探测放大芯片 (PDIC) 的研制[D]. 厦门: 厦门大学, 2006.

- [18] Takahiro Takimoto, Naoki Fukunaga, et al. High Speed Si-OEIC(OPIC) For Optical Pickup[J]. IEEE Transaction on Consumer Electronics, 1998, 44(1): 137 -

142.

- [19] Motohiko Yamamoto, Masaru Kubo, et al. Si-OEIC with Built-in Pin- photodiode [J]. IEEE Transaction on Electron Devices, 1995, 42 (1): 58-63.

- [20] H. Zimmermann. Monolithic Bipolar, CMOS and BiCMOS Reciver OEICs[J]. IEEE, 1999: 31-40.

- [21] A. Ghazi, T. Heide, et al. CMOS PIN Fiber Receiver and DVD OEIC[J]. IEEE Proc. EDMO'99, 1999:108-112.

- [22] A. Ghazi, T. Heide, et al. DVD OEIC and 1Gbit/s Fiber receiver in CMOS Technology[J]. IEEE, 2000: 224-226.

- [23] C. Seidl, H. Schatzmayr, et al. A Programmable OEIC for Laser Applications in the Range from 405nm to 780nm[J]. IEEE Proceedings of ESSCIRC, Grenoble, France, 2005: 439-442.

- [24] J. Sturm, M. Leifhelm, et al. Optical Receiver IC for CD/DVD/Bule-Laser Application[J]. IEEE Journal of Solid-State Circuits, 2005, 40 (7): 1406 -1413.

- [25] H. Zimmermann, K.Kicschnick. Low-offset BiCMOS OEIC for optical storage system[J]. Electronics Letters, 2000, 36(14): 1223-1224.

- [26] H. Zimmermann, H.Dietrich. Low-cost silicon receiver OEIC[J]. Proc. SPIE, 2001, 4600: 14-25.

- [27] H. Zimmermann. Advanced Silicon OEIC[J]. IEEE, 2002, 153-163.

- [28] Park.Deuk Hee, Gob. Chae Dong, et al. Triple wavelength OEIC with improved optical responsivity[J]. Proceedings of SPIE-The International Society for Optical Enginneering, 2009.

- [29] M. Förtsch, H. zimmermann, et al. Low-Offset CMOS OEIC for Optical Storage Systems[J]. IEEE Transactions on Consumer Electronics, 2003, 49(4): 1125-1128.

- [30] Gerben W. de Jong, Jozef R.M. et al. A DC-to-250MHz Current Pre-Amplifier with Integrated Photo-Diodes in Standard BiCMOS or Optical-Storage Systems[J]. IEEE ISSCC, 2002, 1(1): 362-363, 474.

- [31] 关林风, 李爱华, 姚行中等. 光盘驱动器原理和维修技术[M]. 北京: 科学出版社, 2001.

- [32] 韩广兴, 韩雪冬. 影碟机原理与维修[M]. 北京: 电子工业出版社, 1997.

- [33] 王建, 杨品, 巴林凤. 多媒体技术及其应用[M]. 大连: 大连理工大学出版社, 1999.

- [34] 张建勇, 马建设, 徐端颐等. 光电探测器安装误差对差动相位探测信号的影响[J]. 光学技术, 2006, 32(6): 909-911.

- [35] 周晓波. 激光头信号检测与处理系统的研究[D]. 大连: 大连理工大学, 2002.

- [36] Capella Microsystems Inc. CM1295P2SA[Z]. 2003

- [37] SONY. CXA2586M[Z].

## 第二章 BCD 工艺下 PIN 光电探测器的设计

光电探测器是PDIC中重要的光电转换器件，它位于检测芯片的最前端，将接收到的光信号转换成相应的电流信号。光电探测器的结构有多种，包括肖特基（SB）二极管、金属-半导体-金属（MSM）光二极管、PN（或PIN）光电二极管、雪崩光二极管（APD）等。其中，PIN光探测器由于具有频带宽、响应度较高，使用方便的特点，而成为CD/DVD光盘存储系统中PDIC检测芯片的首选。本文利用低成本的0.5μm BCD工艺特点，实现类似PIN结构的光电探测器探测。

### 2.1 BCD 工艺的选择<sup>[1][2]</sup>

BCD（Bipolar、CMOS、DMOS）是一种单片集成工艺技术，1986年由意法半导体ST公司率先研制成功，这种技术能够在同一芯片上制作Bipolar，CMOS和DMOS器件。BCD工艺把双极器件和CMOS器件同时制作在同一芯片上。它综合了双极器件高跨导、强负载驱动能力和CMOS集成度高、低功耗的优点，使其互相取长补短，发挥各自的优点。更为重要的是，它集成了DMOS功率器件，DMOS可以在开关模式下工作，功耗极低。不需要昂贵的封装和冷却系统就可以将大功率传递给负载，低功耗是BCD工艺的一个主要优点之一。整合过的BCD工艺制程，可大幅降低功率耗损，提高系统性能，节省电路的封装费用，并具有更好的可靠性。

BCD工艺典型器件包括低压CMOS管、高压 MOS管、各种击穿电压的LDMOS、垂直NPN管、垂直PNP管、横向PNP管、肖特基二极管、阱电阻、多晶电阻、金属电阻等；有些工艺甚至还集成了EEPROM、结型场效应管JFET等器件。由于集成了如此丰富的器件，这就给电路设计者带来极大的灵活性，可以根据应用的需要来选择最合适的器件，从而提高整个电路的性能。

BCD工艺的主要应用领域为电源管理（电源和电池控制）、显示驱动、汽车电子、工业控制等领域。而本文主要利用该工艺制作探测器。普通的CMOS工艺中，没有低浓度的层，光电探测器难以形成纵向结构。而BCD工艺，有BN<sup>+</sup>埋层和低掺杂的N-EPI外延层，可以研制类似PIN结构的光电探测器。

## 2.2 PIN 探测器的工作原理与特性参数

### 2.2.1 光电探测器的工作原理

光电探测器是把光信号转变成电信号的半导体器件。基本工作原理包括以下三个过程<sup>[3]</sup>：(1) 入射光照下，光子进入材料被吸收从而产生光生载流子；(2) 载流子在耗尽区内建电场的作用下，向探测器的两极漂移运动；(3) 光电流与外电路相互作用，输出电信号。

PN结就是一个最简单的光电探测器，但它具有两个主要的缺点：

(1) 它的结电容或耗尽区电容较大。

(2) 它的耗尽层宽度最大也只有几微米，而长波长的光的穿透深度比耗尽层宽度还大，所以大多数光子没有被耗尽层吸收，而是进入不能将电子空穴对分开的电场为零的N区，因此长波长的量子效率很低。

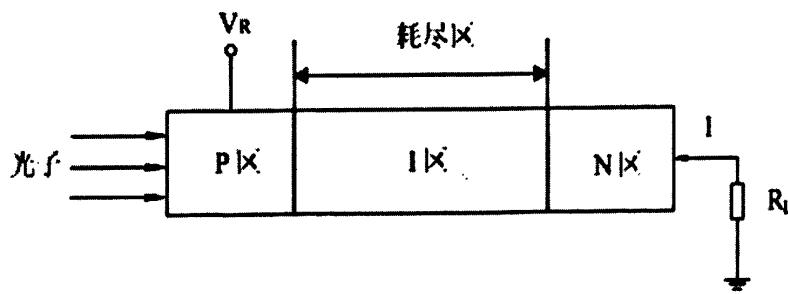

为了克服这个问题，通常采用 PIN 探测器，其结构如图 2-1 所示。器件由 P 区、N 区和本征 I 区组成。工作时，在器件两端加上大小为  $V_R$  的反向偏置，其在结中形成的电场和内建电场方向相同。当光子能量大于材料的禁带宽度 ( $h\nu > E_g$ ) 时入射光将被半导体吸收，激发 P 区、I 区、N 区的价带，产生光生电子-空穴对。电场作用下电子和空穴被分离，导带中电子向 N 区运动，价带空穴向 P 区运动，在器件两个电极上产生光电压，在外电路上产生光电流。即可将接收到的光信号转换成电信号输出。

图 2-1 PIN 探测器结构

由于 I 区的作用 PIN 光电探测器具有以下几个优点<sup>[4]</sup>：(1) 大大提高了器件的探测能力。由于 I 区加入较宽，使得光生载流子的产生率增多，提高了器件

的响应度；（2）因为 I 区有强电场，光生载流子在强电场作用下以较快的速度向电极漂移，提高了响应速度；（3）因为 I 区的存在，耗尽层被展宽，结电容减少，提高了响应频率。

### 2.2.2 PIN 光电探测器主要性能参数

PIN 光电探测器的主要特性包括量子效应、光谱响应响应、暗电流以及频率响应等<sup>[5]</sup>。

#### （1）量子效率和光谱响应

量子效率  $\eta$  是半导体光电探测器最重要的指标。量子效率定义为吸收一个入射光子能够产生的电子-空穴对个数，即

$$\eta = \frac{\text{产生的电子-空穴对个数}}{\text{入射的光子数}} = \frac{I_p / q}{P / h\nu} \quad (2.1)$$

其中  $P$  为单位入射光功率， $I_p$  为产生的光电流， $q$  为电子电荷， $h\nu$  为光子能量。

响应度也是衡量光电探测器的最主要性能指标之一。入射到吸收区的光子产生的光生载流子在耗尽区内建电场的作用下，向探测器的两极漂移运动，并在输出端形成光电流。响应度用来表征单位入射光功率所产生的光电流即

$$R_e = \frac{I_p}{P} = \eta \cdot \frac{q}{h\nu} \approx \frac{\eta\lambda}{1.24} \quad (2.2)$$

量子效率越高，其响应度便越高，即光电转换效率越高。材料不同的光电探测器具有不同的响应度，所以应该选择合适的材料来制造探测器。当波长一定时，响应度  $R_e$  为一固定值，它表明量子效率  $\eta$  同入射光功率无关，因而光电流的大小与入射光的光功率  $P$  成正比，入射光的光功率  $P$  变化时，探测到的光电流也相应地变化，可以利用这一关系来探测变化多端的光学信号。实际半导体光电二极管中，在 30%~95% 之间。为了获得高的量子效率，耗尽层必须足够厚，以便能够吸收大部分的入射光线。耗尽层越厚，光生载流子电子和空穴漂移到 PN 结两端所需的时间越长，载流子的漂移时间决定了光电探测器的响应速率，因此必须在响应速率与量子效率之间进行折衷选择。

#### （2）暗电流特

光电二极管中，没有光照时，在半导体内部、由于热电子发射等原因也会产

生自由载流子电子和空穴，它们在电场的作用下也会产生电流，这种无光照时在电路上流动的电流称之为暗电流。暗电流是一种噪声信号，我们希望它越小越好。一般说来，光电二极管的暗电流由体内电流和表面电流两部分组成。表面暗电流主要由表面复合所引起的。对于浅结器件，表面暗电流较大。体内暗电流则主要取决于材料和器件结构。在低偏压下，器件的暗电流主要是产生—复合电流及扩散电流；当电场足够高时，暗电流大小将由隧穿电流或雪崩过程所决定。它的主要组成部分如下：

① 产生—复合电流  $I_{g-r}$ 。在耗尽区中的产生—复合电流  $I_{g-r}$  与偏压  $V$ 、有效载流子寿命  $\tau_e$  及温度  $T$  的关系为<sup>[6]</sup>：

$$I_{g-r} = \frac{qn_iAW}{\tau_e} [1 - \exp(-qV/kT)] \quad (2.3)$$

其中， $q$  是电子电荷， $k$  是 Boltzmann 常数， $\tau_e$  为有效载流子寿命， $A$  是光面积， $W$  是耗尽区宽度， $n_i$  为本征载流子浓度。

② 扩散电流  $I_{diff}$ 。扩散电流是由耗尽区四周的非耗尽  $p$  区和  $n$  区内以及耗尽区边界热激发的少数载流子向耗尽区的扩散而形成。表示为<sup>[7]</sup>：

$$I_{diff} = I_s [1 - \exp(qV/kT)] \quad (2.4)$$

其中， $I_s$  为反向饱和电流。

③ 隧穿电流。当材料的禁带中存在较多的陷阱能级，通过禁带中的陷阱或缺陷能级将产生隧穿电流；或在相对较高的偏压下时，电子直接从结的一边的价带隧穿到结另一边的导带构成带间隧穿电流。在一个均匀掺杂的耗尽区中，带间隧道电流。由于我们的器件是工作在较低的偏压下，隧穿电流对暗电流的影响非常小，可以忽略不计。

④ 表面漏电流  $I_L$ <sup>[8]</sup>。表面漏电流 ( $I_L$ ) 流是由于器件表面的物理特性不完善，如有表面缺陷、不清洁和加有偏置电压而引起的。

$$I_L = qS\Delta n = \frac{Aqn_iS_0}{2} \quad (2.5)$$

其中  $A$  为  $pn$  结面积,  $n_i$  为本征载流子浓度,  $S$  为表面复合速度,  $S_0$  为本征表面复合速度, 对于 P 型表面  $S_0 = \sigma_n v_{th} N_s$ ,  $\sigma_n$  为俘获截面,  $v_{th}$  为载流子热运动速率,  $N_s$  为单位表面积内复合中心数,  $\Delta n$  为 P 型表面的非平衡少数载流子浓度。表面漏电流是由结的泄漏电阻  $R_{sh}$  形成的旁路电流。 $R_{sh}$  是由  $pn$  结的微分电阻及工艺缺陷(如光刻针孔)等造成的旁路电阻并联而成的。对探测器而言, 负载电阻较大, 在施加反向电压的情况下,  $R_{sh}$  所造成的电流不能忽略, 它严重影响着探测器的性能。通常, 二极管的反向特性与器件的表面处理及使用环境有密切关系。

### (3) 频率响应

光电探测器正常工作所能探测到入射信号的调制频率是有限的, 调制频率高于光电探测器频率响应的入射光信号将不能被正确探测出。频率响应是光电探测器对加在光载波上的电调制信号的响应能力的反应。表征了光电探测器的频率特性光电二极管的响应速度是由探测器的上升时间或下降时间来衡量的, 通常取两者之间较大值<sup>[5]</sup>。在半导体光电探测器中, 影响响应速度的因素主要有三个:①耗尽层中光生载流子的渡越时间;②耗尽层外面的载流子的扩散时间;③耗尽的电容。耗尽层的电容是影响速度的主要因素, 加大探测器本征层的宽度对提高量子效率和减小光电探测器电容是一致的, 而增大宽度载流子在耗尽层的渡越时间将会增加。减小光电探测器的面积可以有效减小结电容和暗电流, 但是小面积的光电探测器给有效耦合带来了难度。因此为了优化响应速度, 需要选择适当的吸收深度和光电探测器面积。比较合理的选择是选择一定的耗尽层宽度, 使得载流子渡越时间是调整时间周期的一半<sup>[9]</sup>。然而本文由于采用商用的 BCD 工艺, 因而耗尽层的宽度实际上已经由工艺决定了, 而为了跟实际产品接轨, 光电探测器的光敏面也受到了限制。

## 2.3 PIN 探测器等效电路模型

### 2.3.1 PIN 光电探测器示意图

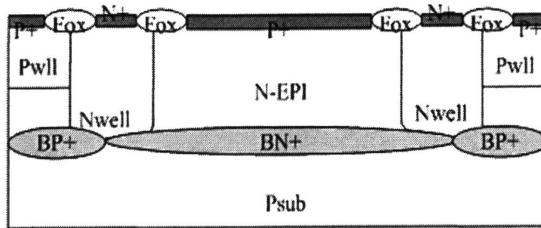

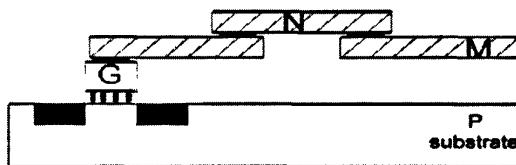

本文利用 BCD 工艺中拥有低掺杂的外延层(N-PEI)和  $BN^+$  埋层的特点设

计了 PIN 结构的光电探测器，截面结构如图 2-2 所示。PIN 光电探测器的阳极由  $P^+$  源或漏扩散得到。阴极则由  $BN^+$  埋层组成，并通过 Nwell、 $N^+$  引出。而中间的 I 层则由 N-EPI 得到，I 层的宽度较宽可吸收绝大多数光子。这样 PIN 结构的光电二极管不但可以在较高的频率下工作，而且具有较高的量子效率和光响应度。

图 2-2 PIN 光电探测器示意图

在探测器阵列中，由于光生载流子有一定的扩散长度，当光照在某个象限探测器且接近相邻象限一侧时，相邻的这个象限即使不受光照，也可能有一定的光电流输出，各象限探测器之间会相互串扰。为了减小探测器阵列中各象限探测器之间的相互影响，各探测器必须有良好的隔离。光电探测器工作在反向偏压状态，因此采用 PN 结保护环隔离。图 2-2 中 N 阵外围的 P 阵形成 PN 结起到了隔离各个探测器互相串扰的作用。

### 2.3.2 等效电路模型

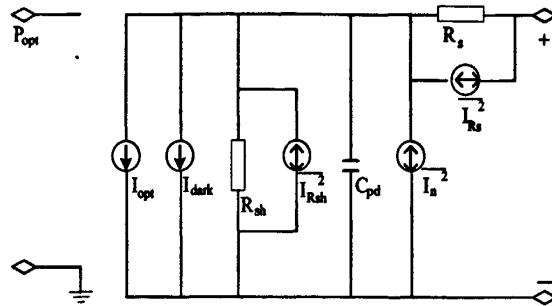

BCD 工艺 PDK 中没有提供光电器件的模型。对于 PDIC 设计，为了准确预测光电探测器的性能，需要建立其等效电路模型，以便以分析。为了跟实际设计软件兼容 PIN 光电探测器用一个三端点模型等效<sup>[10]</sup>，如图 2-3 所示。左端点为光信号输入端，以  $P_{opt}$  和地电压差  $V(P_{opt})$  来等效入射光的光功率。右边两端点对应器件的两个实际的电端口，上端点对应正极（n 区），下端点对应负极（p 区）。图中  $I_{opt}$  和  $I_{dark}$  分别表示探测器的光电流和暗电流， $C_{pd}$  表示探测器的结电容， $R_{sh}$  和  $R_s$  分别表示探测器的并联和串联电阻， $\overline{I_n^2}$ 、 $\overline{I_{R_s}^2}$  以及  $\overline{I_{R_{sh}}^2}$  分别表示探测器的散弹噪声、串联电阻的热噪声和并联电阻的热噪声。下面对模型中各模块作简单的介绍。

图 2-3 PIN 探测器等效电路模型

### (1) 光电流模型

光电探测器的光电流模型包括两部分：稳态模型  $I_{eq}$  和动态模型  $I_{opt}$ 。分别为：

$$I_{eq} = R_e \cdot V(P_{opt}) \quad (2.6)$$

$$I_{opt} = I_{Req} = \frac{I_{eq}}{1 + j\omega R_{eq} C_{eq}} \quad (2.7)$$

其中  $R_e$  为探测器光谱响应度， $C_{eq}$  和  $R_{eq}$  分别为引入的等效电容和等效电阻，满

足  $f_{-3dB} = \frac{1}{2\pi R_{eq} C_{eq}}$ 。为了减小引入的  $R_{eq}$  对噪声特性的影响，电流输出结构中

$R_{eq}$  应取足够大。

### (2) 暗电流模型

对理想的光电探测器，在无光照的时候应该没有光电流，然而实际上仍然存在较小的电流。由于探测器工作在很低的反偏电压下，这里忽略隧穿电流的影响。由式 (2.3-2.5) 可得到：

$$I_{dark} = I_{g-r} + I_{diff} + I_L \quad (2.8)$$

### (3) 并联电阻模型

并联电阻是零偏压、无光照下的动态电阻（或称暗电阻），它与反向饱和电流之间有如下关系<sup>[8]</sup>：

$$R_{sh} = \left( \frac{dV}{dI} \right)_{V=0, P_{opt}=0} = \frac{KT}{qI_0} = \frac{KT}{qA_0 J_0} \quad (2.9)$$

#### (4) 结电容模型

忽略 PN 结侧面电容的影响，探测器的结电容近似为一个平板电容，可表示为：

$$C_{pd} = \frac{\epsilon_s A_0}{x_w} = A_0 \sqrt{\frac{\epsilon_s q N_A N_D}{2(N_A + N_D)(V_{bi} - 2KT/q - V)}} \quad (2.10)$$

考虑到串联电阻的影响，式中 V 取电容两端偏压，在本文中，理论计算的  $C_{pd}$  约为 0.278PF。

#### (5) 串联电阻模型

从 BCD 工艺 PDK 中的二极管模型中的串联电阻参数计算得到。

#### (6) 噪声模型

散弹噪声是探测器的主要噪声，当光信号进入光电探测器时，光子产生-复合的统计特性会引发散弹噪声。光电效应使光生载流子的数量起伏变化，其统计特性服从泊松过程。不计背景辐射电流，考虑暗电流后，散粒噪声谱密度为<sup>[8]</sup>：

$$\overline{I_n^2} = 2q(I_{opt} + I_{dark}) \quad (2.11)$$

探测器的噪声还包括串联电阻热噪声谱密度  $\overline{I_{Rs}^2}$  和并联电阻热噪声谱密度  $\overline{I_{Rsh}^2}$ ，分别为：

$$\overline{I_{Rs}^2} = \frac{4KT}{R_s}, \overline{I_{Rsh}^2} = \frac{4KT}{R_{sh}} \quad (2.12)$$

## 2.4 本章小结

本章介绍了光电探测器的基本原理和性能参数。充分利用 BCD 工艺的低掺杂的外延层（N-PEI）和 BN<sup>+</sup>埋层特点设计了与工艺完全兼容的 P<sup>+</sup>/N-EPI/BN<sup>+</sup>光电探测器结构，并建立了探测器等效电路模型。经仿真得到此类探测器的结电容约为 0.28PF，带宽为 400 MHz，响应度为 0.21A/W。

## 参考文献

- [1] 陈志勇, 黄其煜, 龚大卫. BCD 工艺概述[J]. 半导体技术, 2006, 31(9): 641-644, 659.

- [2] 杨银堂, 朱海刚. BCD 集成电路技术的研究与进展[J]. 微电子学, 2006, 36 (3): 31-319.

- [3] 施敏[著], 赵鹤鸣, 钱敏, 黄秋萍译. 半导体器件物理与工艺(第二版) [M]. 苏州: 苏州大学出版社.

- [4] 刘丽娜. 用于塑料光纤通信 650nm 硅 PIN 光电探测器的研制[D]. 厦门: 厦门大学, 2003.

- [5] 陈弘达. 微电子与光电子集成技术[M]. 北京: 电子工业出版社, 2008.

- [6] P. Baeri, S. U. Campisano, G. Foti et al. Arsenic diffusion in silicon melted by high-power nanosecond laser pulsing[J]. Apply Physics Letters. 1978, 33(2):137.

- [7] S. R. Forrest, Williams, G. F. Kim, O. K et al, Excess-noise and receiver sensitivity measuremens of In 0.53 Ga 0.47 As/InP avalanche photodiodes [J]. Electron Letter. 1981,17(24): 917-918 .

- [8] 齐丕智等. 光敏感器件及其应用[M]. 北京: 科学出版社, 1987.

- [9] S. M. Sze. Physics of Semiconductor Devicds [M]. NEW York: JOHN WILEY & SONS 1981.

- [10] 卞剑涛. 单片集成光盘信号探测放大芯片 (PDIC) 的研制[D]. 厦门: 厦门大学, 2006.

## 第三章 跨阻前置放大器的设计与仿真

前置放大器是 PDIC 等光接收组件的关键部分之一，其性能在很大的程度上决定了整个光接收机的性能。它将光电探测器的电流信号转换并放大成一定幅度的电压信号。因为探测器的光电流一般很微弱，如果采用一般放大器进行放大，放大器本身会引入较高的噪声，后一级放大器将对前一级放大器输出的信号和被引入的噪声进行放大，信噪比不会得到改善。这就要求它与光电探测器相匹配，从而得到尽可能高的增益、带宽和输出信噪比<sup>[1]</sup>。设计光接收机前置放大器时需要注意以下几点<sup>[2]</sup>：

- (1) 尽量减小等效输入噪声电流，提高灵敏度；

- (2) 带宽与信号速率相适应；

- (3) 产生足够大的增益，以克服后续电路噪声的影响。

这三个要求是相互制约的，带宽的增加将导致噪声的增加和增益的下降。此外，当温度变化时放大器应当保持增益、带宽和灵敏度的稳定。输入阻抗要足够小，以避免光电探测器寄生电容对带宽的影响。

### 3.1 跨阻前置放大器的分类

一般来说，光接收芯片前置放大器可以采用低阻前置放大器、高阻前置放大器或跨阻前置放大器结构三大类，以下将做简单介绍。

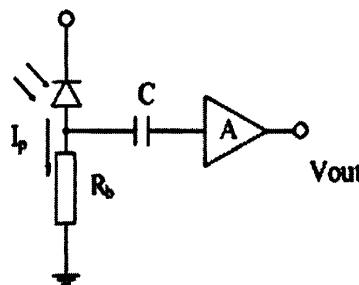

#### (1) 低阻前置放大器

低阻放大器是一种最基本的结构相对简单的放大电路如图 3-1 所示<sup>[3]</sup>。检测光电流通过电阻  $R_b$  后产生信号电压，然后通过放大电路对电压进行放大。输出电压范围是电阻  $R_b$  和放大器增益 A 的函数。如果放大器的噪声相对较低，则该前置放大器的低值电阻  $R_b$  将是产生放大器噪声的主要因素。随着  $R_b$  电阻值的增大，噪声电流将减小，但是频率响应会变差。带宽受第一级放大器的等效输入电阻  $R_i$  和等效输入电容  $C_i$  的限制，即：

$$f_b = \frac{1}{2\pi R_i C_i} \quad (3.1)$$

从式 3.1 可见，放大器的带宽与时间常数  $R_i C_i$  成反比。如果  $C_i$  保持不变，通过减小  $R_i$  提高带宽，但会引起放大器信噪比下降。为了获得较大的带宽，通常将  $R_i$  值取得较小，一般选用  $50\Omega$  的低电阻。低阻前置放大器的特点是结构简单，不需要或仅需要很少的均衡，动态范围较大，缺点是噪声大，灵敏度低，增益小。

图 3-1 低阻前置放大器

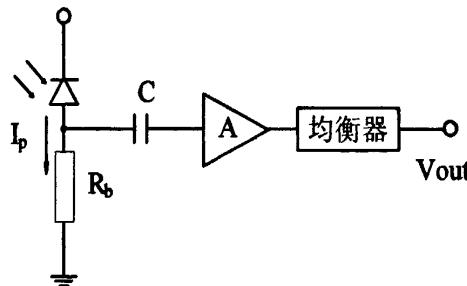

## (2) 高阻前置放大器

图 3-2 所示为高阻型前置放大器的放大电路<sup>[4]</sup>，它是建立在获得最大增益的理论基础上的，形式与低阻型相同。它的输入阻抗非常高( $1\sim 10 M\Omega$ )，热噪声非常小，灵敏度是所有类型中最大的一个。

图 3-2 高阻前置放大器

但高阻前置放大器的特点是输入阻抗高，电路时间常数较大，影响了接收机的频率特性，限制了 -3dB 带宽。同时，由于时间常数较大，当信号速率较快时，信号脉冲会产生严重失真，需要在前端电路中进行频率补偿。采用高阻的偏置电阻  $R_b$ ，其动态范围小，当传输速率较高时，在输入信号的高频分量损失太多，

因而对均衡电路提出了很高的要求，一般只在较低速的系统中使用<sup>[5]</sup>。

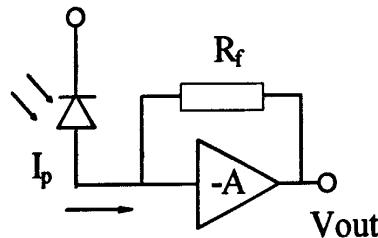

### (3) 跨阻前置放大器

负反馈跨阻前置放大器是一种电压-并联负反馈拓扑结构，如图 3-3 所示。

由电路理论可知，负反馈可以稳定增益，增加动态范围和带宽，减少噪声等<sup>[6][7]</sup>。

负反馈技术的特点可以用于前置放大器的设计。跨阻放大器是在光互联系统中最常采用的前置放大器结构，它具有许多低阻和高阻放大器不具备的优点，对系统的增益，噪声以及带宽进行了很好的折中。跨阻放大器成为高速光纤通信电路的最佳选择。其中，反馈电阻  $R_f$  形成电压并联负反馈。本文单片集成光接收芯片中所设计的前置放大器就是采用这种结构。

图 3-3 跨阻前置放大器

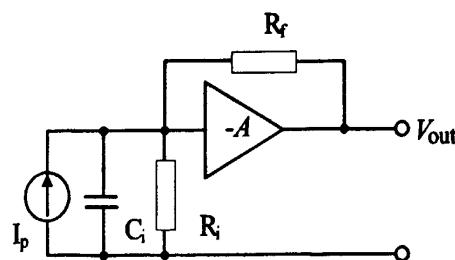

## 3.2 跨阻前置放大器的性能分析

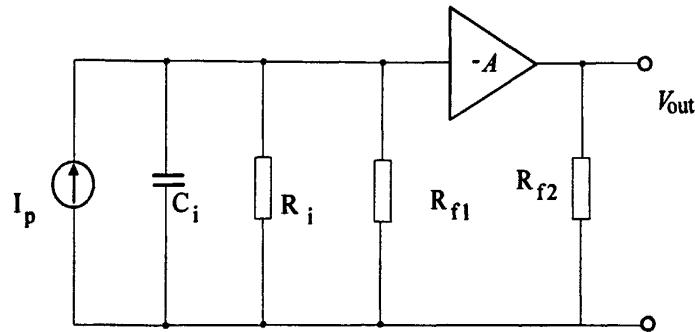

跨阻放大器等效小电路图如图 3-4 所示。其中， $I_p$  为光检测器等效电流， $C_i$  为光检测器的寄生电容， $C_f$  为基本放大器的输入电容， $R_i$  为基本放大器的电阻， $R_f$  为反馈电阻， $A$  为基本放大器的中频电压增益。

图 3-4 跨阻前置放大器小信号电路

### (1) 增益

图 3-5 是跨阻放大器的密勒等效电路，由密勒定理可以直接计器的等效输入阻抗和等效输出阻抗<sup>[8]</sup>。

$$R_{f1} = \frac{R_f}{1+A}, R_{f2} = \frac{R_f}{1+A^{-1}} \approx R_f \quad (3.2)$$

图 3-5 跨阻前置放大器密勒等效电路

跨阻放大器的开环增益为：

$$A_r = \frac{V_{out}}{V_{in}} R_i = A R_i \quad (3.3)$$

跨阻放大器的闭环增益为

$$A_{rf} = \frac{A_r}{1 + A_r \beta} = \frac{A_r}{1 + A_r \frac{1}{R_f}} = \frac{A}{\frac{1}{R_i} + \frac{A}{R_f}} \quad (3.4)$$

如果  $A \gg 1$ ,  $R_f < R_i$ , 则有

$$A_{rf} = \frac{A}{\frac{1}{R_i} + \frac{A}{R_f}} \approx R_f \quad (3.5)$$

由式 3.5 可知，跨阻放大器的跨阻增益与反馈电阻  $R_f$  的阻值有关， $R_f$  越大，负反馈越深，跨阻增益越大。

## (2) 带宽

令  $C_T = C_s + C_i$ , 互阻前置放大器的电流-电压传输函数为：

$$H(\omega) = \frac{V_o(\omega)}{I_p(\omega)} = \frac{A}{\frac{1}{R_f} + \frac{1}{R_i} + j\omega C_T} \approx \frac{R_f}{1 + j\omega R_f C_T / A} \quad (3.6)$$

$$\text{互阻放大器的}-3\text{dB 带宽为: } BW_{-3dB} \approx \frac{A}{2\pi R_f C_T}$$

由此可以得出以下结论:

- ① 反馈电阻  $R_f$  越小, 互阻放大器的频带越宽。

- ②  $C_T$  越小, 互阻放大器的频带越宽。光电探测器确定了, 光电探测器的寄生电容  $C_s$  也就确定了, 所以一般不容易通过减小  $C_T$  来提高带宽。

- ③ 基本放大器的电压增益(开环增益)越大, 互阻放大器的频带越宽。

从上面的分析可知,  $R_f$  越小, 跨阻放大器的频带越宽;  $C_i$  越小, 可以增加放大器的带宽, 降低噪声。当  $R_f$  和  $C_i$  一定时, 放大器的闭环带宽和放大器开环增益成正比。但是, 也不能无限制的增大开环增益来提高带宽。由于放大器密勒电容的存在, 增大增益的同时, 也增大了密勒电容的影响, 使总  $C_i$  增加, 从而减小了放大器的带宽, 增大了放大器的噪声<sup>[9]</sup>。

### (3) 噪声

噪声是一种随机现象, 限制了一个电路能够正确处理的最小信号电平, 现今的模拟设计者经常要考虑的问题, 因为其与功耗、速度和线性度之间是相互制约的<sup>[8]</sup>。由于噪声的存在, 限制了光接收芯片接收弱信号的能力, 即最小可接收的平均光功率, 因此噪声指标是反映光接收芯片性能因素。放大电路中的噪声源可以分为两类: (1) 器件噪声: 包括热噪声、散弹噪声和闪烁噪声, 主要由电阻和MOS管产生; (2) 干扰: 包括衬底噪声和电源噪声。

跨阻放大器的热噪声, 主要来自反馈电阻的热噪声和MOS管的热噪声。电阻中的热噪声是由电子作杂乱无章的热骚动而造成的。电阻热噪声可以用电流噪声源或电压噪声源来表示, 其功率谱密度分别为:

$$S_i(f) = 4kT/R, S_v(f) = 4kTR \quad (3.7)$$

式中,  $k$  为玻尔兹曼常数,  $T$  为热力学温度。

而 MOS 管是依靠载流子在沟道中的漂移运动工作的，也有热噪声，最大的噪声来源是在沟道产生。当 MOS 管工作在饱和区时，其沟道热噪声电流功率谱密度为：

$$S_i(f) = 4kT\gamma g_m \quad (3.8)$$

式中， $\gamma$  为系数， $g_m$  为 MOS 管跨导。沟道热噪声的扰动引起栅极热噪声，在高频处影响很大。MOS 管的栅极、源极和漏极材料都有一定的电阻，因而也产生热噪声。

闪烁噪声又称为低频噪声或  $1/f$  噪声，这种噪声的特点是频谱集中在低频段，且功率谱密度随频率的降低而增大。一般认为这种噪声是由于半导体晶格结构的缺陷所造成的载流子在晶体表面的产生和复合引起的。低频时，MOS 管的噪声主要由它决定。闪烁噪声可以用一个与栅极串联的电压源来模拟，其功率谱密度近似由下式给出

$$S_v(f) = \frac{K}{C_{ox}WL} \frac{1}{f} \quad (3.9)$$

其中， $K$  是与工艺有关的常数， $C_{ox}$  为单位面积的栅氧化层电容， $L$  为栅长， $W$  为栅宽。 $1/f$  噪声谱密度与频率成反比。

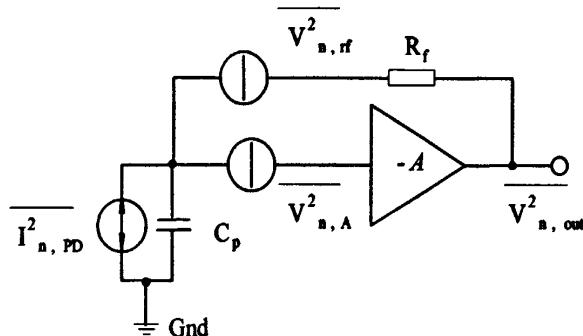

图 3-6 负反馈跨阻放大器噪声模型

理解了噪声来源之后，接下来对跨阻放大器的噪声进行分析，其模型如图 3-6 所示<sup>[10][11]</sup>。图中， $\overline{V^2_{n,A}}$  为开环电压放大器的等效输入噪声谱密度，是反馈电阻噪声电压谱密度， $\overline{I^2_{n,PD}}$  为探测器的等效电流噪声密度， $\overline{V^2_{n,out}}$  是输出电压噪声谱密度。

假设各噪声源不相关，开环放大器增益  $A \gg 1$  且  $\omega_r \rightarrow \infty$ ，则输出噪声电压和输入噪声电流谱密度分别为：

$$\left. \begin{aligned} \overline{V_{n,out}^2} &= \overline{I_{n,PD}^2} R_f^2 + 4KTR_f + \overline{V_{n,A}^2} \\ \overline{I_{n,in}^2} &= \overline{I_{n,PD}^2} + 4KT/R_f + \overline{V_{n,A}^2}/R_f^2 \end{aligned} \right\} \quad (3.10)$$

由式 (3.10) 可以看出，跨阻的噪声直接加到输入端，但是增加跨阻值可以减少等效输入电流谱密度。但是在噪声减小的同时降低了放大器的带宽。

通过以上对跨阻放大器各项性能指标的具体分析，可知其跨阻增益、带宽和噪声之间存在权衡。当  $A$  和  $C_i$  一定时，反馈越深，即  $R_f$  越小，跨阻放大器的频带就越宽。但是反馈越深，跨阻增益就越小。而且，反馈越深，反馈电阻所引入的噪声就越大。因此，要使整个电路的性能达到最优 必须考虑各个指标之间的相互制约关系。

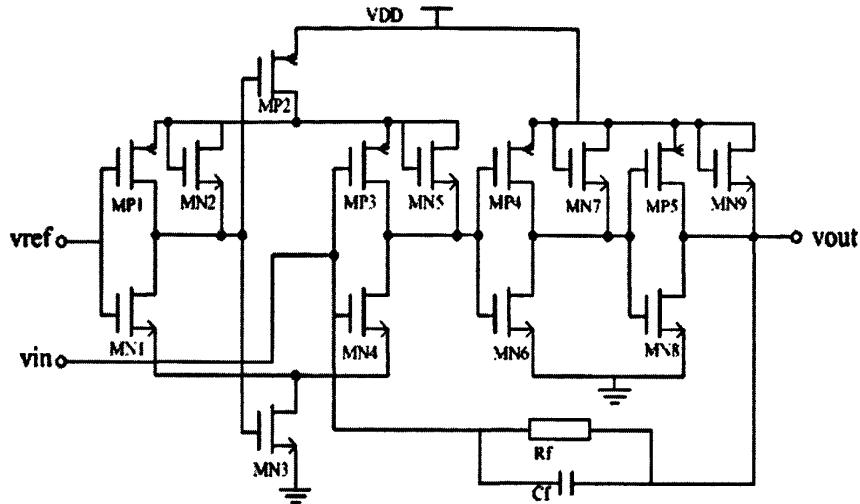

### 3.3 跨阻放大器设计

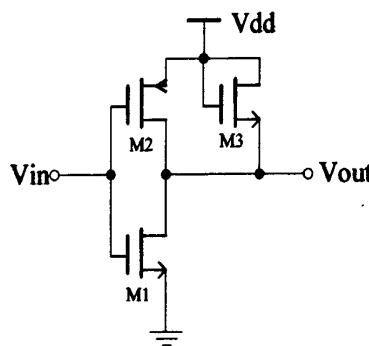

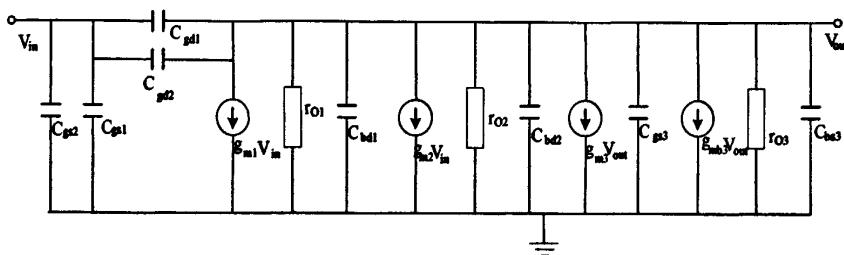

通常，跨阻放大器中可采用差动运算放大器以实现光电流到电压的转换，但是 CMOS 运算放大器的增益带宽积较低，要采用 CMOS 工艺实现高速的 PDIC 比较困难。反向器也可以作为放大器使用，推挽反向器由于两个晶体管都是由输入电压驱动，具有高的增益。同时，它可以实现轨到轨的输出摆幅<sup>[12]</sup>。与运算放大器相比，反向器有更高的带宽且占用芯片面积小。负反馈跨阻放大器的带宽、增益以及稳定性之间存在折衷。开环增益的增加可以提高负反馈跨阻放大器的带宽，采用单级反向器难以实现高带宽的要求，因此本文采用如图 3-7 所示的电路结构<sup>[13][14]</sup>。这样这个三级放大器和反馈电阻  $R_f$  就构成了互阻放大器。反馈电容  $C_f$  用来消除增益峰值。

图中以 MN1~MN5 和 MP1~MP3 构成的互补式自偏置差分放大器(CSDA) 作为输入级。MN6、MN7、MP4 以及 MN8、MN9、MP5 构成另两个推挽放大器。以下将对这两部分进行分析。

图 3-7 TIA 结构原理图

### 3.3.1 互补式自偏置差分放大器 (CSDA)

作为输入级的互补式自偏置差分放大器 (CSDA) 的结构如图 3-8 所示<sup>[13][14]</sup>。一个 NMOS 管输入差分放大器和一个 PMOS 管输入差分放大器去掉负载后连接在一起，并从 MP1 和 MN1 的漏极端引出  $V_b$  作为 MP3 和 MN3 的偏置电压，就构成了基本的 CSDA。

图 3-8 CSDA 结构图

MN3、MP3 的栅极都连接在 MP1 和 MN1 的漏极，这样构成的自偏置结构组成负反馈的环路，工艺参数、温度等因素的变化引起静态偏置电压的偏移都可以通过此负反馈得到修正，使静态工作点保持稳定。为了有尽可能大的输出摆幅，

MN3 与 MP3 工作在线性区,  $V_H$  和  $V_L$  可以分别接近 Vdd 和地电位, 这样 CSDA 的输出摆幅  $V_H - V_L$  就接近 Vdd。由于 CSDA 中 MN3 与 MP4 工作在线性区, 可以提供比静态电流更大的瞬态电流另外, 在传统的 CMOS 差分放大器中 MN3(或 MP4) 工作在饱和区, 其工作电流(静态电流)不变, 不可能提供很大的瞬态电流, 因此 CSDA 更适合于高速应用。CSDA 中有四个输入 MOS 管, 因此其差模电压增益约为传统差动放大器的两倍, 即

$$A_{vd} \approx \frac{g_{mn} + g_{mp}}{g_0} \quad (3.11)$$

其中,  $g_{mn}$  为 MN1 和 MN2 的跨导,  $g_{mp}$  为 MP1 和 MP2 的跨导,  $g_0$  为放大器的输出电导。

### 3.3.2 推挽反相器

图 3-9 所示为推挽反相器, M1 和 M2 的栅极相连作为输入端, 作为放大器使用时 M1 与 M2 都工作在饱和区。而二极管连接形式的 NMOS 作为有源负载, 用来降低每一级的增益, 稳定电路。M3 与 M2 并联也可以与 M1 并联, 但由于图 3-9 中 M3 的衬底和源极不相连, 即  $V_{BS} \neq 0$ , 体效应的作用将使 M3 的跨导  $g_m$  增加, 因此可以减小 M3 的尺寸; 同时, M3 尺寸的减小又可以减小输出端的电容, 有利于带宽的提高。

图 3-9 推挽反相器结构图

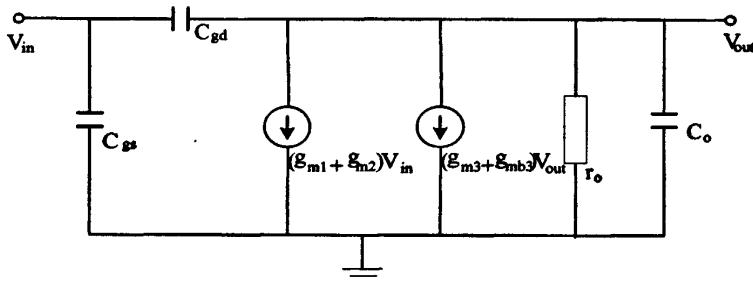

推挽反向放大器的完整小信号等效电路如图 3-10 所示。为了方便计算, 先将该图做简单的处理。令

$$C_{gd} = C_{gd1} + C_{gd2} \quad (3.12)$$

$$C_{gs} = C_{gs1} + C_{gs2} \quad (3.13)$$

$$r_0 = r_{01} \parallel r_{02} \parallel r_{03} \quad (3.14)$$

$$C_o = C_{bd1} + C_{bd2} + C_{gs3} + C_{bs3} \quad (3.15)$$

则小信号等效电路可以简化为如图 3-11 所示。

图 3-10 小信号等效电路图

图 3-11 简化的小信号等效电路图

在低频情况下根据图 3-11 可以得到:

$$(g_{m1} + g_{m2})V_{in} + (g_{m3} + g_{mb3})V_{out} = -V_{out} \quad (3.16)$$

因此单级推挽放大器的低频小信号电压增益为:

$$A_{v0} = -\frac{(g_{m1} + g_{m2})r_0}{1 + (g_{m3} + g_{mb3})r_0} \quad (3.17)$$

令 MOS 管 M1、M2 和 M3 的宽长比为:

$$B = \frac{(W/L)_{M1}}{(W/L)_{M3}} \text{ 和 } C = \frac{(W/L)_{M2}}{(W/L)_{M3}} \quad (3.18)$$

因为该放大器将用来实现负反馈结构，因此其输出电压必须等于输入电压，

$V_{in} = V_{out} = \frac{1}{2}V_{DD}$ ，所以 M1 和 M3 的  $(V_{gs} - V_{th})$  相等；且由于饱和 MOS 管的跨

导  $g_m = 2I_D/(V_{gs} - V_{th})$ , 则(3.17)式可近似表示为:

$$A_{v01} \approx -\frac{(g_{m1} + g_{m2})}{g_{m3}} = -\left[ B + (B-1) \frac{(V_{gs} - V_{th})_{M1}}{(V_{gs} - V_{th})_{M2}} \right] \quad (3.19)$$

同时, 根据基尔霍夫电流定律和饱和 MOS 管 I-V 特性方程有以下关系:

$$\frac{1}{2} \mu_p C_{ox} \left( \frac{W}{L} \right)_{M2} (V_{gs} - V_{th})_{PMOS}^2 = \frac{1}{2} \mu_n C_{ox} \left[ \left( \frac{W}{L} \right)_{M1} - \left( \frac{W}{L} \right)_{M3} \right] (V_{gs} - V_{th})_{NMOS}^2 \quad (3.20)$$

因此由以上分析可得低频情况下单级推挽放大器增益为

$$A_{v0} \approx -\left[ B + \sqrt{(B-1)C} \sqrt{\frac{\mu_p}{\mu_n}} \right] \quad (3.21)$$

由式 3.21 可以得到单级放大器的低频增益主要取决于 M1、M2 和 M3 管的宽长比的比值, 与各管具体的宽、长无关。但是为了减小的 MOS 管的寄生电容高带宽, 本文中的所有的 MOS 的沟道长度均取较小的数值或最小值。

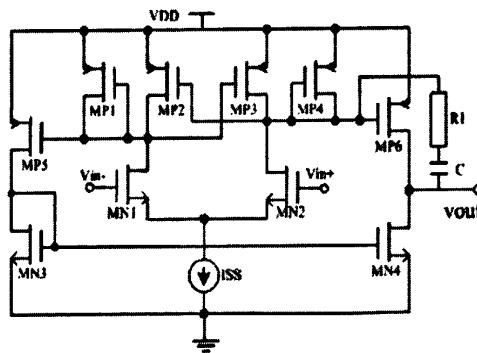

### 3.3.3 输出缓冲器与求和放大器

为了驱动 10PF 的电容和  $10 \text{ k}\Omega$  的电阻并联的负载, 采用了单位增益输出缓冲器<sup>[16]</sup>。输出缓冲器是另一种基本的放大电路, 其主要目的是有效地将信号提供给输出负载, 它要求具有高的输入电阻、高的输出摆幅、高的输出电流、低的输出阻抗、小的功耗以及小的相移等。

3-12 单位增益缓冲器与求和运放原理图

图 3-12 是一个两级运放构成的, 将反向输入端与输出端相连就构成了一个单位增益缓冲器。MN1、MN2 以及 MP1~MP4 构成输入级。MP2、MP3 交叉耦

合成为负电阻，这样把一组正向（MP1、MP2）与负向的二极管连接起来，其阻值为

$$\frac{2}{gm_2 - gm_1} \quad (3.22)$$

其中  $gm_1$ 、 $gm_2$  分别为 MP2、MP3 与 MP1、MP4 的跨导。因此用电流抵消技术可以容易控制这个差分阻值的大小，以实现很大的电阻。与普通的差分放大器相比可以达到更高的增益，可以实现满摆幅工作，经常被用于带宽放大器中，本文的就和放大器也是用此电路结构。

### 3.4 电路仿真与分析

本次电路设计采用 Cadence 中的 Spectre 仿真软件进行电路仿真。仿真结果包括交流仿真、暂态仿真以及噪声分析。仿真过程中探测器等效为一个电流源与  $0.3\text{pF}$  电容并联的整体。参考电压  $V_{ref}$  为  $2.5\text{V}$ ，电源电压为  $4.36\text{V}$ 。

#### (1) 交流仿真

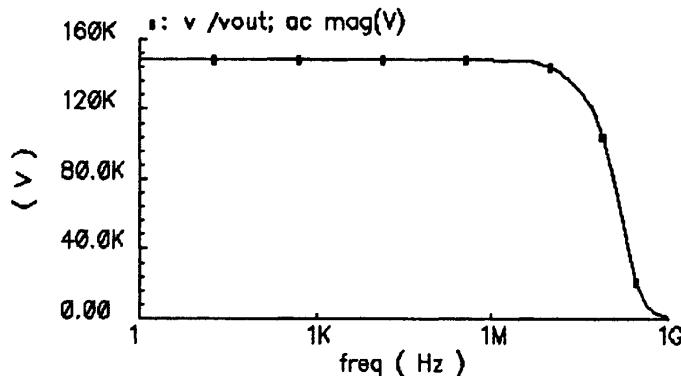

图 3-13 A~D 象限互阻放大器的交流仿真结果

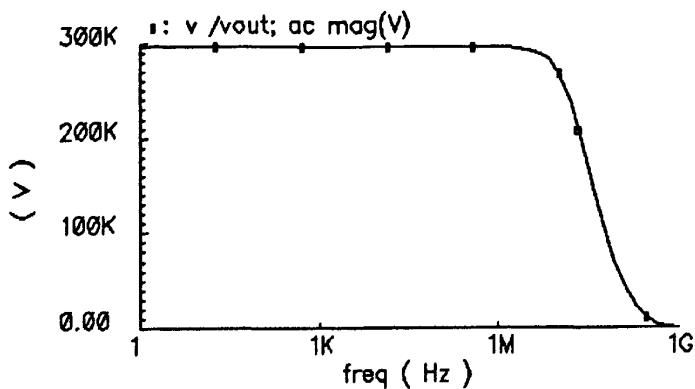

图 3-13 为 A~D 象限互阻放大器的交流仿真结果，其-3dB 带宽为  $79.2\text{MHz}$ ，跨阻增益达到  $150\text{K}\Omega$ 。图 3-14 为 E、F 象限互阻放大器的交流仿真结果，其-3dB 带宽为  $22.1\text{MHz}$ ，跨阻增益达到  $300\text{K}\Omega$ 。可以满足系统的要求。

图 3-14 E、F 象限互阻放大器的交流仿真结果

## (2) 瞬态响应

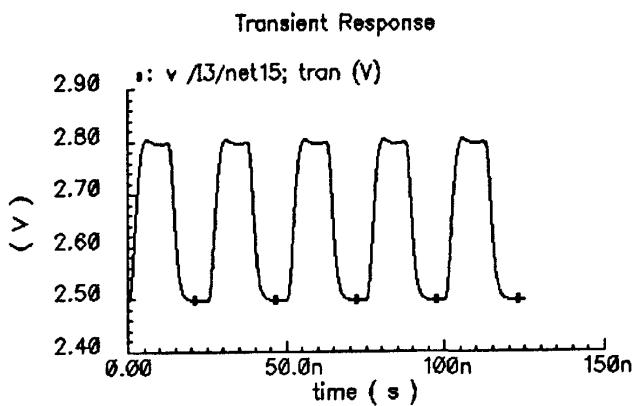

图 3-15 A~D 象限瞬态响应

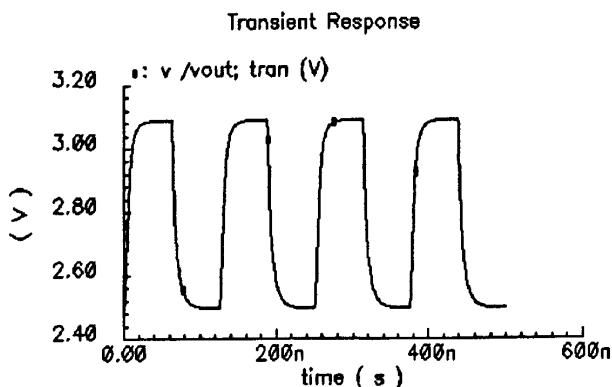

图 3-16 E、F 象限瞬态响应

图 3.15 给出了 PDIC 中 A~D 象限的脉冲响应特性，响应频率为 40MHz。

图 3-16 给出了 E、F 象限的脉冲响应特性，响应频率为 8MHz。从仿真结果可以看出，电路较好的瞬态响应。

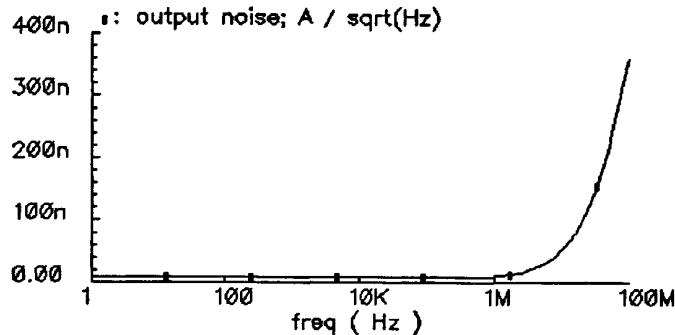

### (3) 噪声

跨阻抗放大器的等效输入电流噪声如图 3-17 所示。在低频下，等效输入电流噪声谱密度大约  $8.6\text{nA}/\sqrt{\text{Hz}}$ 。

图 3-17 TIA 的噪声特性

## 3.5 本章小结

本章着重分析了负反馈跨阻放大器的工作原理及特性，其几个重要的特性指标存在着相互制约。增大反馈电阻  $R_f$  可以提高跨阻增益和改善噪声特性，但降低了带宽，开环增益的增加可以提高带宽，但降低了电路的稳定性。考虑到与  $P^+/N\text{-EPI}/BN^+$  的匹配问题，设计了基于 CSDA 结构的三级跨阻放大器，并采用 spectre 仿真器对跨阻放大器进行了仿真。同时为了提高负载能力采用一个两级运放作为单位增益缓冲器。仿真结果表明：A~D 象限跨阻放大器-3dB 带宽为 79.2MHz，增益达到  $150\text{K}\Omega$ ；E、F 象限跨阻放大器-3dB 带宽为 22.1MHz，跨增益达到  $300\text{K}\Omega$ 。各项指标均能达到设计要求。

## 参考文献

- [1] Parker S, Shastry P. Transimpedance amplifiers for optoelectronic applications[J]. IEEE Microwave Magazine, 2001, 2(1): 52-62.

- [2] 陶蕤, 王志功, 董毅等. 2.5Gb/sCMOS 光接收机跨阻前置放大器[J]. 半导体光电, 2001, 22 (3): 177-180.

- [3] 王志功. 光纤通信集成电路设计[M]. 北京: 高等教育出版社, 2003.

- [4] ParkSM, PaPavassiliou C. On the design of low-noise, gigahertz bandwidth preamplifiers for optical receiver applications[C]. Proceedings of ICECS, 1999, 2(19): 785.

- [5] 张爱清. 用于光纤到户的 850nm 和 650nm 波长光纤收发器的研制[D]. 厦门: 厦门大学, 2006.

- [6] B. Wilson, J. D. Drew. Novel transimpedance amplifier formulation exhibiting gain- bandwidth independence[C]. IEEE Proc. Int. Symp. Circuits and Systems, 1997, 1(1): 169-172.

- [7] 谢嘉奎, 宣月清, 冯军. 电子线路线性部分 (第四版) [M]. 北京: 高等教育出版社, 1999.

- [8] Behzad Razavi 著, 陈贵灿等译. 模拟 CMOS 集成电路设计[M]. 西安: 西安交通大学出版社, 2003.

- [9] Michael Neuhauser, H-MRein. Low-Noise, High-Gain Si-Bipolar Preamplifiers for 10Gb/s Optical-Fiber Links-Design and Realization[J]. IEE, J.SSC, 2000,31(1):24-29.

- [10] David A.Johns,Ken Martin[著], 曾朝阳等[译]. 模拟集成电路设计[M]. 北京: 机械工业出版社, 2005.

- [11] 何乐年, 王忆. 模拟集成电路设计与仿真[M]. 北京: 科学出版社, 2008.

- [12] P. E. Allen, D. R.Holberg[著], 冯军等译. CMOS 模拟集成电路设计(第二版)[M]. 北京: 电子工业出版社, 2005: 145-146.

- [13] Mel Bazes. Two Novel Fully Complementary Self-Biased CMOS Differential Amplifiers[J]. IEEE Journal of Solid-State Circuits, 1991, 26(2): 165-168.

- [14] Hehemann I, Brockherde W, Hofmann H, et al. A Single-Chip Optical CMOS Detector With In-Situ Demodulating and Integrating Readout for Next-Generation

- Optical Storage Systems[J].IEEE Journal of Solid-Stated Circuits, 2004, 39(4): 629-635.

- [15] H. Zimmermann. Silicon Optoelectronic Integrated Circuits[M]. Berlin:Springer, 2004.

- [16] Willy M. C. Sansen[著], 陈莹梅译. 模拟集成电路设计精粹[M]. 北京: 清华大学出版社, 2008: 73-75.

## 第四章 低压 LDO 的设计

由于电源的扰动会对 TIA 产生一定的影响，为了给 TIA 提供一个稳定的电源，本文设计了一种低压降线性电压调整器（LDO，low dropout linear voltage regulator）。

### 4.1 LDO 概述

随着电子技术的发展，尤其是目前便携式产品的迅速发展，电源 IC 发挥的作用越来越大，同时电子市场对电源管理 IC 的需求也越来越高。当今，电子产品已普及到工作与生活的各个方面，其性能价格比愈来愈高，功能愈来愈强，供电的电源电路在整机电路中是相当重要的，电源电路的性能良好与否直接影响着整个电子产品的精度、稳定性和可靠性<sup>[1]</sup>。

LDO 线性稳压器，也称低漏失线性稳压器，是电源管理 IC 中的一种。它是一种降压型电压调节器，可将一宽输入范围内的电池电压转换成我们所需要的稳定电压。

LDO 线性稳压器不仅成本低，噪声低，静态电流小，而且需要的外围元件也很少，通常只需要一两个旁路电容，结构简单。如果输入电压和输出电压很接近，最好是选用 LDO 线性稳压器，可达到很高的效率。因此它在便携式电子产品中越来越受欢迎。同时，它在调整元件上的压降非常低，比传统的线性稳压器有更高的电源转换效率。LDO 的纹波很小，它过滤了电路中的瞬变和噪声，对其驱动的电路起到保护作用<sup>[2]</sup>。LDO 电路工作在线性模式且没有使用电感，因此没有电磁干扰（EMI）的问题。所以 LDO 常用来驱动微控制器、存储器、低压逻辑等对电源波动比较敏感的电路。

自从 90 年代出现 LDO 线性稳压器以来，已从最初的输入/输出压差 0.2V 降至目前的几十毫伏，这样调整管的损耗小，提高了输入电源的转换效率，延长了电池的寿命。自 LDO 线性稳压器问世以来，人们已对它进行了大量的研究和改

进产品层出不穷，性能越来越优越，应用也越来越广泛。目前，低压低功耗 LDO 的设计采用深亚微米数字 CMOS 工艺，需要在更小尺寸上实现更多的功能，并且对功耗、设计周期具有更高要求。所谓深亚微米指的是工艺尺寸在 0.25 微米及其以下的，这是目前国际上集成电路的主流生产工艺<sup>[1-3]</sup>。

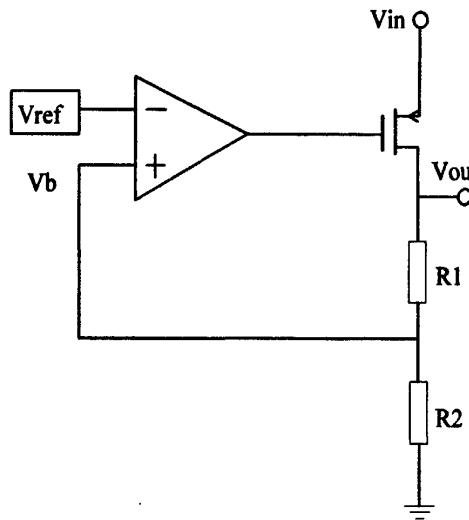

## 4.2 LDO 结构与原理

LDO 是一种线性电压调节器，主要由基准电压源(BGR)、误差放大器(Error Amplifier)、调整管(Pass Element)和反馈网络(Feedback Network)组成。此外，为了实现使能控制、过温、限流保护功能，还可以增加使能电路和过温、限流保护电路。导通器件可以选择 NPN 管，PNP 管，复合管(Darlington 管)，NMOS 管。由于 PMOS 管的落差电压最小所以本文采用 PMOS 作为调整管<sup>[4]</sup>。一个典型的 LDO 线性稳压器简化系统框图如图 4-1 所示。

图 4-1 LDO 结构原理图

LDO 的目的是提供可靠、恒定的电源电压。当电源上电时，基准电压源正常工作，为误差放大器的反相输入端提供一个精确的参考电压  $V_{ref}$ ，输出电压  $V_{out}$ ，经过反馈电阻  $R_1$  和  $R_2$  分压后产生反馈电压  $V_b$ ，将其接入误差放大器的同相输入端。误差放大器比较  $V_{ref}$  和  $V_b$  大小，将两电压之差放大后驱动调整管，通过改变调整管的输出电流，使反馈电压  $V_b$  等于基准电压  $V_{ref}$  从而使输出电压稳定。

在一个固定的电压值<sup>[5]</sup>。

由以上分析可见，我们可以将整个 LDO 线性稳压器看成一个负反馈网络。设 LDO 线性稳压器的开环放大倍数为 A，反馈系数为 F，则稳压器的输出电压为：

$$V_{out} = \frac{A}{1+AF} V_{ref} \quad (4.1)$$

在实际电路中有  $A \gg 1$ ，因此

$$V_{out} \approx \frac{V_{ref}}{F} = \frac{R_1 + R_2}{R_2} V_{ref} \quad (4.2)$$

由此可见其输出电压只取决于基准电压和反馈系数，而与输入电压和负载电流的大小无关。

### 4.3 主要性能指标

主要的设计参数是 LDO 整体性能的衡量标准，通过对设计参数的推导，可以了解各参数的决定因素以及参数之间的关系，从而在设计电路过程中更好的均衡考虑参数的设计，最终设计出一个高性能的线性稳压器<sup>[6-7]</sup>。下面对 LDO 设计过程中所需要考虑的主要指标进行简要的说明。

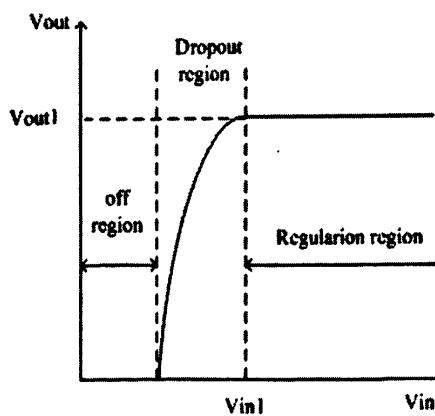

#### (1) 落差电压 $V_{dropout}$

图 4-2 落差电压原理图

LDO 线性稳压器只有在输入电压大于输出电压一定数值时，系统才具有保证输出电压稳定的能力。当输入电压减小到某一临界值时，系统失去对输出电压

的调整能力。落差电压  $V_{dropout}$  就定义为该临界值时输入电压与输出电压之间的差值, 如图 4-2 所示。即:

$$V_{dropout} = V_{in1} - V_{out1} \quad (4.3)$$

早期采用 NPN 达林顿管作为调整管, 其压差在 2.5V~3V 之间; 改用 PNP 和 NPN 结构后, 其压差降为 1.2V~1.5V 之间; 在现代低压线性变换器中多采用功率 MOSFET, 其压差可降至零点几伏。

### (2) 静态电流

静态电流定义为输入电流与输出电流之差, 它的大小决定了 LDO 自身的功耗, 影响 LDO 的转换效率, 此电流为除负载之外其它模块所消耗的电流。其计算如下:

$$I_q = I_{in} - I_{out} \quad (4.4)$$

静态电流包括各种偏置电流和电压调整管的驱动电流, 偏置电流为 LDO 各部分功能模块供电。对于设计来说总是希望静态电流越小越好在满足设计的主要性能不受影响的情况下, 要想提高电流的使用效率, 应尽可能减小 LDO 内部各模块的偏置电流。

### (3) 效率

效率定义为输出功率与输入总功率之比, 反映了 LDO 对电源能量的有效利用率, 表达式如下:

$$\eta = \frac{I_{out}V_{out}}{(I_{out} + I_q)V_{in}} \times 100\% \quad (4.5)$$

其中,  $V_{out}$  是输出电压,  $I_{out}$  是输出电流,  $I_q$  为静态电流,  $V_{in}$  为输入电压。因此  $\eta$  反映了 LDO 对电源能量的有效利用率。

### (4) 线性调整率

线性调整率是指输入电压变化时, 输出电压相对于输入电压的变化率。它是衡量输出电压对输入电压变化的抑制能力。该值越小, 说明输入电压的变化对输出电压的影响越小, LDO 的性能越好<sup>[8]</sup>。定义为:

$$S_i = \frac{\Delta V_{out}}{\Delta V_{in}} \times 100\% \quad (4.6)$$

其中,  $\Delta V_{in}$  为输入电压变化,  $\Delta V_{out}$  为输出电压变化。若 LDO 外接负载  $R_L$ , 则

其与反馈电阻  $R_1 + R_2$  并联, 等效电阻为:

$$R_{eq} = R_L \parallel (R_1 + R_2) \quad (4.7)$$

若误差放大器的开环差模增益为  $A_v$ , 功率调整管的跨导为  $g_m$ , 以  $R_{ds}$  表示输入端到输出端的等效电阻, 则输入电压发生变化后, LDO 的输出可表示为:

$$\begin{aligned} V_{out} &= \frac{R_{eq}}{R_{eq} + R_{ds}} V_{in} - \Delta V_{out} = \frac{R_{eq}}{R_{eq} + R_{ds}} V_{in} - \Delta I_{out} R_{eq} \\ &= \frac{R_{eq}}{R_{eq} + R_{ds}} V_{in} - g_m A_v (V_b - V_{ref}) \\ &= \frac{\frac{R_{eq}(R_1 + R_2)}{R_{eq} + R_{ds}} V_{in} + g_m A_v V_{ref} R_{eq} (R_1 + R_2)}{R_1 + R_2 + g_m A_v R_{eq} R_2} \end{aligned} \quad (4.8)$$

通常认为故忽略  $R_1 + R_2 + g_m A_v R_{eq} R_2 \gg R_1 + R_2$  因此:

$$V_{out} = \frac{R_1 + R_2}{g_m A_v R_{eq} R_2} + \frac{R_1 + R_2}{R_2} V_{ref} \quad (4.9)$$

两边对  $V_{in}$  求导, 得线性调整率为:

$$S_l = \frac{R_1 + R_2}{(R_{ds} + R_L) g_m A_v R_2} \quad (4.10)$$

由式(4.10)可以看出增大误差放大器的增益  $A$  和调整管的跨导  $g_m$ , 可以提高 LDO 的线性调整率。

### (5) 负载调整率

LDO 线性稳压器的负载调整率即负载调整能力, 表示当负载发生变化时, 输出电压保持恒定的能力。假设负载电流变化为  $\Delta I_{out}$ , 输出电压变化为  $\Delta V_{out}$ ,

负载调整率定义为<sup>[9]</sup>:

$$S_o = \frac{\Delta V_{out}}{\Delta I_{out}} \times 100\% \quad (4.11)$$

当误差放大器的同相输入端变化  $\Delta V_b$  时,

$$\Delta I_{out} = \Delta V_b A_v g_m \quad (4.12)$$

$$\Delta V_b = \frac{R_2}{R_1 + R_2} \Delta V_{out} \quad (4.13)$$

可得负载调整率为：

$$S_o = \frac{1}{A_v g_m} \left( \frac{R_1 + R_2}{R_2} \right) \quad (4.14)$$

### (6) 电源抑制比 (PSRR)

电源抑制比是反映 LDO 线性稳压器的输出电压对输入电压纹波抑制能力，它反映 LDO 对输入纹波抑制的交流特性。电源抑制比的值越大，说明 LDO 的纹波抑制能力越强，即输入对输出的影响越小。电源抑制比定义为：

$$PSRR = 20 \lg \left( \frac{\Delta V_{out}}{\Delta V_{in}} \right) \quad (4.15)$$

LDO 的电源抑制主要与基准电压源和误差放大器的 PSRR 有关。

## 4.4 主要电路模块设计

上面已对 LDO 基本组成进行了详细介绍，以上将重点阐述带隙基准和误差放大器的设计。

### 4.4.1 带隙基准电路的设计

LDO 电路利用基准电压作为参考电压来和输出电压的反馈值做比较，并将其误差放大通过负反馈来调整输出电压。因此它是整个 LDO 线性稳压器的一个核心部分，其性能好坏直接影响着 LDO 输出电压的精度，它的精度和稳定性等性能将直接影响到 LDO 的性能<sup>[10]</sup>。

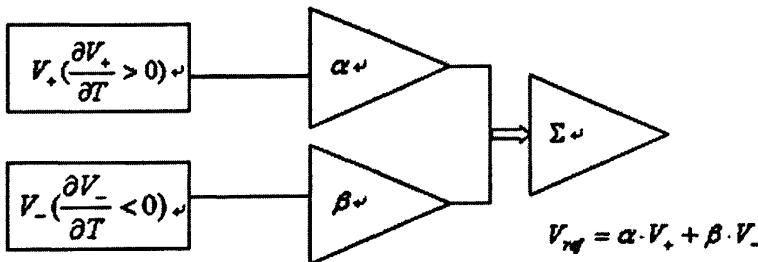

#### (1) 带隙基准电路原理

带隙电压基准的基本要求是将两个拥有相反稳定系数的电压以合适的权重相加，最终获得具有零温度系数的基准电压。例如， $V_+$ 拥有正温度系数，电压  $V_-$  拥有负温度系数，存在合适的权重  $\alpha$  和  $\beta$  满足：

$$\alpha \cdot \frac{\partial V_+}{\partial T} + \beta \cdot \frac{\partial V_-}{\partial T} = 0 \quad (4.16)$$

这样就得到具有零温度系数的基准电压，其原理如图 4-3 所示。基准电压的基本表达式为： $V_{ref} = \alpha V_+ + \beta V_-$ 。

图 4-3 带隙电压基准的一般原理图

双极性晶体管（BJT）有以下两个特性：(1) 双极型晶体管的基极-发射极电压 ( $V_{BE}$ ) 电压与绝对温度成反比；(2) 在不同的集电极电流下，两个双极型晶体管的基极-发射极电压的差值 ( $\Delta V_{BE}$ ) 与温度成正比。因此，双极晶体管构成了带隙电压基准的核心<sup>[11-12]</sup>。

## (2) 负温度系数电压

对于双极型号晶体管，其集电极电流与基极-发射极电压的关系为：

$$I_C = I_s [\exp(\frac{V_{BE}}{V_T}) - 1] \approx I_s \exp(\frac{V_{BE}}{V_T}) \quad (4.17)$$

其中， $I_s$  是双极型晶体管的饱和电流为： $I_s = C_0 T^{4-n} \exp(-\frac{E_g}{V_T})$ ； $V_T = \frac{kT}{q}$ ， $k$  为

玻尔兹曼常量， $q$  为电子电荷。对两边  $I_s$  对  $T$  求导得到：

$$\frac{\partial I_s}{\partial T} = C_0 (4-n) T^{3-n} \exp(-\frac{V_g}{V_T}) + C_0 T^{4-n} \exp(-\frac{V_g}{V_T}) \left( \frac{E_g}{kT^2} \right) \quad (4.18)$$

由式 4.16 和 4.17 可得

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln \frac{I_c}{I_s} - \frac{\partial I_s}{\partial T} \frac{V_T}{I_s}$$

$$\begin{aligned}

&= \frac{V_T}{T} \ln \frac{I_c}{I_s} - (4-n) \frac{V_T}{T} - \frac{E_g}{kT^2} V_T \\

&= \frac{V_{BE} - (4-n) - E_g/q}{T}

\end{aligned} \tag{4.19}$$

其中， $m \approx -1.5$ ,  $E_g = 1.12eV$  是硅的带隙能量。当  $V_{BE} \approx 750mV$ ,  $T = 300K$  时,

$$\frac{\partial V_{BE}}{\partial T} = -1.5mV/^{\circ}C。$$

### (3) 正温度系数电压

如果两个晶体管 ( $I_{s1} = I_{s2} = I_s$ ,  $I_s$  为双极晶体管饱和电流) 偏置的集电极电流分别为  $nI_0$  和  $I_0$ , 并忽略它们的基极电流, 那么它们的基极-发射极电压差值为:

$$\Delta V_{BE} = V_{BE1} - V_{BE2} = V_T \left( \ln \frac{nI_0}{I_{s1}} - \ln \frac{I_0}{I_{s2}} \right) = V_T \ln n \tag{4.20}$$

因此,  $V_{BE}$  的差值就表现出正温度系数

$$\frac{\partial \Delta V_{BE}}{\partial T} = \frac{k}{q} \ln n > 0 \tag{4.21}$$

可以看出这个温度系数与温度及集电极电流的特性无关。

### (4) 基准电压零温度系数的实现

利用上面的正、负温度系数的电压, 可以设计出一个在一定温度范围内的零温度系数的基准电压, 有:

$$V_{ref} = \alpha \cdot V_{BE} + \beta \cdot (V_T \ln n) \tag{4.22}$$

由于  $\partial V_{BE}/\partial T \approx -1.5mV/^{\circ}K$ ,  $\partial V_T/\partial T \approx 0.087mV/^{\circ}K$ , 因此只要令  $\alpha = 1$  就可以得到零温度系数的  $V_{ref}$ 。

$$\beta \cdot (\ln n) (0.087mV/^{\circ}K) = 1.5mV/^{\circ}K \tag{4.23}$$

得到  $\beta \cdot (\ln n) \approx 17.2$

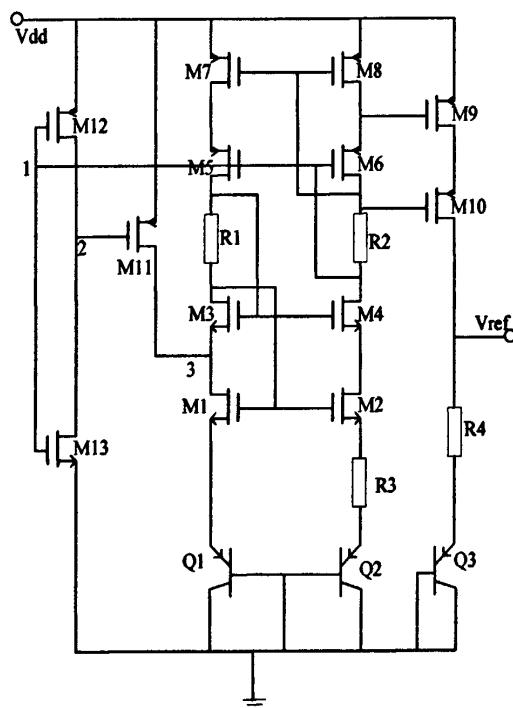

### (5) 带隙基准主体电路

为了实现低功耗, 带隙基准的核心电路及启动电路等各个组成部分都采用的

是非常简洁的结构,带隙基准电路的整体电路结构如图 4.4 所示<sup>[1][2]</sup>。为了使得流过  $Q_1$ 、 $Q_2$  的电流相等,  $M1 \sim M8$  管通过共源共栅连接。 $Q_2$  的发射极面积是  $Q_1$  的  $K > 1$ , 其取值要根据版图的匹配性综合考虑。设计中引入了自偏置共源共栅结构, 可以避免由于 MOS 器件的沟道长度调制造成电源抑制比的下降。为了避免  $M1 \sim M8$  的栅端电压使用额外偏置电压, 这个设计引入自偏置共源共栅结构, 图中  $R_1$  和  $R_2$  维持适当的电压, 使所有的 MOS 管都保持在饱和态。

图 4-4 带隙基准电路

在基准源电路中有个很重要的问题就是启动问题, 因为基准源电路有可能存在电路“简并点”, 所谓的简并点就是, 在上电过程中, 电路中所有晶体管可以无限期的保持关断状态, 因为这样也符合电路的约束条件。所以要保证上电的过程不发生这样的情况, 就需要启动电路破坏这个简并点。在电路上电的时候, 启动电路就开始工作, 向需要启动的电路注入电流, 破坏电路的简并点, 使电路进入正常的稳定工作状态。当上电完成后, 启动电路就关闭, 以节省功耗。图 4-4 中的  $M11 \sim M13$  构成了基准的启动电路, 电源上电时节点 1 高电位  $M13$  导通, 节点 2 电位被拉低, 而  $M11$  导通, 基准进入正常工作状态。而后节点 1 电位降低  $M13$  关断, 节点 2 电位拉高  $M13$  关断, 整个启动电路关断。

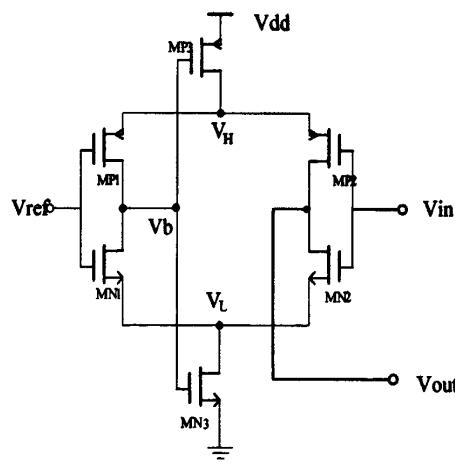

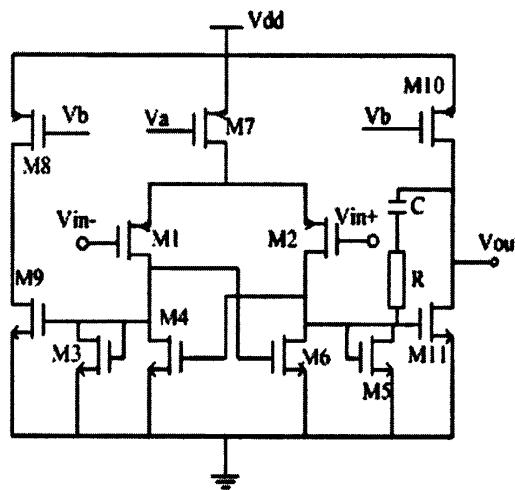

#### 4.4.2 误差放大器

在 LDO 线性稳压器中，误差放大器用来比较输出反馈取样信号与基准电压，并将差值信号经放大后，输出到调整管的输入端，控制调整管的工作状态，使输出电压保持稳定。误差放大器是一个非常重要的模块，它的性能会在很大程度上影响整个 LDO 芯片的性能，如线性调整率、负载调整率等。本文采用的运放如图 4-5 所示。这是一个两级运放 M1~M7 组成差分输入级，M4、M6 组成负电阻，M8~M11 为第二级。由于两级运放一般是不稳定系统，因此采用米勒电容和电阻串联的形式作为补偿。

图 4-5 误差放大器

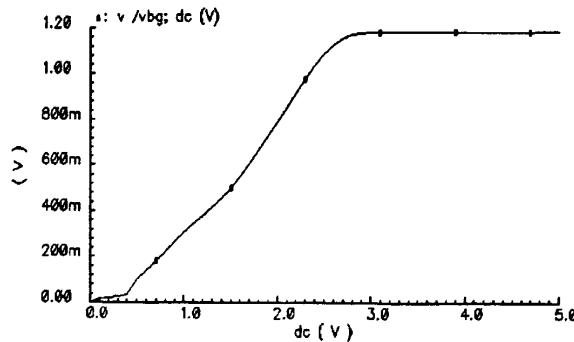

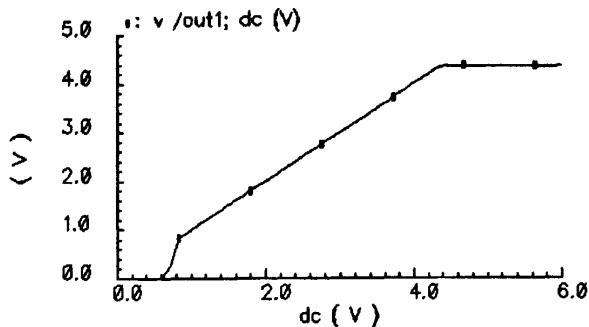

#### 4.5 仿真分析

##### (1) 直流特性

图 4-6 带隙基准输出电压随电源电压的变化

图 4-6 是基准电压随输入电压的变化曲线图。当电源电压大于 2.5V 基

准电压正常工作图。图 4-7 为 LDO 输出电压随电源电压的变化关系图，从图可以看出当 LDO 正常工作时输出电压可以稳定在 4.36V，满足系统的要 求。

图 4-7 LDO 输出电压随电源电压的变化

## (2) 温度特性：

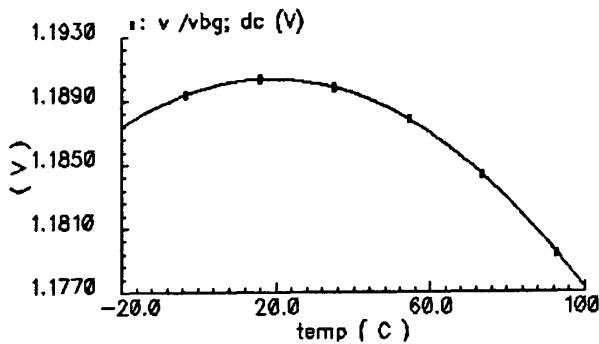

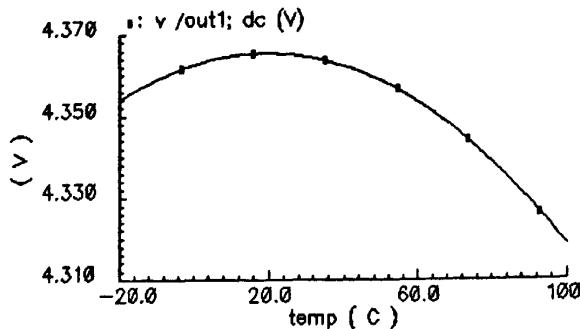

图 4-8 基准电压的温度特性仿真

图 4-9 LDO 的稳定特性仿真

图 4-8 所示为基准电压随温度的变化仿真结果，输入电压为 5V，温度的变 化范围从  $-20^{\circ}\text{C}$  变化到  $100^{\circ}\text{C}$ ，温度系数为  $2.5 \text{ ppm}/^{\circ}\text{C}$ 。图 4-9 为 LDO 随温度 的变化关系曲线图，其趋势与图 4-8 很极相似，因而可以看出基准电压性能对于

LDO 影响很大。

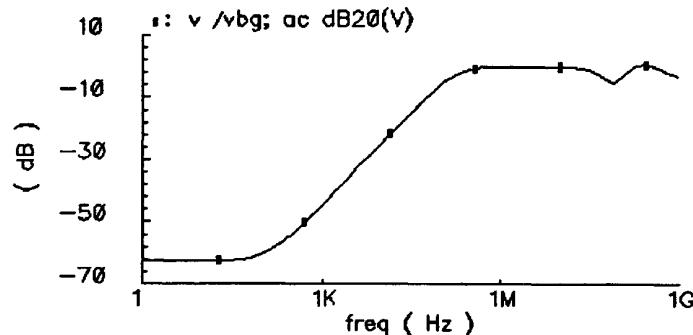

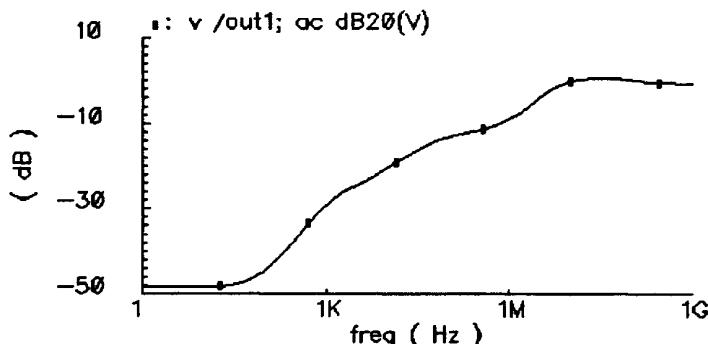

### (3) 电源抑制比:

图 4-10 为基准电压的电源抑制比，在 100Hz 时电源抑制比为-63dB。图 4-11 为 LDO 的电源抑制比，在 100Hz 时电源抑制比为-50dB。

图 4-10 基准电压的电源抑制比

图 4-10 为基准电压的电源抑制比，在 100Hz 时电源抑制比为-63dB。图 4-11 为 LDO 的电源抑制比，在 100Hz 时电源抑制比为-50dB。

图 4-11 LDO 电源抑制比

## 4.6 本章小结

为了防止电源干扰对 TIA 的影响，本章设计了低压 LDO。本章分析了低压 LDO 的工作原理和各种性能指标，以及低压结构中各个模块的特点后提出的一种低压 LDO。重点讨论了其关键模块基准电压及误差放大器的设计。电路仿真结果表明，所设计的 LDO 输出电压为 4.36V，具有较好的电源抑制比。通过对整个芯片的测试表明 LDO 可以为 TIA 提供较为稳定的电源，达到了设计的目的。

## 参考文献

- [1] 白文娟. 一种新型的低压 LDO 的设计[D]. 苏州: 苏州大学, 2010.

- [2] Lee H, Mok P K T. Design of low-power analog drivers based on slew-rate enhancement circuits for CMOS low-dropout regulators[J], IEEE Trans Circuits Systems II: Express Briefs, 2005, 52(9): 563-567.

- [3] Kwok K C, Mok P K T. Pole-zero tracking frequency compensation for low dropout regulator[J], IEEE International Symposium on Circuits and Systems, 2002, 4: 735–738.

- [4] Gabriel A, Rincon-Mora. A low-voltage, low quiescent current, low drop-out regulator [J]. IEEE Journal Of Solid-State Circuits, 1998, 33(1): 71-74.

- [5] 柳娟娟. 低压差线性稳压器中核心模块的设计[D]. 成都: 西南交通大学, 2007.

- [6] 曲光阳. 低功耗高稳定性 LDO 的研究与设计[D]. 浙江:浙江大学, 2008.

- [7] 范东风. 高性能 LDo 线性稳压器的设计[D]. 大连:大连理工大学, 2008.

- [8] 刘其贵, 李建中, 郭振东等. CMOS 单片 LDO 线性稳压器的设计[J]. 电路与系统学报. 2002, 7(4): 5-8.

- [9] Ramy, Tantawy, Elizabeth, J. Brauer. Performance Evaluation of CMOS low drop-out Voltage Regulators[J]. IEEE International Midwest Symposium on Circuits and Systems. 2004: 141-144.

- [10] 付秀兰. 高性能 CMOS 低压差线性稳压器的设计[D]. 合肥: 合肥工业大学, 2009.

- [11] Behzad Razavi[著], 陈贵灿, 程军, 张瑞智等译. 模拟 CMOS 集成电路设计[M].西安: 西安交通大学出版社, 2003.

- [12] Sanborn K, Mads, Ivanov V. A Sub-1V low-noise bandgap voltage reference[J]. IEEE Journal of Solid-State Circuits. 2007, 42(11): 2466-2481.

- [13] R.Jacob Baker[著], 刘艳艳, 张为等译. CMOS 电路设计、布局与仿真(第二版第二卷) [M]. 北京: 人民邮电出版社, 2008.

## 第五章 版图设计

在完成电路设计后，将进行版图设计。在整个设计过程中，版图（layout）设计或者称作物理设计（physical design）是其中重要的一环。它是把每个原件的电路表示转换成集合表示，同时，元件间连接的线网也被转换成几何连线图形。本章结合CSMC 0.5μm BCD工艺的PDK介绍版图设计的工具及流程，讨论版图设计方法与注意事项，完成PDIC的版图设计。

### 5.1 设计流程

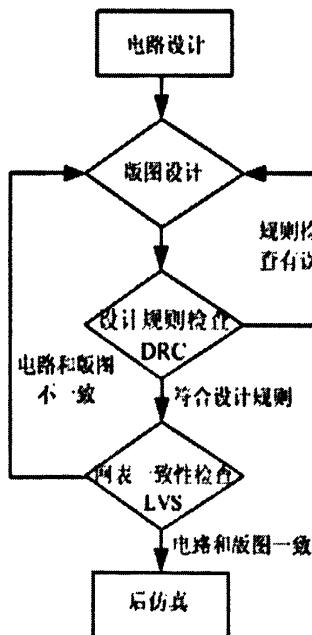

版图是指芯片制造时所用的掩膜上的几何图形，包含了尺寸大小、各层拓扑定义等有关器件的所有物理信息，每一种版图层对应一块掩膜版<sup>[1]</sup>。设计者将设计并仿真优化后的电路转化成一系列层次化的几何图形，每层版图的形状、大小和位置都必须精确设计，同时版图设计还受到制造方设计规则的制约。

图5-1 版图设计流程

集成电路开始到现在经历了小规模集成，中规模集成，大规模集成，到目前的超大规模集成。单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。集成度的提高对于版图的设计要求也越来越高，版

图的设计已经成为了影响芯片性能甚至功能能否实现的重要因素。芯片设计是否能够成功很大程度上取决于版图设计的优劣。在集成电路设计中，从版图往后的设计称为后端设计，包括版图设计与后仿真，其设计流程如图5-1所示。这个过程可简单概括为<sup>[2][3]</sup>：

(1) 明确电路功能，划分模块。首先明确各个电路模块的功能，哪些功能块之间要放在比较近的位置。哪些器件需要良好的匹配。了解该芯片的电源线和地线一共有几组，每组之间各自是如何分布在版图上的。根据电路图画个布局图，然后根据模块的面积大小进行调整。划分成若干个模块，可以将处理问题的规模缩小。

(2) 分层设计。按照电路功能划分好的电路模块进行设计，可以对每个功能块进行再划分，每一个模块对应一个单元。从最小模块开始到完成整个电路的版图设计，设计者需要建立多个单元。

(3) 版图的检查。采用版图验证工具对设计版图依次进行设计规则检查(Design Rule Checking, DRC)、电学规则检查(Electronics Rule Checking, ERC)、版图与电路图对照(Layout Versus Schematic, LVS)验证。DRC是检查版图是否符合设计规则，并给出错误提示。ERC是检查版图的电路拓扑结构、元件等电学错误。LVS是检查由版图提取出的电路信息与电路图是否一致，并给出错误提示。版图的验证采用自底向上的方法。

(4) 总体布线。根据所设计的电路结构，按照节省面积、可测试的原则，完成模块间的互连。进行整个电路的版图设计和验证，并在版图的外围布上焊盘。完成版图的整体设计实现最优布局。

(5) 下定单。确认版图设计无误后，将版图生成GDSII文件，这是目前工业上标准版图数据文件格式。芯片制造厂家根据GDSII文件来制造掩膜，进而制造芯片。

## 5.2 版图设计注意事项

版图设计包括数字集成电路的版图设计和模拟集成电路的版图设计，这两者在版图设计上所要考虑侧重点不一样。而且不同的电路所实现的功能和特性不同，在版图设计时所要注意的事项也不一样。即版图的设计总是和电路息息相关

的。数字电路的版图设计一般都采用自动布局布线来完成，可以不要太多的关注电路的工作情况。模拟电路则不同，一般都是采用手工设计，在版图设计时要更多的了解电路的工作情况。模拟电路版图设计是根据电路进行的，在设计版图之前，作为版图设计者必须先了解这个电路实现的功能，以及流过电路的电流大小和匹配问题，还有就是寄生参数等很多问题。

### (1) 电路功能和电流大小

电路的功能，对于版图设计者来说是至关重要的，它决定了版图设计的布局、隔离、匹配、放置、平衡、交叠、保护电路的设计、输入输出的引线的位置等。工艺中有很多的寄生参数主要包括寄生电容、电阻和电感等。这些寄生参数会影响到整个芯片的性能。电路仿真中，往往不考虑电路中各个部分的连线电阻，将其视为零。但是，在版图设计中各个连线有着自己的寄生电阻。为防止寄生大电阻对电路性能的影响，电路中尽量不走长线。寄生电容会增加电路的延迟，影响电路速度，信号线之间的耦合电容会引入信号间的串扰，影响电路的稳定性。寄生电容分为连线电容和有源区寄生电容。金属层数越高，寄生电容越小，因此较长的高频信号线采用高层金属可以减小寄生电容的影响。金属连线的寄生电容中边缘电容占主要部分，因此应尽量避免相邻的两条信号线平行走线。有源区的寄生电容远大于金属的寄生电容，在版图设计中，可以采用叉指形结构的 MOS 管来减小有源区寄生电容的影响。电路的功能决定了如何有选择的忽略某些寄生参数，或是着重注意某些寄生参数以减少寄生因素对整体性能的影响。

同时电流的大小，将决定你对器件和大多数金属线宽度的选择，以及影响到整体布局。这是由于在工艺中，一根金属所承受的电流能力是有限的。CSMC 的 BCD 工业提供的 PDK 中，如果用三层金属时，第一、二层金属所能承受的电流密度约为  $0.8 \text{ mA}/\mu\text{m}$ ，而第三层金属能承受的电流密度则为  $1.5 \text{ mA}/\mu\text{m}$ <sup>[4]</sup>。由于 PDK 中所提供的晶体管版图都是按最小尺寸来设计，如有大电流要流入晶体管，晶体管的源漏极金属引线会因为宽度太小从而被大电流流过融断，因此可以把晶体管设计成几个来分担电流，或是把晶体管设计成叉指状。

### (2) 匹配问题

模拟电路中对许多器件的匹配有很高的要求，精度和性能通常取决于元件匹配精度如作为运放输入的差分对管、电流镜等。在集成电路中，集成元件的绝对

精度较低，如电阻和电容，误差可达 $\pm 20\% \sim 30\%$ 。但是由于芯片面积很小，其经历的加工条件几乎相同，如果匹配做的到位同一芯片上的集成元件可以达到比较高的匹配精度，如1%，甚至0.1%以下总结了下一些匹配的原则<sup>[5-7]</sup>。

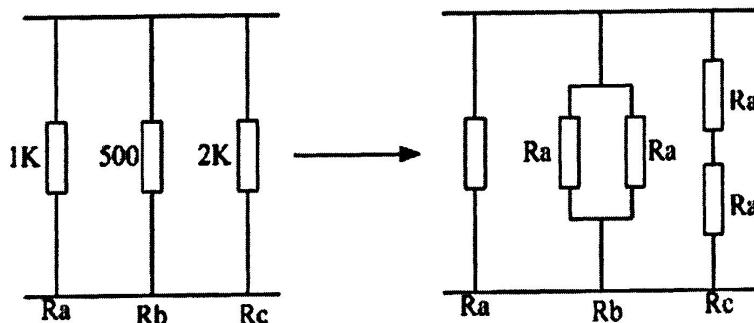

根器件法，如图5-2所示。图中以Ra为基准，来构成Rb和Rc可以获得良好的匹配。此方法也适用于其他类型器件。

图5-2 根器法

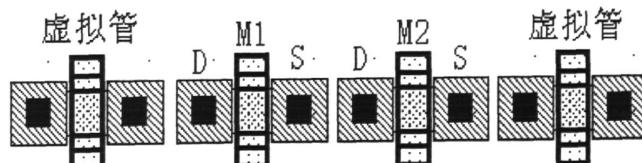

虚拟元器件。在不同环境中的器件会有可见的失配发生，目前造成这个结果的原因还不是很清楚，但是这个问题可以通过在周围放置无用的器件，使得匹配器件的周围环境一样来解决，这就是通常所说的dummy。dummy器件要保持电气连接，因为dummy器件与原器件之间的隔离氧化物是良好的绝缘体，dummy器件上堆积的电荷将影响原器件内部电荷的分布，一般的方法是将dummy器件接全局的静电位即电源或地。如图5-3 所示，标志为M1、M2 的器件都是电路设计中实际应用到的器件。为了使器件处在同样的环境下，在两边分别加了两个虚拟器件。如果需要可以在器件的四周都放置虚拟器件，虚拟器件的大小不需要和电路中实际用的器件一样，只要和他们相邻就可以。

图5-3 虚拟器件

相同的方向。各向异性的工艺步骤会引起工艺参数的不对称性，并且硅衬底本身也具有各向异性的特性。这个原因引起的失配可以通过将匹配器件放在同一个方向上来解决。

共质心排列。将一个匹配器件分成完全相同的单元，且排列成一个对称结构，

那么器件的重心将位于穿过阵列的对称轴的交叉处。将两个或多个匹配器件按一定的顺序排列，使它们具有相同的质心点，称为共质心排列。共质心排列可使得由压力梯度引起的不匹配影响最小化。MOS管的共质心排列时还需注意应尽量合并漏区，因为在一般的电路中  $C_{gd}$  由于密勒效应，对电路的影响较大，应通过合并减小漏区面积，从而减小电容  $C_{gd}$ 。

### (3) 可靠性设计

**天线效应。**在刻蚀多晶硅和氧化层边缘的时候，电荷可能会积累在多晶硅上，所积累的电荷量与多晶硅的面积成正比。如果一个MOS管的栅极连接在一个大面积的多晶硅线上，积累电荷产生的电压可能会破坏栅氧化层。此时的多晶硅线就像天线一样收集电荷，故称天线效应。跳线插入，是防止天线效应的最普遍的方法<sup>[8]</sup>，如图5-4所示。

图5-4 跳线插入

可以看到本来连线的长度过长，通过插入jumper改变了连线方式。从改变后的连接方式分析，在生成连线M时，由于N还没有被生成，所以M不与栅G连通，其上积累的电荷也不会对栅G产生影响，因此只要在距离栅G比较近的地方插入jumper，使M和N都较短，就可以避免天线效应的出现。

**闩锁（Latch-up）效应。**闩锁效应是CMOS工艺特有的寄生效应，严重时会导致电路的失效，甚至会烧毁芯片。闩锁效应是由CMOS工艺中NMOS的有源区、P衬底、N阱和PMOS的有源区构成的n-p-n-p结构产生的，当其中一个三极管正偏时，就会构成正反馈形成闩锁<sup>[9]</sup>。在版图设计时，多增加P衬底接触孔和N阱接触孔的数目，并且衬底接触孔和N阱接触孔的间隔都应当尽量小，可以有效地提高抗闩锁效应的能力，也可以采用保护环来克服闩锁效应。同时使用保护环（Guard ring）抑制闩锁效应是目前应用最广泛的方法，本次版图设计就是使用保护环来防止闩锁效应。

**ESD保护。**当外部高电势的带电体接触到芯片的外引脚时会发生静电放电

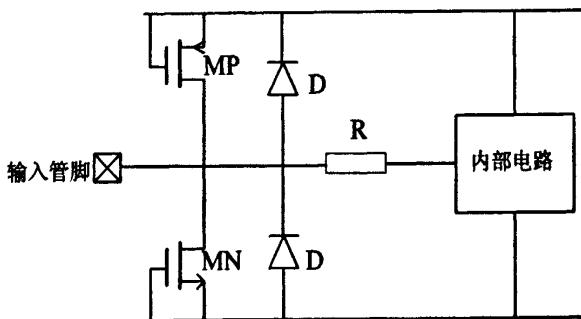

(Electrostatic Discharge, ESD) 现象，可能毁坏芯片上的器件。电子组件或系统在制造、生产、组装、测试、存放、搬运等的过程中，静电会累积在人体、仪器、储放设备等之中，甚至在电子组件本身也会累积静电，而人们在不知情的情况下，使这些物体相互接触，因而形成了放电路径，使得电子组件或系统遭到静电放电的肆虐。因此芯片常使用ESD保护电路，图5-5是一种常见的保护电路<sup>[5]</sup>，但是采用大面积的ESD保护电路会大大增加成本。

图5-5 ESD保护电路

### 5.3 版图验证

版图验证是版图设计中一个重要的步骤，版图验证是检查版图中可能存在的错误并进行改正。Calibre、Assura、Dracula 等都是常用的版图规则验证工具。我们采用的是 Cadence 环境下的验证工具 Dracula。它是一个单独的验证工具，可以独立运行。功能更强大，大型的或整体芯片很多都采用 Dracula 进行验证处理。版图验证包括：设计规则检查(DRC)、电学规则检查(ERC)、版图与电路对照(LVS)。

#### 5.3.1 DRC 验证

集成电路版图设计中，器件尺寸由电路设计决定，但各种连线的间隔和宽度、层与层之间的距离等大多数尺寸则受到制造方设计规则的限制。设计规则检查是检查和发现版图设计中不符合设计规则的错误，运行 DRC 程序，程序按相应规则检查文件运行，发现错误做出标记，并做出解释，设计者根据提示进行修改，

直到 DRC 检查完全通过。DRC 主要检查宽度、间距、包围、延伸、相交等尺寸的限制<sup>[10][11]</sup>。验证顺序如下：

(1) 从 BCD 工艺包中找到 DRACULA 的 DRC 验证文件：drac\_drc\_metal3.rul。由于本次设计用的三层金属，所以选择这个文件。为方便起见，该文件改为 drc.drc。

(2) 在 Cadence 下用 Stream 命令导出 GDSII 文件，与验证文件放在同一个目录底下。

(3) 打开 DRC 规则文件找到底下这两行并进行修改：

INDISK=CELLNAME.gds 改为存放导出版图文件的具体路径和导出文件名

PRIMARY=CELLNAME 改为导出的版图文件

(4) 打开 TEMINAL 终端，键入 PDRACULA 后继续按顺序输入继续输入 /g drc.drc、/f、/jxrun.com>a.log。

(5) 运行完后打开版图调入验证结果。按照验证结果对版图进行修改，修改完之后再重新验证直到没有错误为止。

### 5.3.2 LVS 验证

LVS 程序是将由原电路图产生的元件网表和端点列表文件，与由版图提取产生的元件表、网表和端点列表文件加以对照比较，发现不一致的元件节点，将错误信息写入指定文件，根据这些信息对版图中的每处错误逐一修正直到 LVS 检查完全通过<sup>[12]</sup>。

LVS 验证顺序与 DRC 的顺序很多类似以下只做简单介绍：

(1) 首先从 BCD 工艺 PDK 中找 lvs 验证文件，在 Cadence 下用 CDL 命令导出网单文件，用 Stream 命令导出 GDSII 文件。把这三个文件同时放在一个目录里。

(2) 修改 LVS 验证文件中的路径与文件名，使之与版图的 GDSII 文件，和电路的.cdl 文件保持一致。这与 DRC 的改法一样。

(3) 打开 TEMINAL 终端，输入 LOGLVS 命令和 PDRACULA 命令。验证完毕。

(4) 查看结果并对错误之处进行修改，然后重复上面步骤直到没有错误为

止。

## 5.4 PDIC 版图设计

### 5.4.1 BCD 工艺层次介绍

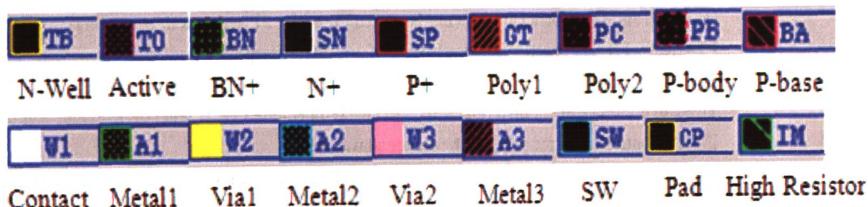

在画版图之前要了解版图的各个层次，CSMC 0.5μm BCD 工艺中<sup>[13]</sup>，主要的版图层如下：

图 5-6 主要的版图层

底下是对工艺对各个层次的具体解释<sup>[4]</sup>：

| No. | Mask              | Layer                   | Digitize  | Tone  | Description                                                                |

|-----|-------------------|-------------------------|-----------|-------|----------------------------------------------------------------------------|

| 1   | BN                | Buried N-               | Buried N+ | Clear | N+ Buried layer implant                                                    |

| 2   | TB                | Nwell                   | Nwell     | Clear | P-channel LV device substrate                                              |

| 3   | ---               | HVNwell 1               | ---       | ---   | HVMOS well implant and BJT region                                          |

| 4   | ---               | Deep-pwell 1            | ---       | ---   | Deep-pwell implant region in LDNMOS                                        |

| 5   | PT                | generate 2              | ---       | Clear | Pwell                                                                      |

| 6   | ---               | HF <sup>(3)</sup>       | ---       | ---   | 40V HVMOS drift region                                                     |

| 7   | NF                | generate <sup>(3)</sup> | ---       | Clear | N-field implant                                                            |

| 8   | TO                | TO                      | TO        | Dark  | Diffusion and channel area                                                 |

| 9   | NM                | N-drift                 | N-drift   | Clear | HVMOS and LDMOS drift implant region                                       |

| 10  | HV                | HVOX                    | HVOX      | Dark  | HV device channel region                                                   |

| 11  | TC <sup>(4)</sup> | Low TC                  | Low TC    | Clear | high resistivity and low Temperature Coefficient poly1 resistor adjustment |

| 12  | IM <sup>(5)</sup> | High Res                | High Res  | Dark  | Poly1 High ohm resistor protection area                                    |

| 13  | GT                | Poly1                   | Poly1     | Dark  | Poly1(for HVMOS gate and bottom plate of inter-Poly poly1 high resistor )  |

| 14  | PB                | P-body                  | P-body    | Clear | LDNMOS and HVMOS P-body implant area                                       |

| 15  | BA <sup>(6)</sup> | P-base                  | P-base    | Clear | High performance vertical NPN base implant area and N-JFET gate implant    |

| 16  | NG                | N-offset                | N-offset  | Clear | LDNMOS N-offset implant area                                               |

| 17  | ---               | NLDD Res <sup>(7)</sup> | ---       | ---   | NLDD Resistor                                                              |

| 18  | NL                | generate <sup>(7)</sup> | ---       | Clear | NLDD implant                                                               |

| 19  | ZP <sup>(8)</sup> | Zener                   | Zener     | Clear | Zener diode adjustment                                                     |

|    |                      |         |         |       |                                                     |

|----|----------------------|---------|---------|-------|-----------------------------------------------------|

| 19 | SN                   | N+      | N+      | Clear | N+ implant                                          |

| 20 | SP                   | P+      | P+      | Clear | P+ implant                                          |

| 22 | PC                   | Poly2   | Poly2   | Dark  | Poly2 (for LV CMOS gate, upper plate of inter-Poly) |

| 23 | W1                   | Contact | Contact | Clear | Contact                                             |

| 24 | SW <sub>0</sub>      | SW      | SW      | Clear | Schottky contact window                             |

| 25 | A1 T1 <sub>[0]</sub> | Metal1  | A1 T1   | Dark  | Metal1                                              |

| 26 | W2                   | Via1    | Via1    | Clear | Via1                                                |

| 27 | A2 T2 <sub>[0]</sub> | Metal2  | A2 T2   | Dark  | Metal2                                              |

| 28 | W3                   | Via2    | Via2    | Clear | Via2                                                |

| 29 | A3 T3 <sub>[0]</sub> | Metal3  | A3 T3   | Dark  | Metal3                                              |

| 30 | CP                   | Pad     | Pad     | Clear | Bond pad opening                                    |

**Notes:**

- ① HVNwell and Deep-pwell are drawing layer, only used for PT generation, not tooling.

- ② PT= not{((TB-HVNwell)+0.69um/ side)-0.69um/ side}+Deep-pwell.

- ③ HF is a drawing layer, only used for NF generation, NF=PT-HF.

- ④ TC is an option layer for high resistivity and low Temperature Coefficient poly1 resistor adjustment.

- ⑤ IM is an option layer for poly1 high resistor adjustment.

- ⑥ BA is an option layer for high performance vertical NPN base adjustment and N-JFET gate implant.

- ⑦ NLDD Resistor is a drawing layer, not tooling, NL is generated, NL=SN-NLDD Res-NG.

- ⑧ ZP is an option layer for Zener diode adjustment.

- ⑨ SW is an option layer for schottky diode contact window.

- ⑩ T1 is Top thick metal for SM process, T2 is Top thick metal for DM process, T3 is Top thick metal for TM process.

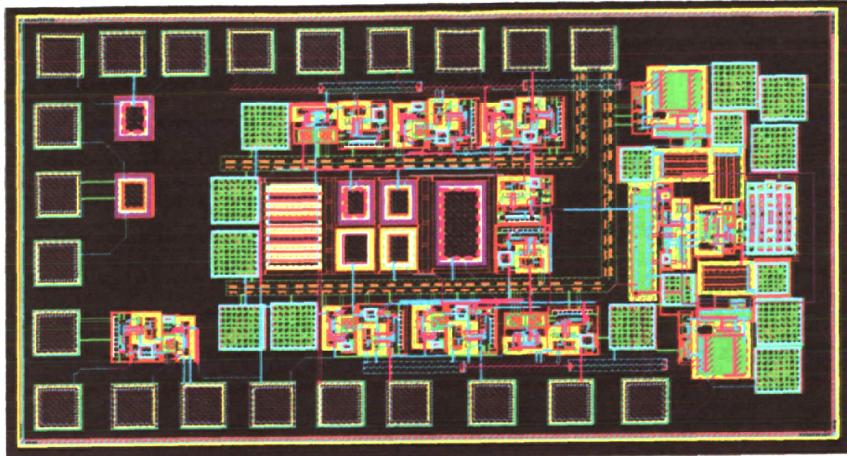

### 5.4.2 PDIC 版图绘制

集成电路版图设计可根据不同的要求选择适合的设计方法，包括全自动法、半定制法、全定制法。通常情况下全自动法主要用于纯数字电路的设计，半定制主要用于数模混合电路的设计，而全定制主要用于模拟电路的设计。三种设计方法的版图设计周期中，全自动最短，半定制次之，而全定制最长。为了缩短设计流程本次版图设计中所有的单元器件版图都是使用 CSMC 提供的 PDK 通过 Cadence 版图工具 xLLayout 自动产生，采用人工布局布线。

按照功能把整个版图划分为：探测器阵列、LDO 低压线性稳压源、放大电路三大模块进行层次化设计。为了防止探测器互相串扰，使用 PN 结反向隔离技术进行隔离，同时整个探测器阵列加上保护环使探测器与电路之间的影响力求将到最小。为了方便测试还单独画出 PD。

在CSMC 0.5μm BCD工艺规则中要求，金属面积必须达到一定30%，所以必须增加虚拟金属。IC电路工作时要避免光直接照射，而探测器工作则需要直接接受光照。为了解决这个矛盾，版图设计时就是利用这个设计规则。有电路的地方

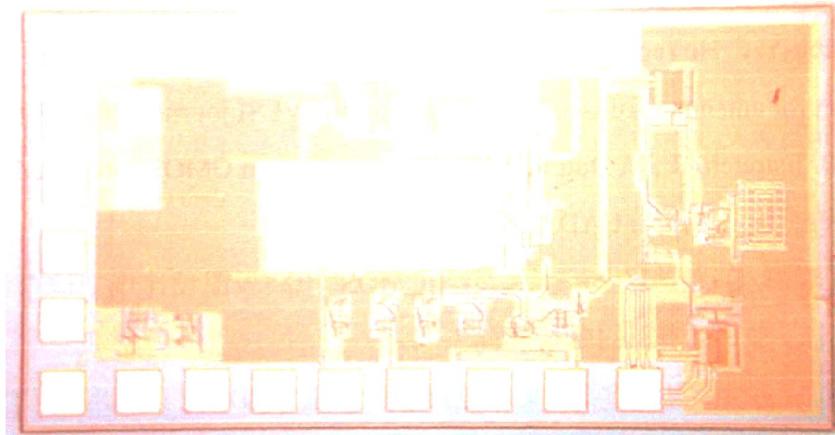

尽量用虚拟金属覆盖住。最后绘制完的芯片如图5-7所示，版图面积约为 $981\times1982\mu\text{m}^2$ 。而实际芯片如图5-8所示。为了方便测试左上脚为两个单独的探测器，左下角为单象限TIA的电路；右边部分为单片集成的PDIC。

图5-7 单片集成PDIC芯片的版图

图5-8 实际芯片

## 5.5 本章小结

本章首先介绍了版图设计的流程、注意事项及设计技巧。基于CSMC 0.5  $\mu\text{m}$  BCD工艺的工艺规则，采用Cadence的版图设计工具Virtuoso Layout Editor，设计了PDIC光接收芯片版图，版图面积约为 $981\times1982\mu\text{m}^2$ ，采用Dracula进行版图验证。

## 参考文献

- [1] 颜黄萍. 硅基单片集成 850nm 光接收芯片的研制[D]. 厦门: 厦门大学, 2010.

- [2] 吴冬燕. 集成电路版图设计的技巧[J]. 福建电脑, 2009, 4: 186-187.

- [3] 程未, 冯勇建, 杨涵. 集成电路版图(layout)设计方法与实例[J]. 现代电子技术, 2003, 3: 75-78.

- [4] CSMC Technology Corporation. 160.5um 25V VGS 25V VDS DPTM BCDMOS Process Design Rule-WTD-73D56 9E10 [Z].

- [5] Behzad Razavi[著], 陈贵灿, 程军, 张瑞智等译. 模拟CMOS集成电路设计[M]. 西安: 西安交通大学出版社, 2003。

- [6] Alan Hastings[著], 张为等译. 模拟电路版图的艺术(第二版) [M]. 北京: 电子工业出版社, 2007.

- [7] 金善子. 模拟电路版图设计中的匹配艺术[J]. 中国集成电路, 2006, 91: 48-51.

- [8] Tsung-Yi, HoYao-Wen, ChangSao-Jie Chen. Multilevel routing with jumper insertion for antenna avoidance[J]. Integration the VLSI journal, 2006, 39: 420-432.

- [9] D. B. Estreich, R .W. Dutton. Modeling Latch-up in CMOS integrated circuits and systems[J]. IEEE Trans. CAD, 1982: 157-162.

- [10] 薛耀国, 韩继国, 冯金初等. 硅栅CMOS 电路版图设计规则检查全面性探讨 [J]. 微电子学与计算机, 1994, 4:4-7.

- [11] 韩雁, 洪慧, 马绍宇等. 集成电路设计制造中EDA工具实用教程[M]. 杭州: 浙江大学出版社, 2007.

- [12] 石春琦, 吴金, 常昌远等. LVS 版图验证方法的研究. 2002, 25(2): 165- 169.

- [13] CSMC Technology Corporation. PdkST3100\_20090921[Z].

## 第六章 封装测试

封装和测试是芯片制造过程中的重要环节。由于 PDIC 是一种光电集成电路，其封装与测试有一定的特殊要求，因此本章将讨论 PDIC 的封装结构，设计相应的测试装置，完成 PDIC 主要性能的测试。

### 6.1 PDIC 的封装

传统集成电路的设计、制造、封装以及测试都是在一个单位内完成的。然而随着技术的发展，在集成电路产业中出现了分工。设计者专门对电路进行设计，然后把设计好的版图或者数据交给集成电路制造厂制造，集成电路制成之后由相关的企业完成键合、封装，最后根据设计者的要求对集成电路进行测试。

本次光接收机设计的流片是采用多目标芯片（Multi Project Chip）或称为 MPW（Multi Project Wafer，多项目晶圆）技术，其特点就是将多种具有相同工艺的集成电路设计放在同一晶圆片上流片，可以降低研究开发费用。流片后，每个设计品种可以得到几十片芯片样品，这一数量对于设计开发阶段的实验、测试已经足够。而实验费用就由所有参加 MPW 的项目按照芯片面积分摊，实验成本大大降低。

芯片测试是芯片实现的重要环节。芯片测试可以有几种途径，一是在晶片测试，二是键合测试，再有就是封装测试。本次测试根据实际情况选择了封装测试，PDIC 光接收芯片的封装属于光电子封装。半导体光电子封装是指通过电连接、光耦合、温控、机械固定及密封措施，使半导体光电子器件成为具有一定功能且性能稳定组件的装配过程<sup>[1]</sup>。

与电子封装一样，光电子封装必须考虑系统所需要的电、热、机等各方面因素，还需光的隔离，防止器件由于杂散光的进入而产生干扰。PDIC 封装的基本特征就是提供到达探测器芯片的光和电的连接。光的连接就是光的入射。电的连接则包括信号的输出和偏置电压。此外封装还提供一个良好的电的、热的、光的和与大气环境隔绝的环境。一般来说，这些要求不用非常严格，但是由于探测器的电信号可能非常弱，所以在封装中还必须尽可能的降低噪声的影响。

为了便于测试，本次流片采用两种封装形式。一种是厦门三优光机电科技开发有限公司进行的 ROSA 封装，另外一种是厦门华联电子进行的简易封装结构方式，如图 6-1 所示。

图 6-1 PDIC 封装

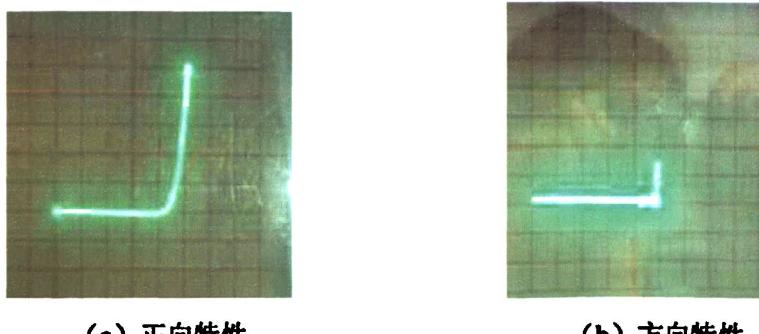

## 6.2 光电探测器测试

本文采用 XJ4810 半导体图示仪测量了探测器的 I-V 特性，结果如图 7.3 所示。图中正向 I-V 特性曲线的横坐标为 0.1V/格，纵坐标为 50 $\mu$ A/格，得到器件的正向阈值电压约为 0.43V。反向 I-V 特性曲线的横坐标为 5V/格，纵坐标为 50 $\mu$ A/格，器件反向击穿电压约为 25V。

图 6-2 光电探测器的 I-V 特性曲线

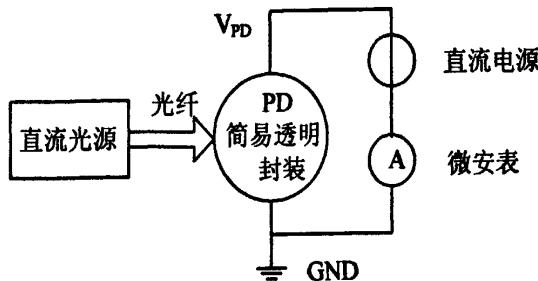

本文采用 Keithley 6514 system electrometer 测量了探测器的暗电流。探测器响应度测试电路如图 6-3 所示。将 650nm 的直流光源通过三维调整架探测器调整，使光直接照射到探测上。直流电源为探测器提供偏压。光功率计测出进入探测器的光功率，微安表测出探测器的光电流，便可计算出探测器的响应度。在

2.5V 反向偏压下，测得自制 PIN 光电探测器的响应度为 0.185A/W。

暗电流测试是在厦门三优光机电科技开发有限公司完成的，采用 Keithley 6514 system electrometer 测量。测得暗电流很小，为 3 pA。而结电容则采用 Keithley 590 高频 C-V 特性测试仪对光电探测器结电容进行测试。扣除由于封装、焊盘等带来的寄生电容影响，在 2.5V 反向偏压下探测器结电容约为 0.356PF。

图 6-3 探测器响应度测试电路

通过对 PD 的 I-V 特性、暗电流、响应度和结电容的测试，可以比较清楚的了解 BCD 工艺下 PIN 光电探测器的性能。

### 6.3 PDIC 的测试

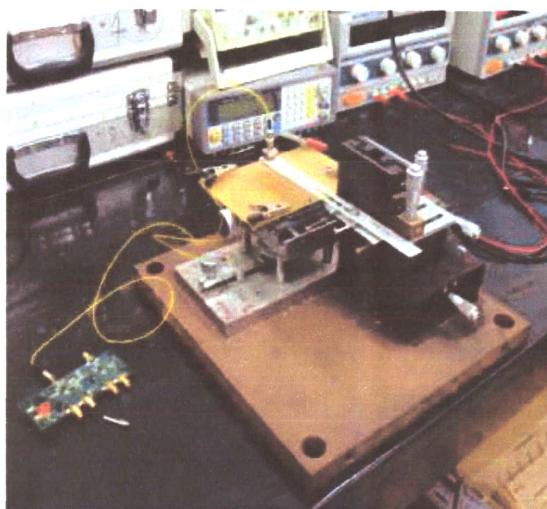

#### 6.3.1 测试装置与方案

PDIC 的测试电路原理图如图 6-4 所示，其中外接负载电阻和电容分别为：

$$R_L = 10K\Omega, \quad C_L = 10pF.$$

图 6-4 PDIC 的测试方案

在测试中，采用的主要测试平台如图 6-5 所示。我们采用厦门优迅高速芯片有限公司提供的 UX2210D 激光器驱动芯片及其测试电路板来驱动激光器，激光器则是采用武汉翌升光电的 650nm 同轴带尾纤封装形式的激光器（FC 接口）。通过调节激光器的电流得到合适的直流光功率，调制光信号电路板并作用于激光器后产生调制光信号，图中左下角就是光发射模块。激光器的尾轴光纤的出光的一端固定在五维调整架上，测试样品放在探测台上，通过五维调整架可以调整芯片的位置，激光器发出的光经透镜可垂直照得芯片上。

图 6-5 测试装置实物图

### 6.3.2 PDIC 的测试

#### (1) 直流特性测试：

PDIC 直流特性测试采用的是简易的封装，由于每个管脚只有六个管脚，扣除 Vdd、Gnd、Vref 三个必须引线外，只能再引三个象限的输出端口。结果如下表：

PDIC 直流特性表

$$(V_{dd} = 5V, V_{ref} = 2.5V, \lambda = 650nm, R_L = 10k, C_L = 10P)$$

| 样<br>品 | 项目名称       | 象限    |       |   |   |       |   |     | 功耗<br>(mW) |

|--------|------------|-------|-------|---|---|-------|---|-----|------------|

|        |            | A     | B     | C | D | E     | F | Add |            |

| 1      | 响应度(mV/μW) | 24.63 | 25.06 | — | — | 43.25 | — | —   | 139.38     |

|        | 静态点(V)     | 2.507 | 2.508 | — | — | 2.518 | — | —   |            |

|   |                  |       |       |       |       |       |       |       |        |

|---|------------------|-------|-------|-------|-------|-------|-------|-------|--------|

|   | 失调电压 (mv)        | 7     | 8     |       |       | 18    |       |       |        |

|   | 最大输出电压 (mv)      | 4.09  | 4.12  |       |       | 4.12  |       |       |        |

| 2 | 响应度(mV/ $\mu$ W) | —     | —     | 22.10 | 24.16 | —     | 47.31 | —     | 133.92 |

|   | 静态点(V)           | —     | —     | 2.511 | 2.504 | —     | 2.515 | —     |        |

|   | 失调电压 (mv)        |       |       | 11    | 4     |       | 15    |       |        |

|   | 最大输出电压 (mv)      | —     | —     | 4.14  | 4.05  | —     | 4.10  | —     |        |

| 3 | 响应度(mV/ $\mu$ W) | 28.08 | —     | 21.82 | —     | —     | —     | —     | 124.86 |

|   | 静态点(V)           | 2.514 | —     | 2.509 | —     | —     | —     | 2.485 |        |

|   | 失调电压 (mv)        | 14    |       | 9     |       |       |       | -15   |        |

|   | 最大输出电压 (mv)      | 4.07  | —     | 4.17  | —     | —     | —     | —     |        |

| 4 | 响应度(mV/ $\mu$ W) | —     | 25.01 | —     | —     | 46.81 | 42.29 | —     | 127.76 |

|   | 静态点(V)           | —     | 2.515 | —     | —     | 2.513 | 2.517 | —     |        |

|   | 失调电压 (mv)        |       | 15    |       |       | 13    | 17    |       |        |

|   | 最大输出电压 (mv)      | —     | 4.04  | —     | —     | 4.10  | 4.06  | —     |        |

从上面的测试结果可以看到，响应度和失调电压都在设计指标要求范围内。

但静态点总体有偏大趋势。同时，在测量中发现外界干扰也对芯片直流点产生较大影响。一方面是由于实际工艺偏差造成，另一方面则是由于电路设计和版图设计的问题，特别是版图匹配及布局仍有待提高。

## (2) 传输特性测试

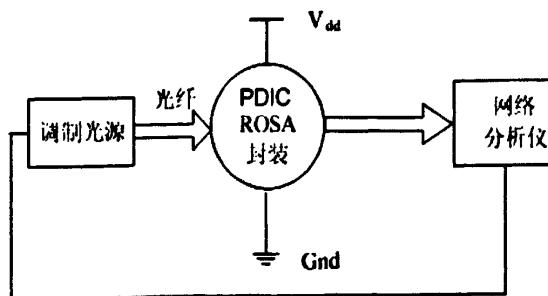

为了进一步了解 PDIC 光接收芯片的性能，估计其小信号带宽，采用网络分析仪测试传输特性<sup>[2]</sup>，其测试电路如图 6-6 所示，采用 Agilent E8362B 20GHz 矢量网络分析仪，如图 6-7 所示。

图 6-6 传输特性测试电路

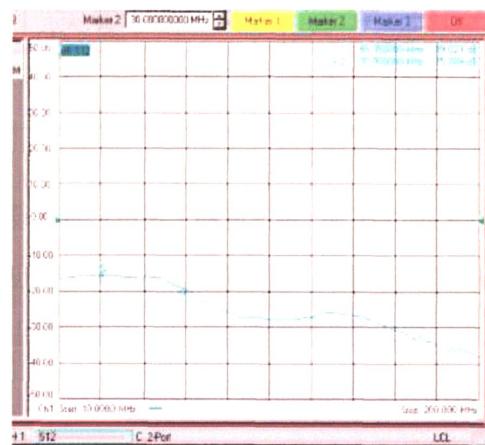

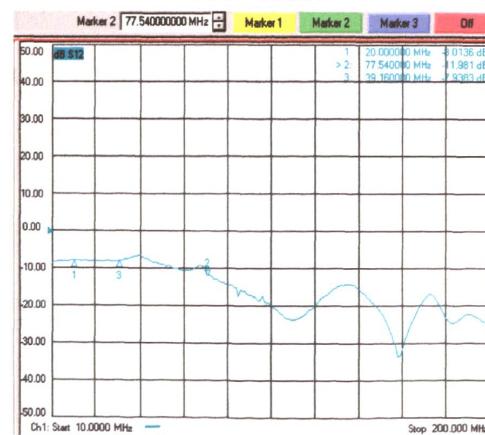

将网络分析仪的输出信号加载在 650nm 光发射模块上，光接收芯片接收调

制的光信号，转化为电流信号并且进行放大，输出至网络分析仪的接收端，通过扫描频率测量  $S_{21}$  参数（传输系数），反映出整个传输通道的输出/输入特性。图 6-8 为两个高带宽部分样品的  $S_{21}$  频率特性图。图中可看出其-3dB 带宽约为 65MHz、71MHz。

图 6-7 Agilent E8362B 20GHz 矢量网络分析仪

(a) 样品1

(b) 样品2

图6-8 频率特性曲线

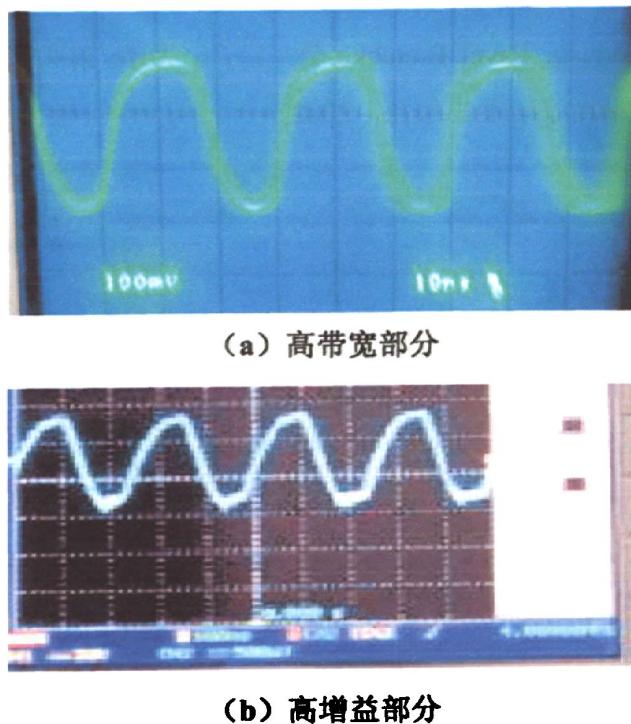

### (3) 瞬态特性测试

图6-9 (a) 为高带宽部分的35MHz脉冲瞬态图像，可以看出该频率下瞬态波形光滑漂亮。图6-9 (b) 为高增益部分的4MHz脉冲瞬态图像。

图 6-9 瞬态图像

## 6.4 本章小结

本章首先根据实验室条件介绍了 PDIC 的封装形式及测试方案。流片回来对光电探测器及 PDIC 进行测试，测试结果表明，2.5V 反向偏压下，PIN 探测器结电容约为 0.356 PF, 650nm 波长的响应度大约 0.185A/W；PDIC 中 A~D 部分的带宽 65MHz 左右，响应度为： $21.82\text{mV}/\mu\text{W} \sim 28.08\text{mV}/\mu\text{W}$ ；E、F 部分的灵敏度为： $42.29\text{mV}/\mu\text{W} \sim 47.31\text{mV}/\mu\text{W}$ 。

## 参考文献

- [1] C.A.哈珀[M], 贾松良, 蔡坚等译. 电子组装制造——芯片•电路板•封装及元器件[M]. 北京: 科学出版社, 2005.

- [2] Reinhold Ludwig, Pavel Bretchko 著, 王子宇等译. 射频电路设计——理论与应用[M]. 北京: 电子工业出版社, 2002.

## 第七章 工作总结与展望

DVD 数字光盘产业发展迅猛，在娱乐、通信、多媒体等领域应用广泛，与人们的工作、学习和生活息息相关。大部分的 DVD 生产都是在我国完成的，然而一些关键技术主要由索尼、夏普、东芝、松下以及飞利浦等国外一些大公司所垄断。PDIC 是光学头的关键元件之一，相比国外该技术的研究还处在起步阶段。本文采用 BCD 工艺实现单片集成的 PDIC 的研制。本文研究工作主要成果有：

1. 从低成本角度出发，利用 BCD 工艺  $BN^+BN+$  埋层的特点设计了与工艺完全兼容的类似 PIN 结构的光电探测器及其阵列。

2. 根据负反馈跨阻放大器的理论知识，设计了基于 CSDA 结构的负反馈跨阻放大器。为了提高负载能力设计了一个两级运放作为单位增益缓冲器。采用 spectre 对负反馈跨阻放大器进行了仿真，高带宽（A~D）和高增益（E~F）部分的灵增益分别为  $150\text{ k}\Omega$  和  $300\text{ k}\Omega$ ；带宽分别达到  $79.2\text{MHz}$  和  $22.1\text{MHz}$ 。

3. 为了抑制电源干扰跨阻放大器的性能影响，设计了低压线性稳压器 LDO。仿真结果表明其输出电压可以达  $4.36\text{V}$ ，有较好的电源抑制比。

4. 采用 Cadence 软件完成单片集成 OEIC 的版图设计，并在无锡华润上华科技有限公司采用  $0.5\mu\text{m}$  的 BCD 工艺进行 MPW 流片。

5. 利用实验室的测试条件对流片回来芯片进行了两种形式的封装，并做了具体的测试。测试结果表明， $2.5\text{V}$  反向偏压下，PIN 探测器结电容约为  $0.296\text{ PF}$ ， $650\text{nm}$  波长的响应度大约  $0.185\text{A}/\text{W}$ 。PDIC 中 A~D 部分的带宽  $65\text{M}$  左右，响应度为： $21.82\text{mV}/\mu\text{W} \sim 28.08\text{mV}/\mu\text{W}$ ；E、F 部分的灵敏度为： $42.29\text{mV}/\mu\text{W} \sim 47.31\text{mV}/\mu\text{W}$ 。功耗约  $130\text{mw}$ 。所测指标均能达到设计要求。

尽管测试结果达到了设计要求，但还是存在着一些问题。解决好这些问题也是今后进一步研究的方向。下面就主要问题进行简要讨论：

1. 经测试，发现所设计的光电探测器的响应度比仿真时要小。这一方面可能是由于光对准及聚焦方面存在一定的问题，使得光能量不能全部会聚在光敏面上，需要在装置特别是聚焦方面做进一步努力。另一方面则可能是由于工艺偏差的。在实际设计的时候，采用的参数由 PDK 得到，跟实际工艺会有一定偏差。

2. 在测试中发现静态点总体有偏大趋势，而且随着外界干扰发生较大变化。

这可能是由于电路本身的电源抑制比不过高造成的。因而需要提高整体电路的电源抑制比，并进一步稳定静态工作点。版图方面也需进一步改进，比如匹配和整体布局、布线等。考虑到版图面积问题本次流片也没有采用 ESD 保护电路，实际应用，则必须要考虑 ESD 保护问题。这些问题的存在使得本次流片难以达到整机应用，实现产品商业化。

## 附录 攻读硕士学位期间发表论文

### 发表论文：

- [1] 柯庆福, 程翔, 芦晶, 张寅博, 李继芳, 陈朝.光学头中单片光电集成硅基PDIC 的设计[J]. 半导体技术, 2010, 35(10): 1016-1019.

- [2] 芦晶, 程翔, 颜黄萍, 李继芳, 柯庆福, 陈朝. 光收发器中光电集成接收芯片的实现[J]. 半导体技术, 2010, 35(3): 291-294.

- [3] Jifang Li, Huangping Yan, Xiang Cheng, Yuanqing Huang, Qingfu Ke, Chao Chen. Fabrication of a monolithic optical receiver for 850nm fiber transmission[J]. Proc of SPIE, OIT 2009, Vol. 7509111-7509119. (EI 收录, EI: No.20100212633300).

## 致谢

本文是在我的导师程翔老师的悉心指导下完成的。工作中所取得的成绩都凝聚着她极大的心血。程老师渊博的学识、严谨的治学态度和自由的学术思想使我深受启发，是我们学校的榜样。在读研期间，程老师在生活和学习上都给予无微不至的关心，在此向程老师表示深深的敬意和衷心的感谢。

感谢陈朝教授，他对本文的研究项目给予了悉心的指导，并提供了完成项目所需必要的设计平台。

感谢卞剑涛博士，陈伟、芦晶师兄他们对本文的研究项目给予了直接的指导与帮助，对本项目提出了非常重要的意见与建议，与他们的交流我收获不少。感谢颜黄萍、李继芳两位老师以及张寅博师弟，他们不仅直接参与了项目的研究，而且也对项目的实验提供了大量的帮助，并提出了宝贵意见。

感谢倪祖荣老师，他对本项目提供了必要的测试仪器，并且指导和参与了项目的芯片测试实验。感谢厦门优迅高速芯片有限公司，提供的测试仪器与测试环境，感谢厦门三优光机电科技开发有限公司和厦门华联电子有限公司，为芯片的封装提供了很大的帮助，对项目的完成给予了重大的帮助。

感谢我的父母，他们的殷切期望和无私的爱是我一生中的强大精神支柱。感谢自己其他家人以及所有关心自己的朋友。

2011年4月

于厦门大学科学楼232