## 摘要

随着集成电路设计技术与加工工艺的进步以及低功耗的迫切需求，电路的工作电压越来越低，目前一些用于手持设备的嵌入式系统的处理器核电压甚至已经达到了1V以下。同时，系统的时钟频率也在不断提高，以满足手持设备日益增加的多功能与高性能的要求。

电路工作电压的降低必然导致对电源电压噪声的要求更加严格，与此同时，数字集成电路随着功能的增加和速度的加快，其工作时状态翻转的电流变化( $\Delta I$ )增大，系统的带宽增加。 $\Delta I$ 是电路板上产生电源电压噪声最主要的原因之一，所以，现代高速电路的电源系统设计正面临着越来越严峻的在更大带宽内保证低电源电压噪声的挑战。

电源完整性(Power Integrity,PI)设计的目标就是指保证系统稳压电源在经过电源传输系统后在指定器件端口相对该器件对工作电源要求的符合程度，即控制电源电压的噪声在一可接受的范围内。

开关电源由于其高效率的优点，使得目前它在手持设备的主电源电路中获得广泛应用。

本文以手持设备和开关电源为前提，以实现电源完整性为目标，进行电路板级的电源分配系统设计。首先详细介绍了应用于手持设备的各种电源管理技术及理论，并以此为基础进行电压变换电路的设计，设计内容包括开关控制器的分析，选型，无源器件的选型与电路设计，电路的PCB设计以及电源地层设计，然后采用目标阻抗法，利用Cadence公司的PI分析软件，对电源分配系统的各组件，即开关电源模块，电源/地层和旁路电容进行建模，通过仿真，分析最后完成设计。

采用目标阻抗法的电源完整性仿真结果显示在整个系统的工作带宽内，1.35V的VCC\_C电源系统阻抗小于所要求的目标阻抗225毫欧，3.3V的VCC3电源系统的阻抗小于330毫欧。最后通过设备工作在大负载切换情况下的实测得VCC\_C和VCC3中最大电源噪声分别为60毫伏和100毫伏左右，小于设备稳定工作所要求的5%\*VCC的电源电压噪声容限。

本课题分析并实现的利用目标阻抗法对电源系统进行优化设计，能够与主流的电路板设计工具很好的结合，避免传统的电源系统设计中过份依靠芯片厂商提供的参考设计或仅凭工程师经验进行的不足，实现较佳的成本与性能的综合效益，同时对其他中小功率电子设备的电源系统的设计也具有借鉴意义。

**关键词：**手持设备、开关电源、电源分配系统、旁路电容、电源完整性

## Abstract

With the development of the design technology and manufacture technique of the IC , and the urgent demand of low-power design, supply voltage becomes lower and lower. Now, some processor in embedded system, which is used in handheld terminals, can even work under the condition that the core supply voltage is less than 1 volt. Meanwhile, in order to get high performance with that more functions are added into the system, the clock frequency is increasing.

The lower supply voltage means the more little noise margin. Furthermore, delta current ( $\Delta I$ ) of digital IC ,which occurs at the moment that circuit state changes, is enlarged because of more and more function blocks are integrated into one single chip. System bandwidth is also widened for that the clock becomes faster than before.  $\Delta I$  is one of the main causes for power supply noise. In a word, the design of power system of modern high-speed circuit faces the challenge of meeting the need of low noise in a widen bandwidth.

The design of power integrity aims to ensure the voltage of the point of load satisfy the IC's specification of power supply, that is ,maintain the noise voltage in an acceptable range.

Switch-mode power supply is widely used in handheld devices because of its prominent advantage of high efficiency.

The design of board-level power distribution system is implemented in this article. It is based on the switch-mode power supply used in portable devices and guarantees satisfaction to power integrity. First, several kinds of power management technologies and theories usually used in portable environment are presented and analysed. Then, we design the DC voltage converter circuit, which includes analysis and selection of controller IC, passive components selection and PCB design. Second, utilize Cadence PI analysis EDA tools to establish simulation models for switching power module, power/ground plane and bypass capacitors, which compose PDS, to simulate and analyze by using the method of target impedance.

Power integrity simulation with the method of target impedance shows that within the 500MHz system bandwidth the impedance of 1.35V and 3.3V power systems are respectively less than 223 mohms and 330mohms. Finally, the tests under the big load switching condition indicate that the maximum noise of 1.35V and 3.3V power distribution systems are repectively about 60 mV and 100mV, which meet the required 5%\*VCC noise standard.

The optimizing design method of target impedance, which is present in this work, can co-operate with mainstream EDA tools of PCB design. It avoids the disadvantage of egregiously depending on the reference design provided by the IC vendors or on engineers' experience that exists in traditional power system design and obtain better comprehensive benefit between cost and performance. This paper would also be used for reference for other micro power devices' power distribution system design.

**Key words:** handheld terminals, switch-mode power supply, power distribution system, bypass capacitor, power integrity

## 东南大学学位论文独创性声明

本人声明所呈交的学位论文是我个人在导师指导下进行的研究工作及取得的研究成果。尽我所知，除了文中特别加以标注和致谢的地方外，论文中不包含其他人已经发表或撰写过的研究成果，也不包含为获得东南大学或其它教育机构的学位或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示了谢意。

研究生签名: 孙伟 日 期: 07.3.18

## 东南大学学位论文使用授权声明

东南大学、中国科学技术信息研究所、国家图书馆有权保留本人所送交学位论文的复印件和电子文档，可以采用影印、缩印或其他复制手段保存论文。本人电子文档的内容和纸质论文的内容相一致。除在保密期内的保密论文外，允许论文被查阅和借阅，可以公布（包括刊登）论文的全部或部分内容。论文的公布（包括刊登）授权东南大学研究生院办理。

研究生签名: 孙伟 导师签名: 印龙 日 期: 07.3.18

# 第一章 绪论

## 1.1 课题背景

电子信息产业的飞速发展已经并仍然在深入地影响着人们的信息获取、交流以及日常生活和娱乐的方式，其中重要一点体现是面向个人应用的手持类电子产品的迅速普及，如手机，个人影音娱乐产品和便携式 GPS 导航仪等等。这些面向最终消费者的电子产品的一个重要特点是其生命周期较短，产品更新换代的速度很快，且随着技术进步，产品的性能及功能价格比越来越高，因此，随之带来的必然是巨大的市场需求，例如，据调研机构 iSuppli 预计 2006 年第二季度全球手持电子设备市场出货量是 2.29 亿部，同比 2005 年同期增长 20%，对比 2005 年全球 8.2 亿部的出货量，2006 全年有望达到 9.42 亿部的出货；就中国市场而言，据权威部门统计，截至 2006 年底中国仅手机用户已超过 4.5 亿，并且近两年每年新增和更换手机的用户超过一亿。

集成电路是电子产品的硬件主体，集成电路产业作为电子信息行业的基础性和支撑性角色在近几十年来也遵循着著名的摩尔定律以令人称奇的速度发展着。以目前数字集成电路领域的主流——CMOS 技术为例，超大规模集成电路技术的进步不可避免的是 CMOS 晶体管的特征尺寸——晶体管可生产的最小沟道长度越来越小，从 180nm 到 130nm 再到 90nm, 65nm 的深亚微米工艺。晶体管特征尺寸的减小带来的是电路的工作电压降低，从 5V 往 3.3V, 1.8V, 1.2V 不断降低，目前市场上有的面向嵌入式系统应用的处理器的核电压甚至已经达到了 1V 以下。电源电压的越来越低，所允许的电压噪声也越来越小，所以电子产品的电源系统设计面临着越来越严格的低噪声要求。

电源电压降低的另一个拉动原因是电路的低功耗需求，手持设备通常以电池作为能量源，电路与系统的功耗是衡量产品技术水平与性能的一个重要指标。CMOS 电路的功耗主要由三部分组成：动态功耗，短路电流功耗和漏电流功耗<sup>[1]</sup>，其中动态功耗是由电路中的负载电容充放电形成的。它可以由公式 1.1 得到，其中 V 是电源电压，C 是电路中的负载电容，a 是开关活动因子（负载电容平均翻转次数），f 是时钟频率。

$$P_d = aCV^2 f \quad (1.1)$$

通常情况下，动态功耗占电路总功耗的 85%~90%<sup>[2]</sup>，是电路功耗的主要成分，且与电源电压有着平方律的关系，故降低电源电压对降低电路的功耗意义重大。

开关式 DCDC 变换电路因为其突出的高效率的特点，使得它在对功耗敏感的手持设备中获得日益广泛的应用。开关电源相对于较早出现的线性电源的缺点是因为其功率路径上的开关器件工作于开和关的非线性状态下，故产生的电压噪声比线性电源要大。所以在采用开关电源技术的电源系统中需要格外关注电源噪声的控制。

集成电路发展的另一个显著特点是在单片的器件上集成更多的功能，乃至片上系统（System On Chip, SOC）越来越多的出现在目前的电子产品中。单片集成电路功能的增加带来的结果是需要更大的电路状态翻转电流  $\Delta I$ ，而且随着时钟频率的提高，信号上升时间的减小，电路工作的速度不断得到提升，系统的带宽增大。对负载器件而言，只有保证电源系统在整个工作带宽范围内维持较低的输入阻抗  $Z_s$ ，才能有效控制负载端的电压噪声  $\Delta V$  ( $\Delta V = \Delta I * Z_s$ )，使电源电压维持在电路正常工作所要求的范围内。

## 1.2 国内外研究现状

目前，与高速高密度电路板设计领域相关的一些问题受到了国内外学者广泛的研究和关注，比如互连网络的信号完整性，电路与产品的电磁兼容性以及 PCB 板的热设计等。对于高速 PCB 的设计，国外的研究开展得较早，研究人员开展各种数值方法的研究并建立相关模型，商用公司应用研究人员的成果，聘请计算机软件人员开发各种商用软件，目前，比较好的软件有 Cadence 公司的 SpectraQuest, Mentor Graphics 公司的 ICX/Hyperlynx, Sigity 公司的 Speed2000, Ansoft 公司的 HFSS/Spicelink/Siwave 等，另外，也有相配套的测试设备的出现，比如，Tektronix 公司和 Agilent 公司的高速示波器和逻辑分析仪可

用于信号完整性测试，欧洲的 EMC 公司的电磁兼容扫描仪 EMC-Scanner 可用于对 PCB 进行电磁场近场测试。

相比于信号完整性和电磁兼容性，电源完整性引起关注的时间较晚，相应的理论还不成熟，要做全面的分析研究，对研究者的要求也较高，因为电源完整性关注的是负载器件上工作电压的稳定性，而电源作为全局性的信号，在电子产品中不但涉及到板级，同时关系到封装和芯片级。

板级上，在目前的多层高速电路板中，电源和地通常为单独的层，在系统带宽不断增大的条件下，电源地层的寄生电感效应和谐振特性对高速电路的电源完整性产生直接的影响。所以目前国外的很多研究者都对PCB上的电源地层提出了各种建模和模型降阶优化的方法。归纳起来，模型建立的基本方法主要有三种1) 路的方法2) 场的方法3) 场路结合的方法。

路的方法是以集中的观点来观察和研究问题域。目前工程中广泛应用的算法是上世纪60年代后发展起来的近代电路理论，它的理论基础是Kirchhoff定律和欧姆定律为代表的经典电路理论。用局部等效电路元（Partial Element Equivalent Circuit,PEEC）<sup>[3]</sup>对PCB层进行建模，即用大量的电阻电容电感（RLC）集总元件模拟实际的PCB电源地层的电气行为，再基于上述的经典电路理论用电路分析软件如SPICE等进行分析求解。

在微波频段（300MHz-300GHz）内，电源层与地层形成一个平板波导系统，目前研究较多的是利用场的方法分析板上因集成电路状态翻转产生的 $\Delta I$ 噪声的电磁能量在层空间的动态传输效应，并计算波导系统的谐振频率。通常采用时域有限差分法（Finite-Difference Time-Domain,FDTD）的计算方法，FDTD是通过对麦克斯韦方程作离散化，来分析电磁波在空间中传播的数值方法。利用FDTD分析时，必须对于考察的空间做适当分割，其分割单元大小与时间步长必须符合稳定法则<sup>[4]</sup>。最后将FDTD时域所求电磁场值经由傅立叶变换，可以得到频域上的响应。

场路结合的分析方法是一种工程常用的方法。它是通过场的方法提取等效电路参数，形成等效子电路，进而用路的方法进行分析。在许多仿真软件中使用了此方法，这常常是工程上的一种折衷算法。因为场的算法虽较精确但会消耗大量的计算机资源，而路的算法虽对计算机的性能要求较低，但计算结果相对粗略。两种算法的结合会在精确度和计算速度上达到一个相对的平衡。

在封装和芯片级上的电源完整性研究点主要是考虑在封装和芯片里安放去耦电容，改进封装技术减小封装的寄生参数和优化芯片的电源地网络的布局来达到减小电源噪声的目的，分析的手段多是利用基于SPICE的模型和计算软件。

目前的PCB模型分析和理论计算往往多是基于十分简单的PCB外形结构，虽然精度已经很高但很难与电路板设计的工程实践相结合。所以现在市面的电源完整性分析工具都对电源系统各组件的模型进行了等效转换或简化处理，以求得在工程中具有实用价值。但目前国内，电源完整性的分析和研究开展的并不广泛，电源工程师通常主要关注电源电路的本身，而电路工程师在指导PCB工程师进行电源相关部分设计时往往是依赖于芯片厂商提供的参考设计和工程经验，但是芯片厂商并不会完全了解用户的实际系统，导致推荐的参考设计可能存在着过设计或欠设计的情况，引起产品的成本增加或性能下降以及上市时间的延长。

### 1.3 论文的工作内容和意义

本课题的主要工作是在手持设备电源系统环境下的电源完整性的分析与优化设计，重点在于对包含了开关电源，旁路电容，PCB电源地层的整个电源分配系统的模型分析，仿真计算，以及最后的测试，验证。从而实现电路板级的电源分配系统的优化设计方法，并对影响电源完整性的因素和旁路电容的寄生参数作了分析说明。

课题以一款高性能的便携式GPS导航仪为研究平台，利用可与Cadence的PCB设计工具Allegro集成使用的电源完整性分析模块Allegro PCB Power Integrity作为分析仿真工具，该工具采用的即是前文所述的场路结合的方法。课题完成的意义在于对手持设备的电源系统的硬件器件选型，电路设计给出一种全面考虑的方法，并对电路板的布局布线设计提供指导作用，实现在产品硬件设计阶段达到性能与成本间较佳的综合效益。

具体的研究工作包括以下几点：

- 分析在手持设备电源中的各种电压变换技术及特点，着重分析了在系统主电源中应用越来越广泛的开关电感式电压变换电路的工作原理及与影响电压噪声的电路中的各相关因素。

- 通过查阅资料与文献，对电源完整性理论作了简单整理与归纳，并对电源完整性与信号完整性，电磁兼容性之间的相关性做出阐述。

- 分析课题所选用的仿真环境下的模型定义，并对实际中电源分配系统各组件建立模型，通过仿

真、优化完成电源分配系统设计中的重要内容—旁路电容的选型和布局设计。

- 通过在静态和动态，时域和频域对电路性能的数据实测，对设计方法和仿真计算进行验证。

## 1.4 论文的组织结构

全文分六章：

第一章：绪论 介绍课题背景及论文的主要内容，结构。

第二章：介绍手持设备中电源电路的各种实现技术，以及电源管理方面的相关内容。

第三章：系统阐述电源完整性的概念，以及电路系统中影响电源完整性的主要因素。

第四章：是本文的重点，涉及电源分配系统设计的主要方面，包括电源电压变换电路的设计，PCB 中电源地层的设计，旁路电容的选型及在 PCB 上寄生参数的分析和基于目标阻抗法的电源分配系统设计，仿真与分析。

第五章：对设计方法的结果和仿真进行测试，验证。

第六章：总结与展望，总结全文的工作，展望了将来的研究方向。

## 第二章 手持设备的电源管理技术

### 2.1 电源管理综述

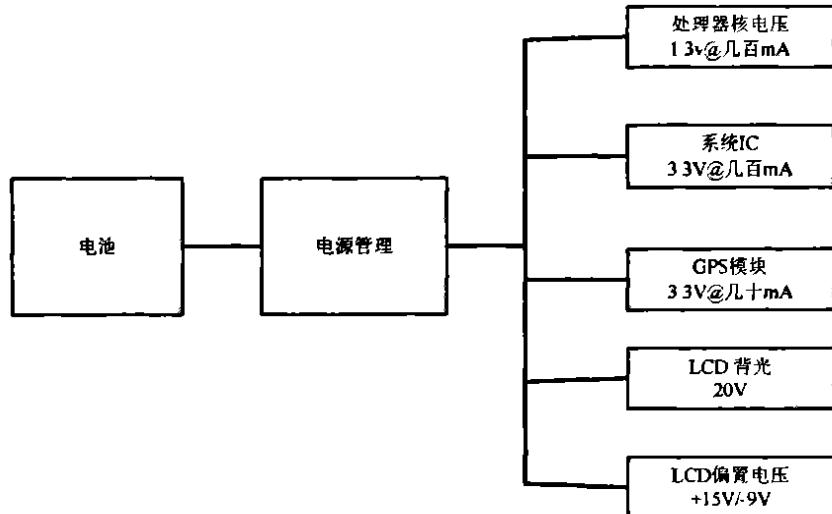

手持设备的能量源一般为可再充电的锂离子或锂聚合物电池，其电压满至空（full to empty）为4.2V-2.7V之间。而设备中负载存在多种电压和功率等级的需求，例如，图2-1给出了一款手持GPS导航仪的部分主要模块负载电源需求。同时，手持设备对硬件和系统的小体积，低功耗有着更迫切的要求：

图2-1 手持GPS导航仪主要功能模块电压或功率需求

电源管理（Power Management）指如何将能量有效分配给系统的不同组件，即负责整机的电源供给及为实现低功耗目的而实施的供电管理调度。对一般手持设备而言，可以划分为电池/外电管理、电压管理和负载管理三个子模块。

其中电压管理子模块主要负责对未稳压的电池电压进行调节以满足不同的负载要求，为整个系统中各模块的工作提供稳定的电压源。目前电压管理的实现技术主要有线性LDO（low dropout），开关电感式和开关电容式三种方式的电压变换器（voltage regulator）。在这些之间选择面临着在总体成本、效率、集成度、设计灵活性以及封装等诸多方面进行权衡的问题。

电压管理的实现方式即电压变换器的采用与电源完整性的分析与设计关系相对最为紧密，下面对各种电压变换器给予详细介绍，最后再简要介绍电池/外电的管理和负载管理。

### 2.2 电压管理

#### 2.2.1 稳定电源的发展

稳定电源是各种电子电路的动力源，被誉为电路的心脏。所有的用电设备都对供电电压有一定的要求，而供电源如市电或电池又难以满足电压不变的要求，为解决这一矛盾，人们便研制了各种各样的稳定电源。所谓“稳定”是指电压或电流的变化小到可以允许的程度，并不是绝对不变的。

稳定电源分稳压源和稳流源两种，本文所述只涉及到稳压源。

19世纪爱迪生发明电灯时，就曾考虑过稳压器。到20世纪初，就已经出现了铁磁稳压器及相应的技术文献。电子管问世不久，就有人设计了电子管直流稳压器。在20世纪40年代后期，电子器件和磁饱和元件相结合，构成了电子控制的磁饱和交流稳压器，至今还在应用。

20世纪50年代，随着半导体工业的飞速发展，晶体管的诞生使串联调整型晶体管稳压电源成了直流稳压电源的中心，这种局面一直维持到20世纪60年代中期。这种电源虽然性能优良，但它的最大的

弱点是由于功率调整管与负载串联，并且晶体管工作在线性区域，稳压器的输出电压调节与稳定借助于功率晶体管上的电压降来实现，因而在输出电压低，电流大的场合，效率非常低<sup>[5]</sup>。

随着半导体技术的进步，电子设备开始从分立元器件进入集成电路时代，体积日益缩小，规模容量逐渐增大。这种晶体管串联型常规电源难以满足形势发展的问题日益显露。20世纪60年代后期，科技工作者对稳压电源技术进行了一次新的总结，使开关电源和可控硅电源得到快速发展。与此同时，将稳压器的大部分元器件都集成在一块硅基片上的集成稳压控制器也在不断发展。从1967年美国Bob Widlar发明了第一块集成稳压控制器uA723至今，集成稳压控制器已经广泛应用于手持设备的电源设计中。今天，很多国外的知名半导体厂商都有了完整的电源稳压器集成IC的产品线，如National Semiconductor（美国国家半导体）的LM系列，Linear（凌力尔特）的LTC系列和TI（德州仪器）的TPS系列等。

虽然从线性稳压到开关稳压效率获得了很大提升，但同时也带来了噪声和干扰的增大，所以在对电源稳定性要求很高的应用场合如模拟和RF环境下，仍然有线性稳压电源的用武之地。

## 2.2.2 线性电压变换器

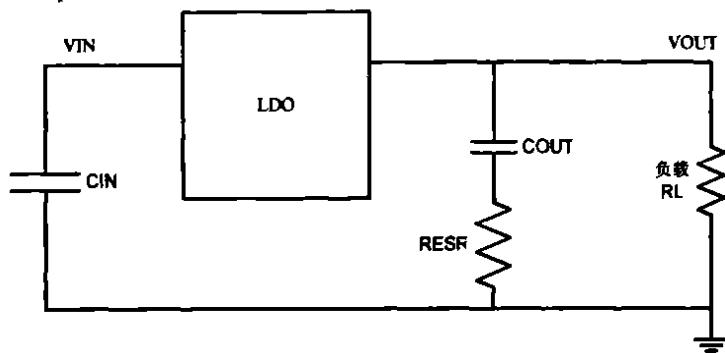

线性 LDO (Low Dropout) 的系统应用原理图比较简单，如下图 2-2 所示

图 2-2 线性 LDO 原理图

LDO 只能实现输入到输出的降压调节输出，在稳态条件下，从负载端看去 LDO 电压变换器就类似一个电阻器，其等效阻值可随负载电流  $I_L$  (即  $R_L$ ) 而改变。

$$\text{其等效阻值 } R_{LDO} = (V_{IN} - V_{OUT}) / V_{OUT} * R_L$$

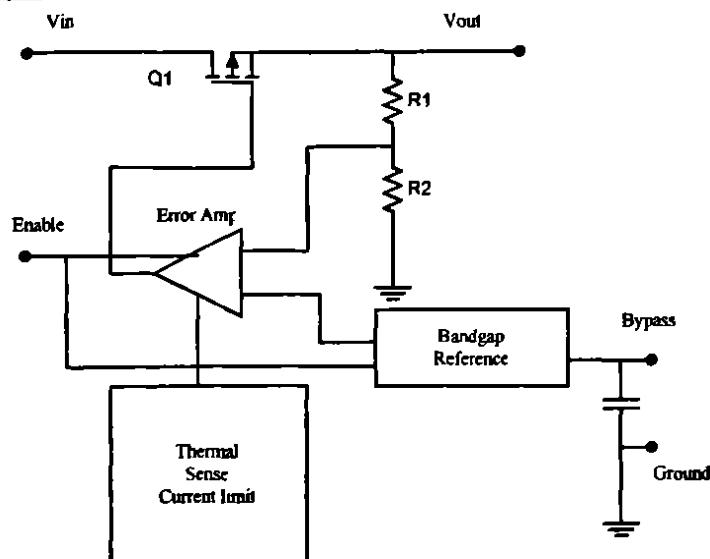

下面结合 LDO 内部的功能结构图 2-3，分析  $R_{LDO}$  的可变控制的实现原理，Q1 称为调整管，位于输入到输出的主通路上， $R_{LDO} = R_{DS(on)}$  ( $R_1, R_2$  为输出电压采样反馈电阻，其阻值相比  $R_L$  和  $R_{LDO}$  很大，可忽略其对  $R_L$  并联阻值的影响)，当负载电阻变化或  $V_{IN}$  变化引起  $V_{OUT}$  微小变化时，由反馈采样电阻采样  $V_{OUT}$  与内部带隙基准源比较将  $V_{OUT}$  的变化量经由误差放大器放大形成负反馈，产生对调整管驱动端的控制电压  $V_{GS}$ ，因为工作于饱和区的 Q1 的  $R_{DS(on)} = V_{DS} / K_p(V_{GS} - V_{TH})^2$ ， $K_p$  为 PMOS 调整管的导电因子， $V_{TH}$  为阈值电压。通过调节  $V_{GS}$  来控制  $R_{DS(on)}$ ，从而控制  $R_{LDO}$ ，实现稳压的目的。

图 2-3 LDO 控制芯片内部功能结构图

Enable 为使能端，用来在系统的空闲或睡眠模式等低功耗模式下关断 LDO，从而进一步降低系统静态的功耗。

Thermal sense 和 Current limit 是对芯片过热和限流的保护。LDO 的输出噪声主要来自于 Bandgap Reference 这个模块，Bypass 脚就是在 Bandgap Reference 的输出端外接一个电容，与电路内部的电阻组成低通滤波器，用以减小调节器的输出噪声。但是增加 Bypass 电容（一般 10nF）带来的不利因素是 LDO 对 Enable（使能）响应速度会变慢（从 us 级到 ms 级），因此如果 LDO 的应用场合没有低噪声的要求或对噪声要求不高，一般建议可不加这个电容<sup>[6]</sup>。

目前手持便携应用中的 LDO 采用诸如芯片级的超小型封装，大小仅为几平方毫米，而且多采用芯片内置的频率补偿方案，使得传统的依赖输出电容的 ESR 产生的零点 ( $Z = 1/R_{ESR}C_{OUT}$ ) 来提高稳定裕度不再成为必需，所以能够实现输入和输出只采用低 ESR 的陶瓷电容器的解决方案，所以成本较低，输出纹波更小，多用于模拟或 RF 等对噪声更加敏感的部分，缺点是只能降压输出，且压差大时效率较低。（效率  $\eta = V_{OUT}/V_{IN}$ ）。

### 2.2.3 开关电感式电压变换器

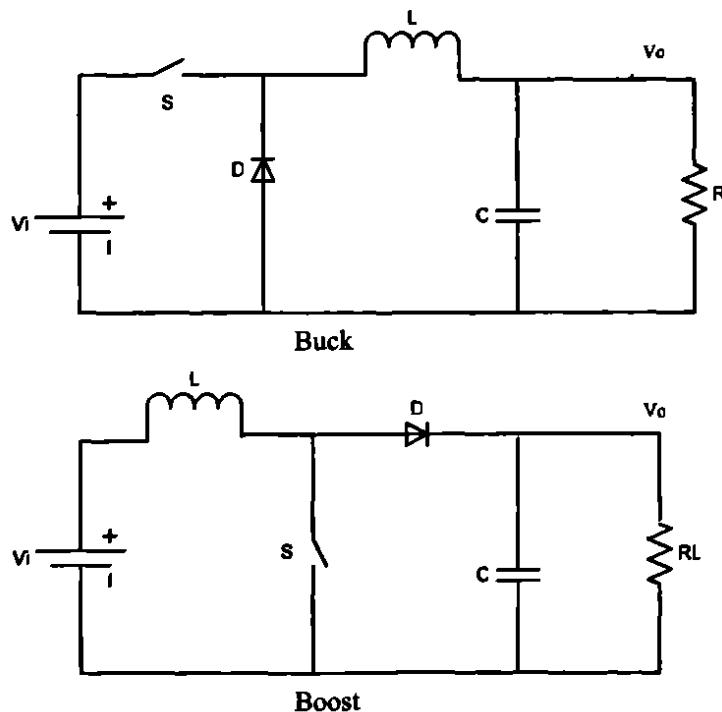

#### ➤ 开关电感式的各种电路拓扑结构及基本原理

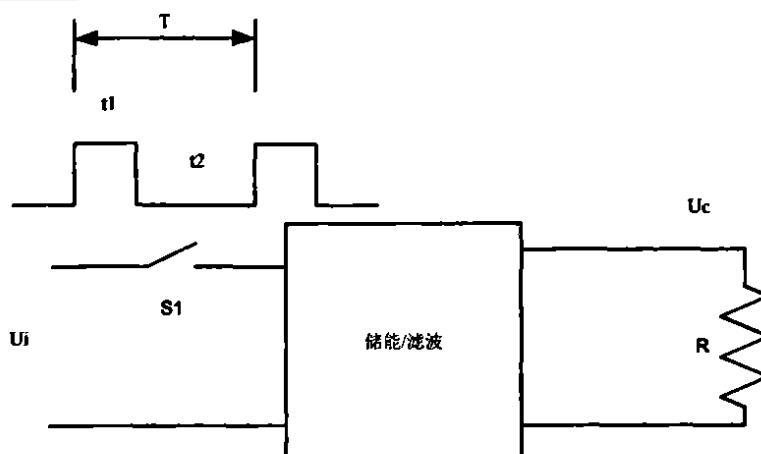

开关电感式DCDC变换器是用半导体功率器件作为开关，利用电感作为储能元件将负载线路与源电压一会相接，一会断开，则负载上也得到另一个直流电压，类似于斩波的原理。以降压的斩波变换为例，如下图2-4所示：开关S1在周期方波的控制下，间歇性的开合，t1时间代表开关导通，t2时间代表开关断开，T为控制方波的周期。通过S1将输入直流电源进行变换，再经储能滤波单元，得到输出的平均直流电源  $U_o = D \cdot U_i$ ，式中D为控制方波的占空比， $D = t_1/T$ 。通过调节占空比D，可实现对  $U_o$  的控制。通常调节占空比方式有两种，一种为PWM（Pulse Width Modulation）调节，维持T不变，改变t1；另一种为PFM（Pulse Frequency Modulation）调节，维持t1不变，改变T。PFM调制的缺点是：容易产生谐波干扰，滤波器设计也比较困难。

图 2-4 降压斩波示意图

由于半导体功率器件工作于开关状态，所以其功率损耗相比于线性 LDO 的调整管的 MOSFET 要小得多，故开关 DCDC 的转换效率很高，一般能达到 90% 左右。高效率是开关电源取得广泛应用的最主要原因，尤其在手持设备环境的低功耗要求下。

开关电感式 DCDC 变换电路主要包括功率级和控制电路两部分。功率级电路包括：

1. 功率半导体开关，常为功率 MOSFET（或集成于控制 IC 中）和续流二极管

2. L, C 储能滤波单元

控制电路在手持设备中的开关电感 DCDC 变换中一般为集成的控制器 IC，完成对输出采样（通过外部电阻网络或控制 IC 内集成的电阻网络实现采样），实现产生控制开关操作的占空比 D 的负反馈回路。

根据功率级中开关和 L, C 储能滤波单元间不同的拓扑连接结构，不仅可实现降压变化（Buck），还可实现升压式（Boost）、升\_降压式（Buck-boost）等几种类型的 DCDC 变换。具体结构形式如图 2-5 所示

Buck-boost

图 2-5 常见开关电感式电压变化功率级拓扑结构

在手持设备中 Buck 型变换器用的比较普遍，所以下一节以 Buck 电路为例详细分析电路的工作原理以及控制电路部分的分析。

#### ➤ Buck 型电压变换器电路分析<sup>[7]</sup>

在进行稳态特性分析前，为简化分析，做以下几点假设

1. 开关管，二极管均是理想元件，即导通时压降为零，截至时电流为零

2. 电感，电容是理想元件。电感工作在线性区而为饱和，寄生电阻为零，电容的 ESR 为零。

3. 数学演算时输出电压中的纹波电压与输出电压的比值小到允许忽略。

一般工作情况下，电感电流在一个开关周期内连续，称为 CCM (Continuous Conduction Mode) 工作模式，当负载电流很小时，开关电流不再连续而进入一种 DCM (Discontinuous Conduction Mode) 工作模式，下面以 CCM 为前提进行分析并给出二者的临界条件：

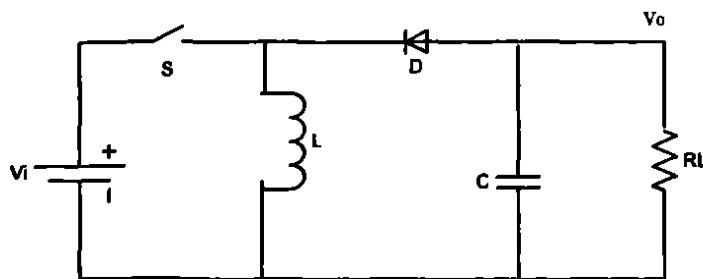

现重画 Buck 电压变换电路如下图 2-6，开关 S 由功率 MOSFET M1 取代，D 代表 M1 导通的时间  $T_{on}=T_s \cdot D$ ， $T_s$  为开关控制方波的周期，D 为占空比。稳态工作时的两种状态分别如图 2-6 中所示：

图 2-6 Buck 变换器稳态工作状态

图中箭头为电流流向：在 ON 状态，输入电压通过电感 L 对电容 C 充电同时向负载供电，电感电流  $IL$  线性增加，到  $IL > io$  时，电容由放电变为充电，直到开关断开，进入 OFF 状态，由于 L 的感生电动势，二极管 D 导通，电感向负载放电，维持负载的连续工作，电感电流随之下降到  $IL < io$  时电容由充电变为放电状态，与 L 同时向负载供电。直到下一个周期又进入 ON 状态，如此周而复始。图中 D1

在 M1 关断时导通提供电路的回流通路，故称为续流二极管。

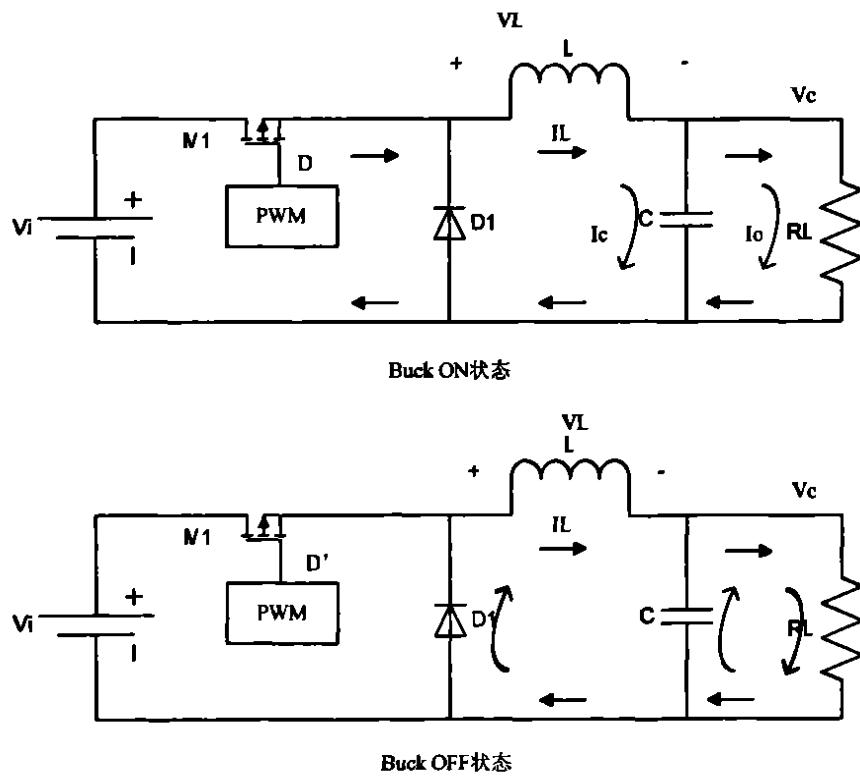

一个周期内电感与电容的电压电流波形见下图 2-7

图 2-7 Buck 变换器 CCM 工作波形图

由电感电压电流公式：

$$v_L(t) = L \frac{di_L(t)}{dt} \quad (2.1)$$

对式 2.1 两端积分  $\frac{1}{L} \int_0^{T_s} v_L(t) dt = i_L(T_s) - i_L(0)$ ，因为在稳态工作，所以  $i_L(T_s) = i_L(0)$ ，故一个周期内，电感电压的平均值为零，即  $\int_0^{T_s} v_L(t) dt = L[i_L(T_s) - i_L(0)] = 0$ 。

同时也有电感的纹波电流如图 2-7(b)所示，有

$$\Delta I_L = \Delta I_L 1 = (V_i - V_o) T_{ON} / L = \Delta I_L 2 = V_o T_{OFF} / L \quad (2.2)$$

$$V_o = V_i \times D, D = T_{ON} / T_s \quad (2.3)$$

$$\text{由电容电压电流公式: } i_c(t) = C \frac{dv_c(t)}{dt} \quad (2.4)$$

对上式两端积分有  $\int_0^{T_s} i_c(t) dt = C [v_c(T_s) - v_c(0)]$ , 同理在稳态工作有  $v_c(T_s) = v_c(0)$ , 所以一个周期内, 电容电流的平均值为零, 即  $\int_0^{T_s} i_c(t) dt = C [v_c(T_s) - v_c(0)] = 0$ 。

所以一个开关周期内电感的平均电流值  $I_L = I_o = V_o / R_L$ , 电容的平均电压值  $V_c = V_o = I_o R_L$ 。流经电容的电流对电容产生的电压  $\Delta V_o$  称为纹波电压, 其波形如图 2-7(d) 中所示, 综合以上有

$$\Delta V_o = \frac{1}{C} \int_{T_s}^{2T_s} i_c dt = \frac{1}{C} \left( \frac{1}{2} \times \frac{\Delta I_L}{2} \times \frac{T_s}{2} \right) = \frac{\Delta I_L}{8C} T_s \quad (2.5)$$

由图 2-7(b) 看出当  $\frac{1}{2} \Delta I_L = I_o$  时, 为 CCM 与 DCM 的临界状态, 定义临界状态的电感值为  $L_c$ , 可推导出  $L_c = \frac{V_o^2}{2P_o f_s} \left( 1 - \frac{T_{on}}{T_s} \right)$ ,  $f_s$  为开关工作频率,  $f_s = 1/T_s$ ;  $P_o$  为变换器输出功率,  $P_o = V_o I_o$ 。

## ► 开关电感式电压变换器的控制方式

开关电源的控制方式主要有: 电压型, 电流型, 电荷型, 平均电流性和  $V^2$  性<sup>[8]</sup>。手持设备中运用的非隔离的 DCDC 开关电压变换器的控制方式主要有电压型和电流型, 控制电路的实现均由集成的控制 IC 完成。电流型又分电感峰值电流型(简称电流型)和电感平均电流型。其中以前者应用居多。虽然控制电路由 IC 来实现, 但对于电子系统设计工程师来说, 掌握常见的电压型和电流型控制方式的基本原理和特点, 才能有助于在不同应用环境下做出合适的选择。

以下主要分析 Buck 型拓扑结构的电压性和电流型(电感峰值电流型)控制方式。

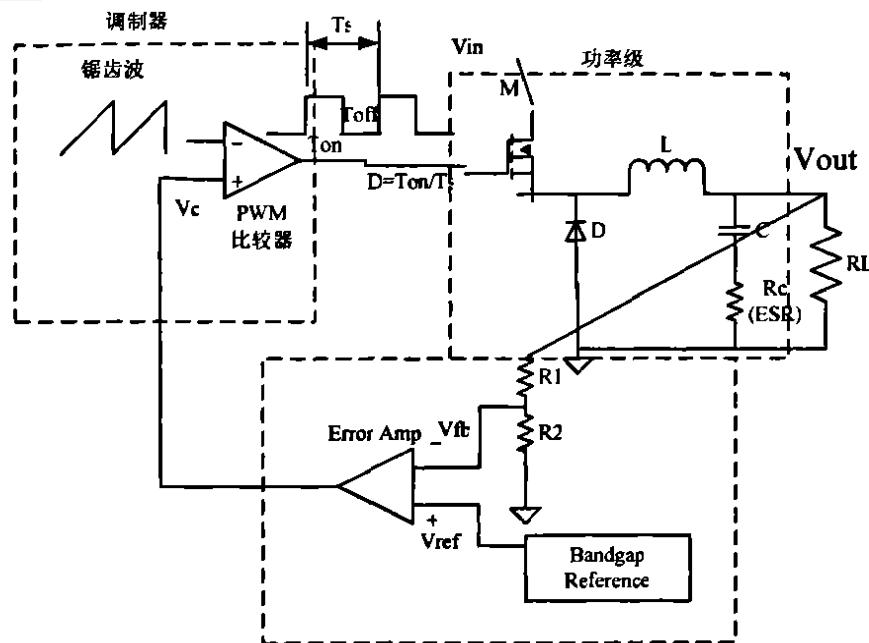

### 1. 电压型控制方式

Buck 型电压变换器实质上是一个电压负反馈的电路系统。电压型控制方式是指其反馈通路只有一个电压反馈环。如图 2-8 所示<sup>[9]</sup>:

该控制方式的工作过程是: 反馈采样电阻网络 R1, R2 对输出电压  $V_o$  采样所得反馈电压  $V_{fb}$  与基准电压  $V_{ref}$  之间的误差经误差放大器 EA 加以放大得到  $V_c$ , 然后  $V_c$  信号作为 PWM 比较器的门限与控制器内部的斜波电压发生器的电压输出进行比较, 最后用比较器输出来驱动主开关。当直流输出电压由于输入电压或负载变化产生波动时, EA 的输出电压  $V_c$  将调整与锯齿波的交点发生变化, 从而使输出电压  $V_o = V_i (T_{on} / T_s)$  保持不变。M 导通时间的改变使采样电压总是等于基准电压  $V_{ref}$ 。即

$$V_o = \frac{R_1 + R_2}{R_2} V_{fb} = \frac{R_1 + R_2}{R_2} V_{ref} \quad (2.6)$$

反馈、误差放大及频率补偿

图 2-8 电压型控制方式的 Buck 电路架构

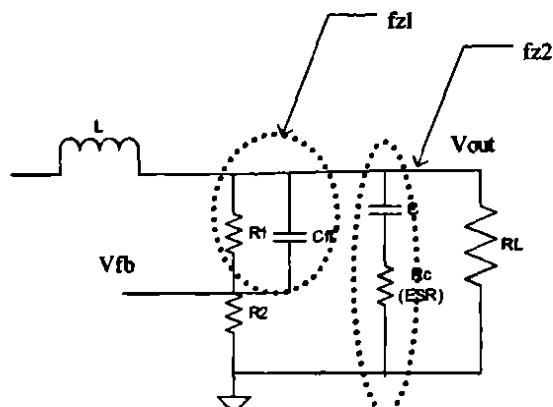

电压型控制方式的优点是结构比较简单，只有一个电压反馈环，理解起来比较容易。并且抗干扰能力较强。缺点是电感电流经输出电容产生 90 度的延迟，对负载电流变化的响应只能通过输出端电压的变化之后才能做出调整动作，所以动态响应性能较差，而且储能滤波的 LC 单元对整个环路的传递函数增加了双极点，为了保障环路足够的稳定相角裕度，需要对环路进行复杂的频率补偿，补偿一般在两个环节进行：一是控制器 IC 内部的在误差放大器部分施行的补偿，另一个是系统电路设计时利用输出电容的 ESR 或在反馈网络中加一个小的相位超前电容器来在适当的频率处各加入一个“零点”来保障一定的相角裕度。如图 2-9，其中  $f_{z1} = \frac{1}{2\pi R_1 C_f}$ ,  $f_{z2} = \frac{1}{2\pi R_c C}$ 。

图 2-9 控制器外部的频率补偿

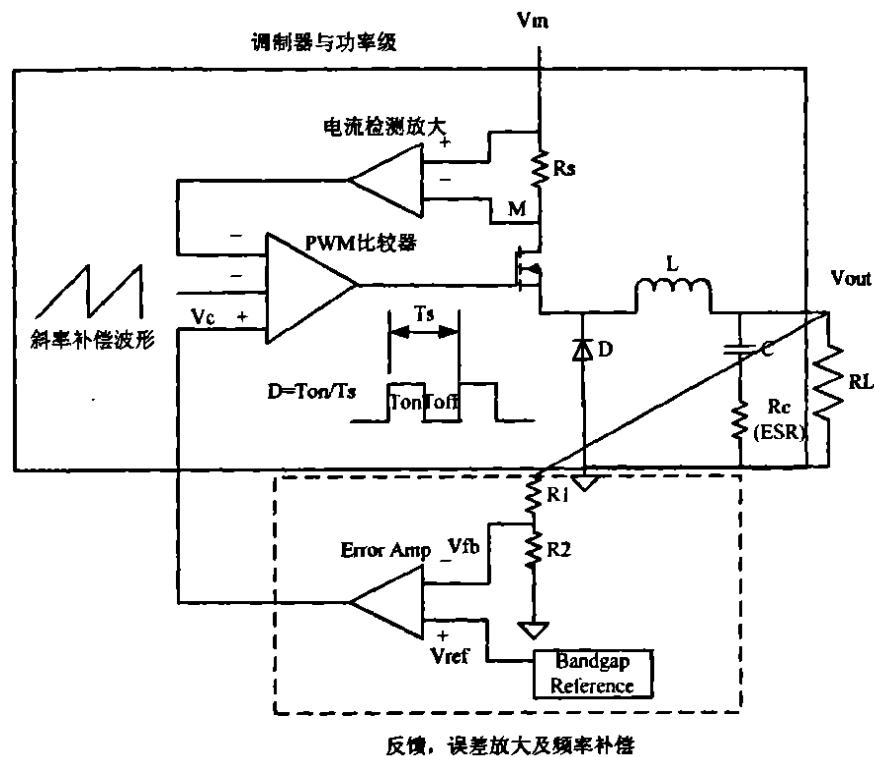

## 2. 电流型控制方式

Buck 电路中，储能滤波的 LC 元件使得系统成了一个二阶系统。根据控制理论，一个 n 阶系统要达到最优控制需要 n 个独立的反馈变量，因而同时引入电容电压和电感电流两个状态变量的电流型控制方法提高了 PWM 控制策略的性能<sup>[10]</sup>。所以目前电流型控制的 DCDC 变换器获得了越来越广泛的应用。

电流型控制方式为双环控制，一个为电流内环，一个为电压外环。如图 2-10 所示：

图 2-10 电流型控制方式的 Buck 电路架构

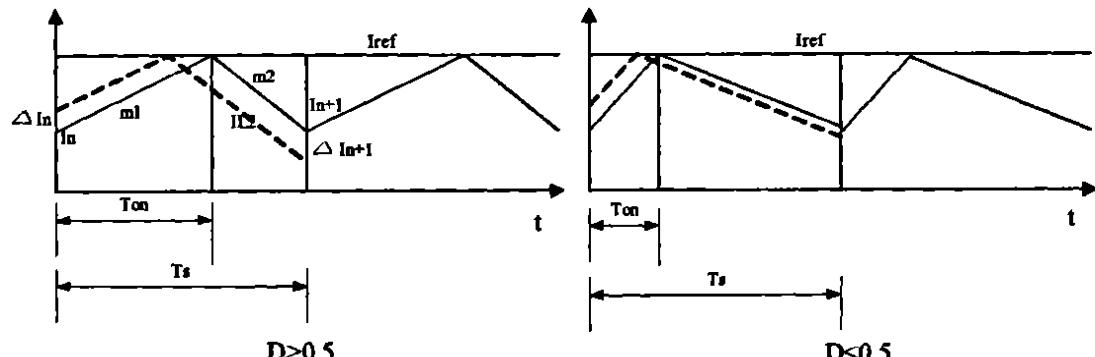

与电压型控制的区别在于 PWM 比较器的固定锯齿波由电感电流的采样检测信号和一斜率补偿信号的叠加信号所取代。这样，对输入电压或负载变化引起的电感电流变化不需要经过输出电容的延迟就能等到调整响应，所以其动态性能得到很大改善。但是，一般采样检测的电感电流信号的幅值比较小，容易受到噪声的干扰，所以抗噪性能不如电压型控制。电流控制型存在其固有的开环不稳定性，需要进行斜率补偿以保证对电流扰动的收敛性。仍然以 Buck 电路为例，当没有斜率补偿信号时，如图 2-11 示

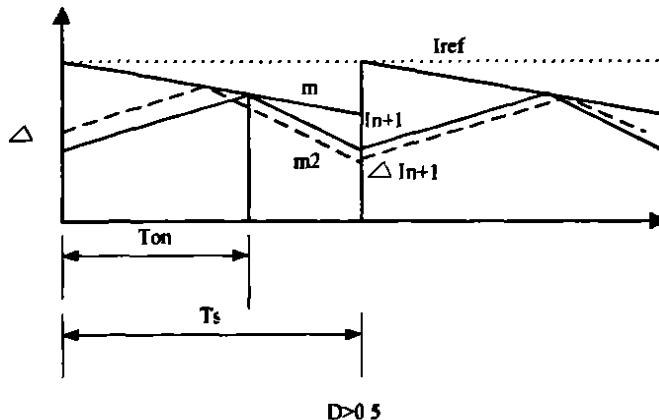

图 2-11 占空比大于 0.5 时不稳定的示意图

图中  $I_{ref}$  为误差放大器输出电压  $V_c$  确定的一个参考电流， $m_1$  为开关管导通期间电感电流上升斜率的等效折算值， $m_2$  为开关管关闭期间电感电流下降斜率的等效折算值， $I_n$  为  $t=nT_s$  时的电感电流， $I_{n+1}$  为  $t=(n+1)T_s$  时的电感电流， $T_{on}$  为开关管一个周期内的导通时间， $T_s$  为开关周期。由上节分析的 Buck 电路得下式<sup>[11]</sup>：

$$T_{on} = L \frac{I_{ref} - I_n}{V_i - V_o} = \frac{V_i - V_o}{L}, \frac{I_{ref} - I_{n+1}}{T_s - T_{on}} = \frac{V_o}{L} \quad (2.7)$$

两式消去  $I_{ref}$  后得到  $I_{n+1} - I_n = \frac{V_i}{L} T_{on} - \frac{V_o}{L} T_s$ ，又由  $T_{on} = L \frac{I_{ref} - I_n}{V_i - V_o}$ ， $D = V_o / V_i$  有：

$$I_{n+1} = \frac{-D}{1-D} I_n + \frac{1}{1-D} I_{ref} - \frac{V_o}{L} T_s \quad \text{在稳态情况下若 } I_n \text{ 存在微小扰动，忽略后两项的 } I_n \text{ 的高阶无穷}$$

小量有  $\Delta I_{n+1} = \left[ \frac{-D}{1-D} \right] \Delta I_n = \lambda \Delta I_n$ , 若使电感电流的扰动收敛必须使  $-1 < \lambda < 1$ , 即  $D < 0.5$ 。

为解决这一问题, 普遍采用的方式是在PWM比较器反相端加上一斜率补偿(Slope Compensation)信号, 加入斜率补偿后的电感电流信号如图2-12所示,  $m$ 为斜率补偿信号的斜率, 一般取 $m=0.75m^2$ 左右, 可保证在解决占空比 $D$ 接近1的情况下维持稳定<sup>[12]</sup>。

图 2-12 加入斜率补偿信号后电感电流波形

电流型控制方式下, 电感  $L$  被视为恒流源, 因此 LC 滤波器结合负载电阻只产生一个单极点  $\frac{1}{2\pi R_L C}$ , 与电压型控制方式相比更加容易进行补偿, 其简化的内部补偿方法使得电路设计方案中可采用极低 ESR 的电容器(如陶瓷电容)的优点, 而不需要依靠 ESR 产生的零点来保证稳定裕度, 从而有效地减小输出电压的纹波。

#### ➤ 同步整流

由于半导体技术的进步, 低电压, 大电流的 DCDC 变换有着越来越广泛的应用, 而变换电路中的续流二级管的导通压降产生的损耗显得越来越突出。同步整流技术就是用另外一个功率 MOSFET 取代续流二极管, 利用其导通电阻很小的特点来进一步提高 DCDC 转换器的效率。

#### ➤ 开关电感式电压变换器的调制方式

以上所论述的都是固定开关频率的脉冲宽度调制 PWM 方式(Pulse Width Modulation), 这也是开关电压变换器的主要工作方式, 实际中目前应用的还有另外两种调整方式: 脉冲频率调整(Pulse Frequency Modulation) PFM 和混合调制方式。以下分别给予介绍:

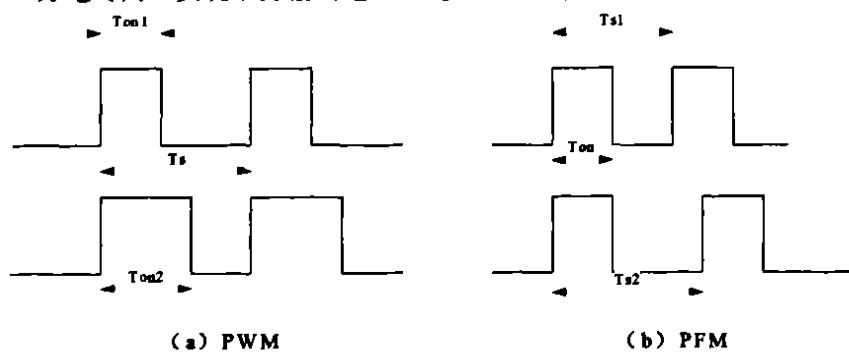

##### 1. PWM 调整方式

PWM 方式是固定开关频率, 通过改变脉冲的宽度来调节占空比, 进而调整储能元件的充放电时间, 实现维持输出电压稳定的目的, 如图 2-13 (a) 所示。

图 2-13 PWM 与 PFM 调整方式

因为开关周期固定, 所以滤波电路的设计比较容易实现。其缺点是受功率开关管的最小导通时间的限制, 对输出电压不能作宽范围调节,

##### 2. PFM 调制方式

如图 2-13 (b) 所示, 开关电压变换器 PFM 调整方式一般是维持开关管的导通时间不变, 通过改变开关频率也即改变了开关周期  $T_s$  来完成对占空比的调节。

手持设备中开关电压变换器中的损耗主要包括 1) 由控制 IC 内部功率 MOSFET 的 DC 阻抗, 电感 DC 阻抗和电容 ESR 引起的  $I^2R$  损耗。2) 与频率相关的功率 MOSFET 驱动产生的栅电容充放电损耗和开关动作过程中的电压电流的重叠造成的损耗。3) 系统的固定损耗: 如电池内阻和保险丝电阻产生的损耗; 控制器 IC 的空闲电流和晶体管的漏电流损耗等。

由于具体执行的应用不同使得负载在一个较宽的范围内变化。而定频的 PWM 调整方式下的损耗基本不随负载变化, 所以在轻负载时效率低下, 而 PFM 方式在轻负载时通过降低开关频率, 减小了与频率相关的损耗从而具有较高的效率<sup>[13][14]</sup>。PFM 方式的缺点是纹波噪声比较大。

### 3. 混合调制方式

混合调制方式就是综合了 PWM 和 PFM 的特点, 通过对电感电流的检测, 在负载变化时在 PWM 和 PFM 方式间进行切换, 保证了在整个工作范围内都获得较高的效率。目前在手持设备中应用的电压变化器的控制器 IC 基本都支持这种混合的调制方式, 以最大限度的延长电池使用时间。

## 2. 2. 4 开关电容式电压变换器

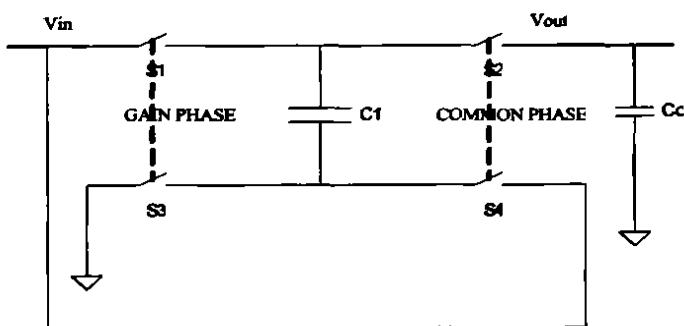

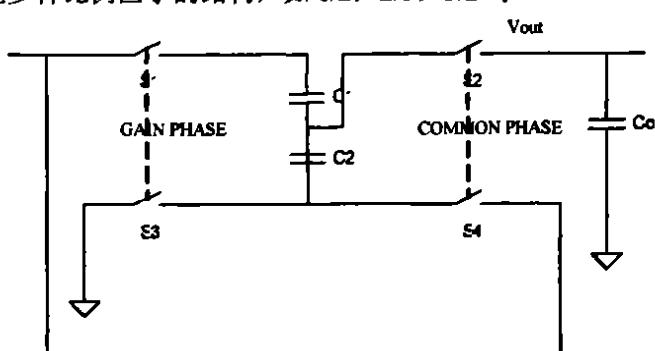

开关式电容电压转换器也称充电泵, 其采用一种所谓“飞 (flying)”或“泵 (pump)”的电容器, 而非感应器或变压器来用于能量存储, 内部 FET 开关阵列控制这些电容的充电和放电。根据不同的控制方式可以实现对输入电压乘以不同比例因子的 DCDC 变换。

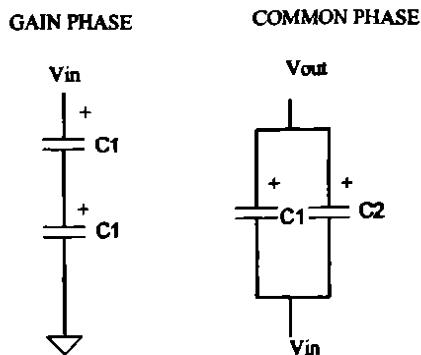

采用一只泵电容可以实现的比例因子有 2, 1 和 -1 等几种, 电容与开关的拓扑结构如下图 2-14, 为比例因子为 2 的情况

图 2-14 一个泵电容时比例因子=2 的拓扑

图中  $C_o$  为输出电容, 以减小输出电压中的纹波,  $C_1$  为泵电容, 开关阵列  $s_1-s_4$  工作于两个状态: 增益相 (GAIN PHASE) 和公共相 (COMMON PHASE), 增益相时  $s_1, s_3$  闭合,  $s_2, s_4$  断开, 公共相时反之。

采用两只泵电容可以实现多种比例因子的结构, 如  $1/2, 2/3, 3/2$  等

图 2-15 两个泵电容时比例因子=3/2 的拓扑

以图 2-15 的  $3/2$  为例, 为直观得求出比例因子, 分别画出开关阵列工作于增益相和公共相的

拓扑<sup>[9]</sup>

图 2-16 开关电容拓扑

增益相时： $V_{C1} + V_{C2} = V_{in}$ ，公共相时： $V_{C1} = V_{C2} = V_{out} - V_{in}$ ，所以 $(V_{out} - V_{in}) + (V_{out} - V_{in}) = V_{in}$ ，有 $V_{out} = 3/2V_{in}$ 。

开关电容的控制方式一般有 PWM, PFM 和混合控制方式<sup>[15]</sup>等，其形式与上节所述的开关电感中的调整方式类似。

手持设备中开关电容电路的应用形式一般为利用开关电容控制 IC 搭接泵电容和输入，输出电容来构建电压变换电路，控制方式以 PFM 居多。因为陶瓷电容的 ESR 要远低于任何其他一种电容，而电容的 ESR 对输出纹波的影响很大，故目前一般只有陶瓷电容推荐用于今天的开关电容稳压电路中。综合来讲，开关电容变换方案的成本介于线性 LDO 和开关电感变换之间，输出电流不超过 300mA，在合适的输入输出环境下也可以达到 80%-90%左右的较高效率。

## 2.3 电池/外电管理与负载管理

### » 电池/外电的管理

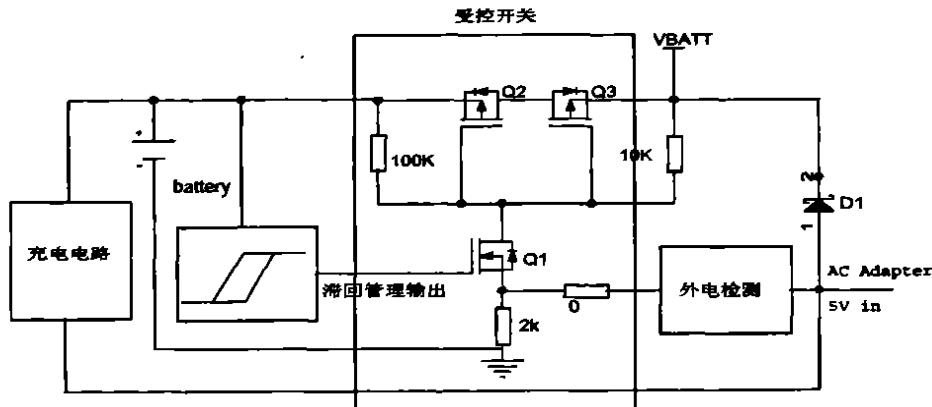

电池/外电管理子模块负责电池的充电、保护和检测，它的主要作用是优化电池利用和延长系统运行时间，同时还负责外电和电池间的可靠切换以及电池的带回管理等任务。

电池/外电管理包括电池充电管理，电池电压带回管理和电池与外电的切换管理三部分。设计功能如图 2-17：

图 2-17 外电与充电管理电路结构图

实现充电管理的充电电路由集成的充电管理芯片和外围分立器件包括防反二极管，充电指示灯和设置充电电流的电阻组成，该部分主要完成：第一，避免电池在低电量时过大的充电电流对电池造成损伤，第二，为电池在充电的不同状态提供状态灯的指示，最后，通过对电池端电压的监测实现正常的充电循环。

电池电压的带回管理就是设定比较电压的高低限值，保证了系统主供电电压位于一设置的合适范围内。

外电电池的切换管理通过外电检测器和受控开关完成，无外电时受控开关打开系统由电池供电，外电接入时开关关闭，切断电池与系统的通路，由外电负责整个系统的供电，同时通过充电管理芯片对电

池进行充电。

### ➤ 负载管理

相对于电压管理和电池/外电管理而言，负载管理是一个更系统的概念，也是目前电源管理的热点之一。其涉及到处理器厂商，电源管理芯片供应商，嵌入式操作系统和终端厂商各方的共同参与与协作，目前的主要技术手段及发展趋势归纳如下：

#### 1 PMU 与处理器的多种工作模式

随着半导体技术的进步，很多的 IO 控制器部分与中央处理单元集成在一起形成 SOC 芯片，故可以将内核与不同的功能单元分成不同的供电域，而处理器定义一些低功耗的模式如待机，睡眠等，在不同的模式下通过关闭 SOC 的一些供电域来进一步降低系统的功耗。为了实现这一策略需要与电源管理单元 PMU 的配合，PMU 一般是将几个通道的 LDO 或可配置的开关变换器集成在一个单芯片上，并且通过对变换器通路加上的控制信号和串行通信信号如 I2C 与 SOC 处理器接口。PMU 供应商会针对特定的处理器的低功耗管理技术提供他们的产品以方便设计工程师实现低功耗的处理器 SOC 的负载管理。

#### 2 负载功率开关

随着系统的功能越来越复杂，对电源子系统而言即意味着将接入越来越多的功能模块负载，负载管理比较简单的方式之一就是在某一功能模块的负载和电源系统之间加入负载功率开关，并实现对该负载功率开关的打开关闭的控制。

系统进入低功耗模式时，由设计工程师针对自己的硬件平台开发的功耗管理软件将负载与电源系统“剥离”，避免电池的深度放电，从而延长电池的使用时间。同时，集成的负载开关还具有过流，过热及反向电流的保护功能<sup>[16]</sup>。

#### 3 DVS, DFM 与 AVS

动态电压调节 (Dynamic Voltage Scaling, DVS) 技术，即基于软件的电压调节，允许软件在处理器运行时动态的改变它的时钟频率和供电电压。DVS 技术利用功耗与电压之间的平方关系，以降低性能为代价，来减少处理器的功耗。因为一般处理器的工作电压与工作频率有着一定的范围对应要求，所以 DVS 要与 DFM (动态频率管理) 配合使用。通常实现方式是通过调用嵌入式操作系统的接口函数对处理器相应寄存器进行配置实现 DFM，通过与 PMU 的 I2C 接口配置 PMU 的控制寄存器实现 DVS。

闭环自适应电压调节 (AVS) 是通过一个反馈机制，动态地将电压调节到特定操作所需的最低水平，在高性能模式中采用额定电压，而低性能模式中则降低电压，实现功耗的降低。

## 2.4 本章小结

- 手持设备的能量源一般为锂离子/聚合物电池，电压为 2.7V-4.2V，因负载存在多种工作电压轨和功率级别以及电池的再充电和低功耗的要求，需要对整个系统进行电源管理。

- 电源管理可分电压管理，电池/外电管理和负责管理三个子模块。

- 电压管理的实现途径主要有线性 LDO (low dropout)，开关电感式和开关电容式三种方式的电压变换器 (voltage regulator)，之间特性对比归纳如下表：

表 2-1 电压变换技术比较

| 电压变换器 | 优点           | 缺点       |

|-------|--------------|----------|

| LDO   | 成本低，噪声小      | 压差大时效率低  |

| 开关电感式 | 高效率          | 成本高，噪声较大 |

| 开关电容式 | 避免采用电感，节省板面积 | 输出电流较小   |

- 本章重点介绍了开关电感式电压变换器的工作原理、反馈控制形式：电压型和电流型；开关控制的调制方式：PWM，PFM 及混合调制方式。

- 电池/外电管理主要负责电池的充电管理，电池外电的切换管理。负载管理是为了实现低功耗对处理器负载进行电压/频率调节和对功能模块负载进行“剥离”操作。

## 第三章 电源完整性理论与分析

### 3.1 电源完整性概念

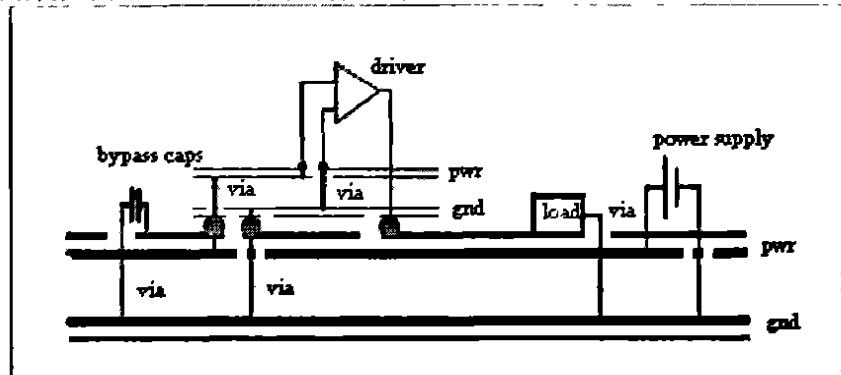

电源完整性（Power Integrity,PI）是指系统稳压电源在经过电源分配系统（Power Delivery System,PDS）后在指定器件端口相对该器件对工作电源要求的符合程度，即控制电源电压的波动在一可接受的范围内。典型的PDS包括稳压电源输出，电源/地层，过孔(via)，电源/地层间去耦/旁路电容几部分的组件，其大致结构如图3-1所示。在现代设计中，系统的供电由这几部分相互作用共同完成。

图 3-1 PDS 结构示意图

电源传输系统在不同频率上的阻抗特性不同，使PCB板上电源层与地层间的电压在电路板的各处不尽相同，从而造成供电不连续，产生电源噪声。

定义PDS的目标阻抗为<sup>[17]</sup>:

$$Z_{Target} = \frac{VCC \times \eta}{\Delta I} \quad (3.1)$$

其中，VCC：电源电压

$\eta$ ：电压噪声容限，一般为5%

$\Delta I$ ：系统最大电流变化值，通常为系统最大电流值的20%-40%，取50%可满足最坏情况的设计要求

满足系统的电源完整性要求就是保证从直流到系统的最高工作频率范围内，PDS系统的阻抗不大于定义的目标阻抗，即 $|Z_{PDS}| \leq |Z_{Target}|$ 。

在手持电子设备的发展过程中，一方面，随着低功耗需求的驱动和半导体设计与工艺的进步，系统中芯片的工作电压VCC越来越低，从5V，到3.3V，2.5V，1.8V等。目前，很多嵌入式的处理器系统的核电压甚至已经设计可以工作于1V以下。另一方面，单位面积的硅片上集成的晶体管数目却越来越多，随着SOC技术的进步，单芯片的功能越来越强大，相应的芯片的工作电流随着功能的增加而增加，同时，系统的频率越来越高，例如，目前工作于百兆以上的嵌入式处理器也亦属常见，频率的升高必然伴随着信号上升时间的减小，导致系统的带宽扩大。结果是系统的电源噪声容限越来越小(5%VCC)而系统中电流变化( $\Delta i/\Delta t$ )却越来越快。所以，要保证PDS在越来越大的带宽内维持在设计允许的目标阻抗内面临更大的挑战。

### 3.2 影响电源完整性的因素

本质上，电源的噪声除了稳压电路本身固有的小部分噪声以外，更主要的是由于电源传送系统的负载工作状态的变化，如处理器的模式切换，大量的数字逻辑的状态翻转引起的负载电流的变化，即 $\Delta I$ ，以及现实世界中的PDS必然存在着寄生参数，如寄生电感 $L_p$ ，寄生电容 $C_p$ 和直流电阻 $R_p$ ，由这些综合形成负载点处看去的电源路径和地路径间的阻抗 $Z_p$ ，因而在负载的电源电压上的产生的噪声就为：

$V_n = \Delta I \times Z_p$ 。在现代 CMOS 电路系统中，影响电源完整性的主要因素有<sup>[18]</sup> 1) 同步开关噪声 2) 旁路电容的非理想性 3) 电源/地平面的谐振和边缘效应。

### 3.2.1 同步开关噪声

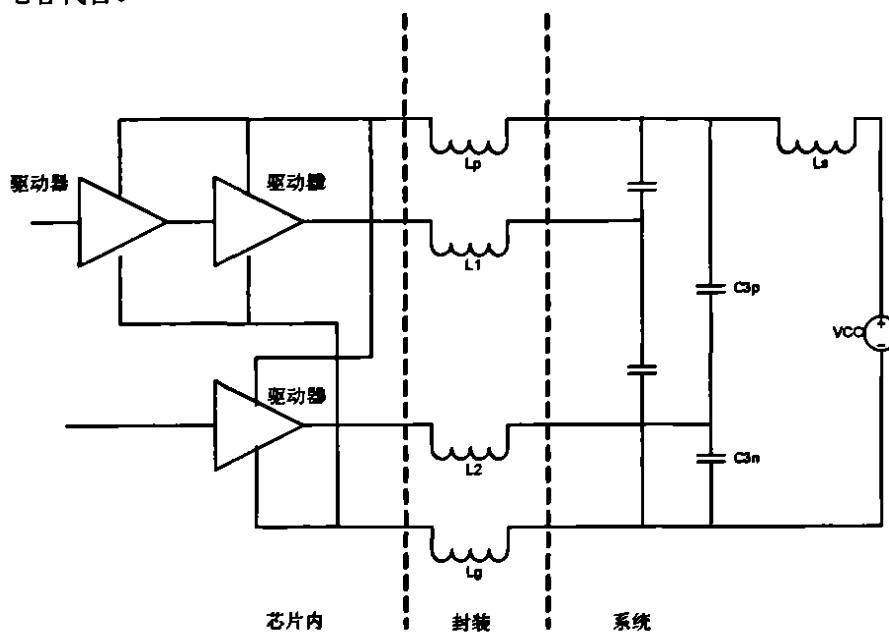

现代 CMOS 工艺集成电路是属于电压型工作器件。静态时器件的工作电流很小，功耗很低，但在电路工作的过程中涉及到内部晶体管的状态翻转和对负载电容的充放电的动态过程，充放电的电流流过非理想的 PDS 和芯片封装的寄生电感和电阻必然引起电源电压的变化，因为在这个动态的变化过程中寄生电感的效应比寄生电阻的效应要显著得多，故在后面的分析中忽略寄生电阻的影响。

同步开关噪声（Simultaneous Switching Noise, SSN）是指当器件处于开关状态，产生瞬间变化的电流 ( $di/dt$ )，在经过回流路径的寄生电感时，形成交流压降，从而引起噪声，所以也称  $\Delta I$  噪声<sup>[19]</sup>。

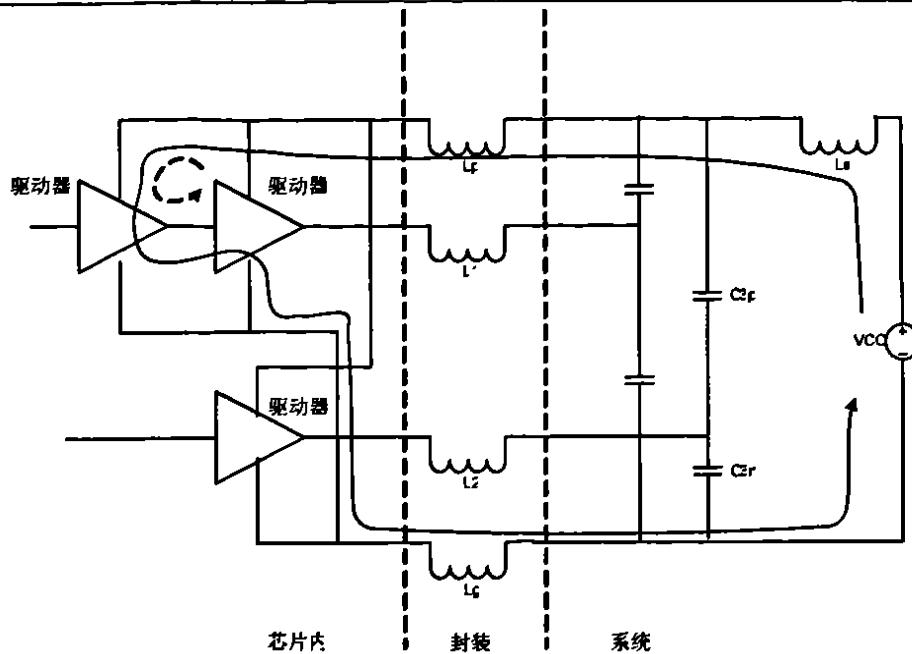

图 3-2 为同步开关噪声模型<sup>[20]</sup>，图中  $L_p$  为芯片电源引脚封装电感模型， $L_g$  为地引脚， $L_1, L_2$  为信号线引脚封装电感（忽略引脚封装之间的互感）， $L_s$  为引脚与电源地层连接寄生电感，为简化分析信号负载均用电容代替。

图 3-2 CMOS 电路开关噪声模型

同步开关噪声伴随着芯片的同步输出（Simultaneous Switching Output, SSO）而产生的，开关时间越短，电流回路的电感越大，产生的 SSN 越严重，有

$$V_{SSN} = N * L_{loop} * (di / dt) \quad (3.2)$$

$V_{SSN}$  为噪声电压

$L_{loop}$  为电流回路总电感， $N$  为同时开关的驱动器数目， $di/dt$  为电流变化速率

#### 1. On-chip 开关噪声

图 3-2 中，当驱动器 1 跳变时，它必须对驱动器 2 的输入电容进行充放电。驱动器 1 由低电平跳变至高电平时的电流路径如图 3-3 所示。驱动器 2 的输入电容的充放电回路分别如图中的实线和虚线所示。其中充电电流流经了电源引脚电感  $L_p$ ，地引脚电感  $L_g$  和 PDS 寄生电感  $L_s$ ，而没有流经信号线封装电感  $L_1$  和  $L_2$ 。因为  $L_p$  和  $L_g$  上的电流反向，所以封装的回路等效电感为  $L=L_p+L_g-2M_{pg}$ ， $M_{pg}$  指  $L_p$ ， $L_g$  间的互感。此时，同步开关的噪声电压为： $V_{SSN} = (L + L_s) * di / dt$ ， $V_{SSN}$  引起此时开关过程中芯片工作电压的阻尼振荡。

图 3-3 on-chip SSN 电流流向图

驱动器 1 由高电平跳变至低电平的分析过程类似，不再赘述。

## 2. Off-chip 开关噪声

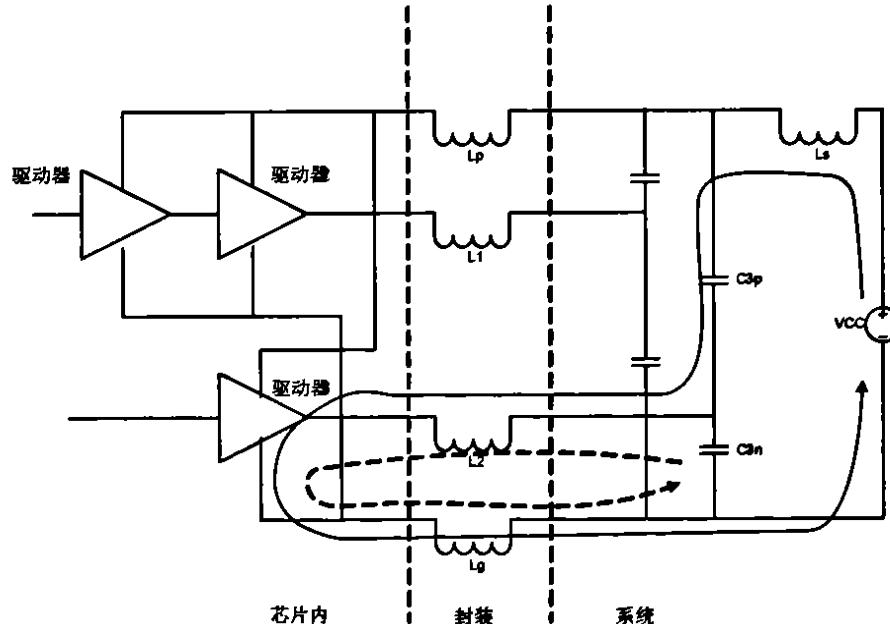

当驱动器 3 发生状态翻转时，引起的充放电电流会流过信号线的封装寄生电感，引起系统的互连噪声，故称为 off-chip（芯片外）开关噪声。以驱动器 3 由高电平跳变至低电平为例，跳变过程中需要对负载电容  $C_{3p}$  充电，同时对  $C_{3n}$  进行放电，电流流向分别如图 3-4 中实线与虚线所示

图 3-4 off-chip SSN 电流流向图

充放电电流都是从信号线流出，从地引脚返回，而不经过电源引脚。忽略与系统电源连接电感的影响，此时芯片的地端产生的噪声电压为：

$$V_{gb} = (L_g - M_{1g}) * di/dt \quad (3.3)$$

使得地端与系统的地不再保持统一的零电位，称为地弹噪声。实际中，地弹噪声往往是 on-chip 和 off-chip 综合影响的结果。

相应的，驱动器从低电平跳变至高电平时，充放电电流从电源引脚流出，从信号线返回而不经过低引脚。引起的电源端的称为电源反弹噪声。

在现代高速 COMS 电路中，一般通过在芯片的电源地引脚附近放置旁路电容来提供 IC 在运行中伴

随的大量的驱动器晶体管的翻转所需的充放电的电荷，如图 3-4 所示，

图 3-5 旁路电容对充电电路的作用

原图 3-3 中的由系统电压供给的高频部分充电电流由旁路电容  $C_d$  提供，有效的避免了 PDS 供电路径上的寄生电感  $L_s$  的影响，降低芯片工作电源的噪声。

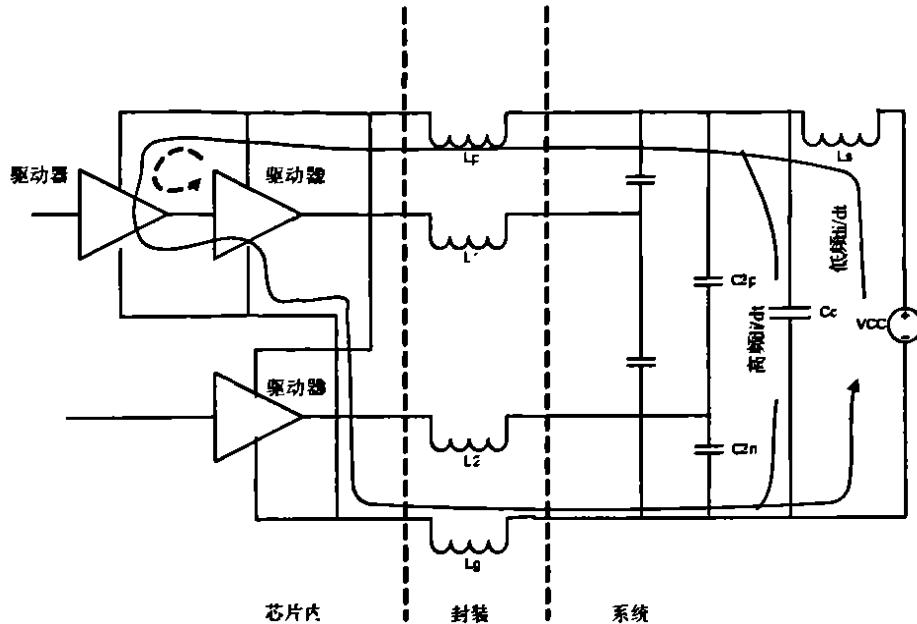

根据式 3.2，进一步减小电源噪声和地弹的措施之一是降低器件的开关速度即减小  $di/dt$ ，如降低系统的时钟频率减小同步系统中受控于同一时钟的器件开关的  $di/dt$ ，但这与追求电路的高速性的初衷相矛盾，所以一般只在有特殊的要求下采用。另外一个更具有实际意义的措施就是，降低芯片器件的封装寄生自感和与 PDS 连接寄生局部自感或增加信号路径与返回路径的互感来减小电压噪声。所以在高速 PCB 设计中电源和地的设计普遍采用层（plane）的方式并用大片铺铜的方法与芯片电源脚连接，并且去耦电容的放置要尽量靠近电源地引脚附近，目的就是为了减小芯片与 PDS 的连接寄生自感，减小信号层与参考层（返回路径层）的距离有效地增加了支路间的互感，综合起来达到有效的减小产生地弹噪声的返回路径上的有效电感。

### 3.2.2 旁路电容的非理想性

在电路中，如果电容起的主要作用是给交流信号提供低阻抗的通路，就称为旁路电容；如果主要是为了增加电源和地的交流耦合，减少交流信号对电源的影响，就可以称为去耦电容；如果用于滤波电路中，那么又可以称为滤波电容；除此以外，对于直流电压，电容器还可作为电路储能，利用冲放电起到电池的作用。而实际情况中，往往电容的作用是多方面的，我们大可不必花太多的心思考虑如何定义。本文里，我们统一把这些应用于高速 PCB 的 PDS 中的电容都称为旁路电容。无论是降低电源平面阻抗，还是减少同步开关噪声，旁路电容都起着很大的作用，电源完整性设计的重点也在如何合理的选择和放置这些电容。

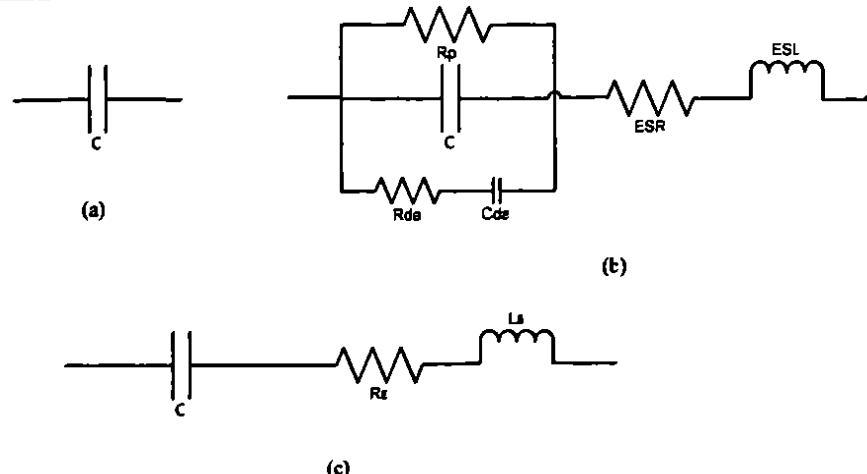

理想情况下，线性电容模型如图 3-5 (a) 所示，其阻抗关系式为  $|Z_c| = 1/\omega C$ ， $\omega$  为信号角频率，单位为弧度/秒，要满足 PDS 的设计目标阻抗，只需要在电源和地层间并上足够大的电容即可满足在系统带宽范围内的阻抗要求。可实际中的电容由于封装，材料等方面的影响，使其具备有电感、电阻的附加特性，表现形式为寄生的电阻元件和电感元件，非线性和介电存储性能，正是由于这些寄生参数的存在限制了电容使用的带宽范围。实际的电容模型如图 3-6 (b) 所示，其中：

图 3-6 电容的各种等效模型

ESR 为等效串联电阻，由电容器的引脚连接和两个极板的等效电阻相串联构成。

ESL 为等效串联电感，和 ESR 类似，也是由电容器的引脚连接和两个极板的等效电感串联构成。还有泄漏电阻  $R_p$ ，介质吸收电容  $C_{da}$ ，和介质吸收电阻  $R_{da}$  等。泄漏电阻  $R_p$  也称为绝缘电阻，值越大，泄漏的直流电流越小，性能也越好，一般电容的  $R_p$  都很大（G 欧姆级以上），所以在一般考虑问题时可以忽略， $R_{da}$  和  $C_{da}$  也是电容的分布参数，但在实际的应用中影响比较小，也忽略不计它<sup>[21]</sup>。

对于旁路电容的分析有两种不同的方法<sup>[22]</sup>1) 传统的时域方法 2) 基于电源系统目标阻抗的频域方法，下面首先对方法一作原理性介绍，之后重点阐述方法二，得出旁路电容方案的选择，布局和设计思路，因为本文所采用的仿真软件的分析，验证也是基于方法二的。

### 1) 传统的时域方法

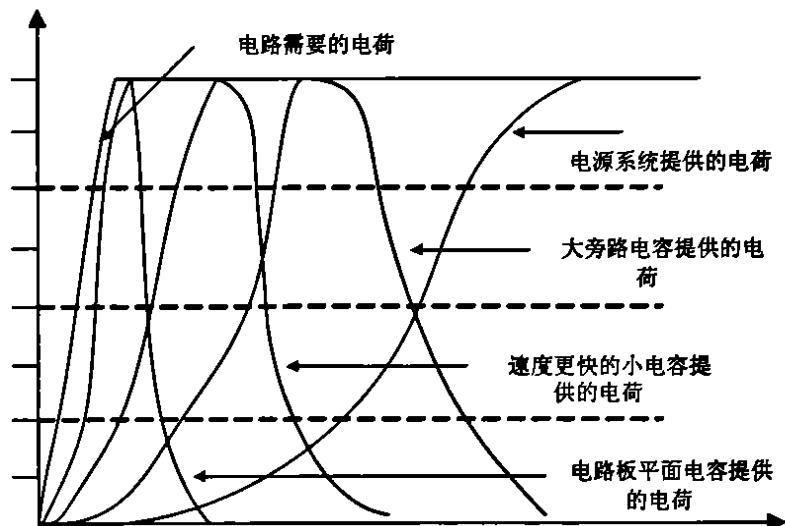

这种方法把旁路电容看作存储电荷的小电池，部分地提供器件在状态翻转时所需要的充放电荷。一般的，这些电荷在整个 PDS 系统中由不同的部分来提供，如图 3-7 所示，

图 3-7 旁路电容的时域供电示意图

第一条曲线代表完成状态转换所需要的电荷数量。曲线下方的面积代表所需要的电子，曲线的斜率代表何时需要这些电子。最右边的曲线表示电源电压变换器所能提供的电荷，虽然它能够提供数量很多的电荷，不过由于供电通路上寄生电感的存在，它们的响应速度受到限制。

电源变换器曲线旁边的曲线代表着比较大的旁路电容所能提供的电荷，它减小了供电通路上的寄生电感，不过由于其自身的 ESL 的存在，还不能让电容足够快地提供器件所需要的电子。

大电容旁边的曲线是代表小电容的曲线，总的来说，小电容所具有的 ESL 比大电容的要小，所以小电容的响应要快一些，不过它们所存储的电荷数量也小，因此它们或许不能单独完成提供器件所需要的全部电荷。

在高频时，由于电容的 ESL 的存在，导致旁路电容的作用收效甚微，电源/地层的平面电容能够很

快地提供所需要的电荷，不过它所能提供的电荷数量也是受限制的。

最后，很可能这些电容加在一起提供的所有电荷也不能满足需求，那么，器件将不能按照设计速度进行工作，系统的速度也就慢了下来。

使用旁路电容的一个目的是减小开关动作期间的供电通路上的寄生电感，电容放置的位置越靠近发生开关动作的器件越好，并且把一些小的，反应更快一些的电容放置在离器件更近的位置。此外，旁路电容的目的是稳定参考电压，在电容尺寸比开关器件小的情况下，对不同的逻辑电路建议遵循以下原则：

- 电容应该放置得靠近参考电压

- 对 TTL 与 ECL 逻辑电路来说，参考电压都是零电位，所以对于这些器件，电容应该放置在地引脚附近

- CMOS 器件的参考电压通常位于低电平和高电平两个电源电压之间。所以对于这类电路，电容应该放置在到器件的电源引脚与地引脚距离相等的位置。

## 2) 基于电源系统目标阻抗的频域方法

理想的稳压电源在直流和交流时的输出电阻均为零，但实际上从负载看去的电源必然存在着输出电阻，因为输出阻抗和负载电流的作用在负载的直流供电电压上叠加了噪声。频率范围内从直流到数 KHz 左右由电源电压变换器保证了较低的输出阻抗，从数 KHz 到几百 MHz，电源/地间并联的旁路电容维持了电源系统的低阻抗，在更高的频带内，电源/地层的分布电容对维持低阻抗开始发挥作用。

从频域角度看，设计电源的旁路电容就是在电路所关心的频带内维持 PDS 系统的阻抗低于设计所定义的目标阻抗。

对电容的高频特性影响最大的则是 ESR 和 ESL，我们通常采用图 3-6 (c) 的简化的实际模型。所以，电容也可以看成是一个串联的谐振电路，其等效阻抗和串联谐振频率为：

$$|Z_c| = \sqrt{R_s^2 + (2\pi f L_s - \frac{1}{2\pi f C})^2}, \quad f_R = \frac{1}{2\pi \sqrt{L_s C}}$$

$f$  为信号频率，单位为赫兹(Hz)，有  $f = \omega / 2\pi$

$Z_c$  为电容阻抗，单位为欧姆 (ohm)

$R_s$  为电容等效串联电容 (ESR)，单位为欧姆 (ohm)

$C$  为电容容值，单位为法拉 (F)

$L_s$  为电容等效串联电感(ESL)，单位为亨利 (H)

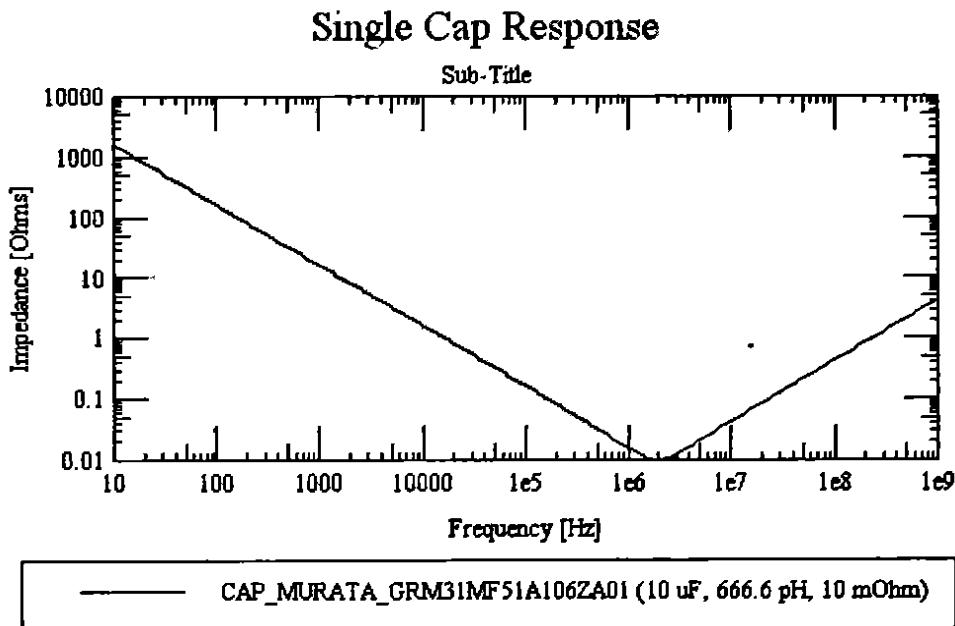

图 3-8 单个电容的阻抗-频率曲线

图 3-8 所示为 10uF 的电容 (ESR=10mohm, ESL=375pH) 的阻抗曲线。串联自谐振频率  $f_r = 1/2\pi\sqrt{LC} = 1/2\pi\sqrt{375\times10^{-12}\times10^{-6}} = 8.2MHz$ ，在高于  $f_r$  的频率范围内由于 ESL 的影响，电容的阻抗呈感性。由图 3-8 显示可知，单个电容只能在一定频率范围内维持一定的低阻抗，例如在图

3-8 中大约在 150KHz 到 400MHz 内阻抗小于 1 欧姆。

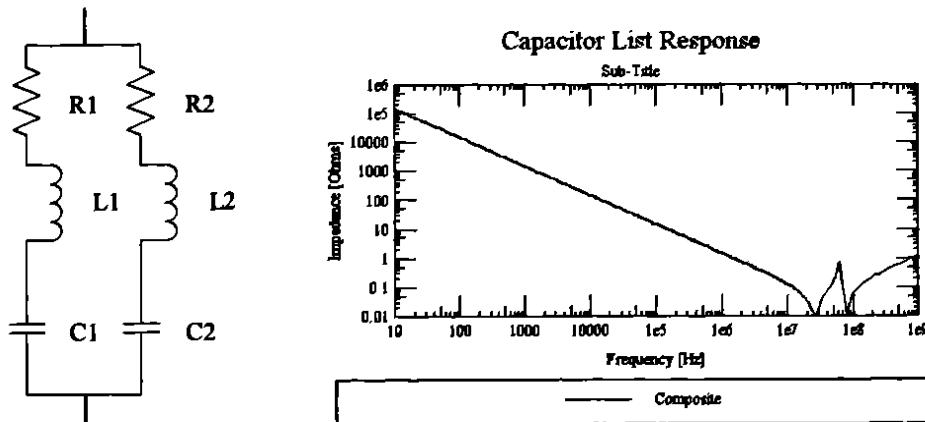

为了在更宽的频率范围内获得更低的阻抗值，实际中需要将更多的，自谐振频率不同的电容并联使用，考虑两个不同值的电容并联的情况，如图 3-9 所示：

图 3-9 两个电容并联及其阻抗曲线

为了简化计算，得到定性的分析结果，设  $R_1=R_2=R$ ,  $C_1>C_2, L_1>L_2$ ，说明  $f_{r1}<f_{r2}$ 。有：

$$X_1 = \omega L_1 - 1/\omega C_1$$

$$X_2 = \omega L_2 - 1/\omega C_2$$

$$Z_1 = R + jX_1$$

$$Z_2 = R + jX_2$$

$$Z = \frac{1}{\frac{1}{Z_1} + \frac{1}{Z_2}} = \frac{(R+jX_1)(R+jX_2)}{2R+j(X_1+X_2)}$$

$X_1, X_2, Z_1, Z_2$  分别为电容的电抗和阻抗， $Z$  为并联后总的阻抗。 $Z$  的实部和虚部分别为：

$$\text{Re}(Z) = \frac{R[2(R^2 - X_1 X_2) + (X_1 + X_2)^2]}{4R^2 + (X_1 + X_2)^2}, \text{Im}(Z) = \frac{(X_1 + X_2) + (R^2 + X_1 X_2)}{4R^2 + (X_1 + X_2)^2}$$

在  $\text{Im}(Z) = 0$  时发生谐振，即

$$X_1 = -X_2 \quad \text{---(a)} \quad \text{或} \quad R^2 = -X_1 X_2 \quad \text{---(b)}$$

在这一点，阻抗等于阻抗表达式的实部。当  $C_1$  的电抗为感抗并不断增加时， $C_2$  的电抗为容抗并不断减小，并且两个电抗相等时，才有(a)满足，这一点叫做反谐振点(antiresonance)或并联谐振点(parallel resonance)，其位于  $f_{r1}$  和  $f_{r2}$  之间。反谐振时，能量在电感和电容间进行周期性的交换，这样流经电源系统的电流很小，系统表现出高阻抗特性。

假设  $R$  很小，(b) 条件只会在当  $X_1$  或者  $X_2$  很小时才发生。且此时  $X_1$  和  $X_2$  一定异号，因此，系统的谐振点一定位于  $f_{r1}$  和  $f_{r2}$  之间。在  $f_{r1}$  点，阻抗的幅度

$$|Z| = R \sqrt{\frac{R^2 + X_2^2}{4R^2 + X_2^2}} \quad (3.4)$$

在  $R \ll X_2$  时，值为  $R$ ；在  $R \gg X_2$  时，值为  $R/2$ 。在  $f_{r2}$  点情况类似。所以，阻抗函数取得最小值不是位于系统的自谐振频率上，也不是位于电容的自谐振频率上，两个电容并联时，阻抗的最小值比 ESR ( $R$ ) 的值小，当  $X_2$  变小时，或者电容间的自谐振频率相互靠近时，或者电容的数量增加时，阻抗的最小值随之减小。

在反谐振点，如果  $X_1 = -X_2$ ，系统阻抗为

$$Z = \frac{R}{2} + \frac{X^2}{2R} \quad (3.5)$$

当  $R$  很小时， $Z$  值与  $R$  近似成反比，如果  $R \ll X$ ，系统的阻抗将很大。所以，为了得到较平坦的阻抗曲线，随着 ESR 的减小，在反谐振点上  $X_1$  和  $X_2$  也要变小，这意味着  $f_{r1}$  和  $f_{r2}$  彼此靠得更近。这说

明了随着 ESR 的减小，需要更多的电容才能达到一个相对平坦的阻抗曲线。

### 3) 旁路电容的选用原则

根据上述的分析，旁路电容的作用在其串联谐振点最为有效，但旁路电容之间或电容的 ESL 与电源地层间会存在并联谐振的现象，发生并联谐振时阻抗值往往超过目标阻抗，为了调节发生并联谐振的频率和减小并联谐振的影响，在选择旁路电容时尽量选择多种电容值，并且将多个电容并联，其串联谐振频率在发生并联谐振的频点附近，可以将并联谐振频点往高频移动，使其落在所关心的频带范围之外，并减小谐振时的阻抗。

## 3.2.3 电源/地平面的谐振

在较慢速的瞬态电流变化时，同步开关噪声主要由寄生的感性效应引起，寄生电感的主要来源是噪声源芯片与电源地层的连接电感和集成电路的引脚封装电感。采用大面积铺铜的电源层与地层的寄生电感较小，一般可忽略其影响。但在更快速的切换时，电源层与地层可视为一个动态的电磁系统，必须考虑其传输效应，因而 PCB 板的电源地层构成了一个平行板波导 (parallel plate waveguide)，在谐振频率 (resonant frequencies) 点，由器件状态转换产生的瞬态电流形成的电磁能量中大部分被电源地层获取，形成谐振 (resonator)。谐振时在层间传播的电压波导致不同位置处的电压波动，可能会导致远离噪声源的敏感器件被误触发。

对于典型的 200um 的电源地层间距和最高至 3GHz 的频率来说，可只考虑平行板波导的 TEM 模式，因为对其他模式来说远低于它们的截止 (cutoff) 频率。在实际中有限尺寸的电源地层还可视为一个由两个理想导电墙(两个层) (perfectly conducting walls, PEC) 和四个非理想墙(板边界) 组成的平板谐振箱。由于 TEM 模式和自由空间平面波的模式失配，在板边界发生能量反射和辐射，产生高频噪声和 EM<sup>[23]</sup>。其他的谐振还包括旁路电容以及表面帖装器件(Surface Mounted Device,SMD)的寄生参数与电源地层的寄生电容产生的 RLC 谐振等等。

通过改善布局和对噪声器件加旁路电容去耦和对电源地层的去耦，可将电源地层的谐振频率向上“搬移”出电路的工作频带外或降低共振强度，有效得减小因谐振而产生的电源地间的噪声电压<sup>[24]</sup>。

## 3.3 电源完整性与信号完整性

### 3.3.1 高速信号的定义

伴随集成电路设计技术和制造工艺技术的进步，CMOS 晶体管特征尺寸—晶体管的可生产的最小沟道长度越来越小，器件的开关时间也越来越短。随之而来的是信号的上升时间和时钟频率越来越高，定义信号的上升时间为终值的 10% 到 90% 这段时间，称为 10-90 上升边，也有定义 20-80 的上升边。上升边与时钟频率的近似关系为<sup>[25]</sup>：

$$RT = \frac{1}{10 \times f_{clock}} \quad (3.6)$$

RT 表示上升边，单位为 ns

$f_{clock}$  表示时钟频率，单位为 GHz

一般认为上升时间小于 4 倍信号传输延迟时可视为高速信号，信号的传输延迟与信号经过的互连线长度关系如下：

$$TD = \frac{Len}{v} \quad (3.7)$$

TD 表示延迟时间，单位为 ns

Len 表示互连线长度，单位为 inch

v 表示信号的速度，单位为 inch/ns

信号速度 v 由麦克斯韦方程求得，有

$$v = \frac{1}{\sqrt{\epsilon_0 \epsilon_r \mu_0 \mu_r}} \quad (3.8)$$

$\epsilon_0$  表示自由空间的介电常数，其值为  $8.89 \times 10^{-12} F/m$

$\epsilon_r$  表示材料的相对介电常数

$\mu_0$  表示自由空间的导磁率，其值为  $4\pi \times 10^{-7} H/m$

$\mu_r$  表示材料的相对导磁率

实际中，几乎所有的互连材料的相对导磁率都为 1，PCB 中常用的板材介质材料 FR4（环氧树脂和玻璃纤维）的在频率 500MHz 到 10GHz 范围内，介电常数在 4.0-4.5 之间变化，计算时取约等于 4，代入上式得  $v = 6 \text{inch/ns} = 15.24 \text{cm/ns}$ ，此可作为一个经验数据。

### 3.3.2 信号完整性概念

广义上，信号完整指的是高速系统中由互连线引起的所有问题，主要研究互连线与数字信号的电压电流波形相互作用时其电气性能参数如何影响系统的性能。所有这些问题分为以下三种影响和后果<sup>[25]</sup>：

#### 1) 时序

由于互连线的传播延迟造成数字系统中的时钟偏移（clock skew）和信号的滞后，这些与电路的时序分析与预算相关的影响因素，潜在的影响了电路的时序问题和速度性能。

#### 2) 噪声

当满足高速信号的条件时，系统中的互连线对信号来说不再是透明的了，而必须当作传输线来处理。对单个网络的信号来说就会产生由于不恰当的互连线设计造成的阻抗不匹配而产生信号的反射，过冲及振铃现象，信号时域的波形产生畸变，可能造成开关器件的误动作或对器件造成损伤。

对两个或多个邻近网络的高速信号来说，因为串扰也会在信号上产生叠加的噪声。串扰是指当信号在传输线上传播时，因电磁能量通过互容和互感耦合对相邻的传输线产生的不期望的噪声干扰，它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。互容引发耦合电流，称为容性串扰，而互感引发耦合电压，称为感性串扰。在 PCB 上，串扰与互连线长度、线间距以及参考地平面的状况等有关。

#### 3) 电磁干扰 (EMI)<sup>[26]</sup>

- 定义

电磁干扰(EMI)指电路板发出的杂散能量或外部进入电路板的杂散能量，它包括：传导型(低频)EMI、辐射型(高频)EMI、ESD(静电放电)或雷电引起的 EMI。传导型和辐射型 EMI 具有差模和共模表现形式。

- 差模 EMI

每个电流都存在一个闭环回路，当电流从一个器件流入另一个器件，在导线上就会产生大小相同的回流，从而构成闭合回路。在 PCB 上，当信号流过导线，如果信号频率低(最多几百 Hz)，回路电流就会沿着阻抗最小的路径，通常是最短且/或最宽的路径，流回到发送信号的器件。一旦信号频率超过几百 kHz(但还在低频范围内)，回流信号就会与信号源发送的信号产生电场和磁场的耦合作用。

这就要求回路应尽可能靠近始发信号路径。在频率较高时，当一条导线直接在接地层上布置时，即使存在更短的回路，回路电流也要直接从始发信号路径下的布线层流回信号源。在高频情况下，回路电流要沿着具有最小阻抗的路径返回信号源，即电感最小和电容最大的路径。这种靠大电容耦合抑制电场，靠小电感耦合抑制磁场来维持低电抗的方法称为自屏蔽。根据每条导线的回路布线，就能实现自屏蔽。

电路中器件输出的电流流入一个负载时，就会产生差模 EMI。电流流向负载时，会产生等值的回流。这两个方向相反的电流，形成标准差模信号，电路板只能近似达到一个理想的自屏蔽环境，完全抵消信号通路及其回路之间的电场和磁场是不现实的，残留的电磁场就形成了差模 EMI。

- 共模 EMI

电流流经多个导电层，如 PCB 上的导线组或电缆，就会产生共模辐射。典型的共模辐射回路电流流经高阻抗路径时产生，进而产生很大的磁场。磁场以共模电流的形式将其能量耦合到导线组、电线或电缆之中，共模特性表现为这些导线组中的感生电流方向全部相同，由于这些导线没有形成回路，所以不能产生相反方向的电磁场，向外辐射能量的大天线就是这样形成的。更糟糕的是，流入和流出电路板及其外壳的导线、电线或电缆的屏蔽罩中也能产生共模电流。因为共模电流是我们所希望的路径之外的电流，可能流过很大的回路面积，而电流的回路面积对 EMI 有重要的影响，所以共模 EMI 往往成为比较主要的问题。

### 3.3.3 PI 与 SI 的关系

信号完整性通常关心的是时钟信号的抖动以及信号波形的上升/下降/保持时间，电源完整性通常关心的是工作器件所承受的实际电源电压波动。信号完整性技术经过几十年的发展，其理论和分析方法都已经较为成熟，电源完整性是一种较新的技术，它被认为是高速高密度 PCB 设计目前最大的挑战之一。二者概括比较，如下表<sup>[27]</sup>

表 3-1 信号完整性与电源完整性

|      | 信号完整性        | 电源完整性   |

|------|--------------|---------|

| 性质   | 时域的概念        | 频域的概念   |

| 发展水平 | 技术相当成熟       | 理论在不断完善 |

| 测试方法 | 阻抗测试，波形测试，眼图 | 网络分析仪   |

| 仿真工具 | 非常丰富，功能强大    | 功能不断提高  |

电源完整性与信号完整性有密切的关系。稳定的电源供应是良好的信号品质的基础，而良好的信号品质也能降低电源噪声的产生，两者相辅相成。具体可从以下几点说明

- 阻抗控制

解决信号完整性的有效办法很大程度上基于对互连线阻抗的控制，在微带线，带状线等单端传输线的互连线中，都是以靠近信号路径的电源层或地层作为信号的返回路径，此时称为参考层，保证返回路径的连续性才可更有效的保证在整个信号路径上传输线阻抗的一致。电源地层间的充分去耦也有效减小发生返回路径在电源和地层间切换时对传输线阻抗的影响。同时，参考层的完整也减小了电源和地路径的寄生阻抗，减小了电源反弹和地反弹噪声，有利于电源的完整性。

- 串扰控制

控制串扰最实际的两种方法是：a) 在走线之间进行隔离 b) 走线靠近相应的参考层。串扰与走线到参考层之间距离的平方成反比<sup>[22]</sup>。

- 公共地阻抗耦合

公共地阻抗耦合是系统内传导型 EMI 的一种主要途径，其产生的共模噪声与公共的地阻抗值成正比，低阻抗的电源平面和地平面设计也有效地减小了因公共地阻抗而发生的 EMI 的危害性。公共阻抗的大小与电源地层间距，层厚度和层间介质的介电常数等因素相关。

- 地弹噪声

上节所论述的地弹噪声在芯片和 PCB 间产生共模电压，此电压会叠加在其他信号电压上，产生信号完整性问题。地弹噪声电压通常比信号电压要小，而且不会影响发送端的信号，但对接收信号会产生影响。例如，对 TTL 电路来说，以零电平为参考电压，如果输入信号电压为  $V_{in}$ ，噪声电压为  $V_{gb}$ ，那么接收端实际判别的信号幅度减小为  $V_{in}-V_{gb}$ 。CMOS 电路是以电源和地电压的平均值为参考电平，地弹噪声对信号的影响本质是一样的。

- 信号回路面积

控制 EMI 最重要的原则就是控制回路面积<sup>[22]</sup>。信号回路面积是指从信号的源开始，通过走线到信号接收端，从信号接收端再到参考层，在参考层中通过走线下方的路径流到信号源的下方，最后再回到信号源的闭合回路的面积。简单得说，这个回路所包含的面积等于走线的长度乘以走线到参考层的高度。高频的共模 EMI 是与回路面积紧密相关的，如果要想把 EMI 减少到最小，就必须把回路面积减少到最小。

直流电压对高速的回流信号没有任何意义，回流信号在电源层和地层是一样的，从交流角度看，电源层和地层没有任何区别，即可以说两个层是被旁路电容交流短路的。此时，靠近芯片的旁路电容充当了信号源的角色，有效得减小了高频信号回路的面积，从而控制了 EMI，同时完整的电源和地层还能对处于层间的信号起到屏蔽的作用，提高系统的抗干扰能力。

良好的电源完整性和低阻抗的 PDS 设计对高速系统的信号完整性和 EMI 控制具有十分重要的意义，其实本质上三者本来就是息息相关的，本小节只是偏重从几个不同概念的角度对它们之间的关系加以审视，实践中往往解决好了一个问题，同时也会带动好其他问题的解决。

### 3.4 本章小节

- 电源完整性是指电源经过电源分配系统（PDS）后为负载器件提供低噪声的满足器件要求的工作电压。

- PDS 由电压变换电路，电源地层，旁路电容的相互连接构成。

- 影响电源完整性的主要因素为：delta I 噪声，旁路电容的寄生效应，电源地平面的谐振等。

- 电源完整性，信号完整性与系统 EMI 是紧密相关的三个方面，未来的研究热点是统筹各个因素进行综合分析。

## 第四章 电源分配系统设计与仿真

### 4.1 硬件平台介绍

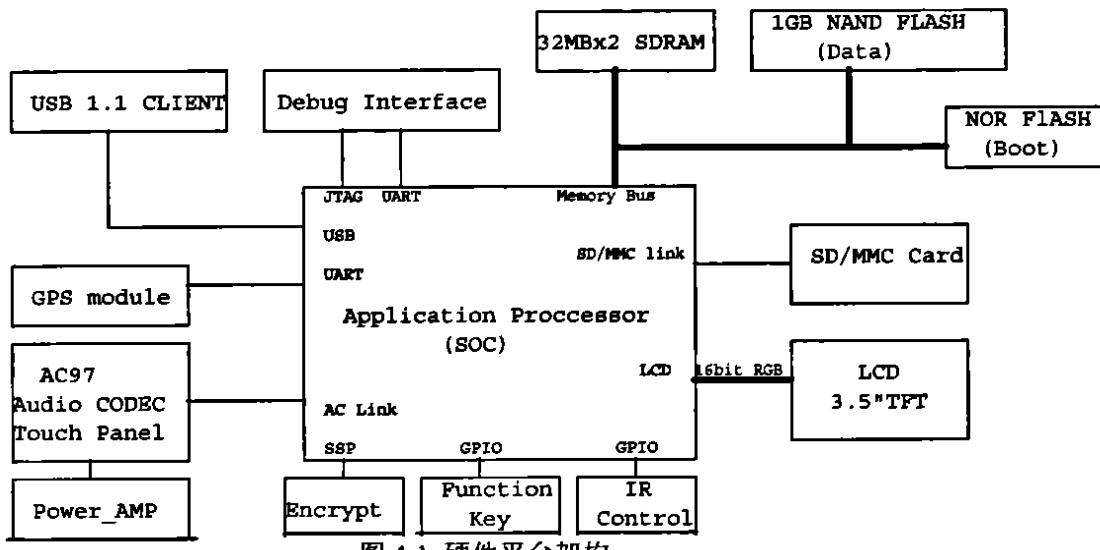

本课题所基于的硬件平台为一款手持式 GPS 导航设备，在具备传统的 PDA (Personal Digital Assistant) 所具有的个人信息管理、电子计算、数据存储、电子文档阅读、音乐播放、网络通信等功能基础上，更具特色的应用是在功能日渐强大的嵌入式处理器平台和操作系统基础上，加上 GPS (Global Positioning System) 定位功能模块和先进的导航软件系统，实行精确的全球定位和导航功能，适合应用于汽车驾驶导航，大范围定位管理等环境下。整个设备的功能框图如下：

图 4-1 硬件平台架构

稳定可靠的电源是电路与系统正常工作的最基本前提，在设备的系统功能定义，关键器件的选型和电路设计开始前需要对整个电路中的负载的电压需求，噪声容限，功率需求做出预算，并以此作为基础对供电系统及电源管理电路做出分析，器件选型，设计测试等工作。

3.3V 电压轨作为 LVCMOS (Low Voltage CMOS) 的一个标准电平，很多的 CMOS 集成电路的设计工作电压也选择了 3.3V，以实现方便的标准化和兼容性。所以整个设备中以 3.3V 作为系统的 IO 电压，这个电压轨所供的负载环境比较复杂且供电范围最广。

通过查阅器件数据手册和结合实际工程中的测试经验数据，分析系统中几个主要的电压轨的供电域的功率和噪声容限如下表所示：

表 4-1 硬件系统主要模块的电压与功率需求

| 电压轨   | 功能模块               | 电流估算       | 电压噪声容限 |

|-------|--------------------|------------|--------|

| 3.3V  | 处理器 IO             | 50uA-300mA | 5%-10% |

|       | 存储设备               | 10uA-200mA |        |

|       | LCD 显示 (digital)   | 5mA        |        |

|       | 音频 CODEC           | 20mA       |        |

|       | RS232 Transceiver  | 10mA       |        |

| 1.35V | 处理器 CORE           | 100-400mA  | 5%-10% |

| 5V    | LCD 显示 (VCom)      | 5mA        | 10%    |

|       | 音频功放               | 5-200mA    |        |

| -5V   | LCD 显示 (VCom)      | 5mA        | 20%    |

| 15V   | LCD 显示 (Bias)      | 1mA        |        |

| -9V   | LCD 显示 (Bias)      | 0.5mA      |        |

| 20V   | LCD 显示 (Backlight) | 20mA       |        |

IO 部分所带的负载最多，功耗占系统功耗的比重也较大。而且随着功能越来越强的 SOC 的出现，单片负载电流更加集中，且手持设备的处理器的 IO 电压轨的负载即 SOC 芯片上的“片内外设”也随着处理器的睡眠、正常工作等模式间频繁切换造成开关电流噪声较大。本文选系统 IO 电压和核电压两路作为分析，研究对象。由于电路设计部分类似，故下一节的电路设计论述只涉及系统 IO 这一路。

## 4.2 稳压电路设计

### 4.2.1 控制器 IC 选型

输入电压为锂电池电压：3.7V-4.2V，系统 IO 电压定为 3.3V，工作时负载电流为 100-600mA。通过第二章的对各种电压变换器的特点分析，选用高效率和具有快速动态响应的电流控制模式 buck 型开关电感式电压变换器，可获得约 90% 的转换效率和更快的负载响应。

控制器是开关电压变换器中集成度最高的部分，目前流行的 Buck 控制器基本集成了除输入输出电容、储能电感外的其他所有器件。其主要功能是完成输入误差信号到输出控制信号的转换，即控制算法的实现。Buck 开关控制算法的实现主要由控制器内的时钟部分、误差放大部分、逻辑控制部分来完成，详细的控制原理见本文第二章所述，此处不再赘述。

所选器件 EUP3406 的主要电气参数<sup>[28]</sup>如下：

- 1) 最大负载电流: 600mA

- 2) 输入电压范围: 2.5V-5.5V

- 3) 输出电压: 最低可调至内部参考电压 0.6V

- 4) 开关频率: 1.5MHz

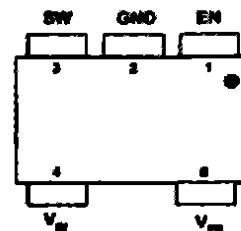

- 芯片为 SOT23-5 封装，整体外形如右图 所示

引脚定义: 1) EN 使能脚高电平有效 2) GND 系统地

3) W 连接储能电感的开关节点 4) Vin 输入电

源 5) Vfb 电压负反馈输入点

### 4.2.2 无源器件选型

Buck 型开关变换器的外围无源器件主要包括输入输出电容，储能电感，反馈电阻网络及用于优化系统特性的补偿电路。选型首先依赖于电源系统的设计环境及指标，包括输入输出电压、电流范围，输入输出纹波要求，转换效率，EMI，体积，成本等。其次，所选控制器的控制模式，开关频率也是选型设计的主要选择依据。选择的顺序为先储能电感，后输入输出电容。

#### ● 储能电感 L

根据预先定义的纹波电流值来选择储能电感的电感值大小，纹波电流通常规定为最大负载电流的 40% 即  $\Delta I_L = 40\% * 600mA = 240mA$ ，较大的输入电压 Vin 和输出电压 Vout 导致电流纹波加大，较大的电感则可抑制电流纹波的增加，根据第二章中的稳态分析有：

$$L = \frac{1}{f * \Delta I_L} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right) = \frac{1}{1.5MHz * 240mA} 1.4V \left( 1 - \frac{1.4}{4.2} \right) = 1.3uH \quad (4.1)$$

取 2.2uH 可满足设计要求。同时要注意电感的饱和电流要大于电路最大可提供的负载电流 600mA。

#### ● 输入电容 Cin 与输出电容 Cout

输入输出电容作为电源滤波电容，由于电容内等效串联电阻 (ESR) 的存在，使电容在使用中会将一部分电能转换为热能而发热。从效率和热稳定性角度出发，应尽量选取具有低 ESR 特性的电容，一般认为在额定电流下长期工作所产生的温升应不超过 10 °C<sup>[29]</sup>。

由于控制器内上端的功率 MOSFET 的电流波形为占空比位 Vout/Vin 的方波，控制器从输入源端吸取的脉动电流会造成输入电压的波动，输入电容的主要作用就是为这一脉动电流提供低阻抗的回路，尽量维持输入电压的稳定。输入电容的大小要求与负载，输出电压和输入电源的阻抗有关。输入电容的最大均方根 (RMS) 电流为

$$I_{Cin(rms)} = I_{OUT} \sqrt{D(1-D + \frac{r^2}{12})} = 126 \text{mA} \quad (4.2)$$

其中  $r = \frac{\Delta I_L}{I_{OUT}}$

电容容量越大对输入脉动电流的缓冲越好。频率、电容容量同输入整体电压纹波的具体数量关系如式 4.3 所示，实际选择输入电容时应不低于该式推算出的容量最小值。 $(T_s=1/f)$

$$C_{IN(\min)} = I_{OUT(\max)} \times D_{(\max)} \times \frac{T_s}{V_{IN(ripple)}} \quad (4.3)$$

取 0603 封装的 10uF 陶瓷电容可满足设计要求。

输出电容的 ESR 与输出电压的纹波大小直接相关，由输出纹波要求决定 ESR，关系为

$$V_{out(ripple)} = \Delta I_L \times (ESR + \frac{1}{8 \times f \times C_{OUTPUT(\min)}}) \quad (4.4)$$

对于输出电容的选择主要由 ESR 决定，又因为 ESR 的大小直接与电容的容量大小相关，满足上式的 ESR 要求的电容一般即可有充足的裕度达到电容上 RMS 电流的要求。

综合分析，选用 0603 封装的 10uF 陶瓷电容可满足设计要求。

- 负反馈电阻网络和频率补偿网络

输出电压的调节是通过负反馈电阻网络的分压比来实现的。对于 0.6V 的基准电压，有

$$V_{out} = 0.6 \left(1 + \frac{R_2}{R_1}\right) \quad (4.5)$$

由此决定反馈电阻的比值关系，为减小设定电压的误差选用 1% 精度的电阻器件。

在输出端与反馈端的电阻间并接 22pF 的电容，它与该电阻构成一个超前补偿的零点  $f_z = 1/2\pi RC$ ，可以增加电路的带宽，改善对负载突变的瞬态响应性能。

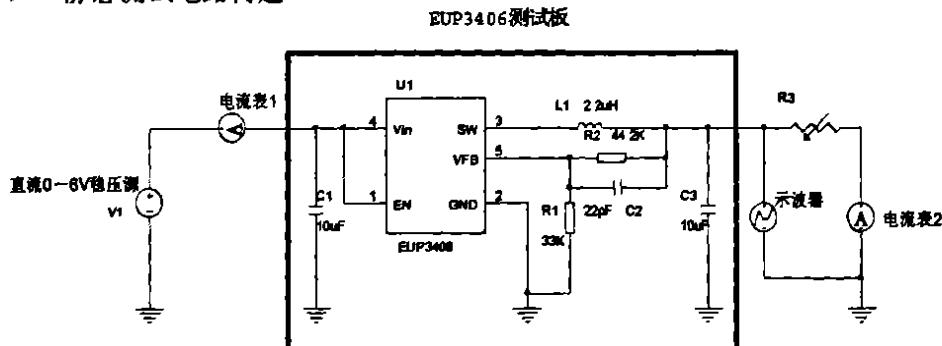

### 4.2.3 电路原理图

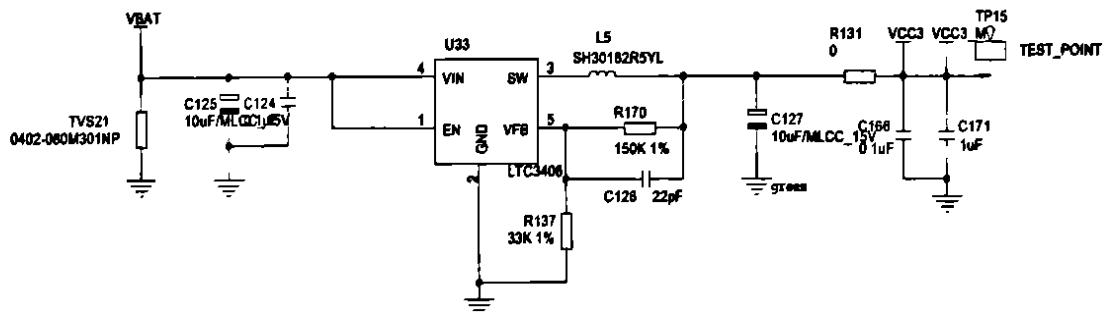

根据以上选型分析和控制器 IC 的功能定义，设计电路图如下：

图 4-2 稳压电路原理图

图中 VBAT 为电池端的电压，VCC3 为系统 IO 电压 3.3V。输入端并联的 TVS 为防静电高压损伤的压敏电阻。R131 为便于系统调试而加入的零欧姆电阻。TP15 为测试点，便于调试测量时与测试设备连接，与输入输出并联的小电容用于滤除高频电源噪声。

## 4.3 电源 PCB 设计

### 4.3.1 稳压电路 PCB 布局布线

手持终端设备内部空间较小，应在电路上充分考虑的前提下，进行合理的 PCB 布局布线，以使电源系统稳定工作。同时，移动终端设备的使用环境复杂，国际上和国内对于这类设备 EMI 的限制较严格，通过在 PCB 布局布线方面多加处理来达到标准要求，相对于电路改进、外壳屏蔽等手段都要廉价和方便。

针对如上这些问题，在 Buck 开关变换器的设计中应遵循下面几个主要原则<sup>[30]</sup>：

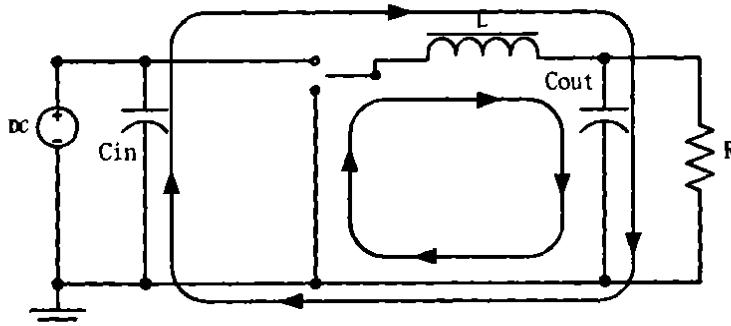

#### ► 减小主电流回路面积

图 4-3 表示了充电和放电的两个主电流回路。由于这两个回路具有较大的开关电流，其谐波成份丰富，会由于环路的天线效应对外造成干扰<sup>[31]</sup>。因此应尽量将输入输出电容、电感、控制器靠近，减少回路面积，这样可以有效的降低对外干扰。同时应尽量使这两个回路的电流在空间上保持同方向流动，这样可以减少由交变电场引起的 EMI 干扰。

图 4-3 开关稳压电源的电流回路

#### ➤ 敏感信号远离干扰源

在降低主电流回路干扰的情况下，还应使变换器内部敏感信号或其他敏感电路尽量远离强干扰区。特别是稳压器内部的反馈端及补偿电路都是高阻输入端，因此极易受干扰，应尽量在布局布线时远离电感及主电流走线，一个有效做法是将其布于PCB的另一面。

#### ▲ 降低电源、地线分布参数影响

PCB 线路板是电气连接的实现手段，当频率和电流大小达到一定量级时其等效 R、L、C 分布参数便不能忽略不计。因此，对于需要大电流走线的电源、地、信号线应尽量缩短加粗，这样可以减小线路等效电阻，提高效率。同时，保证输入输出电容、控制器共地良好，尽量以大面积铺铜作为共地点，将此共地点以多个过孔连接到地平面。

上述三条原则是 Buck 型开关变换器应参考的通用规则，在实际的布局布线应对具体的控制器和外围器件电路特性进行分析，结合通用规则规划具体的布局布线方案。针对 EUP3406 控制器，为减小布线的寄生参数影响和提高性能，具体布局布线建议如下：

- 输入电容尽量靠近控制器输入端 Vin

- 输入电容与输出电容的负端尽可能靠近在一起

- 保证功率通路 Vin, SW, GND 的走线短而粗

- 负反馈电阻网络接于 Cout 和地之间，且控制器反馈端 VFB 直接连到反馈电阻间

- 将噪声节点 SW 的走线远离敏感节点 VFB 节点

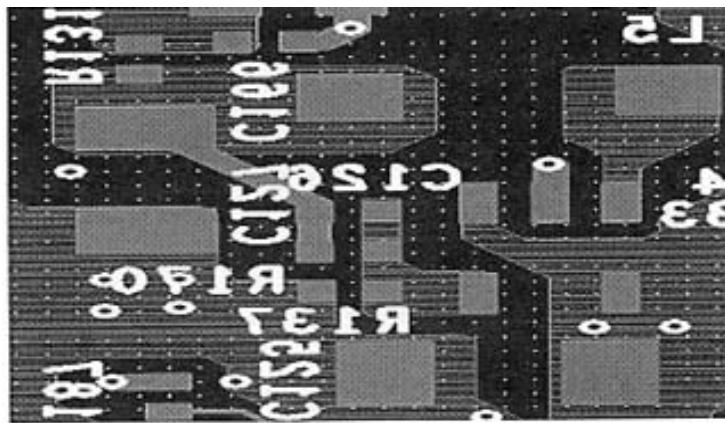

遵循上述通用的和针对具体控制器的原则，稳压电路部分的 PCB 设计如下：

图 4-4 开关稳压电路的 PCB 布局设计

### 4.3.2 电源地层设计

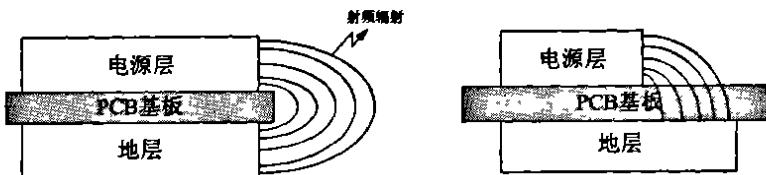

高速数字电路中的电源地层为数字信号的交换提供稳定的参考电压，并且为高速信号提供信号回流路径，同时，完整的电源地层结构对其中的带状线传输的信号提供空间屏蔽功能。对地平面，为保证连续的信号回流路径和屏蔽作用，尽量不要分割。同时，大面积的铜的直流电阻值也很小，有利于减小低频的电源噪声。关于平面层尺寸的规则，可遵循所谓的 20H 规则：为了减少电磁干扰的对外辐射，要求在 PCB 板中所有的电源层的边界都要比地层小 20H，其中的 H 指的是电源层和邻近地层之间的距离。20H 规则的仿真结果如图 4-5 所示。

图 4-5 20H 规则的仿真结果

从图 4-6 中可以看出，当电源与地层之间的距离满足 20H 的时候，能够非常有效的减小对外的辐射。根据文献<sup>[32]</sup>，两层板 20H 规则有比较好的效果，但对于多层板效果会相对差些，综合其他因素，对于地层设计的原则是腐蚀掉尽量少的铜，电源层其次，最后是信号层。

同时，对多层板的层叠设计主要考虑以下几点：

- 稳定、低噪声、低交流阻抗的 PDS

- 传输线阻抗要求

- 串扰噪声抑制

- 空间电磁干扰的吸收和屏蔽

- 结构对称、防止变形

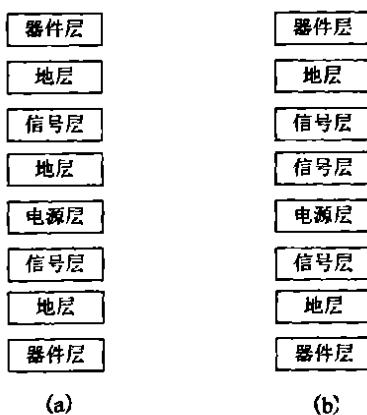

最优的层叠结构应该达到 1) 每一条高速走线必须有一个连续的参考层（电源或地层）2) 每一个电源都应该有一对平行的电容性的电源—地参考层。成对的电源地层还有助于提高整个电路板的机械强度。对于 8 层板来说，最理想的层堆栈应该如图 4-6(a) 所示，但是在实际中为了缓解布线的压力采用了如图 4-6(b) 所示的层堆栈。

图 4-6 理想的层堆栈和实际采用的层堆栈形式

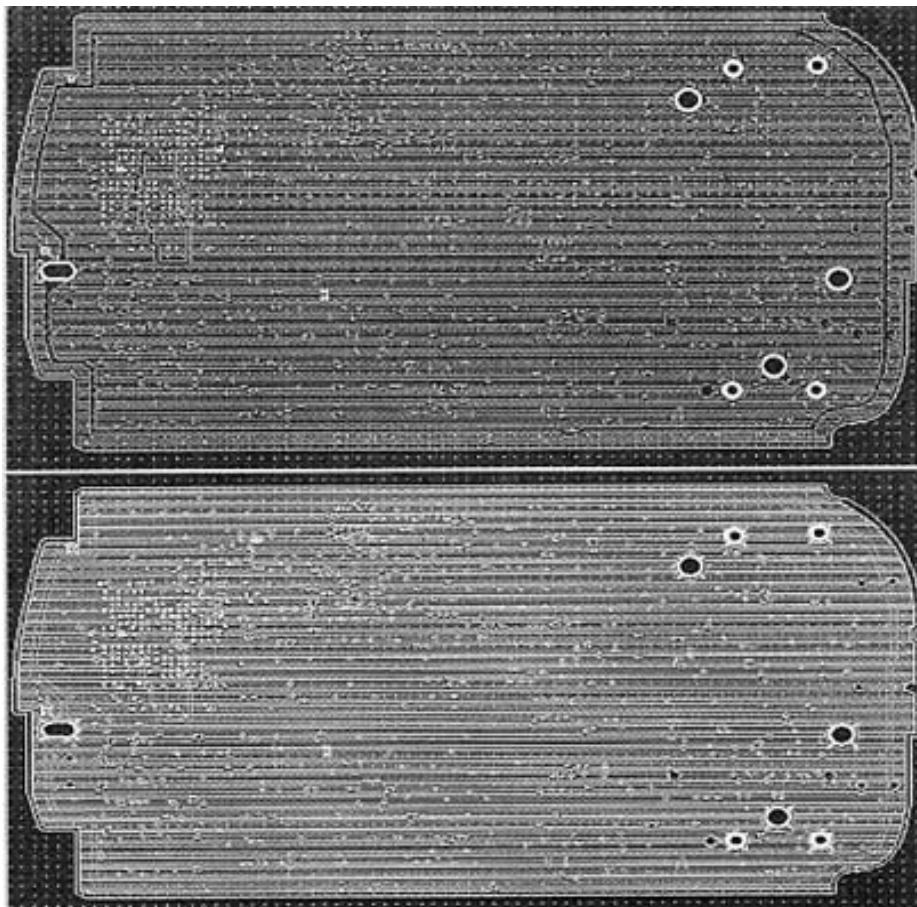

设计的电源地层如图 4-7 所示，黄色为其中一个地层，红色为电源层，其中电源层的靠近边框的 shape 为地网络环路带，在电气上是与地层相连。层上的圆孔为电路板与整机的机械安装定位孔。散布于层上的小圆孔为层间布线所打的过孔 (via)。

图4-7 PCB中的电源/地层

#### 4.4 电源完整性仿真

由于电子产品的更新换代加速，尤其手机、手持娱乐设备等市场潜力巨大的消费电子类朝着小型化、多功能的方向发展，导致在电路板设计阶段面临着高速高密度和信号完整性、电源完整性以及热设计等多方面的挑战。面对巨大的市场需求，已有很多专业的 EDA 软件供应商推出了可用于电源完整性设计的仿真分析软件，如 Cadence 公司的 Allegro PCB PI，Ansoft 公司的 Siwave 系列软件，Sigrity 公司的 SPEED 系列软件等。

本文采用 Cadence 公司的 Allegro PCB PI 作为仿真工具，它可以在 PCB 设计环境中被直接调用，便于在工程设计中采用。

##### 4.4.1 仿真工具简介

本文中仿真工具采用 Cadence 公司的 Allegro PCB Power Integrity 仿真模块，该模块可以对高速 PCB 的电源分配系统进行设计、建模和分析。仿真采用的策略是在系统的工作频域范围内确认 PDS 阻抗满足定义的目标阻抗要求，电源分配系统中包括的部件——稳压模块、各种旁路电容和电源地层均采用较简化的 SPICE 模型，保证了仿真运行的高效率。通过仿真分析决定选用多少规格的旁路电容并联起来并如何布局来满足阻抗要求，结果显示频域内的阻抗/频率曲线。

使用 Allegro PCB PI 模块时，工作流程如下：

1) 设置电路板参数

SQ PI 使用设置向导来建立用于电源完整性分析所必要的 PCB 环境参数：板框、平面层铺铜、DC 网络分配以及 PCB 层叠关系。

2) 定义目标阻抗

根据实际的电路系统电气参数：电源电压，噪声容限和负载情况来定义一个合适的目标阻抗。

- 3) 通过单点仿真进行旁路电容的选择和优化

- 4) 通过多点仿真优化旁路电容的布局

#### 4.4.2 模型分析与建立

##### 4.4.2.1 稳压电路模型

因为 Buck 电路的功率 MOSFET 以时间为参变量周期性的做着开关动作，所以开关管是一个非线性器件，导致整个稳压电路是一个非线性电路。在 Cadence 的 PCB PI 仿真环境里，用 VRM (voltage regulator module) 对开关稳压电路建模，即用等效的 SPICE 电路模型代替非线性的开关稳压电路，实现对电路的仿真计算和分析。

在 PDS 的分析设计中，用 VRM 对开关稳压电路进行建模，重点在于宏观上对稳压电路的功率级与负载间寄生参数的描述，稳压电路对负载瞬态响应的描述，而不需要反映微观上的具体控制器 IC 的实现机制，而且从实际角度来说，因为涉及各个公司的 IP 保护，获取控制器 IC 的电路模型几乎是不可能的。虽然也有很多研究者对各种方式的开关稳压电路建立了各种线性电路模型，但是存在着与电源完整性仿真环境的整合问题，而且电源完整性重点在于整个 PDS 系统的研究与分析，所以用 VRM 对开关稳压电路模拟即可满足了电源完整性的系统设计需求，其精度足以满足用来估计 PDS 中旁路电容的需求<sup>[33]</sup>。

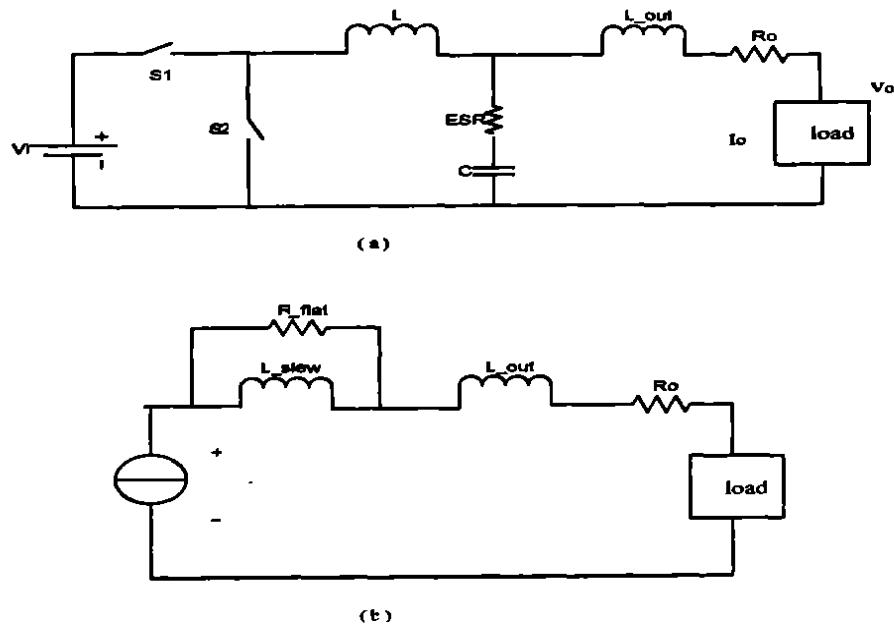

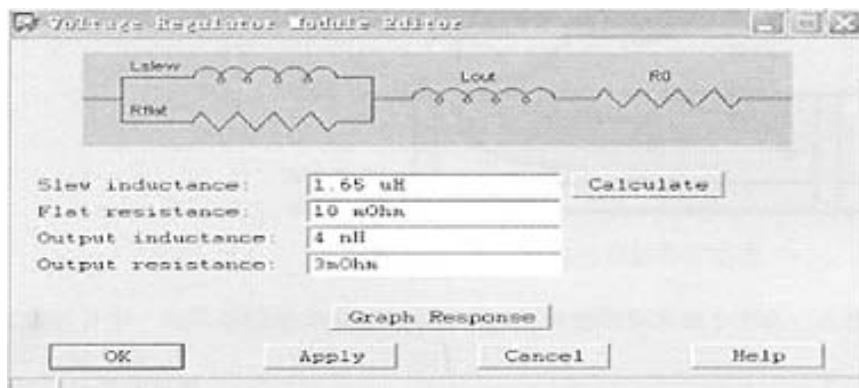

开关稳压电路的功率级电路和 VRM 的线性化模型分别如图 4-8 中 (a), (b) 所示

图 4-8 (a) Buck 电路的功率级 (b) 简化的 VRM 线性电路模型

图(a)中  $L$  和  $C$  为标准 Buck 电路中的储能电感与电容，电阻  $ESR$  为电容  $C$  的串联等效电阻。 $L_{out}$  表示电源的输出电感，来自于负载与 PDS 的连接引脚和电源通路的电感，一般为 nH 数量级，并且 VRM 的最高有效频率也是由  $L_{out}$  决定。 $R_o$  为 VRM 和负载点之间通路的电阻值，电源地层对上一个平方的铜电阻大约是 1mohm， $R_o$  通常为几个毫欧。

图 (b) 中的 VRM 的线性电路模型中由一个理想电压源和一些外围电阻，电感元件构成。理想电压源的电压值为开关稳压电路的输出电压值。外围的大部分无源元件可以从 (a) 中找到对应的原型。其中， $L_{out}$  与  $R_o$  直接从实际的电路中获取，即直接代表 (a) 图中的  $L_{out}$  和  $R_o$ ； $R_{flat}$  代表实际中输出储能电容  $C$  的 ESR 电阻。

$L_{slew}$  是唯一一个在实际电路中找不出对应物理对象的模型元件。从开关稳压电源的电路原理分析可知，整个稳压电路是一个闭环的电压负反馈自动控制系统。当负载电流变化时，由于实际反馈系统的带宽通常为 1KHz 到几百 KHz 范围呢，所以需要一定的时间并采用控制调节机制如 (PWM, PFM 等) 进行调节来维持输出电压的稳定，一般电流型开关电感稳压电路需要至少几个开关周期来完成这一调节。

过程。VRM 中用  $L_{slew}$  对这一负载电流变化的响应过程进行模拟，电感值由  $L_{slew} = V \frac{dt}{di}$  确定。V 为调节过程中的电压噪声大小。 $di$  代表负载电流变化量， $dt$  代表调节过程所需的时间。具体数值可从控制器 IC 的参数数据表中获取。

在仿真过程中可以通过 VRM Editor 对模型的参数进行方便的设定和修改，用户界面如下图

图 4-9 VRM 模型编辑器

#### 4.4.2.2 旁路电容模型

根据 3.2.2 节的分析，电源完整性分析中的旁路电容可用 RLC 串联网络对实际的电容中的 ESR，ESL 和电容值建立模型。但从电容厂家提供的产品数据表中，往往获取不到所需的 ESR 和 ESL 的具体数值。所以一些电容厂家在网站上提供了用于电源完整性仿真的电容模型可供下载，如 TDK 和 Murata 等，这类模型精确度比较高。本设计中采用的是 Murata 的高频陶瓷电容，其参数和模型编号如下表，当然，也可以在仿真软件里建立自己的模型，但往往精度稍差。

表 4-2 旁路电容模型参数

| 模型名称                         | 电容值    | ESR     | 介质  | Nom.inductance* | 谐振频率(Hz) | 封装   |

|------------------------------|--------|---------|-----|-----------------|----------|------|

| CAP_MURATA_GRM155R71E103KA01 | 0.01uF | 10mohms | X7R | 325pH           | 82.2M    | 0402 |

| CAP_MURATA_GRM155F51E104ZA01 | 0.1uF  | 10mohms | Y5V | 325pH           | 25.9M    | 0402 |

| CAP_MURATA_GRM188F51C105ZA01 | 1uF    | 10mohms | Y5V | 325pH           | 8.21M    | 0603 |

| CAP_MURATA_GRM31MF51A106ZA01 | 10uF   | 10mohms | Y5V | 325pH           | 2.59M    | 1206 |

\*注：Nom.inductance 为模型指定的默认寄生电感量，此时的电感值没有考虑到电容在 PCB 的布局和安装寄生电感，实际仿真时要修正该值，相应的谐振频率也将发生改变

- 模型的主要文件组织

- (Decap Capacitor Library,DCL)文件是一个以 dcl 为后缀的 ASCII 文件，指定了电容族的分组，每一个电容族具有一些共同的特性如：装配类型，温度和湿度系数等。不同的电容族用不同的名称加以区别，这个名称也是对 device files 的索引依据。

- (Device Files)器件文件是一个文本文件，文件名为“dcl 文件中的电容族名称.txt”，器件文件定义了电容在 PCB 设计中的器件位号，封装符号文件 (\*.psm)，装配的表面焊盘文件 (\*.pad) 以及电容在仿真中的信号模型。

- (Device Model Library) DML 模型文件定义了模型中的电气参数，包括电容值，电容固有寄生电感 (intrinsic inductance) , 安装寄生电感 (nominal mounted inductance) 和等效串联电阻 (effective series resistance)。

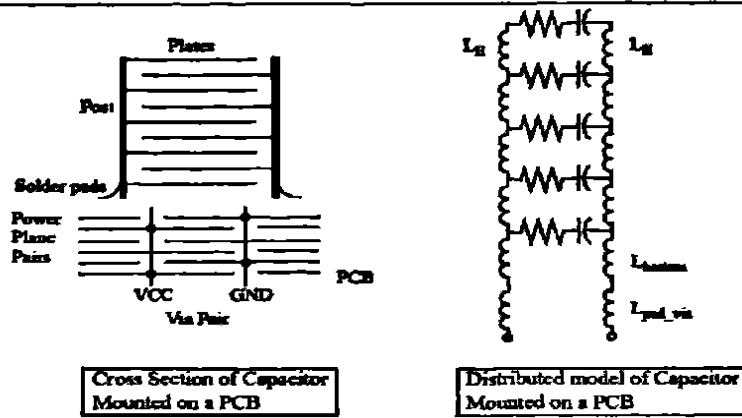

- 模型中电容 ESL 的分析

电源完整性分析中的电容模型与信号分析中的电容模型的重要区别就是要考虑到电容的 ESR 和 ESL 参数的影响。而 ESL 在频域范围内又影响到电容的谐振频率，电容组的反谐振频率等，旁路电容的作用在谐振频率点效果最佳。同是，减小反谐振点幅度的最有效的方法就是减小电容的 ESL。所以电容的 ESL 对旁路电容的具体效果具有十分重要的影响。

电容的 ESL 又受到实际 PCB 环境的影响，对于表面安装的电容，具体主要有以下部分：

- 1) PCB 上的焊盘 (PADS) 布局

- 2) 电容厚度 (即 intrinsic inductance, 电容的固有寄生电感)

- 3) 电源地层, 过孔等的分布电感 (即 nominal mounted inductance 电容的安装寄生电感)

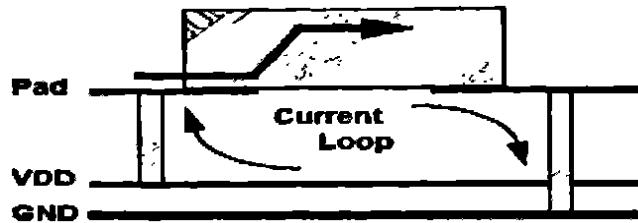

- 这三部分构成一个闭合的电流回路, 如图 4-10 所示, 如果回路的面积越小, 电容的 ESL 越小。

### Mounted Capacitor

图 4-10 旁路电容的安装寄生电感

在 PCB 设计中, 应尽可能减小旁路电容的电流回路的面积来减小 ESL, 在模型中需要对电容的安装寄生电感加以考虑

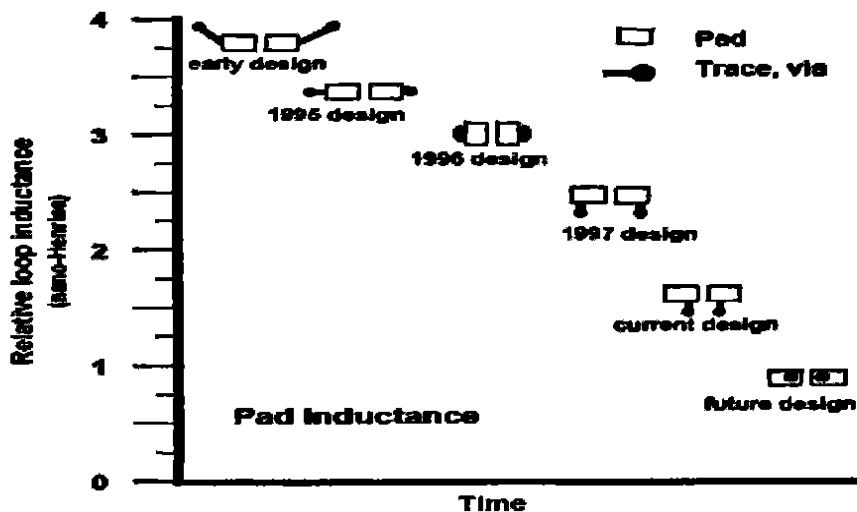

#### ➤ 过孔与焊盘布局

过孔与电容焊盘布局与 ESL 的关系如图 4-11 所示

图 4-11 旁路电容的焊盘连接设计趋势

总的设计原则是过孔要尽量靠近电容的焊盘, 采用短而粗的连接线, 电源与地层间距越小越好, 图中最右下角的是采用过孔打在焊盘上的方式, 可以获得最小的寄生环路电感量。在目前 PCB 工艺中盲孔可以采用这种方式, 但盲孔的制板成本要增加将近一倍, 所以设计中需结合成本分析, 综合考虑。

#### ➤ 电容的厚度

今天业界广泛采用的陶瓷电容为 MLCC (Multi-layer Ceramic Capacitor) 多层陶瓷电容, 由于陶瓷薄膜堆叠技术越来越进步, 使得所生产出来的电容值也越来越高, 已逐渐取代了电解电容和钽质电容。表面贴装 MLCC 电容器件的高度对在工作时的电流环路也产生一定的影响。

图 4-12 贴片 MLCC 电容的分布模型

由图 4-12 的电容的分布模型可以看出电容高度越大，导致电流环路越大，寄生的电感量也随之越大。在 Allegro PI 的电容模型中电容厚度的影响反映在模型的固有寄生电感参数中。本课题所选用的各种电热厚度如下表 4-3：

表 4-3 旁路电容厚度

| 电容 (uF) | 0.01 | 0.1 | 1   | 10  |

|---------|------|-----|-----|-----|

| 厚度 (mm) | 0.5  | 0.6 | 0.8 | 1.0 |

#### ➤ 安装寄生电感 (Mounted inductance)

旁路电容在 PCB 板上的安装寄生电感量是影响电源完整性的一个关键因素。它是包含电容引脚，焊盘的连接，连接的布线，过孔和电源地层对间介质的介电常数，层距等构成外部的电流环路因素的影响总和构成的环路电感，因而随着板上安装位置，过孔尺寸的不同而不同。

安装寄生电容在模型中的体现为 nominal mounted inductance 参数。Cadence PI 工具中用一个称为 FastHenry 的仿真器对每一个具体的电容器件估算出电容的安装寄生电感量，计算出的值并不保存在模型中，而是保存在一个临时数据文件中，该文件生成于当前进行 FastHenry 计算的电容模型所在的当前目录下，模型中仍保存着指定的缺省值，仿真计算时用计算出的值替换掉模型中的缺省值。

此时计算出来的安装电感还没有考虑到电容焊盘的连接引线的寄生电感，在进行后面所述的多点仿真时，再考虑上述因素，这样就完整了模拟了电容在实际 PCB 环境中各种因素所造成的总的环路寄生电感量。

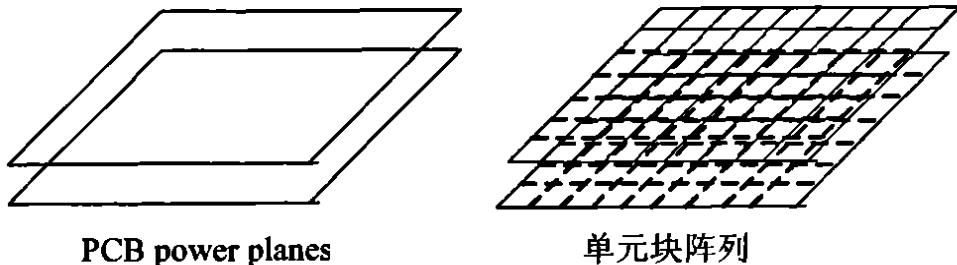

#### 4.4.2.3 电源地层模型

在 Allegro PCB PI 环境中，根据电源层的几何结构和材质建立 SPICE 模型，用于电源完整性的仿真分析，在单点仿真时将电源地层用一个集总的电容模型代替，在更精确的多点仿真中用分布参数模型对其进行模拟，采用 SPICE 模型比一般的场求解方法要快，且能与开关电源，旁路电容和负载的等效 SPICE 模型集成在一个电路分析环境中，具有更高的效率。

在 4.4.1 节中阐述的仿真流程的第一步，设置电路板（以矩形为例）参数中，提供了以下参数

- 电源层长度  $l$

- 电源层宽度  $w$

- 层间电解质厚度  $d$

- 电介质介电常数  $\epsilon$

- 铜皮厚度  $t$

正是基于这些参数对电源地层建立模仿其行为的电路模型

#### ● 集总参数模型

低频时，从电源地层的 PCB 结构可以看出，电源层和地层以及中间的电解质构成了一个平板电容器。所以可以用平板电容器的公式对其电气行为进行近似描述：

$$C = \epsilon \frac{wl}{d} \quad (4.6)$$

$C$  为电源地层间的单位面积电容, 单位为法拉

- 分布参数模型

集总的电路模型只有在电路元件的尺寸相对所承载的信号的波长“很小”时才是有效的<sup>[34]</sup>, 因为实际的电路板环境中往往包含有频带很宽的谐波信号成分, 高频谐波信号的波长就会与电源层的尺寸处于同一个数量级, 导致集总的电路模型不再有效。所以需要用分布的参数模型才能更好的模拟电源地层的电气行为, 分布参数模型的基本思想是将电源地层划分为多个小的单元块, 如图 4-13 所示, 这样划分的前提是层间距  $d$  相比层的几何空间尺度  $w$  和  $l$  而言是很小的, 实际中也确实如此。

图 4-13 电源地层单元块模型

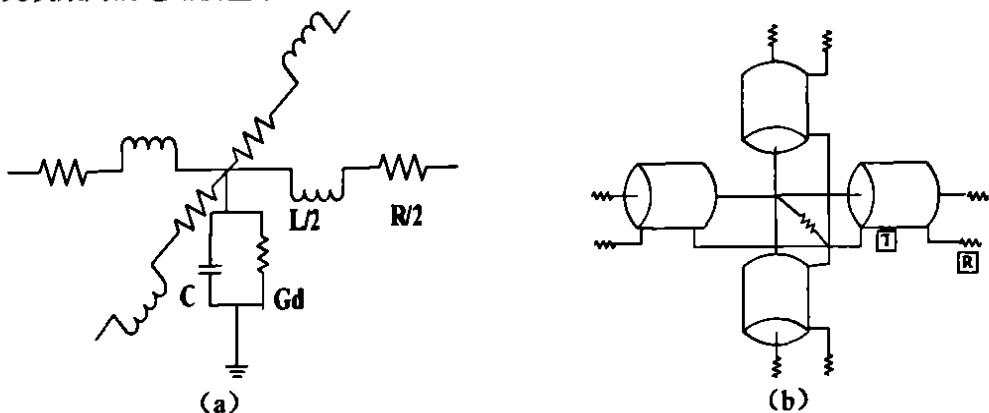

- 单元块的电路模型

对单元块采用的电路模型常用的有 1) RLGC 单元和 2) 传输线单元

图 4-14 电源地层单元块电路模型

分布如图 4-14 (a) 和 (b) 所示, 具体参数定义如下

在 (a) 中<sup>[35]</sup>:

$$\begin{aligned} C &= \epsilon \frac{wl}{d} & L &= \mu_0 d & R_{dc} &= \frac{2}{\sigma_c t} \\ R_{ac} &= 2 \sqrt{\frac{\pi f \mu_0}{\sigma_c}} & G_d &= \omega C \tan(\sigma) \end{aligned} \quad (4.7)$$

式中  $\mu_0$  表示自由空间的导磁率, 其值为  $4\pi \times 10^{-7} H/m$

$\sigma_c$  为铜的电导率, 单位为西门子/米

$R_{dc}$  电源和地层的金属铜的直流电阻,  $R_{ac}$  是由电流的趋肤效应引起的交流电阻,  $f$  为信号的频率, 这两部分共同组成  $R$ 。层间的介质损耗由电导  $G_d$  表示, 其中  $\tan(\sigma)$  为介质的损耗角,  $\omega$  为信号角频率, 单位为弧度/秒。

因为电源和地层的直流电阻很小, 考虑无损传输线的条件下, 在传输线单元块中, 需要确定的参数是特性阻抗  $Z_0$  和延迟时间  $t_d$ , 电源层间单位面积的电容为  $C_a = \frac{\epsilon}{d}$  单位为法拉/单位面积, 在层间介质中平面波的传播速度为:

$$v = \frac{C_{light}}{\sqrt{\epsilon_r}} = \frac{1}{\sqrt{L_a C_a}} \quad (4.8)$$

$C_{light}$  为真空中光速,  $\epsilon_r$  为层间电介质的相对介电常数,  $L_a$  为电源层的每平方电感量, 单位为亨利/每方

由式 4.7 可得:

$$L_a = \frac{1}{C_a v^2} \quad (4.9)$$

由  $L_a$  和  $C_a$  即可确定传输线单元模型的特性阻抗和延迟分别为

$$Z_o = \sqrt{L_a / C_a} \quad t_d = \sqrt{L_a C_a} \quad (4.10)$$

$L_a, C_a, Z_o$  和  $t_d$  四个参数只要确定了其中两个即可推出其余两个参数, 从而足以全面描述不考虑直流损耗的电源地层的传输线特性<sup>[36]</sup>。

图中 T 即为理想无损传输线单元, R 代表传输线的损耗, 与 RLGC 单元中的类似, 主要包括以下几个方面:

电流的趋肤效应: 随着频率的升高, 电流趋向于在导体的外表面上流动, 产生趋肤效应, 使得电路流过的横截面很薄, 导致铜层的电阻加大。在趋肤效应存在时电源地层的传输线单元中损耗电阻

$$R = \frac{l}{w \sigma_c \min(t, \delta)} \quad (4.11)$$

其中  $l, w$  分别为电源层的长和宽,  $t$  为铜层厚度,  $\sigma_c$  为铜的电导率,  $\delta$  为趋肤深度, 有  $\delta = \frac{1}{\sqrt{f \mu \pi \sigma_c}}$ ,  $f$  为信号频率,  $\mu$  为电源铜层的导磁率。

介质损耗: 来源于层间电介质的电导性, 与频率和电容量成正比, 如式 4.6 中最后一个方程所示。

#### ► 单元块的划分

数字系统中的信号在时域的波形多为近似的方波或梯形波, 包含着丰富的谐波信号成分, 以 50% 占空比, 频率为 F 的理想方波信号为例, 其傅立叶表达式为:

$$f(t) = \frac{2}{\pi} \sum_{n=1,3,5,\dots} \frac{1}{n} \sin 2\pi n F t \quad (4.12)$$

从式中可以看出该信号包含了频率为 F 的基波信号和频率为 3F, 5F... 的奇谐波信号成分, 实际中由于很少有绝对的 50% 的占空比, 所以还包含有偶谐波信号成分。任何谐波的幅度可由  $2/(n\pi)$  计算得出, 所有谐波及其幅度的集合构成了信号的频谱。

带宽用来表示频谱中有效的最高正弦波频率分量, 对于上升时间有限的任何波形, 有效指的是信号的谐波幅度高于相同频率的理想方波中相应谐波幅度的 70% 时的那个频率点, 也称为拐点频率 ( $F_{3dB}$ )。

虽然可以通过 FFT (快速傅立叶变换) 求得时域中信号的频谱, 从而得出信号的带宽, 但工程中信号的完整时域描述或解析表达往往很难达到, 所以经常通过一些容易获取的参数来估算信号和系统的带宽:

#### 1) 基于上升时间 RT 的估算<sup>[37]</sup>

标准的信号上升时间的指从最大信号摆幅的 10% 到 90% 所需要的时间。一个时间常数为  $\tau$  的网络的阶跃电压输入信号的响应由以下方程确定:

$$V = V_{input} (1 - e^{-\frac{t}{\tau}}) \quad (4.13)$$

$t$  为时间变量,  $V_{input}$  为输入电压, 如果假设输入电压为 1V, 则响应的电压上升时间

$RT = 2.195\tau$ , 网络的频率响应的 3dB 频点  $F_{3dB} = \frac{1}{2\pi\tau}$ , 联立上述两式有  $RT = \frac{1.09}{\pi F_{3dB}} = \frac{0.35}{F_{3dB}}$ , 即

$$\text{带宽 } BW = F_{3dB} = \frac{0.35}{RT} \quad (4.14)$$

虽然这种分析不能完全应用在实际的系统中, 因为理想的阶跃信号是不存在的, 但  $F_{3dB}$  仍然是对数字信号进行频谱分析的有效参数, 因为该频点下包含了绝大部分的频谱能量。

## 2) 基于时钟频率 $F_{clock}$ 的估算

在很多情况下并不是总能知道某个波形的上升时间，在已知系统的时钟频率的条件下，假定上升时间是时钟周期的 7%，这与许多微处理器和 ASIC 驱动板极总线的情况接近<sup>[25]</sup>，因此根据这个假定，再结合 1) 中的结论，可估算出带宽与时钟频率的关系式：

$$\text{带宽 } \text{BW} = 5 \times F_{clock} \quad (4.15)$$

在确定了信号的带宽及考虑的最高频率成分后，采用业界通用的规则，所选模型的单元尺寸小于最高频率信号的波长的十分之一，可得到满意的运算精度。

本课题的硬件平台中板级上最高频率信号为 SDRAM 的时钟信号，频率最高可配置为 99.5M，据此估算系统中板级上信号的带宽为

$$\text{BW} = 5 \times 99.5 \text{MHz} = 497.5 \text{MHz}, \text{ 以 } 500 \text{MHz} \text{ 代之。软件仿真带宽设置为 } 1 \text{GHz, 可满足分析的要求。最高频率分量信号的波长为 } \lambda = \frac{c}{f} / \sqrt{\epsilon_r} = \frac{3 \times 10^8 \text{ m/s}}{500 \text{MHz}} / \sqrt{4.5} = 28.3 \text{mm}$$

$C$  为真空中光速， $f$  为信号频率， $\epsilon_r$  为板层电介质的介电常数。课题中硬件板的外框以近似矩形结构表示为长 105mm，宽 61mm，为了使单元的尺寸小于 1/10 的最高频率信号的波长即 2.83mm，将整个层划分为 40X25 的网格结构。当然，划分的越细，计算的精度越高，代价是需要的运算时间也越来越大，所以，在满足 1/10 通过规则的前提下，还可在精度和时间之间进行折中性选择。

### ➤ Allegro PCB PI 采用的电源地层模型

Allegro 中 PI 分析采用的是传输线单元模型，单元结构即为上文论述过的图 4-12 中 (b) 所示的结构。基本形式为星型连接的四个传输线单元构成（在各边界处为三个传输线单元），因为在 x 方向和 y 方向都有传输线单元，所以重复计算了层的电容。导致计算出的特性阻抗下降了  $\sqrt{2}$  倍，信号速度上升了  $\sqrt{2}$  倍，在软件进行计算时会进行补偿纠正。在每个节点，一个传输线单元与三个相似的传输线连接的这种结构，导致了各传输线终端都没有被良好的进行阻抗匹配的端接，会出现传输线的谐振，影响仿真的精度，但是，当选用足够小的单元尺寸后，一个单元的传输时间小于信号上升时间的 20% 时，使得在一个上升时间内，传输线的近端影响远端两次，从而大大减小的信号反射的影响，提高了仿真的精确度。

对于非矩形结构的板外形结构，和板上存在的通孔，当划分的单元尺寸比通孔尺寸小时，通孔的影响就可以忽略了，对非规则的复杂外形结构，通过细分单元并进行矩形化近似，可以将不规则的结构影响降低。

在层模型建立后，在频域内对每个节点处的阻抗进行分析，每个节点的互阻就表示当一个电源地在此节点连接时所看到的频域的 PDS 的阻抗，不同的节点阻抗也说明了在空间上板上不同位置的电压噪声也是不一样的。

### 4.4.2.4 负载模型

对于大多数的 CMOS 工艺的器件而言，输出阻抗一般为几十至一百欧姆，相比于 PDS 的阻抗很大，所以对直流的电压源来说，可以将负载器件当作一个的电流源，即噪声电流源，根据实际运行时负载最大的电流变化量设定噪声电流源的参数。

### 4.3.3 仿真与分析

在设置完成电路板物理参数和建立 PDS 中各部分的模型后，就可以进行仿真确定旁路电容的用量和在 PCB 上的布局，确认在完成设计后是否达到系统所要求的目标阻抗。

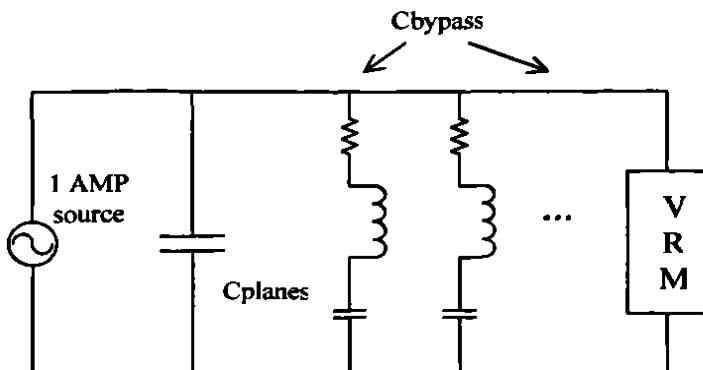

#### 4.3.3.1 单点仿真

在 Allegro PCB PI 中通过单点仿真 (single-node) 根据电路板工作环境而设定的目标阻抗，确定旁路电容的选择，此时电源地层用集总参数的一个电容代替，并且此时旁路电容并没有被放置在实际的电

路板上，因而没有考虑具体的电容布局的影响。但是如果单点仿真中选择的电容不能满足目标阻抗的要求，在考虑到实际电容布局的时候，也一定同样不能满足目标阻抗的要求，所以进行单点仿真时是进行PDS设计的重要一个环节，通过此环节来决定需要多少的旁路电容，仿真基于的原理图如下：

图 4-15 单点仿真原理图

在 SPICE 仿真器中通过加一安培的交流信号源进行频域扫描的交流 AC 仿真，即可得出 PDS 的阻抗与频率的关系，并与目标阻抗比较，仿真结果以直观的图形显示。

在进行仿真前需要根据实际的电路板设置好各项参数，如板外框，层叠情况等，需要注意的是 Allegro PCB PI 将板外框以最接近实际的矩形拓扑代替，电路板物理环境的参数见下表：

表 4-4 电路板物理参数

| 参数 | 板外框尺寸      | 板层 | 板厚  | 铜厚    | 介质层厚  | 介质材料 | 介质介电常数 |

|----|------------|----|-----|-------|-------|------|--------|

| 数值 | 105mmX61mm | 8  | 1mm | 52 微米 | 80 微米 | FR4  | 4.5    |

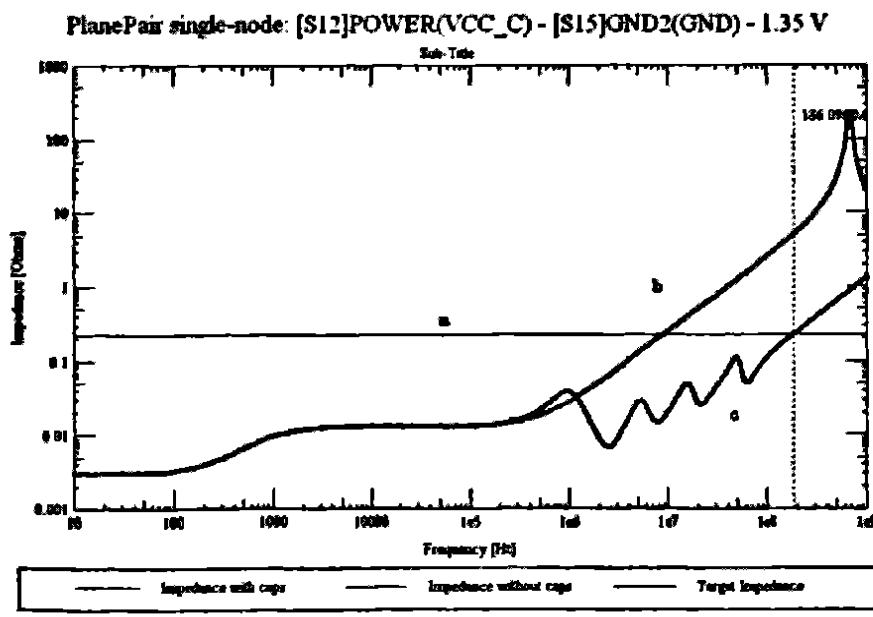

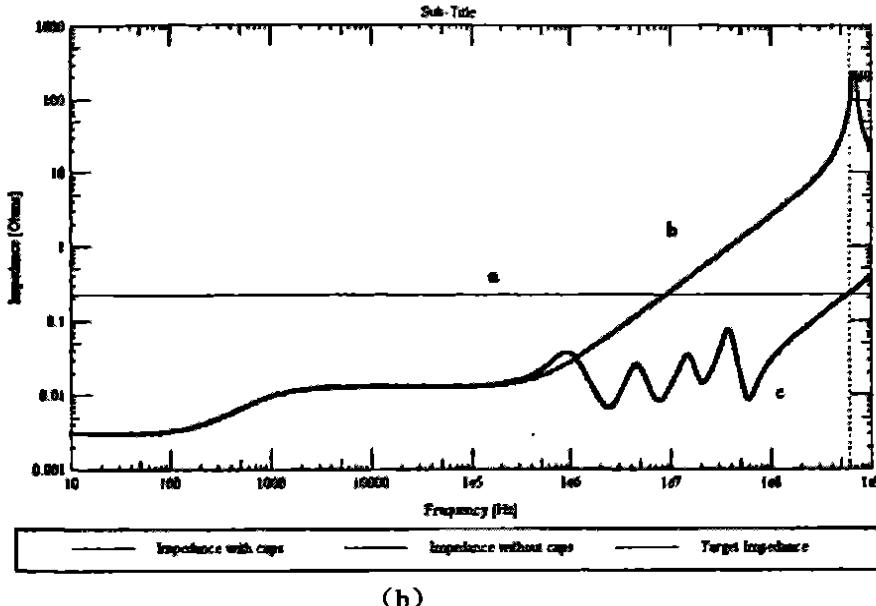

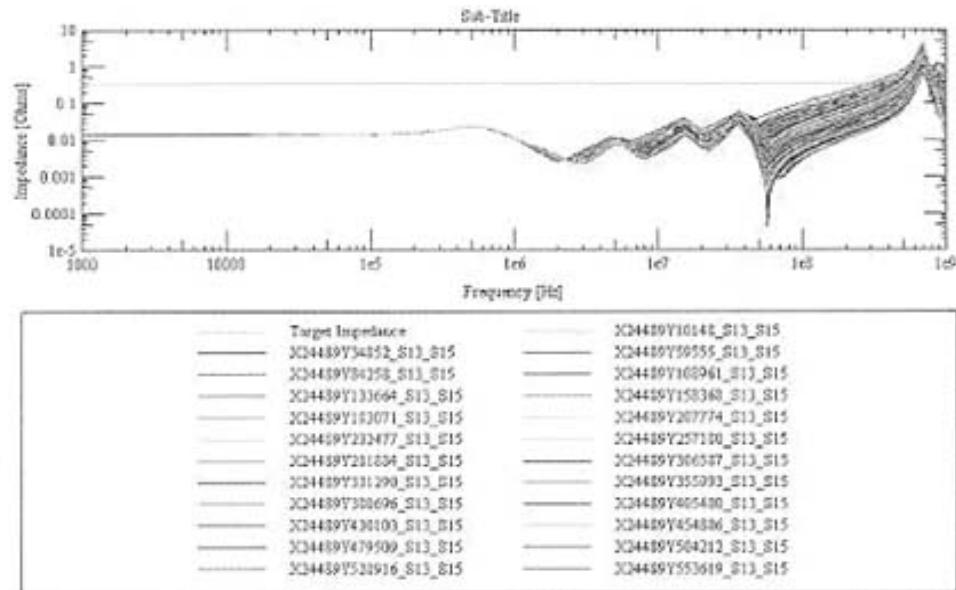

- 核电压 VCC\_C 的单点仿真

仿真环境参数如表 4-5 所示

表 4-5 单点仿真参数

|          | 电压   | VRM    |        |       |       | 噪声容限 | 目标阻抗    | 分析频带    |

|----------|------|--------|--------|-------|-------|------|---------|---------|

|          |      | L slew | R flat | L out | R o   |      |         |         |

| VCC_C 系统 | 1.35 | 1.65uH | 10mohm | 4nH   | 3mohm | 5%   | 225mohm | 10-1GHz |

| VCC3 系统  | 3.3  | 1.65uH | 10mohm | 4nH   | 3mohm | 5%   | 330mohm | 10-1GHz |

(a)

PlanePair single-node [S12]POWER(VCC\_C) - [S15]GND2(GND) - 1.35 V

(b)

图 4-16 VCC\_C 单点仿真阻抗曲线

图(a)中直线 a 为目标阻抗线, b 为没有加旁路电容的阻抗线, c 为各加了一颗表 4-2 种列出的电容的阻抗线。从 b 可以看出在较低的频段内由 VRM 保持了低于目标阻抗的值, 在大于 10MHz 左右时, 由于 VRM 与负载的连线电感导致阻抗大于目标阻抗, 且阻抗一直随频率上升, 直到约 700MHz 之后, 此时电源地层的电容开始发挥作用, 引起阻抗随频率下降而下降。

在曲线 c 中, 由于旁路电容的作用, 使 PDS 在直到 186MHz 范围内阻抗都低于目标阻抗, 曲线出现了几个峰值点是由于电容间的 ESL 和电容发生并联谐振引起。但 186MHz 仍然不满足所关心的 500MHz 的带宽要求, 需要增加谐振频率高的旁路电容量。

增加 0.01uF 电容到 8 颗, 0.1uF 和 1uF 各 2 颗, 得到阻抗曲线如图(b)所示, 此时 PDS 低于目标阻抗的频率加大到 680MHz 左右, 满足设计要求。

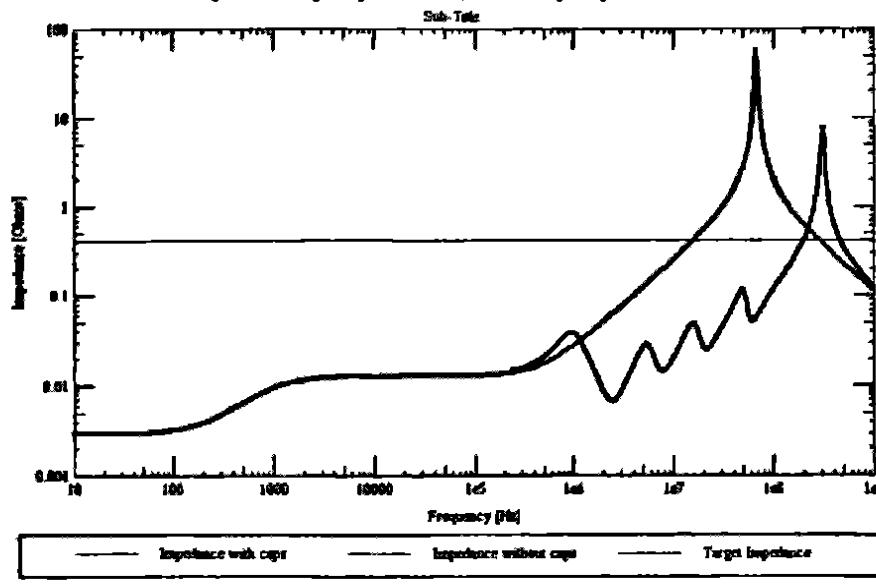

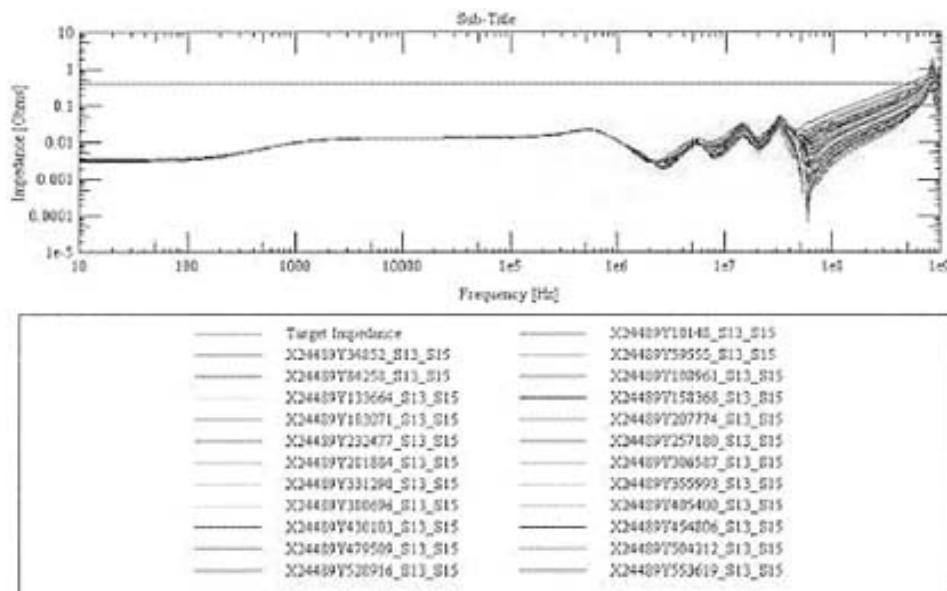

- IO 电压 VCC3 的单点仿真

目标阻抗设定值见上表 4-5, 类似的仿真所得阻抗曲线示于图 4-17, 图 (b) 中的旁路电容配置为 30 颗 0.01u, 0.1u, 1u 和 10u 各 3 颗。

PlanePair single-node [S13]POWER(VCC3) - [S15]GND2(GND) - 3.3 V

(a)

图 4-17 VCC3 单点仿真阻抗曲线

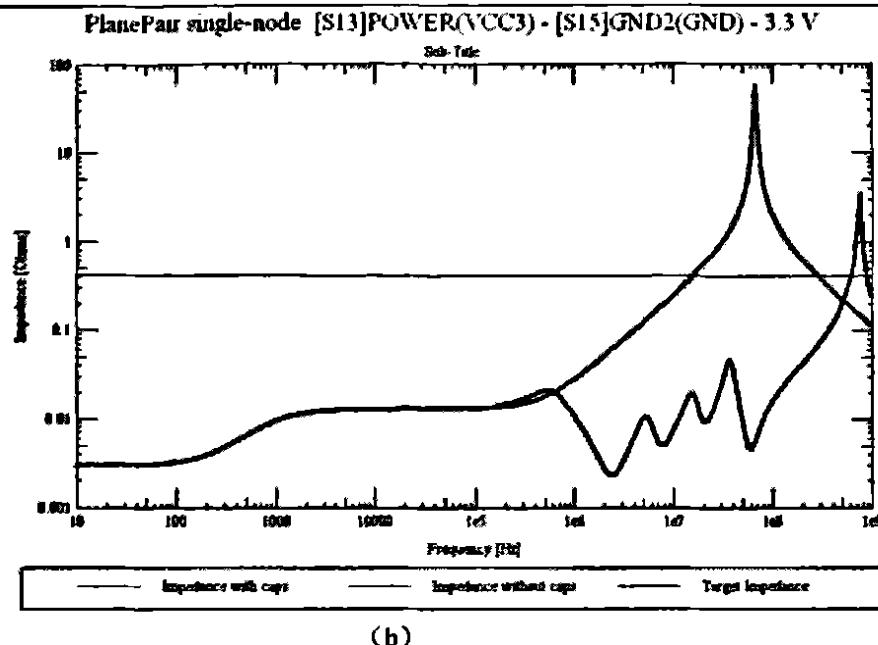

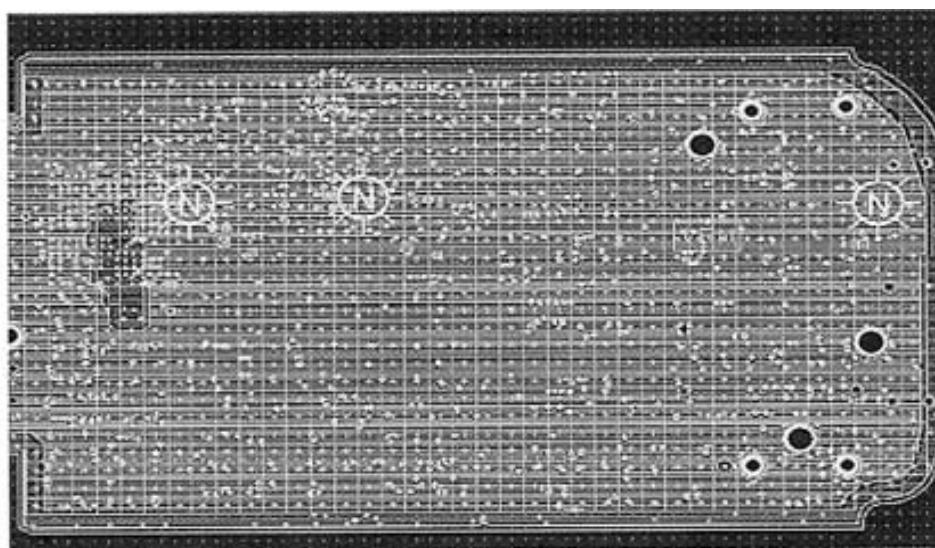

#### 4.3.3.2 多点仿真

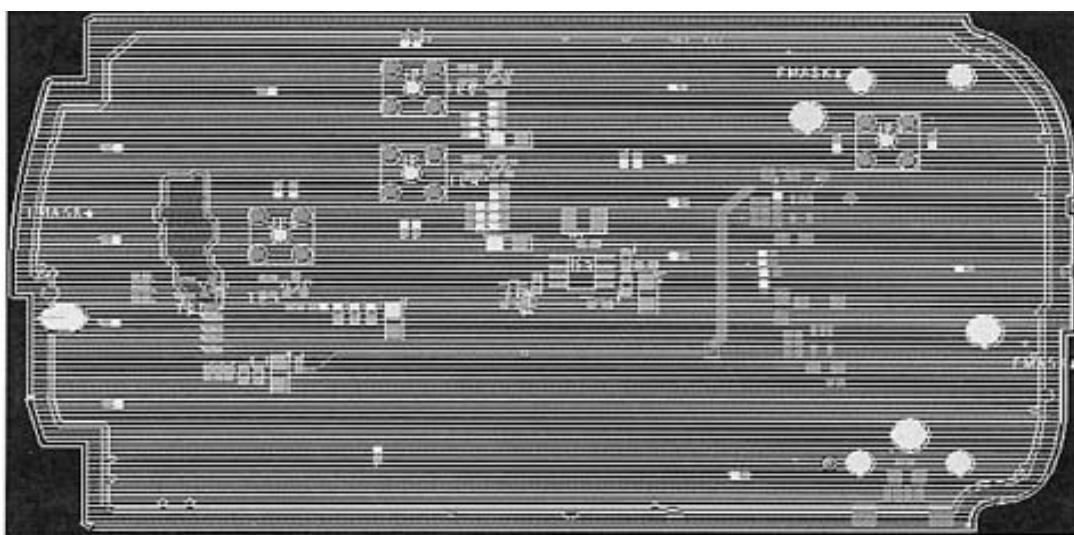

多点仿真与单点仿真的区别在于它考虑了电源地层的寄生参数和旁路电容在 PCB 上布局的影响，从而更加接近实际的电路环境，在完成单点仿真确定了旁路电容的选择后，在 PCB 上依次放置 VRM，模拟负载的噪声电流源和旁路电容，并进行旁路电容安装寄生电感的参数计算，加入到待仿真的电容模型中，最后设置电源层模型的单元块划分 40X25，完成后，PCB 如图 4-18 所示，图中根据实际的电路板布局放置了代表处理器，SDRAM 和音频单元这些电流较大的负载的噪声电流源，网格显示了电源层划分的单元模型。

图 4-18 多点仿真的 PCB 截图

VCC3 系统的旁落电容预布局的多点仿真如图 4-19 (a)，图中的曲线族代表板上不同空间节点的阻抗曲线，可以看出有部分曲线在系统带宽范围内超过了目标阻抗线，通过 crossprobe 功能找出在系统带宽范围内 (500MHz) 阻抗大于目标阻抗的位置，增加这一区域的电容分布，从而改善 PDS 的阻抗特性，经多次重新布局电容后得到 (b) 的阻抗曲线，在整个板空间和整个带宽范围内，达到了设计要求的目标阻抗。

(a)

(b)

图 4-19 VCC3 多点仿真阻抗曲线族

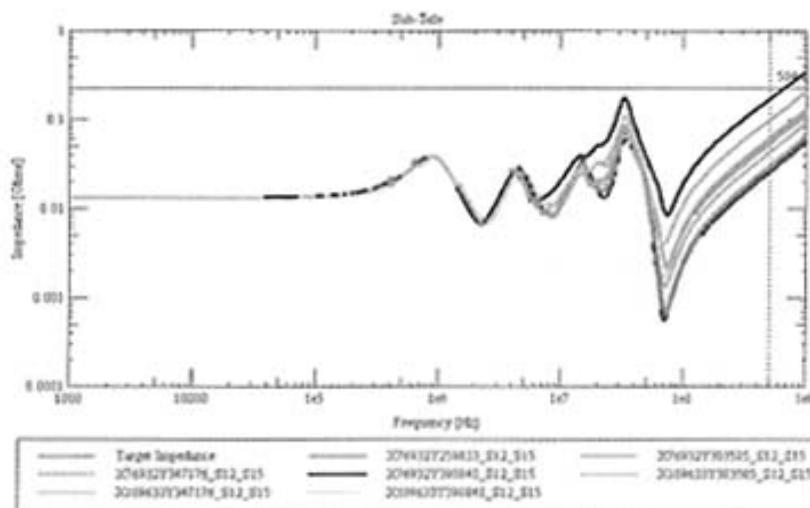

VCC\_C 部分因为只有一个负载即 CPU 且层面积比较小，单元分布数设为 2X4，旁路电容的布局相对容易确定，经多点仿真波形如下：

图 4-20 VCC\_C 多点仿真阻抗曲线族

通过仿真分析得出以下几点 PDS 的设计原则：

- PDS 阻抗设计的关键就在于旁路电容的选用和布局，因为电容在 PCB 板上的安装寄生电感影响了电容的谐振频率，寄生电感的增加，降低了电容的自谐振频率点，影响了电容的有效频率范围，通过并联多个电容，等效于多个 ESL 并联，从而减小了总的 ESL，缓解了因为安装寄生电感的不利影响。

- 对于电流较大的负载，附近要分布足够的各种规格的电容以实现去耦的作用，小电容因为厚度小，安装寄生电感也小，谐振频率最高，用于高频去耦，同时要分布适当的大电容，以满足负载在状态切换过程中的电流所需的足够电荷量。

- 为保证整个 PCB 中的 PDS 阻抗在空间上尽量保持一致，需要将高频下发挥作用的小电容均匀分布在整個板空间上，以抑制电源层的谐振引起的阻抗加大。

- 电容的 ESL 包含本身固有 ESL 和安装寄生的 ESL。高频时，安装寄生的 ESL 对电容的行为起主导作用，通过改变电容的安装位置（如 TOP 或 BOTTOM 层），电容的焊盘，引线连接方式，以及板层间的介质厚度都会影响到电容的在 PCB 上的寄生环路电感量，从而对旁路电容的效果产生重要影响。

## 4.5 本章小结

- 电源电压变换电路的设计内容包括：分析输入源和负载环境的要求，确定电压变化的技术方案（线性电源，开关电源等），本课题选用开关电源，首先选定控制器 IC，然后根据纹波电压，电流电压极限值等技术参数进行电感电容等无源器件的选型设计。

- 高速电路中采用的 PCB 电源地层的设计方式，不仅对降低电源通路阻抗，减小电源电压噪声，保证系统的电源完整性具体十分重要的意义，对降低系统的 EMI，加强层间信号的屏蔽和电路板的机械强度也有很大帮助。

- 目前很多专业的 EDA 软件供应商都推出了可用于电源完整性设计的仿真分析软件模块，如 Cadence 公司的 Allegro PCB PI, Ansoft 公司的 Siwave 系列软件，Sigrity 公司的 SPEED 系列软件等，本文中仿真工具采用 Cadence 公司的 Allegro PCB Power Integrity 仿真模块。

- 旁路电容的选择和布局是电源分配系统设计中的一个重要环节，旁路电容在其串联谐振点具有最佳的去耦效果，但电容在 PCB 上由焊盘，过孔，连线等构成的安装寄生电感的存在降低了它的谐振频率，故削弱了电容在高频部分的去耦能力。

- 通过旁路电容的电流回路面积越大，安装寄生电感越大，所以容值越大的电容往往其安装寄生电感越大。在电源分配系统中要选用多种容值的旁路电容分布其间。

- 旁路电容的布局对保证整个 PCB 板空间内的电源分配系统阻抗一致性具有重要作用，对电流大的负载器件要设计足够的电容量和不同谐振频率的电容对其进行旁路，并将电容靠近其安装。

## 第五章 测试与分析

### 5.1 电压变换电路性能测试

电压变换电路的性能指标分静态性能和动态性能两部分，静态性能包括电压纹波，变换效率等，动态性能主要指电路对负载突变和源电压突变的动态调节性能，在电池供电的手持设备中，效率是个重要的考虑因素。在实际使用环境中电路的动态性能受旁路电容，PCB 寄生参数等 PDS 系统部件的影响，所以通过在电源分配系统的电压时域实测代替单纯的电压变化电路的动态测试，故本小节所述内容只含静态测试。

#### 5.1.1 测试环境

- 测试工具：万用表：FULUX      示波器：TEK 100MHZ    电源：ATTEN 30V/5A

- 静态测试电路构建

图 5-1 电压变换电路静态测试电路

#### 5.1.2 测试数据

表 5-1 : VCC C(1.35V)输出电压,输出电压纹波,效率表

| 输入电压<br>Vin(V) | 输入电流<br>Iin (mA) | 输出电压<br>Vout (V) | 输出电流<br>Iout (mA) | 纹波值<br>Vpp (mV) | 效率<br>η (%) |

|----------------|------------------|------------------|-------------------|-----------------|-------------|

| 3.31           | 11.5             | 1.40             | 20                | 32              | 74          |

|                | 50.8             | 1.40             | 100               | 60              | 84          |

|                | 99.8             | 1.40             | 200               | 60              | 85          |

|                | 350              | 1.40             | 600               | 70              | 73          |

|                | 420              | 0.785            | 1000              | 110             | 57          |

| 3.61           | 10.7             | 1.39             | 20                | 36              | 72          |

|                | 47.5             | 1.40             | 100               | 60              | 82          |

|                | 91.3             | 1.40             | 200               | 60              | 85          |

|                | 290              | 1.40             | 600               | 70              | 80          |

|                | 390              | 0.8              | 1000              | 110             | 57          |

|      |      |      |      |     |    |

|------|------|------|------|-----|----|

| 5.00 | 10.7 | 1.40 | 20   | 48  | 69 |

|      | 47.5 | 1.40 | 100  | 72  | 76 |

|      | 91.3 | 1.41 | 200  | 72  | 85 |

|      | 290  | 1.43 | 600  | 80  | 82 |

|      | 390  | 1.42 | 1000 | 100 | 75 |

表 5-2: VCC3(3.3V)输出电压,输出电压纹波,效率表

| 输入电压<br>Vin(V) | 输入电流<br>Iin (mA) | 输出电压<br>Vout (V) | 输出电流<br>Iout (mA) | 纹波值<br>Vpp (mV) | 效率<br>η (%) |

|----------------|------------------|------------------|-------------------|-----------------|-------------|

| 3.31           | 40.6             | 3.12             | 35                | 32              | 82          |

|                | 138.4            | 2.95             | 100               | 60              | 65          |

|                | 300              | 2.93             | 200               | 60              | 59          |

|                | 820              | 2.44             | 600               | 75              | 54          |

|                | 450              | 0.69             | 1000              | 110             | 47          |

| 3.61           | 34.1             | 3.30             | 35                | 20              | 94          |

|                | 98.8             | 3.30             | 100               | 32              | 93          |

|                | 210              | 3.30             | 200               | 38              | 87          |

|                | 600              | 2.75             | 600               | 80              | 76          |

|                | 300              | 0.7              | 1000              | 200             | 65          |

| 5.00           | 27               | 3.32             | 35                | 48              | 86          |

|                | 74.2             | 3.32             | 100               | 65              | 89          |

|                | 157              | 3.34             | 200               | 65              | 85          |

|                | 470              | 3.38             | 600               | 85              | 86          |

|                | 270              | 0.83             | 1000              | 220             | 61          |

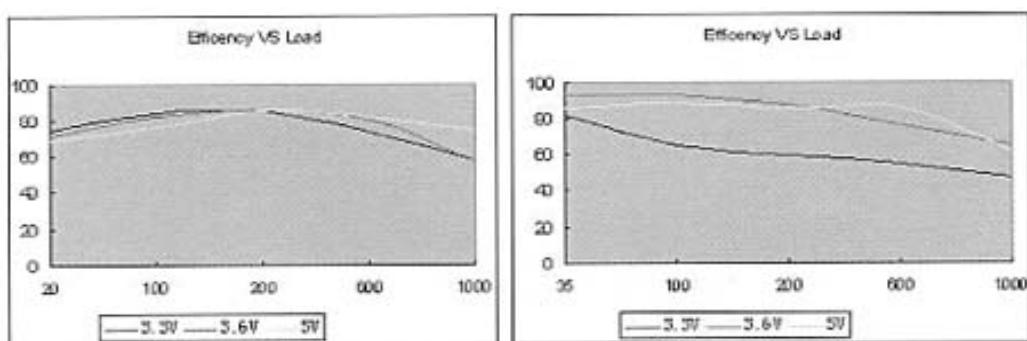

$V_o=1.35V$  $V_o=3.3V$

图 5-2 电压变换电路效率测试曲线

### 5.1.3 结果分析

测试数据显示，在本课题的锂电输入，正常工作时负载范围 100-500mA 以内的使用环境下，1.35V 的核电压和 3.3V 的 IO 电压两路均能取得较好的设计指标：静态纹波电压峰峰值小于 5%电源电压以及 90%左右的高效率。

## 5.2 PDS 阻抗测试

电源分配系统（PDS）设计中所用的目标阻抗法的基本思想就是在 PCB 板上关心的负载点位置看去，电源地间在电路的工作带宽内维持较低的阻抗幅值，这样在负载突变 $\Delta I$ 发生的情况下，才能保证电源噪声 $\Delta V$ 在一定的范围内。

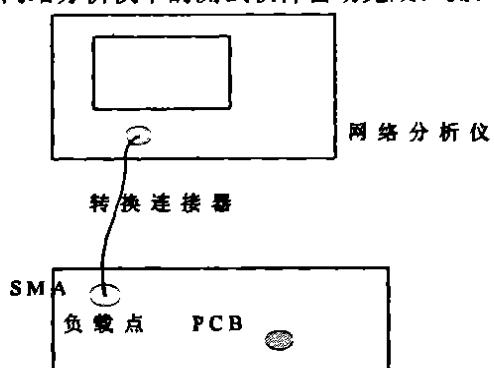

### 5.2.1 测试方法

利用网络分析仪，在待测试板上安装 SMA 连接器作为测试连接点，用转换连接器将网络分析仪端口 1 与待测板实现连接，通过测量单端口反射系数 S11 再在 50ohm 的系统中转换得到单端口的阻抗幅值，这一转换过程由网络分析仪中的测试软件自动完成。测试示意图 5-3

图 5-3 PDS 阻抗测试方法示意图

测试电路板的板基材，铜厚等加工参数定义参照实际的 PDS 所在的板环境，负载点位置参照实际的电路的 PCB 布局，本测试中代表 3.3V 的 SDRAM 负载位置。因为所用的网络分析仪 AgilentE7050B 扫描频率为 300KHz 至 3GHz，无法测到直流的情况，所以直流及低频情况下用一个 4nH 串联的小电感代替电压变换电路的效应。根据实际的电路带宽，最后设定了测试的扫描带宽为 300KHz 至 600MHz。测试板的 PCB 设计如图 5-4：

图 5-4 测试板 PCB 设计

## 5.2.2 测试误差处理

在用网络分析仪的测量过程中，由于信号泄露，负载失配，信号耦合等情况造成测试的结果中存在着系统误差的影响，例如本文中所用的测试转接头和 SMA 连接器，都会对系统误差产生影响。通过校准可以消除系统误差的影响。校准过程就是通过测量特性已知的校准件，得到系统的误差模型，对本例简单的单端口反射测量而言，可使用短路校准件（Short）或开路校准件(Open)，得到系统误差模型后，在对待测器件进行测量时，仪器会将系统误差从测量结果之中去除，得到的是待测器件的特性。保证了测试具有较高的精度。

## 5.2.3 测试结果与分析

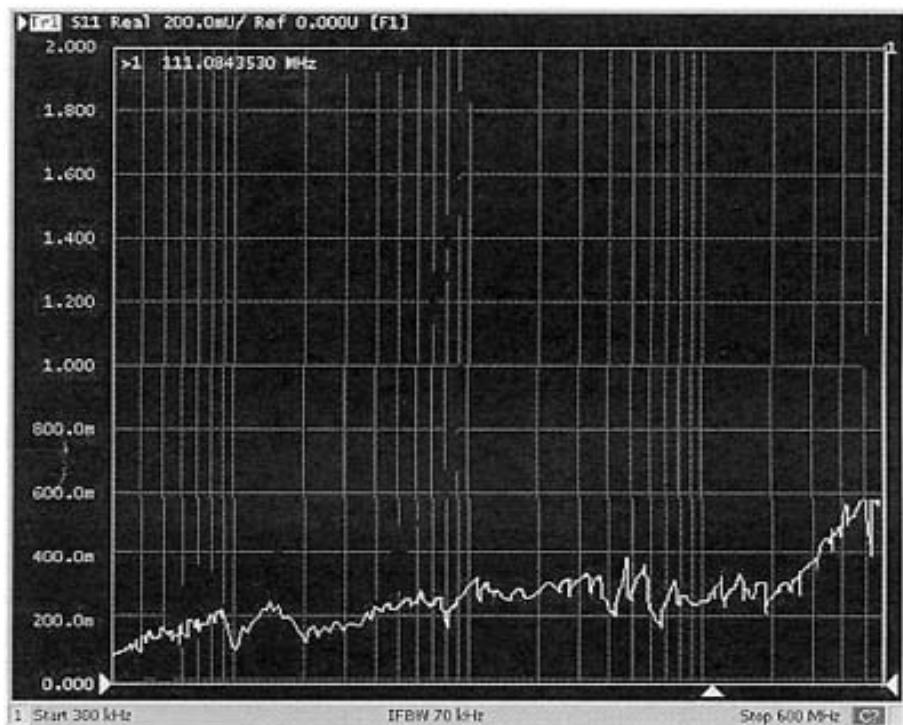

因为 VCC\_C 的电源层面积较小，已经与 SMA 连接器的 PCB 库面积相当，无法在上安装 SMA 接头，故只对 VCC3 的 PDS 系统进行了测试，测试负载点选择的是 SDRAM 的位置。测试结果的阻抗幅值/频率图如图 5-5：

图 5-5 电源分配系统阻抗/频率测试结果

从阻抗曲线显示可以看出，通过选用多种大小，规格和封装的旁路电容，以及合理的电容布局，有效的控制了 VCC3 的电源地间的交流阻抗，以及电容间的反谐振的阻抗幅值，在包含电路工作带宽的较宽的频带内将阻抗基本维持在目标阻抗 330mohm 以下。虽然测试板的物理环境与实际电路的板环境不可能完全一致，包括布局的器件以及跨层信号线在电源地层上的过孔等等方面，导致阻抗不可能完全精确，但通过阻抗变化趋势的控制，即可对旁路，去耦电容的选择和布局以及负载的布局设计提供依据，达到更优化的设计电源分配系统的目的。

## 5.3 电压轨动态实测

在手持设备的工作过程中，为了延长电池的使用时间，处理器单元通常被设计为可以工作于待机，休眠等多个低功耗的模式。这样，在工作模式切换时，整机的功耗及电流就会发生较大的变化，同时，在配有外部存储卡，如 SD, CF 卡时，卡的热插拔不仅引发处理器模式的切换还伴有卡负载的接入以及任务的启动等等，都会产生负载电流的变化，即 $\Delta I$ 的发生，进而在电压轨上产生电源噪声。

### 5.3.1 测试情景

在本课题所基于的设备环境下，设备运行时功耗测试如下表 5-3

表 5-3 实验设备功耗测试表

| 工作状态   | 测试环境                                     | 测试结果       |

|--------|------------------------------------------|------------|

| 静态运行   | 电池端 4.0V, 默认音量及背光, 桌面或主界面静置 5s 稳定电流。     | 198mA      |

| 音频运行   | 电池端 4.0V, 音量最大, 背光最亮, 标准 1KHz 音频 MP3 文件。 | 460~510 mA |

| GPS 运行 | 电池端 4.0V, BeelineGPS, 默认音量及背光。           | 256~260mA  |

| 睡眠     | 电池端 4.0V。                                | 2~3 mA     |

动态测试设定的情景为：电池电压 4.0V，播放标准 1KHz 音频 MP3 文件，音量最大，并通过睡眠按键和插拔 SD 卡，进行睡眠唤醒间切换，测得在 VCC3 和 VCC\_C 输出电压回路上，最大 $\Delta I$  分别为 250mA 和 200mA 左右。

### 5.3.2 测试结果与分析

通过采用示波器进行时域观测，测试通道设为交流耦合档，以捕捉较大电源噪声的出现。测试点选择为系统复位电路的电源端，因为过大的电压轨塌陷的电源噪声可能导致系统复位，对设备的正常工作产生影响，所以选择系统的复位电路端作为观测点。

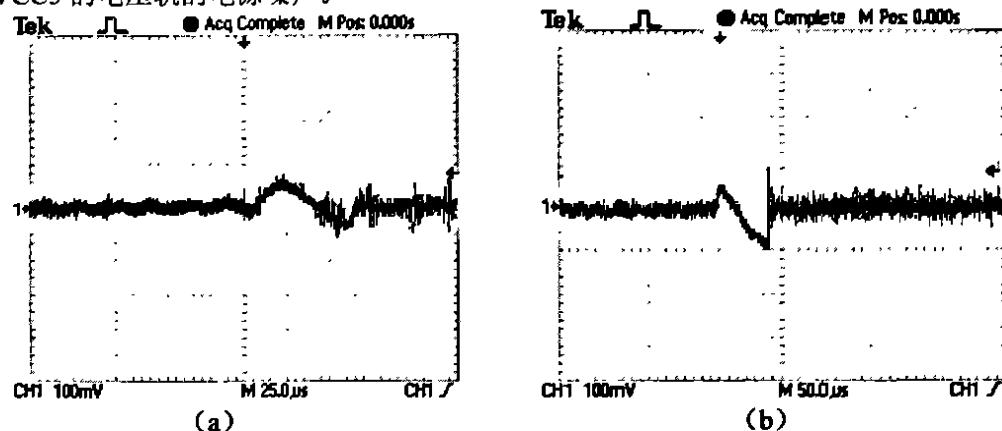

通过多次观测，记录其中的最大电源噪声如图 5-6 所示，(a) 为 VCC\_C 的电压轨的电源噪声，(b) 为 VCC3 的电压轨的电源噪声。

图 5-6 电压轨动态时域测试结果

结果显示 1.35V 的 VCC\_C 的噪声电压最大峰值约为 60mV, 3.3V 的 VCC3 的噪声最大峰值电压约为 100mV。噪声电压峰值小于电源系统所要求的 5% 的噪声容限。

## 5.4 测试结论

电压变换电路性能测试验证了稳压电路的设计和元器件的选择在所需的负载电流下能满足了电路和系统工作所要求的电压静态电压纹波要求和功率变换的高效率。

电源分配系统的阻抗测试和通过对电压轨的动态时域观测显示通过基于目标阻抗法的仿真与设计达到了在设备运行时对电源噪声的控制要求。

## 第六章 总结与展望

### 6.1 总结

本文利用目标阻抗法，以一款手持式 GPS 导航仪为硬件平台，对采用开关电源为主电源的电源分配系统进行了分析，仿真与优化设计。首先介绍了用于手持设备电源管理的不同技术的基本原理、特点和应用环境，其中重点对目前常用的开关电感式电压变化器作了分析。接着对电源完整性的概念和相关理论给出解释和整理，并阐述了目标阻抗法的含义，为后文的分析与设计奠定理论基础。

在现代高速电路系统设计中，信号完整性与 EMI 已引起足够的关注，而电源完整性与二者都有密切联系，本文也从高速电路板设计常关注的一些技术环节，如阻抗控制，高频电流回路面积，串扰等方面分析了三者之间的共通之处，更有助于理解电源完整性在改善电路板整体性能表现中的重要意义。

在实现用目标阻抗法进行板级电源分配系统设计的这一主要章节，在从电压变换电路设计，控制器与无源元件选型，PCB 电路布局，电源地层设计的过程中，对可能影响电源噪声性能的因素进行了详细分析，并给出相关措施或在电路设计与布局中应注意的环节。再通过仿真来帮助进行旁路电容的选择和布局，首先，根据电路系统的负载环境和噪声要求定义电源分配系统的目标阻抗，并根据电路板的物理参数设置好仿真环境，并进行预布局，然后通过电路和器件分析，并结合仿真的软件环境建立电源系统各组件的电路模型，通过场路结合的办法，先用场求解器软件提取电路板环境中器件的寄生参数并反馈回电路模型，加以修正。后通过电路仿真软件得出频域和 PCB 板空间内的电源系统阻抗数据，最后，直到确认在系统带宽内电源系统阻抗小于要求的目标阻抗，完成整个电源系统的设计。

在最后的测试与分析环节，通过时域内静态和动态的测试，得出电源系统电路的性能数据，验证了设计方法的有效性，所设计的电源系统各项指标满足设备运行的要求。本课题虽然是基于手持设备和开关电源的前提，但所论述的观点和实现的优化设计方法的运用对一般的中小功率设备的电源系统设计也具有借鉴意义。

### 6.2 展望

本文提出了手持设备电路板级设备供电的电源完整性优化设计方法，但是，因为电源在一个电路系统中的全局性地位，涉及的因素相当广泛，并且目前的仿真软件功能和手段还相对有限，因此，结合本文的所做工作和欠缺部分以及将来的技术水平进步，在以下几个方面可以继续一些工作，以求对本文所提的优化设计方法作进一步改进，从而更精确的分析电源系统的性能并将之与电路的其他性能分析相结合，对电路与系统做更全面的考察。

- 在实际分析中，系统设计者只能发现芯片封装外引脚处测得的电源与地是相当稳定的。但是，最终决定器件正常工作的电源应该是定义在芯片端口的，封装端口的测量结果并不能反映出此时的电源完整性状况。因此，将来可以考虑加上芯片厂商提供的封装模型用来对芯片端口处的电源波动及地弹噪声进行仿真。

- 电路中的一些无源器件的相关因素会对电路板寄生参数会产生影响，因而对电源噪声也会产生影响，这些因素主要包括，旁路电容的介质材料，电源地层的铜厚，电路板的基材材料和电路板的不同堆叠层设计，对这些可以做进一步细致的仿真，分析，来提高分析方法的精度。

- 本文所用的负载模型为噪声电流源，是比较保守的模型。而实际的负载电流在不同频率的能量大小是不一样的，所以，结合仿真软件功能的完善可以对负载做更精确的模型。

- 目前很多高速电路中，电源完整性直接影响到信号完整性仿真的精度甚至可用性，所以在常用的用于 SI 分析的 IBIS (I/O Buffer Information Specification) 模型中，可以考虑加入电源噪声的模型，实现更接近实际情况的信号完整性方面的反射，串扰等的仿真与分析。

## 致 谢

在论文结束之际，我首先衷心感谢我的导师时龙兴教授。时老师渊博的知识，严谨务实的治学态度和宽厚热忱的性格，使我获益匪浅。在本人的整个研究生求学期间，时老师不仅在学习上给我以教诲，而且在生活和工作等其它方面也给予了我极大的关心和照顾，谨在此向时老师致以衷心的感谢。

我还要感谢胡晨教授、陆生礼教授。在课题研究的每个阶段和论文的撰写过程中，他们自始至终都给予我悉心的指导和帮助。没有他们的帮助我是不可能完成本课题的研究工作的。

特别需要指出的是，在整个研究过程中还有田晓明，李晶，胡二勤，陶峰，于天国，陈学元等同学的指导与参与。我要对他们在本课题研究工作中所付的心血和精力表示感谢。

另外，我还要感谢吴建辉老师、张嗣忠老师、感谢钱德俊、曹宗凯、许扬、沈祺、马涛、尹爱昌等ASIC工程中心同学，为他们在我读研究生期间对我在学业、工作和生活上的关心和帮助。

谨以此文献给我的父母和所有关心我的老师、同学和朋友们！

刘坤

2007年2月

## 参考文献

- [1] N. Wester, K. Eshraghian, "Principles of CMOS VLSI Design, 2nd Edition,"[M] Addison-Wesley Publishing Company, 1993

- [2] P. J. M. Havinga, G. J. M. Smith, "Design Techniques for Low Power Systems,"[J] Journal of Systems Architecture, volume 46:1, 2000

- [3] HEEB H. RUEHLIA. E., "Three-dimensional interconnect analysis using partial element equivalent circuits," [J] IEEE transactions on circuits and systems.vol.39,1992. pp. 974-982

- [4] A.Taflove,"Computational Electromagnetic the Finite-Difference Time-Domain Method"[M] ,Artech House,1995

- [5] 曲学基,王增福,曲敬铠,稳定电源基本原理与工艺设计[M],北京:电子工业出版社,2004年1月,pp.1-10

- [6] BCD 公司,CMOS LDO 在便携式产品中的应用及设计思想[EB/OL], 电子设计技术, 2006 年 6 月

[http://www.ed-china.com/ART\\_8800016254\\_400003\\_500011\\_TS\\_08E11A2A.HTM](http://www.ed-china.com/ART_8800016254_400003_500011_TS_08E11A2A.HTM)

- [7] 张占松,蔡宣三,开关电源的原理与设计[M], 北京:电子工业出版社,2005 年 3 月. pp.16-22

- [8] 西南交大, 开关电源控制方式研究[D], 2001 年 P. 8-9

- [9] 美国国家半导体,2006 年高性能电源管理技术研讨会[M],2006 , pp.1-38

- [10] R.D.Middlebrook,Topics in Multiple-Loop Regulators and Current-Mode Programming 1985 IEEE PESC.Record, pp.716-732

- [11] 韦枫,吴金, "基于斜波补偿的电流模式 PWM DC-DC:系统稳定性分析" [J],电子器件, Vol.26 ,No. 4Dec. 2003

- [12] 姚丰,高效电感式降压型 DC-DC 电源管理芯片的设计[D]:[硕士学位论文],浙江大学 2006

- [13] Wang T , Zhou X , Lee F. A low voltage high efficiency and high power density DC/ DC converter [J] .IEEE Power Elec Specialist s Conf . St Louis , Mis2 souri , USA. 1997. pp.240-245.

- [14] Liner Technology, The datasheet of LTC3411[S].2006

<http://www.bjx.com.cn/files/wx/dyjsyy/2003-3/12.htm>

- [15] 刘述平,梁冠安,彭军,开关电容 DCDC 变换的理论研究[EB/OL],2006

<http://www.igw.com.cn/servicing/electron/13567.html>

- [16] Chris Winkler,负载管理器件简化便携式应用设计[EB/OL],电子设计应用.2006 年 4 月

<http://www.igw.com.cn/servicing/electron/13567.html>

- [17] Cadence SPECCTRAQuest® Power Integrity training manual,2003.8

- [18] 徐红波, 高速通信系统中 PCB 板级电源分配系统对信号完整性影响的研究——电源完整性[D]: [硕士学位论文] 华东师范大学 2005

- [19] 曾峰 巩海洪 曾波.印制电路板设计与制造[M], 北京:电子工业出版社, 2005 年 8 月 pp.118

- [20] 李小平, 高速 PCB 的信号完整性、电源完整性和电磁兼容性研究[D] :[硕士学位论文]四川大学, 2005 年 6 月

- [21] 钱恩学.高速 PCB 设计电容的应用连载系列[EB/OL].上海泰奇科技网 2004 年 6 月

<http://www.i-tech.com.cn>

-

- [22] Douglas Brooks, Signal Integrity Issues and Printed Circuit Board Design[M],北京: 机械工业出版社,2005.8 pp.147-161

- [23] S.Van den Berghe,F.Olyslager,D.De Zutter,J.DE Moerloose and W.Temmerman,Study of the Ground Bounce Caused by Power Plane Resonances,IEEE transactions on C.vol.40.No.2.MAY 1998

- [24] 张存续,高速数位电路之电源完整性[J],电子月刊第九卷第二期,2003年2月

- [25] Eric Bogatin,Signal Integrity:Simplified[M],北京:电子工业出版社,2006. 1 pp.26-44

- [26] Rick Hartley,板级设计中控制共模辐射 EMI 的主要步骤[EB/OL],2006.4

<http://www.edadoc.com/>

- [27] 唐海燕, 高密度 PCB 设计面临新挑战[EB/OL],2004 年 8 月

<http://www.ednechina.com>

- [28] EUP3406 datasheet[S] ver1.0 2006.4

- [29] 中国电源学会主编. 现代电源技术(1) [M]. 科学出版社, 1997 出版, pp. 101-116.

- [30] 田晓明, 王非, 刘昊, 移动设备中 Buck 变换器的原理与选型设计 [J], 电子产品世界, 2004.1

- [31] Clinton Jensen, Layout Guidelines for Switching Power Supplies. National Semiconductor, 1999.10

- [32] Huabo Chen,Jiayuan Fang,Effects of 20-H rule and shielding vias on electromagnetic radiation from printed circuit boards.Electrical Performance of Electronic Packaging,2000 IEEE Conference on.23-25 Oct.2000.pp.193 -196.

- [33] Larry D. Smith, Raymond E. Anderson, Douglas W. Forehand, Thomas J. Pelc, and Tanmoy Roy, Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology.IEEE transactions on advanced packaging,vol.22.NO.3 ,8,1999

- [34] 邱关源, 电路 (第四版) [M], 北京:高等教育出版社, 2001 年 5 月

- [35] Joong-Ho Kim and Madhavan Swaminathan, Modeling of Irregular Shaped Power Distribution Planes Using Transmission Matrix Method, IEEE Transactions on Advanced Packaging, , vol. 24, No 3, AUGUST 2001

- [36] Larry Smith, Tanmoy Roy, Raymond Anderson, Power Plane Spice Models for Frequency and Time Domains, Sun Microsystems, Inc.

- [37] Stephen H. Hall, Garrett W. Hall, James A. McCall, High-Speed Digital System Design—A Handbook of Interconnect Theory and Design Practices[M], John Wiley & Sons, Inc.2000.pp.293-294