西安电子科技大学

---

硕士学位论文

---

升压型AC-DC有源功率因数校正控制器的设计

---

姓名：刘超

---

申请学位级别：硕士

---

专业：电路与系统

---

指导教师：王松林

---

20081201

## 摘要

近年来，开关电源因其高效率和低成本而在各个领域得到了广泛的应用。然而，由于传统的开关电源功率因数较低，造成输入电流畸变严重，谐波分量很高，对电网造成了严重的谐波污染，降低了电能的利用率。采用有源功率因数校正(APFC)技术可以使设备的功率因数接近于1，既治理了电网的谐波污染，又提高了开关电源的整体效率，因此，有源功率因数校正技术对电子行业的发展起着至关重要的作用。

本文首先介绍了功率因数的概念，并阐述了有源功率因数校正的工作原理，然后在此基础上设计了一款升压型有源功率因数校正控制器芯片。该控制器同时引入电压和电流反馈，构成一个双环控制系统，既可以使输入电流跟随输入电压变化，从而实现单位功率因数，提高了电能的利用率，又可以通过反馈控制使输出电压稳定，从而使开关电源变换器的输入实现预稳。

本文设计的有源功率因数校正控制芯片采用 $0.6\mu\text{m}$  30V BCD 工艺，工作于临界导通模式，采用峰值电流模控制，具有结构简单、体积小和功率因数高的特点。通过 HSPICE 仿真平台对所设计的控制芯片进行仿真验证，仿真结果表明，该芯片具有很好的功率因数校正功能，各项指标均达到了预期制定的设计要求。

**关键词：** 有源功率因数校正 谐波污染 峰值电流模 BCD 工艺

## Abstract

In recent years, switch mode power supply has been widely applied because of its high efficiency and low cost. However, as the traditional switch mode power supply has a low power factor, a distortion is introduced in the input current with a high harmonic component, leading to a harmonic pollution to the electricity network and a decrease in the power efficiency. By adopting active power factor correction (APFC), the power factor can be improved to nearly 1, not only getting rid of the harmonic pollution but also improving the efficiency of the switch mode power supply. Therefore, APFC plays a very important role for the development of electronic industry.

Firstly, the concept of power factor is proposed in the paper, and the principle of APFC is also described in detail. Next, based on the principle above, a boost APFC controller is designed. Both the voltage and the current loops are introduced in the design, so that the input current can vary with the input voltage, which makes a high power factor and improves the power efficiency. Furthermore, the output voltage can be stabilized by the feedback loop so as to make the input of switch converter pre-stable.

The controller designed in the paper is based on  $0.6\mu\text{m}$  30V BCD process, and works on the critical-conduction mode by peak-current mode controlling, so it has the characteristics of simple structure, small size and high power factor. The simulation results by HSPICE show that the chip realizes the function of PFC perfectly, and all the simulation data meet the specification well.

**Keyword:** APFC Harmonic Pollution Peak-current Mode BCD process

## 西安电子科技大学

### 学位论文独创性（或创新性）声明

秉承学校严谨的学风和优良的科学道德，本人声明所呈交的论文是我个人在导师指导下进行的研究工作及取得的研究成果。尽我所知，除了文中特别加以标注和致谢中所罗列的内容以外，论文中不包含其他人已经发表或撰写过的研究成果；也不包含为获得西安电子科技大学或其它教育机构的学位或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在论文中做了明确的说明并表示了谢意。

申请学位论文与资料若有不实之处，本人承担一切的法律责任。

本人签名： 刘超                          日期 2009.3.1

## 西安电子科技大学

### 关于论文使用授权的说明

本人完全了解西安电子科技大学有关保留和使用学位论文的规定，即：研究生在校攻读学位期间论文工作的知识产权单位属西安电子科技大学。学校有权保留送交论文的复印件，允许查阅和借阅论文；学校可以公布论文的全部或部分内容，可以允许采用影印、缩印或其它复制手段保存论文。同时本人保证，毕业后结合学位论文研究课题再撰写的文章一律署名单位为西安电子科技大学。

本人签名： 刘超                          日期 2009.3.1

导师签名： 王桂林                          日期 2009.3.1

# 第一章 绪论

功率因数校正和高次谐波抑制是近年来国际上在电力电子系统开发研究中非常热的方向之一。它在环境保护、能源的充分利用和电力的安全使用方面做出了巨大的贡献。在提倡建立节约型社会的今天，本论文所进行的研究工作就更加具有实际应用价值。

## 1.1 AC-DC 电路的谐波对电网的危害

在电力电子学中，AC-DC 称为整流，DC-AC 称为逆变，AC-AC 称为交流变频变压，DC-DC 称为直流-直流变换。值得关注的是在大部分用电设备中，电源直接来自交流电网，但几乎所有的电路都需要使用直流进行供电，因此上述 AC-DC 变换器成为众多电子产品的必需部分。为达到交流转直流的目的，人们设计了各种转换方法，其中最为简单且常用的是桥式整流电路，它被广泛应用于各种开关电源中。

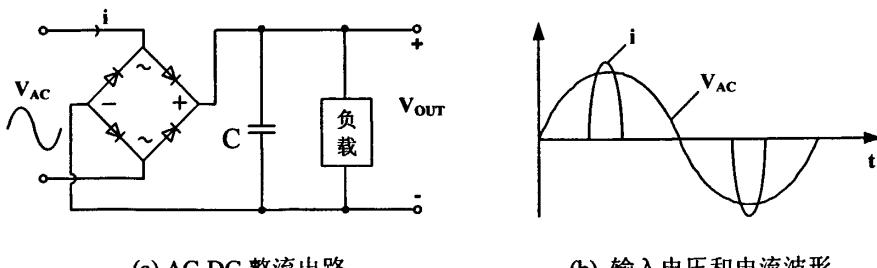

220V 交流电网经输入整流滤波后供给直流电，这是电力电子技术及电子仪器中应用极为广泛的一种基本整流技术。传统 AC-DC 变换器是由二极管桥式整流<sup>[1]</sup>加电解电容滤波电路组成<sup>[2]</sup>，如图 1.1(a)所示。交流市电经二极管整流和大电容滤波后，得到较为平滑的直流电压，再由直流变换器进行 DC-DC 变换，就得到要求的输出电压。整流器-电容滤波电路是一种非线性元件和储能元件的组合。大容量电容用于减小输出电压纹波，并可在系统掉电时为负载提供必要的储能。但由于输入整流电压仅在高于电容电压的瞬间对电容充电，所以输入电流呈尖峰脉冲状，如图 1.1(b)所示。

(a) AC-DC 整流电路

(b) 输入电压和电流波形

图 1.1 单相桥式整流输入电压和电流波形

对这种脉冲状的电流进行傅立叶分解，可得到如下表达式：

$$i = I_1 \sin \omega t + I_3 \sin 3\omega t + I_5 \sin 5\omega t + \dots \quad (1-1)$$

其中,  $I_1$  为基波分量,  $I_3$ 、 $I_5$  分别为三次和五次谐波分量。由于输入电流是一个奇谐函数, 所以表达式中只含有奇数次项的谐波。

由以上分析可知, 输入电流中除含有基波外, 还含有大量的谐波分量。由于只有基波电流能够产生有功功率, 高次谐波使视在功率增加, 所以 AC-DC 变换器输入端功率因数下降。此外, 大量谐波分量涌入电网, 会使电力系统的电流波形畸变, 造成电网的谐波“污染”。即除了正常的工频基波外, 还包含有各种高次谐波<sup>[3]</sup>, 这些产生高次谐波电流的电力负荷称为高次谐波源。

电流畸变对电力系统和电力设备造成的危害主要有以下几点:

- (1) 使电力电容器以及与之相串联的电抗器过电流、过热、发出异常的声响, 甚至于损坏。

- (2) 使变压器和电机产生附加损耗、局部过热、产生附加力矩, 进而造成振动、发出异常声响。

- (3) 高次谐波幅值过大引起继电器、控制电器和计算机误动作。

- (4) 使射线仪器、示波器和电视机的图像变坏。

- (5) 输电线中的高次谐波电流则会干扰与其邻近的通信, 使电磁兼容性问题变得更加突出。

- (6) 高次谐波还会引起计量仪表计量误差, 造成电费收费不合理。因为高次谐波源的用户从电网中吸收的功率是基波, 而向电网送出的却是含有高次谐波的畸变功率, 迫使正常负荷的用户从电网中吸收这些畸变功率, 增加用电损耗, 危害用电设备, 还要多付电费, 而高次谐波源用户反而少付电费。

- (7) 在三相四线制电路中, 三次谐波在中线中的电流同相位, 导致合成中线电流很大, 有可能超过相线电流, 而中线又无保护装置, 使中线因过电流而导致过热, 损坏电气设备, 甚至引起火灾。

这些都严重影响了电能质量、输电效率、设备的安全运行与正常使用。随着电力电子装置的应用日益广泛, 谐波污染问题引起了越来越广泛的关注。

## 1.2 谐波治理的意义与国内外发展现状

近年来开关电源因效率高、成本低, 在各个领域获得了广泛的应用。但是大量电力电子装置的应用给电力系统注入了越来越多的谐波, 致使电网中的谐波污染日益严重, 使得电能的生产、传输和利用的效率降低, 产生严重的电磁干扰, 影响到电网供电质量和用户使用的安全性。电力电子装置所产生的谐波污染已成为阻碍电力电子技术发展的重大障碍, 是电工科学技术界必须解决的问题。

功率因数校正技术<sup>[4]</sup>是提高电子产品的功率因数、降低谐波干扰的有效方法

之一。它可以在不增加资源损耗的前提下，抑制谐波对电网的污染，使交流电的能量得到更有效的利用，从而使得供电质量大大提高，减少谐波“污染”。最早使用的校正方法是无源功率因数校正技术。这种方法仅仅采用电容电感进行滤波，电路简单、成本低、EMI 小，但是体积大、重量重、功率因数不高。

80 年代是现代有源功率因数校正技术发展的初级阶段。它是在负载的整流电路与输出电容之间增加一级功率变换电路，将输入电流校正成与输入电压同相位的正弦波，使功率因数提高到近似为 1，而且具有稳定的直流输出电压。1986 年美国公布《功率因数等于 1 的电源》的专利，这是最早的较完整的升压式 PFC 电路。此期间的研究工作主要是基于 Boost 变换器，围绕连续导电模式或不连续导电模式的理论研究。但是由于输入电流纹波大，一般不能应用于较大的功率器件中。

90 年代以来，有源功率因数校正技术取得了长足的进步。自 1992 年起，PESC (IEEE Power Electronics Specialists Conference) 专门设立了单相功率因数校正技术专题，这被看作是单相有源功率因数校正技术发展的里程碑。从此不断有新颖的功率因数校正原理、拓扑结构及控制方法出现，有源 PFC 控制器从分体电路发展到集成电路。在这个时期，一些国家和世界性的学术组织也分别颁布和实施了一些限制输入电流谐波的标准，进一步促进了功率因数校正技术的发展。

近年来，功率因数校正技术的研究热点集中在：新拓扑结构的提出，把 DC-DC 变换器中的新技术（软开关技术和开关电容功率网络等）应用于 PFC 电路中，新控制方法的提出以及单级 PFC 变换器的研究。各种不同功率因数校正控制芯片在市场上纷纷出现：Onsemi、ST、Microlinear 等公司都有多款功率因数校正芯片投放到市场。随着半导体和电源技术的发展，结构简单、成本低、功率因数高、输出纹波小且具有高次谐波抑制的有源功率因数校正电路将成为功率因数校正技术的研究发展方向。

进入二十一世纪，PFC 技术的研究方兴未艾，特别在我国，对于这方面的要求和标准规范还不健全，选择此课题研究的目的和意义具有如下几点：

- (1) 开关电源功率因数校正技术作为电源的一门新兴技术，它的作用和重要性已经得到广泛的认可，如何提高功率因数已成为当今电力电子界的研究热点。

- (2) 提高功率因数可以减少输入电流的谐波成分，从而降低对其它设备的干扰。

- (3) 提高功率因数能节省能源，提高电能质量，保证电力系统安全稳定地运行。

- (4) 针对谐波污染，国际已经制定了各种相关的标准和规定，以限制谐波的危害，净化电磁环境，如 MIL-STD-1399、BELLCORE001089、IEC555-2、

IEEE519 等，其中 IEC555-2 标准自 1994 年起在欧盟国家全面实施，所有不符合此标准的用电装置不准在欧洲销售。

- (5) 在用电设备中采用 PFC 控制芯片可以提高功率因数、提高效率、降低电源整机成本、提高开关电源的可靠性，对于提高产品的竞争力具有十分重要的意义。

### 1.3 论文的内容安排

论文结合当今功率因数校正技术的现状和发展趋势，详细介绍了有源功率因数校正（APFC）的基本原理和控制方法，并基于  $0.6\mu\text{m}$  30V BCD 工艺和 HSPICE 仿真软件，设计了一款升压型有源功率因数校正控制器 XD5622。

论文共分为五章。第一章是绪论，主要介绍论文的背景、国内外的发展以及论文的章节安排；第二章主要介绍了功率因数校正的基本原理和控制方法等相关知识，着重介绍了升压型 APFC 的特性；第三章主要介绍了 XD5622 的系统设计，包括系统指标、架构图以及工艺的选择；第四章详细介绍芯片 XD5622 中关键子模块的设计与仿真验证，并给出了仿真波形和仿真数据；第五章是电路典型应用及整体功能仿真验证。

## 第二章 功率因数校正的基本原理

在开关电源中引入功率因数校正技术，一方面可以消除由于整流滤波电路产生的谐波电流，另一方面可以提高功率因数，这是开关电源的一大发展趋势。功率因数校正可分为无源功率因数校正和有源功率因数校正，在新型开关电源中一般采用有源功率因数校正技术，它是抑制谐波电流、提高功率因数的行之有效的方法。本章介绍功率因数校正的原理和实现方法。

### 2.1 功率因数的基本概念

#### 2.1.1 功率因数的定义

由于受到电抗的作用，发电机发出的交流电流往往滞后于交流电压一定的相位，就是说发电机发出的电能只有一部分被利用，而相当一部分的电能以磁场能的形式在发电机与用电设备之间往返变化而不能被释放，这就是我们所说的“功率因数”。

功率因数（PF：Power Factor）指的是交流输入信号的功率（P）与视在功率（S）的比值<sup>[5]</sup>，即功率因数：

$$PF = \frac{P}{S} \quad (2-1)$$

在线性电路中，阻抗  $Z = R + jX$ 。其中R为电阻，X为电抗。无论是感抗或者容抗，均会使正弦电压和电流产生相位差，但电压和电流均为正弦波。所以在线性电路中，功率因数描述了负载的电抗特性，其定义为

$$PF = \frac{P}{S} = \cos \varphi \quad (2-2)$$

其中， $\varphi$  是正弦电流波形相对于电压波形的相位差。只有当负载呈电阻性时，电压与电流波形相位相同， $PF=1$ 。

在非线性电路中，当电源电压是正弦波时，输入电流波形发生正弦畸变，导致功率因数很低，相移功率因数不能正确反映这种关系，因为非线性负载的功率因数与电流波形的失真情况紧密相关。因此，功率因数定义为

$$PF = \frac{P}{S} = \frac{V_1 I_1 \cos \varphi}{V_1 I_{rms}} = \frac{I_1}{I_{rms}} \cdot \cos \varphi = \gamma \cos \varphi \quad (2-3)$$

式（2-3）中， $V_1$  表示输入电压基波有效值； $I_{rms}$  表示交流输入电流的有效值， $I_{rms} = \sqrt{I_1^2 + I_2^2 + \dots + I_n^2}$ ， $I_1, I_2, \dots, I_n$  分别为输入电流的基波分量、二次谐波、...

$n$  次谐波的有效值； $\cos\varphi$  表示交流输入市电的基波电压与基波电流的相移因数； $\gamma = I_1/I_{rms}$  为交流输入市电电流的波形畸变因数。

所以 PF 可以定义为交流输入市电电流的波形畸变因数  $\gamma$  与相移因数  $\cos\varphi$  的乘积。即 PF 主要由两个因素决定：一是交流输入市电的基波电流与基波电压的相位差  $\varphi$ ，另一个是交流输入市电电流的波形畸变因数  $\gamma$ 。而传统的功率因数概念是在电阻性线性负载、并假定输入电流无谐波电流（即  $I_1=I_{rms}$ ）或交流输入市电电流的波形畸变因数为 1 ( $\gamma=1$ ) 的条件下得到的，这样 PF 的定义就变成了  $PF = \cos\varphi$ 。

交流输入市电的  $\cos\varphi$  低，表示设备的无功功率大，供电设备的利用率低，供电设备的导线、变压器绕组损耗大。电流波形畸变因数  $\gamma$  值低，则表示输入电流的谐波分量大而基波电流的幅度小，将造成输入电流的波形畸变，对电网造成污染，严重时还会造成用电设备的损坏。相移因数  $\cos\varphi$  减少了供电线路中传送的有效能量，使无功功率在供电线路上传送，降低了供电线路的使用效率。

### 2.1.2 功率因数 (PF) 与总谐波失真 (THD) 的关系

由以上分析可以看出降低高次谐波分量就可以达到提高功率因数的目的，它们之间的关系简单推导如下。

总谐波失真<sup>[4]</sup> (THD: Total Harmonic Distortion) 是指用信号源输入时，输出信号比输入信号多出的额外谐波成分，它的定义式为：

$$THD = \sqrt{\sum_{n=2}^{\infty} \left( \frac{I_n}{I_1} \right)^2} = \sqrt{\frac{I_2^2 + I_3^2 + \dots + I_n^2}{I_1^2}} = \frac{\sqrt{\sum_{n=2}^{\infty} I_n^2}}{I_1} \quad (2-4)$$

功率因数的表达式为：

$$PF = \frac{V_1 I_1}{V_1 I_{rms}} \cos\varphi = \frac{I_1}{I_{rms}} \cdot \cos\varphi = \frac{I_1 \cos\varphi}{\sqrt{\sum_{n=1}^{\infty} I_n^2}} \quad (2-5)$$

由式 (2-4) 和 (2-5) 可知：

$$\gamma = \frac{I_1}{I_{rms}} = \frac{I_1}{\sqrt{\sum_{n=1}^{\infty} I_n^2}} = \frac{1}{\sqrt{1 + (THD)^2}} \quad (2-6)$$

因此功率因数 (PF) 与总谐波失真 (THD) 的关系为：

$$PF = \frac{I_1}{I_{rms}} \cos\varphi = \frac{1}{\sqrt{1 + (THD)^2}} \cos\varphi = \gamma \cos\varphi \quad (2-7)$$

由以上讨论可以看出，功率因数和交流输入市电电流的谐波成分有关，那么

利用 THD 和电流波形畸变因数  $\gamma$  之间的关系式就可以得到：

$$THD = \sqrt{\frac{1}{\gamma^2} - 1} \quad (2-8)$$

当交流输入市电的电压、电流同频同相时，有  $\cos \varphi = 1$ ，则：

$$PF = \gamma \cos \varphi = \gamma = \frac{1}{\sqrt{1 + (THD)^2}} \quad (2-9)$$

对纯正弦电压、电流而言，由于总谐波成分为零，所以波形畸变因数  $\gamma$  为 1，并且正弦电压、电流之间的相位差为零，则电源输入侧的功率因数就为 1。如果正弦电压、电流之间的相位差不为零，则电路的功率因数就为  $\cos \varphi$ 。当  $\varphi = 0$  且  $THD = 10\%$  时，利用式 (2-9) 就可以计算出对应的 PF 值为 0.995。所以控制交流输入电流的谐波电流有助于改善电路的功率因数和降低对电网的谐波污染。目前，通常采用 PFC 技术来改善开关电源电路的功率因数，经过校正后的开关电源电路的 PF 可大于 0.99、 $\gamma$  小于 3%、THD 小于 10%。

当  $\varphi = 0$  时，PF 与 THD 之间的关系如表 2.1 所示。

表 2.1  $\varphi = 0$  时，已知 PF 值计算和测量 THD 的结果

|             |        |        |       |         |         |

|-------------|--------|--------|-------|---------|---------|

| PF 值        | 0.5812 | 0.9903 | 0.995 | 0.99875 | 0.99955 |

| THD(计算值)(%) | 140    | 14     | 10    | 5       | 3       |

| THD(实测值)(%) |        | 10     | 7     | 4.27    |         |

由此可以看出，THD 指标能很好地衡量非线性电路的功率因数。例如当 THD 小于等于 5% 时，功率因数可以控制在 0.999 左右。

## 2.2 功率因数校正的实现方法

### 2.2.1 实施功率因数校正的意义

在没有功率因数校正的开关电源中，交流输入电压经整流后，直接加到滤波电容器的两端。只有当交流输入电压高于滤波电容两端的电压时，滤波电容才开始被充电，因此，输入电流波形为宽度很窄的脉冲。这种电流不仅严重滞后电源电压，而且谐波分量很大，输入总谐波失真可达 100%~130%，功率因数通常只有 0.6~0.7。

功率因数较低的开关电源存在许多问题<sup>[4]</sup>，比如：使电网波形畸变，线路损耗增大；降低供电系统的功率因数，增大系统的供电量；降低用电设备的使用寿命；干扰仪器、仪表；使计算机无法工作等。为了防治电力系统谐波的危害，许多国家制订了谐波管理标准，对电器设备和其它非线性负载向电网注入电流谐波

的含量作了严格的限制。从 1992 年起国际上开始以立法的形式限制高次谐波，我国国家技术监督局在 1993 年颁布了国家标准 GB/T 14549-93《电能质量公用电网谐波》。国际电工委员会于 1998 年对谐波标准 IEC555-2 进行了修改，另外还制定了 IEC61000-3-2 标准。有关规定主要有以下几个作用。

- (1) 防干扰，核心是限制电网的谐波电流成分，如欧洲制定的 EN60555-2 标准，一部分条文对特殊输入电流波形的用电设备的谐波电流提出了严格限制，同时还规定了不符合此标准的产品不准进入欧洲市场。

- (2) 减小输入电流的谐波成分，从而降低对其它用电设备的干扰。

- (3) 提高电网设备的利用率。

- (4) 提高电网设备的安全性。电网功率因数的提高，减小了高频谐波电流成分，从而使三相四线制供电系统的中线电位正确，减小了中线电流，提高了供电系统的可靠性。

在同样输入条件下，增大输出功率有两种办法：一是提高电源效率，二是提高功率因数。提高电源效率要受到电源电路水平的限制，难度较大，而且效果也不明显，只有提高功率因数值最有效，表 2.2 给出了有关数据的比较。

表 2.2 功率因数校正与电路有关参数的比较

| 参数              | 一般电路 | 提高效率 | 提高 PF |

|-----------------|------|------|-------|

| UL 认可的 VA 值     | 1140 | 1440 | 1440  |

| 电源效率 $\eta$ (%) | 75   | 90   | 75    |

| 总效率 $\eta$ (%)  | 75   | 90   | 73    |

| 功率因数(PF)        | 0.65 | 0.65 | 0.95  |

| 最大输出功率(W)       | 702  | 842  | 995   |

正是由于有关标准的强制规定，以及功率因数校正控制集成电路生产厂家的不懈努力，功率因数校正技术才得到了广泛的应用。

### 2.2.2 功率因数校正的实现方法

功率因数校正的基本原理，就是通过校正电路，使交流输入电流波形完全跟随交流输入电压波形，也就是使输入电流和输入电压同相位，即通过输入电流与输入电压同频同相来达到提高功率因数的目的<sup>[6]</sup>。

由功率因数的定义  $PF = \gamma \cos \varphi$  可知，要提高功率因数一般有两个途径：

(1) 使  $\varphi = 0$ ，也就是输入电压、输入电流同相位，即相移因数  $\cos \varphi = 1$ ，所以  $PF = \gamma$ 。

(2) 使  $I_{rms} = I_l$ ，输入电流正弦化，即  $I_l/I_{rms} = 1$ ，所以  $PF = \cos \varphi$ 。

综合以上方法，就可以实现  $PF$  为 1 的目标，即  $PF = \gamma \cos \varphi = 1 \times 1 = 1$ 。

提高 AC-DC 电路输入端功率因数和减少输入电流谐波，就是使输入电压和输入电流同相位，且输入电流正弦化。利用功率因数校正技术可以使交流输入电流波形完全跟踪交流输入电压波形，使输入电流波形呈纯正弦波，并且和输入电压同相位，此时整流器的负载可以等效为纯电阻。常用的功率因数校正电路有多种，按照软开关<sup>[7][8]</sup>（Soft-Switch）特性，可以分为零电流开关功率因数校正技术和零电压开关功率因数校正技术；按照供电方式可分为单相功率因数校正技术和三相功率因数校正技术；按照电路结构可分为无源功率因数校正技术（PPFC）和有源功率因数校正技术（APFC）两类。

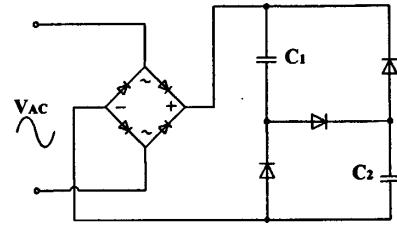

典型的无源功率因数校正（PPFC）电路如图 2.1 所示，它利用电容、二极管网络组成填谷式（Valley Fill）PFC 整流电路<sup>[9]</sup>。当输入电压高于  $C_1$  和  $C_2$  两端的电压时，两个电容处于串联充电状态；当输入电压低于电容  $C_1$ 、 $C_2$  两端的电压时，两个电容处于并联放电状态。由于电容和二极管组成的充放电网络增大了整流二极管的导通角，可以改善输入电流的波形，从而提高功率因数。在 AC-DC 整流器电路的输入端加 LC 无源滤波器，是对电网实施补偿的被动方法，虽然这种方法既可以补偿谐波，又可以补偿无功功率，且结构简单、成本低，但由于无源滤波器是通过在电力系统中为谐波提供一个并联低阻抗通路以起到滤波作用的，其滤波特性由系统和滤波器的阻抗之比决定，因此存在以下缺点：

- (1) 滤波特性受电网系统阻抗和运行状态影响较大，容易和系统发生并联谐振，导致谐波放大，使滤波器过载甚至烧坏；

- (2) 只能消除特定的几次谐波，对某些次数谐波可能起放大作用，可能导致滤波器过载；

- (3) 滤波补偿要求和调压要求有时难以协调；

- (4) 这些 LC 滤波器往往工作在工频低通或带通状态，因而滤波器的有效材料消耗多，体积大；

- (5) 难以得到高功率因数（一般只能提高到 0.9 左右）。

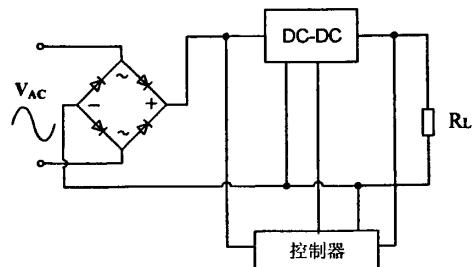

有源功率因数校正（APFC）电路，自上世纪 90 年代以来就得到了迅速推广。这是对电力电子设备进行自行改进的主动方法，是对 AC-DC<sup>[10]</sup>整流电路内部进行功率因数校正，从而使电路尽

图 2.1 典型无源功率因数校正电路

图 2.2 APFC 工作原理图

可能不产生谐波。而且输入电压和电流同相位，从电源的输入端看，整个电路是纯阻性的，实现了高功率因数低谐波的 AC-DC 电路<sup>[11]</sup>。有源功率因数校正技术工作原理如图 2.2 所示，在整流器和负载之间接入一个 DC-DC 开关变换器，应用电流反馈技术，使输入端电流波形跟踪交流输入正弦电压波形，可以使输入电流波形接近正弦，使功率因数提高到 0.99 以上。由于这个方案应用了有源器件，故称为有源功率因数校正（Active Power Factor Correction），简称 APFC。它具有以下优点：

- (1) 平滑的交流输入电流波形，较小的高频谐波电流成分；

- (2) 交流电流过零点平滑，无较大的间断；

- (3) 启动时输出直流电压的超调量小，可以控制在 5%~10% 的范围内，启动速度快；

- (4) 良好的直流输出稳定性，在各种条件下都不会产生自激；

- (5) 空载时直流输出电压的上升量不超过额定值的 3%；

- (6) 高功率因数，PF 高达 0.99 以上；

- (7) 较低的总谐波失真，THD 小于 10%；

- (8) 较宽的输入电压范围，可达 90~270V；

- (9) 磁性元件体积小。

APFC 电路的主要缺点是：电路复杂，成本高，EMI 较高。

由于有源功率因数校正（APFC）技术具有补偿特性好的优点，在实际应用中占有绝对优势，而且电路形式多样，控制集成电路品种齐全。本文主要针对有源功率因数校正技术（APFC）进行介绍。

## 2.3 APFC 的基本理论

### 2.3.1 APFC 主电路的拓扑结构

APFC 主电路拓扑结构主要有：降压式（Buck）、升/降压式（Cuk）<sup>[12]</sup>、反激式（Flyback）、升压式（Boost）等<sup>[13][14]</sup>。降压式结构因功率开关管直接和整流桥的输出相连，使得开关管的噪声直接影响电网，滤波困难，功率开关管上的电压应力大，且控制功率开关管的驱动电平是浮动的，驱动电路复杂，所以很少被采用。升/降压式结构须用两个功率开关管，且有一个功率开关管的驱动控制信号浮动，电路复杂，也较少采用。反激式结构输出与输入隔离，输出电压可以任意选择，采用简单电压型控制，由于反激式电路结构自身的限制（开关管所要求承受的电压高，电感峰值电流高等），一般适用于 150W 以下功率的应用场合。Boost 拓扑结构简单<sup>[15][16]</sup>，方便使用电流进行控制，可以在一定的电压输入范围内保持

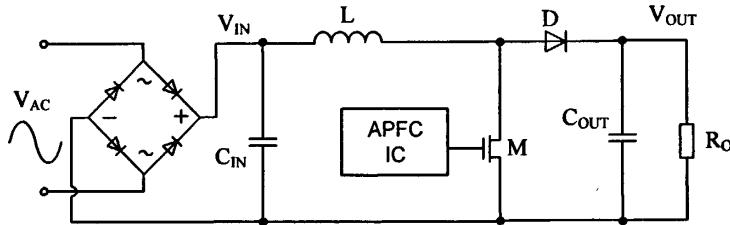

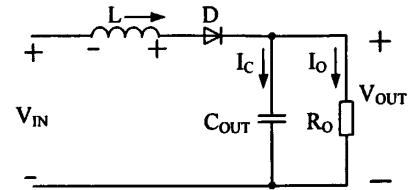

较高的功率因数，因而常作为优选的一种拓扑，其拓扑结构如图 2.3 所示。交流市电  $V_{AC}$  经过全桥整流后得到半波正弦信号  $V_{IN}$ ，之后送至升压转换器。升压转换器由升压电感 L、功率开关管 M、续流二极管 D、输出电容  $C_{OUT}$  和功率因数校正器 APFC IC 组成。通过控制功率开关管的导通和关断，使交流输入电流跟随输入电压，成为近似同频同相的正弦波，从而实现近似等于 1 的功率因数<sup>[17]</sup>。

图 2.3 升压型 APFC 电路的拓扑结构

升压式结构具有以下特点：

- (1) 电路有输入电感，可减少对输入滤波器的要求，并可以防止电网中的浪涌对主电路瞬态冲击。

- (2) 如果工作在连续电流模式时，电路对电网的电磁干扰（EMI）小，RFI 低。

- (3) 输出电压大于输入电压峰值，对电网电压低（AC100V）的国家和地区特别适合。例如，输入 90~132V 交流，可转化为输出直流 200V；若输入为 90~254V 交流，直流输出可为 400V。

- (4) 高频开关器件的电压不超过输出电压，且控制开关管的源极（或双极晶体管的发射极）电位始终为零（接于地电位），因此对功率管的控制比较容易。

- (5) Boost 电路能在国际标准规定的输入电压和频率变化范围内保持正常工作。

正是由于升压式电路结构具有上述优点，因而在 APFC 电路中得到了广泛的应用。

### 2.3.2 APFC 的控制理论

基于升压式电路结构的有源功率因数校正电路可以使用多种控制方法<sup>[18]</sup>。根据电感电流是否连续，可分为不连续导通模式（DCM）、临界导通模式（TM）和连续导通模式（CCM）<sup>[19]</sup>。根据是否直接选取瞬态电感电流作为反馈量和被控制量，CCM 模式又分为间接电流控制和直接电流控制两大类；在直接电流控制方法中，按照检测电流不同，又分为峰值电流控制、滞环电流控制和平均电流控制三种控制方法。

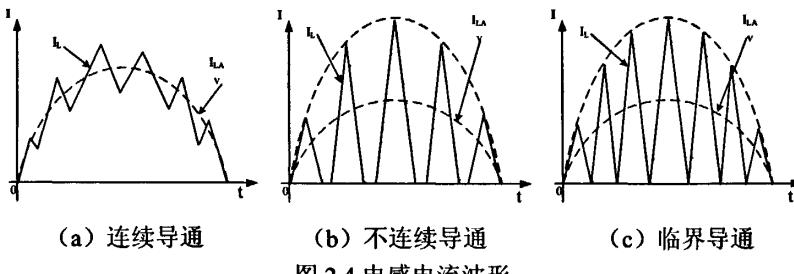

- (1) CCM 的主要优点有：输入输出的电流纹波小，滤波容易，RMS 电流小，

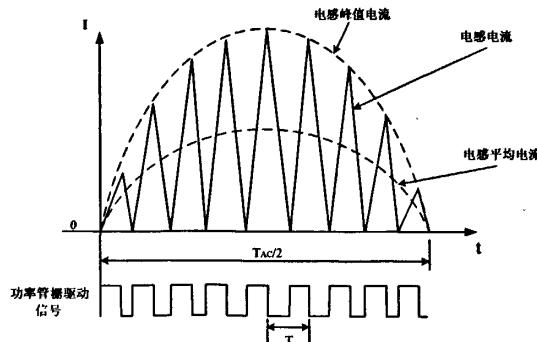

器件的导通损耗小。主要缺点有：在硬开关状态下，开关损耗较高，尤其是在续流二级管有较大反向恢复电流的情况下。而采用软开关技术又会增加电路的复杂度、制作成本也会提高。采用该模式的 PFC 电路电感电流波形如图 2.4 (a) 所示。

- (2) DCM 的主要优点有：开关管可以实现零电流导通，降低了开关损耗，避免了快恢复二极管的反向恢复电流过大，既降低了损耗又减小了开关管的电流应力。主要缺点有：器件的电流应力较大，导通损耗较高，限制了其在较大功率变换器中的应用。采用该模式的 PFC 电路电感电流波形如图 2.4 (b) 所示。

- (3) 临界导通模式的优点有：由于功率开关管在电感电流为零时导通，大大降低了导通损耗和续流二极管反向恢复时的损耗；临界导通模式将电感电流保持在连续和非连续的边界；由于每个开关周期都在电感电流放电至零时结束，只需对电压环路进行补偿。缺点有：输入电流和输出电压的纹波与连续导通模式相比都较大，由于频率可变也存在潜在的 EMI 问题。但是与非连续导通模式相比，临界导通模式的输入电流和输出电压纹波都比较小、功率因数也比较高，但电路结构要复杂一些、控制相对复杂、成本较高。可以说，临界导通模式是连续导通模式和非连续导通模式的有益折衷。采用该模式的 PFC 电路电感电流波形如图 2.4 (c) 所示。

图 2.4 电感电流波形

开关电源电路根据不同的反馈取样控制信号，可以分为电压控制模式和电流控制模式两种。电压模式是将输出电压采样分压后反馈到 PWM 比较器，输出 PWM 信号控制功率开关管，从而控制输出电压。电压控制模式是一个单闭环电压控制系统，即只有一个反馈环路，系统响应慢，很难达到较高的线性调整率精度。电流模式除了具有电压模式的输出电压反馈控制以外，还具有一个电流反馈控制，将两个控制信号进行比较，输出的 PWM 信号控制功率开关管。电流模式是电压、电流双闭环控制系统，一个是检测输出电压的电压外环，一个是检测功率开关管电流或电感电流、具有周期限流功能的电流内环。与电压模式控制方法相比，电流模式控制方法具有较好的电源电压和负载调整特性、响应速度更快，

因此在 APFC 电路中得到广泛的应用。在连续导通模式中电流模式控制方法又主要分为三种控制方式：滞环电流控制、平均电流控制、峰值电流控制。

- (1) 滞环电流控制是检测 APFC 电路中电感上的电流，当电感电流达到一定值时，开关管开始导通；电感电流下降到一定值时，开关管陡然截止。它的控制方式是利用工作频率改变来控制开关管的导通和截止。一般设计输出滤波电路时，按最低工作频率考虑。所以开关电源的体积小、重量轻、工作损耗小。

- (2) 平均电流控制是开关电源和电子镇流器对有源功率因数校正用得最多的一种方法。THD 值小，对噪声不敏感，电感电流峰值与平均值之间的误差小，具有恒定的工作频率，可以任意拓扑各种控制电路，输入电压可以调节。其缺点是控制电路比较复杂，需要增加电流误差放大器，而且外围器件的参数设计和选择也较为复杂。

- (3) 峰值电流控制法是检测峰值电流，采用恒定的开关电源频率，只有稳定的工作频率才能有效地、快速地测出峰值电流，并将这一电流均化来控制开关管，对 PWM 进行调节，使输入电流与输入电压保持同步，从而提高功率因数。由于输入电流被均化，在电路中需要对输入电流波形进行斜坡补偿。

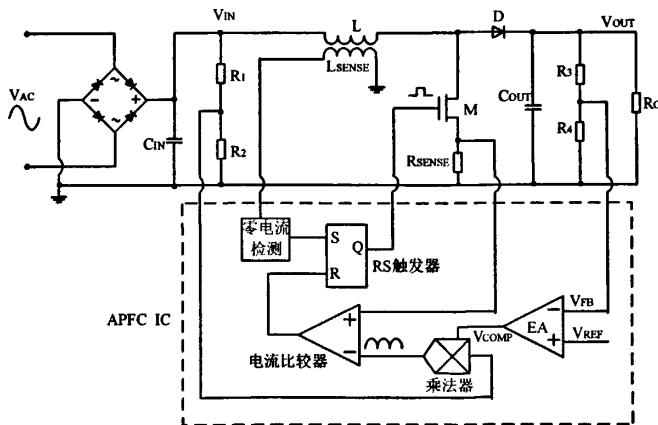

在临界导通模式下，APFC 电路通常采用峰值电流控制技术<sup>[4]</sup>。它的电流上限是一个正弦基准电流，由误差放大信号与输入电压经全桥整流后的分压信号相乘后获得，下限为零。其基本结构如图 2.5 所示。

图 2.5 采用峰值电流控制的 Boost APFC 变换器

其工作过程如下：交流输入电压  $V_{AC}$  经过桥式整流后得到  $V_{IN}$ ， $V_{IN}$  通过  $R_1$ 、 $R_2$  分压取样后作为乘法器的一个输入信号，而输出电压  $V_{OUT}$  的反馈信号  $V_{FB}$  和基准电压  $V_{REF}$  经过误差放大器比较放大后得到信号  $V_{COMP}$ ， $V_{COMP}$  是乘法器的另一个输入信号。在稳定状态下，误差放大器的输出电压在半个工频周期内将保持

恒定，乘法器的输出信号将跟随整流后的正弦电压  $V_{IN}$  变化。乘法器的输出信号作为基准信号输入到电流比较器的反相端，而开关管 M 上的电流取样信号则作为电流比较器同相端的输入信号。当电感的电流值为峰值，即电流比较器同相端的信号幅值达到反相端的信号幅值时，通过 RS 触发器输出一个复位信号，关断功率开关管，电感电流开始下降。当  $L_{SENSE}$  构成的零电流检测器检测到电感电流下降到零时，则通过 RS 触发器输出一个置位信号，开启功率开关管，电感电流开始上升。通过这样反复的开关过程，就可以使输入电流波形与输入电压的波形基本一致，达到功率因数校正目的。

与平均电流控制相比，峰值电流控制技术电路比较简单、所需外围器件少、成本低。在 300W 以下的中小功率应用场合，采用 Boost 拓扑结构，临界模式(TM) 与峰值电流控制技术的结合，也是当前主流产品的核心技术。

## 2.4 升压型峰值电流模稳态分析

交流电网电压一般采用 50Hz 的工频，经全桥整流后得到 100Hz 的半正弦波。该频率比功率开关管的开关频率（几十 KHz~几个 MHz）小得多，所以在功率开关管的一个或几个开关周期内，可以近似认为输入电压是不变的，因此本文设计的稳态分析都按照直流稳态分析进行<sup>[20]</sup>。

### 2.4.1 单个开关周期内的基本特性

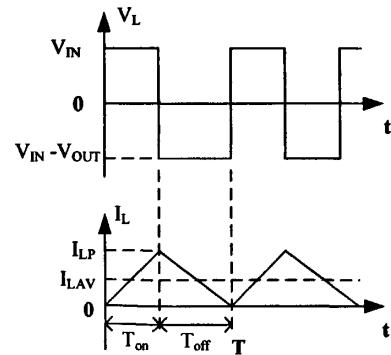

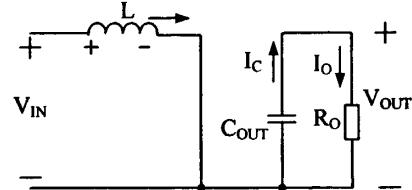

升压型电路结构如图 2.3 所示，电路中电感电压和电感电流波形如图 2.6 所示。设某一时刻整流后的电网输入电压为  $V_{IN}$ ， $T$  为功率开关管的开关周期， $T_{on}$ 、 $T_{off}$  分别为一个周期内开关管的导通时间和关断时间。功率 MOSFET 作为开关调整元件，它的导通与关断由驱动电路决定， $L$  为升压电感， $D$  为续流二极管， $C_{OUT}$  为滤波电容， $R_O$  为连接在输出端的负载。为简化电路分析，这里假设所有元件均为理想元件。

功率开关管 M 导通阶段 ( $0 < t < T_{on}$ )，由于 NMOS 管源漏间的压降<sup>[21]</sup>很小，所以二极管 D 反向截止，等效电路如图 2.7 所示。电源给电感进行储能，电感电流就从零线性上升到  $I_{LP}$ ，此时加在电感 L 两端的电压为：

图 2.6 峰值电流模式中电感电压和电感电流波形

$$V_L = V_{IN} = L \frac{di}{dt} = L \frac{I_{LP}}{T_{on}} \quad (2-10)$$

在导通期间，流经电感的电流增量为：

$$\Delta I_L (+) = \frac{V_{IN}}{L} \times T_{on} \quad (2-11)$$

电感储存的能量为：

$$E = \frac{1}{2} L (I_{LP})^2 = \frac{V_{IN}^2 T_{on}^2}{2L} \quad (2-12)$$

在这段期间，输出电容  $C_{OUT}$  给负载提供输出电流，选择适当大小的输出电容值来保证足够的放电时间。

开关管 M 关断阶段 ( $T_{on} < t < T$ )，因为电感电流不能突变，电感两端电压反向，方向如图 2.8 所示，二极管导通，电感通过二极管给输出电容  $C_{OUT}$  充电，使得输出电压高于输入电压，电感两端的电压为：

$$V_{OUT} - V_{IN} = L \frac{I_{LP}}{T_{off}} \quad (2-13)$$

此期间电感上的电流下降量为：

$$\Delta I_L (-) = \frac{V_{OUT} - V_{IN}}{L} \times T_{off} \quad (2-14)$$

因为两个阶段电感电流变化量  $\Delta I$  相等，则有：

$$\Delta I = \frac{V_{IN} T_{on}}{L} = \frac{(V_{OUT} - V_{IN})}{L} T_{off} \quad (2-15)$$

令  $D$  为一个周期内的开关导通占空比，则有  $T_{on} = DT$  和  $T_{off} = (1-D)T$ ，将  $T_{on}$  和  $T_{off}$  代入式 (2-15) 可得：

$$V_{OUT} = \frac{V_{IN}}{1-D} \quad (2-16)$$

由于  $0 < D < 1$ ，则输入输出电压关系为： $V_{IN} < V_{OUT}$ ，这是图 2.3 所示的电路结构被称作 Boost 变换器的原因。

#### 2.4.2 半个工频周期内的基本特性

将上面的分析拓展到半个工频周期。设  $V_{irms}$  为交流输入电压有效值， $\omega$  为交流输入电压的角频率，则正弦交流输入电压经桥式整流后的瞬时值可表示为：

$$V_{IN}(t) = \sqrt{2} V_{irms} \sin \omega t \quad (0 \leq \omega t \leq \pi) \quad (2-17)$$

对于采用峰值电流控制的 Boost 型 APFC (可参照图 2.5)，由于乘法器的引

图 2.7 开关 M 导通时的等效图

图 2.8 开关 M 关断时的等效图

入，峰值电流比较器的基准信号与输入电压整流后的信号  $V_{IN}(t)$  同频同相，所以电感峰值电流  $I_{LP}(t)$  在半个工频周期内必然呈现一种与  $V_{IN}(t)$  同频同相的正弦包络。又因为开关周期远小于半个工频周期，可以近似认为电感电流  $I_L(t)$  的平均值  $I_{LAV}(t)$  就是输入电流  $I_{IN}(t)$ ，而由前面的分析可知，电感电流的平均值为峰值电流的一半，所以：

$$I_{IN}(t) = I_{LAV}(t) = \frac{I_{LP}(t)}{2} \quad (2-18)$$

这样就实现了输入电流与输入电压同频同相，从理论上讲，功率因数可以达到 1。设  $P_{IN}$  为输入功率， $I_{LPK}$  为电感峰值电流在半个工频周期内的最大值，则：

$$I_{LPK} = 2 \cdot \sqrt{2} \cdot \frac{P_{IN}}{V_{irms}} \quad (2-19)$$

$$I_{LP}(t) = I_{LPK} \sin \omega t \quad (0 \leq \omega t \leq \pi) \quad (2-20)$$

将式 (2-17)、(2-20) 代入式 (2-11)、(2-14) 可得：

$$T_{on} = \frac{L \cdot I_{LPK} \cdot \sin \omega t}{\sqrt{2} V_{irms} \cdot \sin \omega t} = \frac{L \cdot I_{LPK}}{\sqrt{2} V_{irms}} \quad (2-21)$$

$$T_{off} = \frac{L \cdot I_{LPK} \cdot \sin \omega t}{V_{OUT} - \sqrt{2} V_{irms} \cdot \sin \omega t} \quad (2-22)$$

再将式 (2-19) 代入式 (2-21)、(2-22)，就可得到半个工频周期内的开关频率：

$$f_{sw}(\omega t) = \frac{1}{T_{on} + T_{off}} = \frac{V_{irms}^2 \cdot (V_{OUT} - \sqrt{2} \cdot V_{irms} \cdot \sin \omega t)}{2 V_{OUT} \cdot L \cdot P_{IN}} \quad (2-23)$$

由式 (2-21) ~ (2-23) 可以得出，在临界导通模式下，外部功率开关管的导通时间恒定，频率可变。当交流输入电压为最大时 ( $\omega t = \pi/2$ )，开关频率最小；交流输入电压过零时 ( $\omega t = 0$  或  $\omega t = \pi$ )，开关频率最大。半个工频周期 (用  $T_{AC}/2$  表示) 内的电感电流和功率开关管的驱动脉冲波形如图 2.9 所示。

图 2.9 电感电流和功率开关管驱动脉冲波形

## 第三章 XD5622 的系统设计

根据前面介绍的有关功率因数校正的相关原理，本论文设计了一款功率因数校正专用芯片 XD5622。本章我们将详细介绍 XD5622 芯片的系统设计，包括系统性能参数设计、系统原理框图设计和工艺选择。

### 3.1 芯片的性能参数

XD5622 是一款工作于临界导通模式下的升压型有源功率因数校正控制器，可用于构成符合 IEC61000-3-2 谐波电流限制标准的 300W 开关电源（如 TV、台式 PC 监视器电源等），高端 AC-DC 适配器、充电器，入口电平服务器以及 Web 服务器等。

该芯片的主要特点为：具有较宽的电源电压范围（10V~22V）；内部高线性乘法器中含有总谐波失真优化电路，能在较宽的输入电压范围和较大的负载范围内获得极低的 THD；具有欠压锁定、静态和动态两级输出过压保护功能；低启动电流（ $\leq 70\mu\text{A}$ ）和低静态电流（ $\leq 4\text{mA}$ ）；基于电感的电流检测滤波器电路；输出关断功能；图腾柱式的输出驱动电路，具有-600mA/800mA 的源电流/灌电流能力。

该芯片有 8 个引脚，其定义与功能描述如表 3.1 所示。

表 3.1 芯片引脚功能

| 序号 | 名称   | 功能                                                             |

|----|------|----------------------------------------------------------------|

| 1  | INV  | 误差放大器的反相输入引脚，PFC 变换器的输出电压通过电阻分压器反馈回该引脚，用以提供电压反馈。               |

| 2  | COMP | 误差放大器的输出引脚，该引脚和 INV 引脚之间接有补偿网络，用来确保电压控制环路的稳定性。                 |

| 3  | MULT | 乘法器电路的输入引脚。交流输入市电经整流后的输出电压经电阻分压取样后接至该引脚，为电流控制环路提供电压基准信号。       |

| 4  | CS   | 电流检测控制环路的输入信号引脚。                                               |

| 5  | ZCD  | 零电流检测信号的输入引脚，当检测到流过电感上的电流为零时，触发外部功率开关管导通。                      |

| 6  | GND  | 芯片地引脚                                                          |

| 7  | GD   | 外部功率开关管的栅极驱动信号输出引脚，图腾柱式输出级能够以 600mA 的源电流和 800mA 的灌电流驱动外部功率开关管。 |

| 8  | VCC  | 电源供电引脚，最高值可达 22V。                                              |

参考国外同类芯片设计的电特性参数指标，制订 XD5622 的电特性指标如表 3.2 所示。其中测试条件为： $T_j = -25^\circ\text{C} \sim 125^\circ\text{C}$ ， $V_{CC} = 12\text{V}$ 。

表 3.2 XD5622 电气特性指标

| 符号                                      | 参数       | 测试条件                                                              | 最小值    | 典型值  | 最大值   | 单位            |

|-----------------------------------------|----------|-------------------------------------------------------------------|--------|------|-------|---------------|

| <b>电源供电电压</b>                           |          |                                                                   |        |      |       |               |

| $V_{CC}$                                | 工作范围     | 芯片启动后                                                             | 10.3   |      | 22    | V             |

| $V_{CC_{on}}$                           | 开启门限     |                                                                   | 11     | 12   | 13    | V             |

| $V_{CC_{off}}$                          | 关闭门限     |                                                                   | 8.7    | 9.5  | 10.3  | V             |

| Hys                                     | 迟滞       |                                                                   | 2.2    |      | 2.8   | V             |

| $V_Z$                                   | 稳压电压     | $I_{CC}=20\text{mA}$                                              | 22     | 25   | 28    | V             |

| <b>供电电流</b>                             |          |                                                                   |        |      |       |               |

| $I_{start-up}$                          | 启动电流     | $V_{CC}=11\text{V}$                                               |        | 40   | 70    | $\mu\text{A}$ |

| $I_q$                                   | 静态电流     | 启动以后                                                              |        | 2.5  | 3.75  | $\text{mA}$   |

| $I_{CC}$                                | 电源工作电流   | @ 70kHz                                                           |        | 3.5  | 5     | $\text{mA}$   |

| $I_q$                                   | 静态电流     | $\text{OVP(静态或动态)或 } V_{ZCD}=150\text{mV}$                        |        |      | 2.2   | $\text{mA}$   |

| <b>乘法器</b>                              |          |                                                                   |        |      |       |               |

| $V_{MULT}$                              | 线性工作范围   |                                                                   | 0 to 3 |      |       | V             |

| $\frac{\Delta V_{CS}}{\Delta V_{MULT}}$ | 最大输出斜率   | $V_{MULT}=0 \text{ to } 0.5\text{ V}$<br>$V_{COMP}=\text{箝位电压上限}$ | 1.65   | 1.9  |       | V/V           |

| K                                       | 增益       | $V_{MULT}=1\text{ V}, V_{COMP}=4\text{ V}$                        | 0.5    | 0.6  | 0.7   | 1/V           |

| <b>误差放大器</b>                            |          |                                                                   |        |      |       |               |

| $V_{INV}$                               | 输入反馈电压门限 | $T_j=25^\circ\text{C}$                                            | 2.465  | 2.5  | 2.535 | V             |

|                                         |          | $10.3\text{V} < V_{CC} < 22\text{V}$                              | 2.44   |      | 2.56  | V             |

| $I_{INV}$                               | 输入偏置电流   | $V_{INV}=0 \text{ to } 3\text{ V}$                                |        |      | -1    | $\text{mA}$   |

| $G_V$                                   | 电压增益     | 开环                                                                | 60     | 80   |       | dB            |

| GB                                      | 增益带宽积    |                                                                   |        | 1    |       | MHz           |

| $I_{COMP}$                              | 源电流      | $V_{COMP}=4\text{V}, V_{INV}=2.4\text{V}$                         | -2     | -3.5 | -5    | $\text{mA}$   |

|                                         | 灌电流      | $V_{COMP}=4\text{V}, V_{INV}=2.6\text{V}$                         | 2.5    | 4.5  |       | $\text{mA}$   |

| $V_{COMP}$                              | 箝位电压上限   | $I_{SOURCE}=0.5\text{mA}$                                         | 5.3    | 5.7  | 6     | V             |

|                                         | 箝位电压下限   | $I_{SINK}=0.5\text{mA}$                                           | 2.1    | 2.25 | 2.4   | V             |

| <b>峰值电流比较器</b>                          |          |                                                                   |        |      |       |               |

| $I_{CS}$                                | 输入偏置电流   | $V_{CS}=0$                                                        |        |      | -1    | $\mu\text{A}$ |

| $t_{d(H-L)}$                            | 输出延迟     |                                                                   |        | 200  | 350   | ns            |

| $V_{CSclamp}$                           | 电流采样     | $V_{COMP}=\text{箝位电压上限}$                                          | 1.6    | 1.7  | 1.8   | V             |

| $V_{CSoffset}$                          | 采样电流偏移量  | $V_{MULT}=0$                                                      |        | 30   |       | mV            |

|                                         |          | $V_{MULT}=2.5\text{V}$                                            |        | 5    |       |               |

| <b>零电流检测器</b>                           |          |                                                                   |        |      |       |               |

| $V_{ZCDH}$                              | 箝位电压上限   | $I_{ZCD}=2.5\text{mA}$                                            | 5.0    | 5.7  | 6.5   | V             |

|              |           |                                                           |     |      |     |               |

|--------------|-----------|-----------------------------------------------------------|-----|------|-----|---------------|

| $V_{ZCDL}$   | 箝位电压下限    | $I_{ZCD}=-2.5\text{mA}$                                   | 0.3 | 0.65 | 1   | $\text{V}$    |

| $V_{ZCDA}$   | 上升沿触发电压   |                                                           |     | 2.4  |     | $\text{V}$    |

| $V_{ZCDT}$   | 下降沿触发电压   |                                                           |     | 1.6  |     | $\text{V}$    |

| $I_{ZCDb}$   | 输入偏置电流    | $V_{ZCD}=1 \text{ to } 4.5 \text{ V}$                     |     | 2    |     | $\mu\text{A}$ |

| $V_{ZCDdis}$ | 关断门限      |                                                           | 150 | 200  | 250 | $\text{mV}$   |

| $V_{ZCDen}$  | 重启门限      |                                                           |     |      | 350 | $\text{mV}$   |

| $I_{ZCDres}$ | 关断后重启电流   |                                                           | 30  | 75   |     | $\mu\text{A}$ |

| 输出过压         |           |                                                           |     |      |     |               |

| $I_{OVP}$    | 动态触发电流    |                                                           | 35  | 40   | 45  | $\mu\text{A}$ |

| Hys          | 迟滞        |                                                           |     | 30   |     | $\mu\text{A}$ |

|              | 静态过压门限    |                                                           | 2.1 | 2.25 | 2.4 | $\text{V}$    |

| 栅极驱动         |           |                                                           |     |      |     |               |

| $V_{OH}$     | 漏失电压      | $I_{GDsource}=20\text{mA}$                                |     | 2    | 2.6 | $\text{V}$    |

|              |           | $I_{GDsource}=200\text{mA}$                               |     | 2.5  | 3   | $\text{V}$    |

| $V_{OL}$     |           | $I_{GDsink}=200\text{mA}$                                 |     | 0.9  | 1.9 | $\text{V}$    |

| $t_f$        | 电压下降时间    |                                                           |     | 30   | 70  | $\text{ns}$   |

| $t_r$        | 电压上升时间    |                                                           |     | 40   | 80  | $\text{ns}$   |

| $V_{Oclamp}$ | 输出箝位电压    | $I_{GDsource}=5\text{mA}$ ,<br>$VCC=20\text{V}$           | 10  | 12   | 15  | $\text{V}$    |

|              | UVLO 饱和状态 | $VCC=0 \text{ to } VCC_{on}$ ,<br>$I_{sink}=100\text{mA}$ |     |      | 1.1 | $\text{V}$    |

### 3.2 芯片的整体设计

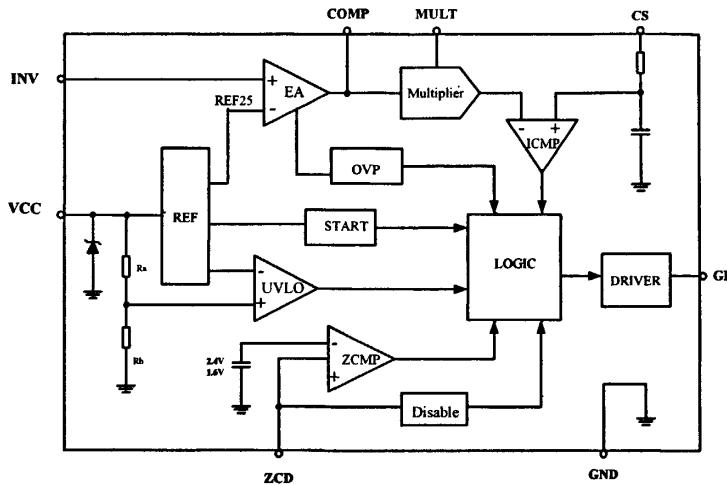

根据芯片的各项功能和性能指标，设计系统框图如图 3.1 所示，包含了系统所必需的电压电流基准、误差放大器、峰值电流比较器、零电流检测器、乘法器、逻辑控制，以及系统的自我保护、故障处理等模块。

该芯片采用升压型临界导通工作模式，峰值电流模控制技术，外部功率开关管的导通时间恒定，开关频率可变。输出电压经电阻分压后接至误差放大器的反相端，与内部产生的基准电压进行差分放大后接至乘法器；通过内部乘法器（Multiplier）来采样输入电压，与误差放大器的输出电压相乘后形成正弦电压基准；通过外部采样电阻检测峰值电感电流并将其转化为电压信号，通过峰值电流比较器来确定外部功率开关管的关断与否。当升压电感 L 上的充电电流达到峰值时，由峰值电流比较器（ICMP）输出控制信号，关断外部功率开关管，升压电感开始放电；当电感电流下降到零时，由零电流检测器（ZCMP）输出控制信号，打开外部功率开关管，升压电感开始充电。此种峰值电流关断零电流开启模式下，扰动信号不会被放大，因此，不需要斜坡补偿就能保证系统的稳定性。该芯片共包括十一个模块，简要介绍如下：

图 3.1 XD5622 系统框图

- (1) 基准模块 (REF): 产生 7V 和 5V 的带隙基准电压, 作为芯片大部分模块的电源; 产生 1.25V 带隙基准电压, 经电阻分压后为芯片各模块提供高精度的带隙基准电压。

- (2) 欠压锁定模块 (UVLO): 当 VCC 高于 12V 时, 芯片正常工作。当 VCC 低于 9.5V 时, 芯片停止工作, 同时功率开关管也被关断。

- (3) 误差放大器模块 (EA): 将 PFC 变换器的输出电压经电阻分压后的反馈信号 INV 与内部基准电压差分放大, 输出信号送至乘法器模块来调节峰值电流比较器的正弦电压基准信号幅度, 从而稳定变换器的输出电压。

- (4) 乘法器模块 (Multiplier): 将误差放大器的输出信号与交流输入电压经整流分压后的信号相乘, 产生峰值电流比较器所需要的正弦电压基准信号。乘法器中包含了一个 THD 优化电路, 这个电路的引入能够在较大的负载范围内减小交流输入电流信号的交越失真, 并能在较宽的输入电压范围内保证极低的 THD。

- (5) 两级过压保护模块 (OVP): 能安全及时地处理动态和静态过压情况: 当快速制动信号 FDOVP 达到翻转阈值时, 输出控制信号关断外部功率开关管; 当软制动信号 SDOVP 达到翻转阈值时, 输出控制信号降低乘法器 (Multiplier) 的输出电压; 静态过压检测信号 STAOPV 高于内部施密特触发器的翻转阈值时, 输出控制信号关断外部功率开关管。

- (6) 零电流检测器 (ZCMP): 当检测到外部电感电流为零时, 输出置位信号到逻辑控制模块, 使功率开关管导通, 进而对电感再次充电。

- (7) 峰值电流比较器 (ICMP): 将电感电流检测信号与乘法器产生的正弦基准信号相比较, 当电感电流达到所设定的峰值门限时, 输出控制信号, 关断外部功率开关管。

- (8) 定时器模块 (START): 芯片上电时, 定时器模块强迫驱动电路向功率开关管的栅极提供一个驱动脉冲, 使升压电感 L 开始第一次充电, 以便产生零电流检测器所需的电流检测信号。

- (9) 禁止模块 (DISABLE): 当 ZCD 电压低于 0.2V (在芯片外部引脚使能) 时, 输出控制信号 DISABLE 为低电平, 通过逻辑控制模块产生控制信号来关断内部的定时器模块和外部功率开关管。

- (10) 逻辑控制模块 (LOGIC): 当升压电感上的电流为零时, 或者达到内部乘法器所设置的正弦基准门限时, 分别输出导通或关断外部功率开关管的驱动信号, 并对各个模块产生的控制信号进行综合处理。

- (11) 驱动模块 (DRIVER): 采用图腾柱式输出以提高源电流和灌电流驱动能力, 其输出信号直接驱动外部功率开关管的导通和关断。

### 3.3 工艺的选择

为了很好的满足芯片的功能和性能要求, 加工工艺<sup>[21]</sup>需要给予很好的考虑。对于功率集成电路, 我们通常考虑 BCD 工艺。

BCD (Bipolar CMOS DMOS) 工艺是一种比较完善的工艺, 可以在同一个芯片中同时制作 Bipolar、CMOS 和 DMOS 器件。它是 1986 年由意法半导体 (ST) 公司率先研制成功。这种工艺有利于将电源与控制器结合起来, 从而向 SOC 方向发展, 是一种极有发展前途的新工艺, 目前全球知名的半导体公司都在竞相开发 BCD 工艺。了解 BCD 工艺的特点<sup>[23]</sup>, 需要先了解双极管 Bipolar、CMOS<sup>[24]</sup>和 DMOS 这三种器件的特点, 详见表 3.3。

表 3.3 Bipolar、CMOS 和 DMOS 器件的特点

| 器件类别    | 器件特点                                       | 应用                           |

|---------|--------------------------------------------|------------------------------|

| Bipolar | 两种载流子都参加导电, 驱动能力强, 工作频率高, 集成度低             | 模拟电路对性能要求较高部分 (高速、强驱动、高精度)   |

| CMOS    | 集成度高, 功耗低                                  | 适合做逻辑处理, 也可做输出驱动             |

| DMOS    | 高压大电流驱动 (器件结构决定漏端能承受高压, 高集成度可在小面积内做超大 W/L) | 模拟电路和驱动, 尤其是高压功率部分, 不适合做逻辑处理 |

BCD 工艺是一种单片集成工艺技术, 它综合了双极器件高跨导、强负载驱动能力和 CMOS 集成度高、低功耗的优点, 使其互相取长补短, 发挥各自的优点。更为重要的是, 它集成了 DMOS 功率器件, 可以在开关模式下工作, 功耗极低。不需要昂贵的封装和冷却系统就可以将大功率传递给负载。低功耗是 BCD 工艺的主要优点之一。整合过的 BCD 工艺, 可大幅度降低功率损耗, 提高系统性能,

节省电路的封装费用，并具有更好的可靠性。

BCD 工艺<sup>[25]</sup>典型器件包括低压 CMOS 管、高压 MOS 管、各种击穿电压的 LDMOS、NPN 管、纵向 PNP 管、横向 PNP 管、肖特基二极管、阱电阻、多晶电阻、金属电阻等<sup>[26]</sup>；有些工艺甚

至还集成了 EEPROM、结型场效应管 JFET 等器件。如此丰富的器件，要提高整个电路的可靠性就必须充分考虑好兼容性，比如高压器件和低压器件的兼容性；双极工艺和 CMOS 工艺的相兼容，尤其是要选择合适的隔离技术；为控制制造成本，必须考虑光刻版的兼容性，还要尽量使同种掺杂能兼容进行。这都需要精确的工艺模拟和巧妙的工艺设计，有时必须在性能与集成兼容性上作折衷选择。通常所用的 BCD 工艺都是双阱工艺，有的工艺会采用三阱甚至四阱工艺来制作不同击穿电压的高压器件<sup>[27][28]</sup>。

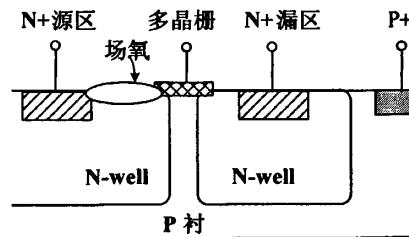

DMOS 与 CMOS 器件结构类似，也有源、漏、栅等电极，但是漏端击穿电压高。DMOS 的主要技术指标有：导通电阻、阈值电压、击穿电压等。DMOS 主要有两种类型，垂直双扩散金属氧化物半导体场效应管 VDMOSFET (vertical double-diffused MOSFET) 和横向双扩散金属氧化物半导体场效应管 LDMOSFET (lateral double-diffused MOSFET)。

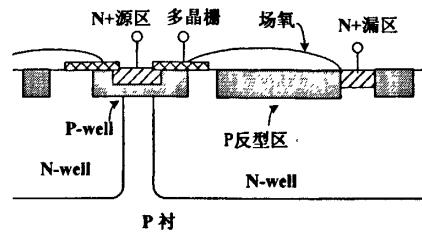

### 1) LDMOS

LDMOS 由于更容易与 CMOS 工艺兼容而被广泛采用。LDMOS<sup>[29]</sup>器件结构如图 3.2 所示，它是一种双扩散结构的功率器件。这项技术是在相同的源/漏区域进行两次注入：一次注入浓度较大的砷 (As)，另一次注入浓度较小的硼 (B)。注入之后再进行一个高温推进过程，由于硼扩散比砷快，所以在栅极边界下会沿着横向扩散更远（图中 P 阵），形成一个有浓度梯度的沟道，它的沟道长度由这两次横向扩散的距离之差决定。为了增加击穿电压，在源区和漏区之间有一个漂移区。LDMOS 中的漂移区是该类器件设计的关键，漂移区的杂质浓度比较低，因此，当 LDMOS 接高压时，漂移区由于是高阻，能够承受更高的电压。图 3.2 所示 LDMOS 的多晶扩展到漂移区的场氧上面，充当场极板，会弱化漂移区的表面电场，有利于提高击穿电压。场极板的作用与场极板的长度密切相关。要使场极板能充分发挥作用，除了要设计好 SiO<sub>2</sub>层的厚度，还要设计好场极板的长度。

LDMOS 元件具有基底，基底中形成源极区和漏极区。在源极区与漏极区之间的一部分基底上产生一个绝缘层，以便在绝缘层与基底表面之间产生一个平面介面。然后在绝缘层的一部分之上形成绝缘构件，在部分绝缘构件与绝缘层之上形成栅极层。通过这种结构，会产生平直的电流通道，这样能减少接通电阻，同

图 3.2 LDMOS 结构图

时维持高的击穿电压。

LDMOS 制造工艺结合了 BPT 和砷化镓工艺。与标准 MOS 工艺不同的是，在器件封装上，LDMOS 没有采用 BeO 氧化铍隔离层，而是直接硬接在衬底上，导热性能得到改善，提高了器件的耐高温性，大大延长了器件寿命。由于 LDMOS 的负温度效应，其漏电流在受热时自动均流，而不是像双极管的正温度效应那样局部形成热点，因此管子不易损坏。所以 LDMOS 管大大加强了负载失配和过激时的承受能力。同样由于 LDMOS 管的自动均流作用，其输入-输出特性曲线在 1dB 压缩点（大信号运用的饱和区段）下弯较缓，所以动态范围变宽，有利于模拟和数字电视射频信号放大。LDMOS 在小信号放大时近似线性，几乎没有交越失真，很大程度简化了校正电路。MOS 器件的直流栅极电流几乎为零，偏置电路简单，无需复杂的带正温度补偿的有源低阻抗偏置电路。

LDMOS 有以下优势：

- (1) 卓越的效率，可降低功率消耗与冷却成本。

- (2) 卓越的线性度，可将信号预校正需求降到最低。

- (3) 高功率密度，使用较少的晶体管封装。

- (4) 超低感抗、回授电容与串流闸阻抗，目前可让 LDMOS 晶体管在双载子器件上提供 7dB 的增益改善。

- (5) 源极直接接地，提升功率增益并免除 BeO 或 AlN 隔离物质的需求。

- (6) 绝佳的稳定性，由于漏极电流温度系数为常数，所以不受热散失的影响。

- (7) 比双载流子更能承受较高的负载不匹配现象 (VSWR)，提高现场实际应用的可靠性。

- (8) 卓越的射频稳定度，在栅极与漏极间内置隔离层，可以降低回授电容。

- (9) 在平均无故障时间 (MTTF) 上有相当好的可靠度。

LDMOS 主要的缺点：功率密度低，容易受到静电的破坏。

## 2) VDMOS

VDMOS 在耐高压和节省芯片面积等方面表现出优异的性能。由于它是垂直导电结构，因此在 P 阵之间存在一个寄生结型场效应管，由于需要保证高的击穿电压，需要一个能承受高击穿电压的漂移区<sup>[30][31]</sup>。

图 3.3 给出了一种与 N 阵等平面硅栅 CMOS 工艺完全兼容的高压 DMOS

器件的结构图。这种结构称为偏置栅 DMOS 结构，两端采用圆形结构可以减少 PN 结曲率，提高耐压程度。利用场氧化实现了沟道区、源区和漏区的自校准过

图 3.3 HVDMOS 结构图

程。它的多晶硅栅的位置是偏的，即多晶硅栅并不完全覆盖源区和重掺杂 N+漏区之间的区域。延伸的漏反型层的存在使得漏耗尽区在高压时扩展进入反型层而不会发生与源区穿通的危险<sup>[32]</sup>。

VDMOS 的显著特点是源极和漏极分别做在芯片的两侧，形成垂直导电通道，多个单细胞并联实现大功率。其工艺是在 N<sup>+</sup>衬底向上生长 N<sup>-</sup>高阻外延层，外延层的厚度和掺杂浓度直接决定 VDMOS 的击穿电压。VDMOS 制作过程是在外延层上采用平面自对准双扩散工艺，在水平方向上形成与 MOS 结构相同的多子导电沟道，沟道长度一般只有 1~2μm。早期的 N<sup>+</sup>源区和 P 体区是由扩散形成，近年来为了精确控制结深，出现了更为先进的离子双注入工艺。值得注意的是 P 体区与外延层构成一个反并联的寄生二极管，并且源区、体区和外延层组成了一个寄生 NPN 管。体二极管代表了 VDMOS 的耐压能力，而寄生三极管一旦触发，就会使器件失效，因此，P 体区与源极短接，并在短接处做浓硼离子注入，以减小体区电阻，削弱寄生三极管触发能力。

VDMOS 工作原理与一般的 MOS 管一样，当栅源电压 V<sub>GS</sub> 大于器件的阈值电压 V<sub>th</sub> 时，水平沟道表面形成强反型层，器件导通；否则器件关断。改变栅压的大小可以控制漏极电流的大小。为了实现高压，必须降低外延层的掺杂浓度。

有源功率因数校正控制芯片一般要求电源的直流工作电压高（10V 以上）、输出电流驱动能力强（几百 mA）、逻辑控制电路响应速度快等。本课题所研究的有源功率因数校正控制芯片的电源电压为 10V~22V，高压输出 400V，中间电路多采用标准 CMOS 和双极器件在常压下工作达到降低功耗的目的，所以设计 XD5622 采用高压工艺设计，即某公司 0.6μm 30V BCD 工艺。

## 第四章 XD5622 关键模块电路设计与仿真

根据芯片的系统架构，本章对临界导通模式下的升压型有源功率因数校正器 XD5622 的关键模块进行详细的设计与分析，包括基准电路、欠压锁定电路、误差放大器、乘法器电路、峰值电流比较器、零电流检测器和驱动电路等。同时给出了各模块基于  $0.6\mu\text{m}$  30V BCD 工艺下的 HSPICE 仿真验证结果。

### 4.1 基准电路设计

电压基准的主要功能是对电源电压进行调制，产生基准电压（T8、T7、VREF46、VREF25、VREF225、VREF2、VREF17、VREF1、VREF035、VREF02），并产生偏置电流，为其它模块提供合适的工作电流。

#### 4.1.1 输入输出信号

输入信号：

VCC2：芯片的电源电压；

GND1：地。

输出信号：

I\_UVLO：输出到欠压锁定模块的偏置电流信号；

I\_EA：输出到 EA 模块的偏置电流信号；

I\_MULT：输出到乘法器模块的偏置电流信号；

I\_DRIVER：输出到 DRIVER 模块的偏置电流信号；

T7：7V 基准电压信号；

T8：5V 基准电压信号；

REF46：4.6V 基准电压信号；

REF25：2.5V 基准电压信号；

REF225：2.25V 基准电压信号；

REF2：2V 基准电压信号；

REF17：1.7V 基准电压信号；

REF1：1V 基准电压信号；

REF035：0.35V 基准电压信号；

REF02：0.2V 基准电压信号。

### 4.1.2 电路设计

#### (1) 偏置电路

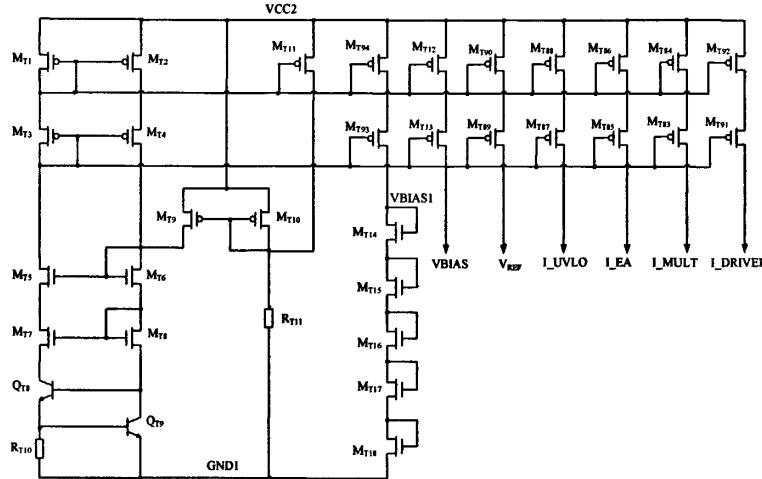

图 4.1 所示为基准电压源的偏置部分的实际电路。

图 4.1 基准偏置电路

在电源上电初期有一个启动的动作来使基准电路摆脱简并点，实现正常工作。偏置的结构采用与电源电压无关的自偏置结构，由  $M_{T1}\sim M_{T8}$  和  $Q_{T8}、Q_{T9}$  以及  $R_{T10}$  组成。 $M_{T9}、M_{T10}、M_{T11}$  和  $R_{T11}$  构成启动电路。其它电流镜像偏置部分的电流，为芯片的其它子模块提供偏置电压和偏置电流。其工作过程如下：

当电源电压  $VCC2$  从零开始上升时， $M_{T9}$  和  $M_{T10}$  的栅电位被  $R_{T11}$  拉低，使得这两个管子导通，进而将  $M_{T5}$  和  $M_{T6}$  的栅电位拉高而使其导通，这样逐渐使偏置部分开始工作，产生一个与电源电压无关的偏置电流，其值为

$$I_{MT1} = I_{RT10} = \frac{V_{BE9}}{R_{T10}} \quad (4-1)$$

$Q_{T8}$  起负反馈作用：当  $I_{RT10}$  升高时， $Q_{T8}$  的发射极电位升高，使得  $V_{BE8}$  下降， $I_{QT8}$  减小，进而减小  $I_{RT10}$ ，使偏置电流稳定。反之亦然。由于  $VCC2$  的范围是 10V~22V，这里设计  $M_{T3}\sim M_{T6}$  为高压 DMOS，隔离高压，防止  $VCC2$  过高时管子被烧坏。

设计  $M_{T11}$  和  $M_{T1}$  的宽长比为 8: 1，这样使得经过电阻  $R_{T11}$  的电流为  $8I_{MT1}$ ，当电流足够大时，就会把  $M_{T9}$  和  $M_{T10}$  的栅电位拉高，使其截止，启动电路完成功能后与工作电路分离，减小了电路的功耗。

#### (2) 电压基准

带隙基准电压<sup>[21]</sup>的产生原理是利用三极管基极-发射极电压  $V_{BE}$  的负温度系数和两个三极管基极-发射极电压差  $\Delta V_{BE}$  的正温度系数相互抵消，来产生一个对

电源电压和温度不敏感的电压信号  $V_{REF}$ 。

NPN 三极管的  $V_{BE}$  和集电极电流  $I_C$  有如下关系式<sup>[33]</sup>:

$$V_{BE} = V_T \ln \frac{I_C}{I_S} \quad (4-2)$$

其中热电压  $V_T = kT/q$ ,  $k$  为波尔兹曼常数;  $I_S$  为晶体管的反相饱和电流, 且

$$I_S = bT^{4+m} \exp(-E_g/kT) \quad (4-3)$$

其中  $b$  是一个比例系数,  $m \approx -1.5$ ,  $E_g \approx 1.12eV$  为硅的带隙能量。将式 (4-3) 代入式 (4-2) 中, 并对  $T$  求导, 假设  $I_C$  保持不变, 可得:

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln \frac{I_C}{I_S} - \frac{V_T}{I_S} \frac{\partial I_S}{\partial T} = \frac{V_{BE} - (4+m)V_T - E_g/q}{T} \quad (4-4)$$

从式 (4-4) 可以看出, 在给定温度  $T$  下  $V_{BE}$  电压的温度系数与  $V_{BE}$  本身的大小有关。当  $V_{BE} \approx 750mV$ ,  $T = 300^{\circ}K$  时,  $\partial V_{BE} / \partial T \approx -1.5mV/^{\circ}K$ , 具有负温度系数。

另一方面, 如果两个同样晶体管  $Q_1$ 、 $Q_2$  的发射极面积之比为  $1:n$ , 集电极电流均为  $I_C$ , 忽略它们的基极电流, 那么

$$\Delta V_{BE} = V_{BE1} - V_{BE2} = V_T \ln \frac{I_C}{I_S} - V_T \ln \frac{I_C}{nI_S} = V_T \ln n \quad (4-5)$$

对  $T$  求导有:

$$\frac{\partial \Delta V_{BE}}{\partial T} = \frac{k}{q} \ln n \quad (4-6)$$

这样,  $\Delta V_{BE}$  就表现出正温度系数。

图 4.2 带隙基准电压电路

根据上述原理, 设计带隙基准的实际电路如图 4.2 所示<sup>[34][35]</sup>。为了增加电路

的匹配精度，图 4.2 中  $R_{T1} \sim R_{T7}$  用作 trimming 电阻，电阻  $R_{T1} \sim R_{T5}$  总值为  $R_2$ ，且  $R_{T6} + R_{T7} = R_3$ 。这里设计  $Q_{T2}$  和  $Q_{T3}$  的发射极面积比为 1: 8， $Q_{T4}$  和  $Q_{T5}$  的发射极面积相等，则  $R_3$  上的压降为

$$V_{R3} = V_{BE3} - V_{BE2} = V_T \ln 8 \quad (4-7)$$

所以

$$V_{REF} = V_{BE1} + (R_3 + R_2) \frac{V_{R3}}{R_3} = \left(1 + \frac{R_2}{R_3}\right) V_T \ln 8 + V_{BE1} \quad (4-8)$$

这样，就可以通过调整前后两项的温度系数，使得正负温度系数相抵而得到零温度系数的电压。但是由于 BE 结电压、集电极电流和失调电压随温度变化而变化，使得 BE 结温度系数并非恒定值， $V_T$  发生器只能用来消除其线性部分，所以带隙电压温度系数仅在  $T=T_0$  时为零，在其它温度条件下为正值或负值。

图 4.2 中  $Q_{T6}$  和  $Q_{T7}$  为两级共源放大器，构成负反馈环路，保证输出基准电压  $V_{REF}$  的稳定性。

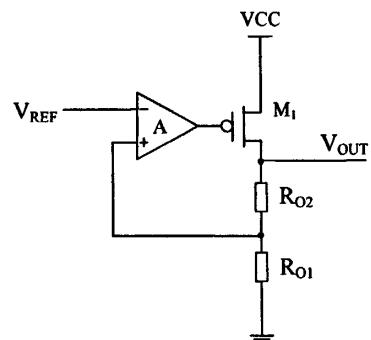

基准的最后一级 Buffer 为缓冲级，用于提高输出电压和增大带载能力。其等效架构图如图 4.3 所示。缓冲级主要通过一个运算放大器构成一个负反馈回路。由于运放的深度负反馈性，使得

$$V_+ = V_- = V_{REF} \quad (4-9)$$

则：

$$V_{OUT} = \frac{V_+}{R_{O1}} (R_{O1} + R_{O2}) = V_{REF} \left(1 + \frac{R_{O2}}{R_{O1}}\right) \quad (4-10)$$

通过调节  $R_{O1}$  和  $R_{O2}$  的比例就可以得到不同的基准电压  $V_{OUT}$ 。如果设置  $M_1$  的宽长比很大，那么  $V_{OUT}$  可以有很大的带载能力，可以用作芯片的内部电源，使芯片内部电路受外部电源影响很小，从而提高电源抑制比。另外，由  $V_{OUT}$  分压得到的低电压基准也具有提供小电流的能力，能够减轻 BCD 工艺中三极管基极吸收电流的影响。 $M_{T22}$ 、 $M_{T23}$ 、 $M_{T33}$  和  $M_{T34}$  为耐高压管 DMOS，用于隔离三极管和电源，防止三极管由于高压而被击穿。该缓冲级的负反馈过程为：

$$V_{OUT} \uparrow \rightarrow V_+ \uparrow \rightarrow V_{GM1} \uparrow \rightarrow V_{OUT} \downarrow$$

这样就保证了输出  $V_{OUT}$  的稳定性。

图 4.3 Buffer 等效架构图

### 4.1.3 仿真验证结果

对设计的基准电路，基于  $0.6\mu\text{m}$  30V BCD 工艺模型，采用 HSPICE 仿真软件进行仿真。

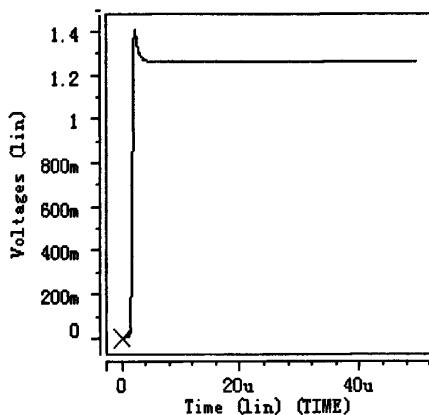

图 4.4 为 1.25V 基准电压的瞬态特性曲线。由图中曲线可以看出，开始时出现过冲现象，随着时间延长，1.25V 基准电压保持稳定，显示了良好的特性。

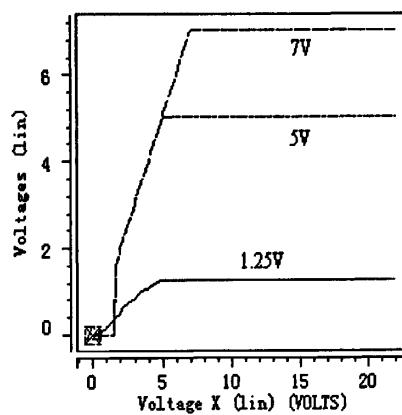

图 4.5 为 1.25V、5V 和 7V 基准电压随电源电压 VCC2 变化的直流特性曲线。从图中可以看出，当电源电压上到 5V 左右时，基准核心电路开始正常工作。在电源电压从 5V 到 22V 的变化范围内，输出基准电压保持恒定。

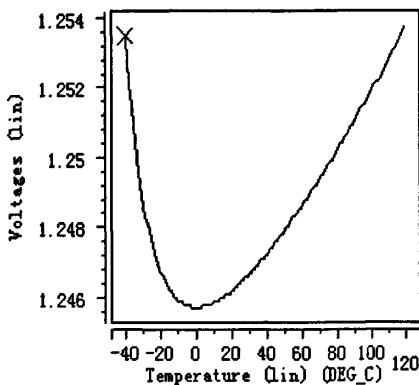

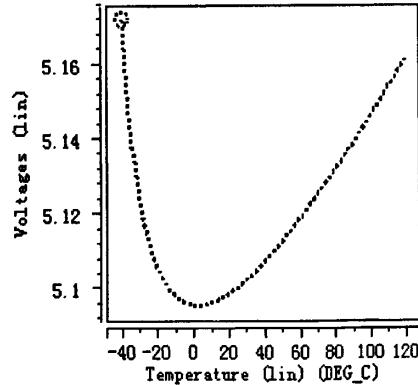

图 4.6 为温度从  $-40^{\circ}\text{C}$  到  $120^{\circ}\text{C}$  变化时，1.25V 基准电压随温度变化的情况。图 4.7 为温度从  $-40^{\circ}\text{C}$  到  $120^{\circ}\text{C}$  变化时，5V 基准电压随温度变化的情况。从图中可见，在  $-40^{\circ}\text{C}$ ~ $120^{\circ}\text{C}$  范围内，1.25V 基准电压波动了 15mV，5V 基准电压波动了 70mV，具有较好的温度稳定性。

图 4.4 基准电压瞬态曲线

图 4.5 基准电压随电源电压变化曲线

图 4.6 1.25V 带隙基准温度特性曲线

图 4.7 5V 带隙基准温度特性曲线

## 4.2 欠压锁定电路设计

欠压锁定（UVLO）电路的主要功能是：当电源电压上升到高于 12V 时，输出信号 EN 为低电平，芯片开始正常工作；当电源电压下降到低于 9.5V 时，输出信号 EN 为高电平，关断内部电源，从而使大部分模块停止工作，并且输出低电平信号 UVLO 关断外部功率管 MOSFET。

### 4.2.1 输入输出信号

输入信号：

VCC2：芯片的电源电压；

GND1：地；

T8：5V 基准电压信号；

REF25：2.5V 基准电压信号；

I\_UVLO：来自基准电路的偏置电流信号。

输出信号：

UVLO：欠压锁定信号，为低电平时关断外部功率管；

EN：使能信号，芯片正常工作时为低电平；

XEN：EN 的反相信号。

### 4.2.2 电路设计

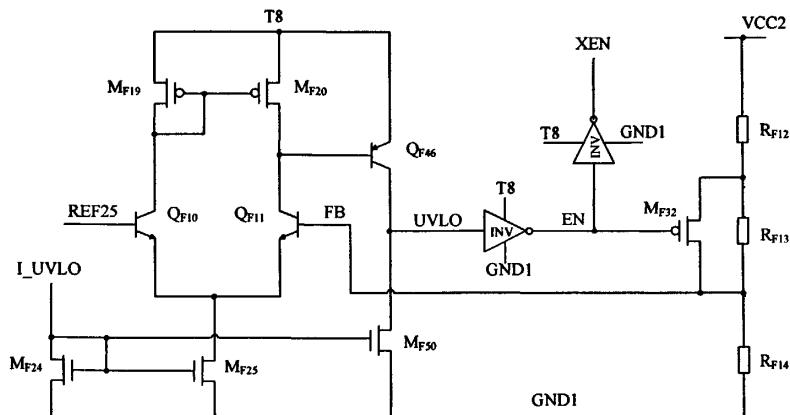

图 4.8 欠压锁定模块电路

当电源电压低于芯片的正常工作范围时，芯片内部某些电路可能无法正常工作，这可能会产生内部逻辑错误，使外部开关管处于不确定状态。若外部开关管处于导通状态而芯片的其它部分不能正常工作时，有可能使芯片烧毁，或者对外

部电路造成损坏。因此，芯片内部加入欠压锁定电路可以保证电源电压低于设定门限时，外部开关管和芯片内部的大部分模块处于关断状态。欠压锁定电路一般采用迟滞比较器来实现，这是为了避免比较器的输出电平在电源电压门限值附近来回翻转，导致芯片出现误动作。

图 4.8 为欠压锁定模块实际电路，其中  $I_{UVLO}$  为本模块提供电流偏置信号， $M_{F24}, M_{F25}, M_{F50}$  具有相同的尺寸，因此  $M_{F25}, M_{F50}$  完全镜像  $M_{F24}$  的电流  $I_{UVLO}$ 。 $M_{F19}, M_{F20}, Q_{F10}, Q_{F11}$  和  $M_{F25}$  构成比较器的第一级，其中  $M_{F25}$  作为尾电流源。 $Q_{F46}$  和  $M_{F50}$  构成第二级放大器。 $REF25$  与  $FB$  通过比较器进行比较之后生成  $UVLO$  信号， $UVLO$  信号控制开关管  $M_{F32}$  的导通状态，从而利用  $R_{F12}, R_{F13}, R_{F14}$  三个电阻对  $VCC2$  分压，产生比较器的负端输入信号  $FB$ 。由于开关管  $M_{F32}$  的状态影响着  $FB$  的产生，使得高低转换电平不相等，从而具有迟滞比较功能。下面对迟滞转换电平进行推导。

当  $VCC2$  比较低时， $UVLO$  为低电平， $EN$  为高电平， $M_{F32}$  关断，此时有

$$FB = \frac{R_{F14}}{R_{F12} + R_{F13} + R_{F14}} \times VCC2 \quad (4-11)$$

随着  $VCC2$  逐渐增大，当  $FB$  电压大于  $REF25$  时，电平发生翻转： $UVLO$  为高电平， $EN$  为低电平， $M_{F32}$  导通。因此，欠压锁定模块中  $VCC2$  的上门限阈值电压为：

$$V_{TH} = \frac{REF25 \times (R_{F12} + R_{F13} + R_{F14})}{R_{F14}} \quad (4-12)$$

当  $VCC2$  足够高，使得  $FB$  大于  $REF25$  时， $UVLO$  为高电平， $EN$  为低电平， $M_{F32}$  导通， $R_{F13}$  被短路，忽略  $M_{F32}$  的导通压降，此时有

$$FB = \frac{R_{F14}}{R_{F14} + R_{F12}} \times VCC2 \quad (4-13)$$

随着  $VCC2$  逐渐减小，当  $FB$  小于  $REF25$  时，电平发生翻转： $UVLO$  为低电平， $EN$  为高电平， $M_{F32}$  关断，芯片进入欠压锁定状态。因此，欠压锁定模块中， $VCC2$  的下门限阈值电压为：

$$V_{TL} = \frac{REF25 \times (R_{F12} + R_{F14})}{R_{F14}} \quad (4-14)$$

通过选择合适的  $R_{F12}, R_{F13}, R_{F14}$  值，设计  $V_{TH}=12V$ ， $V_{TL}=9.5V$ ，典型的迟滞电压为  $2.5V$ 。

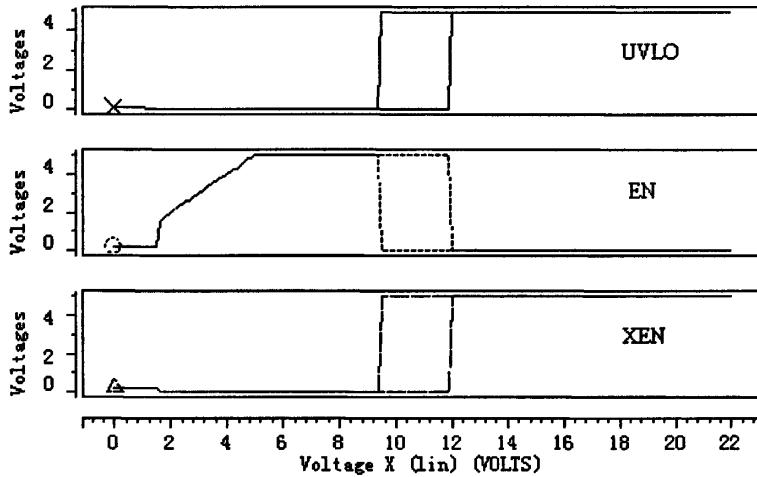

### 4.2.3 仿真验证结果

图 4.9 为 UVLO 的直流特性曲线。由图可知，在 VCC2 由低逐渐增大过程中，当上升到 12V 左右时，UVLO 由低电平翻转为高电平，EN 由高电平翻转为低电平，XEN 与 EN 相反；在 VCC2 由高逐渐减小过程中，当下降至 9.5V 左右时，UVLO 由高电平翻转为低电平，EN 由低电平翻转为高电平，XEN 与 EN 相反。迟滞电压为 2.5V，基本符合设计要求。

图 4.9 UVLO 的直流特性

表 4.1 所示为不同模型和温度下时，欠压锁定模块输入门限阈值电压。由于  $R_{F12}$ 、 $R_{F13}$ 、 $R_{F14}$  的阻值受温度影响，开关管也对电阻值有一定的影响，所以造成 FB 处的电压与设计指标的偏离，从而使欠压锁定模块的门限阈值电压  $V_{TH}$  和  $V_{TL}$  在不同情况下存在一定的偏差。

表 4.1 UVLO 模块门限阈值电压

| MODEL | $T$ (°C)  | -40   | 25    | 85    | 125   |

|-------|-----------|-------|-------|-------|-------|

|       | $V_T$ (V) |       |       |       |       |

| TT    | $V_{TH}$  | 11.74 | 12.0  | 12.21 | 12.36 |

|       | $V_{TL}$  | 9.37  | 9.50  | 9.62  | 9.70  |

| FF    | $V_{TH}$  | 13.21 | 13.52 | 13.80 | 13.98 |

|       | $V_{TL}$  | 10.45 | 10.63 | 10.79 | 10.89 |

| SS    | $V_{TH}$  | 10.43 | 10.62 | 10.80 | 12.40 |

|       | $V_{TL}$  | 8.42  | 8.51  | 8.60  | 9.71  |

| FNSP  | $V_{TH}$  | 10.93 | 11.15 | 11.34 | 11.47 |

|       | $V_{TL}$  | 8.78  | 8.89  | 8.99  | 9.05  |

| SNFP  | $V_{TH}$  | 12.68 | 12.97 | 13.23 | 13.40 |

|       | $V_{TL}$  | 10.06 | 10.24 | 10.36 | 10.46 |

### 4.3 误差放大器设计

误差放大器的主要功能是：将输入信号 INV 与 2.5V 基准信号进行差分比较放大，经反馈回路实现输出电压的稳定。输出信号 COMP 输入到乘法器中，用于调节乘法器的输出电压。同时，本模块的输出 LB5 接至 OVP，作为静态过压检测信号；LB6 接至 OVDET，作为动态过压检测信号。为了防止 COMP 的电压变化过大，电路中对其输出电平进行了高低箝位设计。

#### 4.3.1 输入输出信号

输入信号：

T7：7V 基准电压信号；

GND1：地；

INV：输出电压反馈信号，作为误差放大器的反相输入；

REF25：2.5V 基准电压信号，作为误差放大器的同相输入；

REF225：2.25V 基准电压，对误差放大器的输出 COMP 进行低箝位；

REF46：4.6V 基准电压，对误差放大器的输出 COMP 进行高箝位；

EN：使能信号，来自 UVLO 模块，正常工作时为低电平；

I\_EA：来自基准的偏置电流信号。

输出信号：

COMP：误差放大器输出信号，该引脚与 INV 引脚之间跨接补偿网络；

LB5：静态过压检测信号，输出至 OVP 模块；

LB6：动态过压检测信号，输出至 OVDET 模块。

#### 4.3.2 电路设计

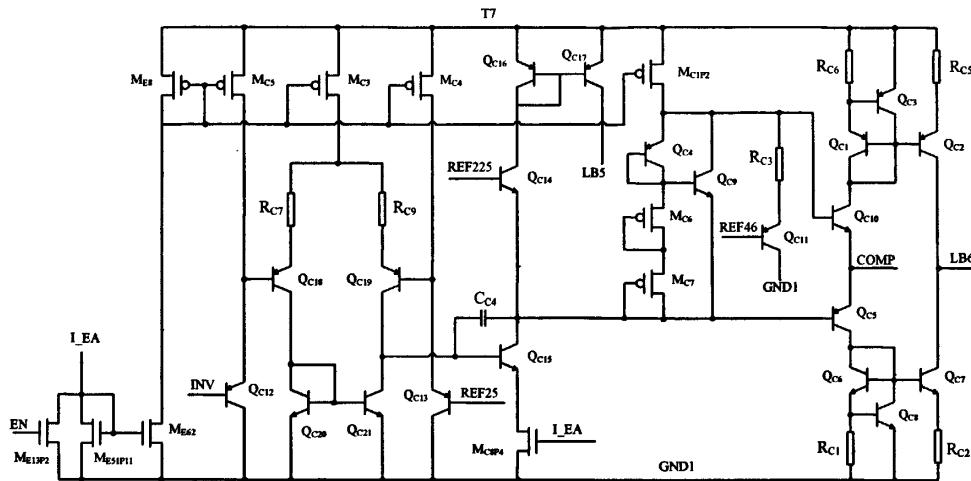

误差放大器<sup>[36]</sup>是保证升压有源功率因数校正器输出稳定的重要环节，为了获得较高的功率因数，减小输出纹波，首先必须保证误差放大器的输出信号 COMP 在半个工频周期内保持恒定，因此所设计的误差放大器的带宽比较窄。具体指标为开环增益 80dB，单位增益带宽为 1MHz。

误差放大器的实际电路如图 4.10 所示，Q<sub>C12</sub>、Q<sub>C13</sub> 构成射随器，用于抬高差分对的输入电压，增大比较器的共模输入范围。Q<sub>C18</sub>~Q<sub>C21</sub> 构成第一级差分放大器，Q<sub>C20</sub>、Q<sub>C21</sub> 作为有源负载。Q<sub>C15</sub> 作为第二级放大器，电容 C<sub>C4</sub> 用于实现密勒补偿。输出级采用甲乙类互补推挽结构。为克服交越失真，在 Q<sub>C10</sub>、Q<sub>C5</sub> 两管基极之间接入一个导电支路，使得在静态时有一个较小的电流从 T7 流经 Q<sub>C4</sub>、M<sub>C6</sub>、M<sub>C7</sub>、Q<sub>C15</sub>、M<sub>C8P4</sub> 到地，在 Q<sub>C10</sub>、Q<sub>C5</sub> 的基极之间产生  $2V_{BE}$  的电位差，所以静态时 Q<sub>C10</sub>、

图 4.10 误差放大器电路

$Q_{C5}$  已有较小的基极电流，因而两管也各有一个较小的集电极电流。在两管交替导通的过程中，将有一小段时间  $Q_{C10}$ 、 $Q_{C5}$  同时导通，避免了两个管子同时截止，因而减小了输出信号 COMP 的交越失真。另外，REF46 是来自基准的 4.6V 基准电压，用于实现对 COMP 的高箝位。REF225 为 2.25V 基准电压，用于实现对 COMP 的低箝位。 $Q_{C3}$  和  $Q_{C8}$  的引入是为了实现对  $Q_{C1}$  和  $Q_{C2}$ 、 $Q_{C6}$  和  $Q_{C7}$  组成的电流镜进行过载保护。当  $Q_{C1}$  发射极电流过大时， $Q_{C3}$  导通，使得  $Q_{C1}$  和  $Q_{C2}$  的基极电位升高，关断电流镜。

在系统环路中，若误差放大器的幅度过大，就会使采样电流过大，从而使输出电压升高，因此需要限制 EA 输出信号的幅度，电路的具体工作过程如下：

当  $V_{INV} > 2.6V$  时， $Q_{C15}$  导通，其集电极电位降低，使得  $Q_{C14}$ 、 $Q_{C16}$  导通，COMP 被低箝位于 2.25V；当  $V_{INV} < 2.4V$  时， $Q_{C15}$  截止， $Q_{C10}$ 、 $Q_{C11}$  导通，通过调节  $R_{C3}$  将 COMP 高箝位于 5.7V；当  $2.4V < V_{INV} < 2.6V$  时，APFC 变换器正常工作，COMP 电压介于 2.25V 和 5.7V 之间。

当 APFC 变换器由于掉载等原因引起输出电压持续过高时， $V_{INV} > 2.6V$ ，COMP 被低箝位于 2.25V，同时  $Q_{C16}$ 、 $Q_{C17}$  导通，LB5 向 OVP 模块输送电流，触发静态过压保护；当 APFC 变换器输出电压突然升高时，跨接于 INV 引脚和 COMP 引脚之间的外围 RC II 类频率补偿网络使  $V_{INV}$  仍稳定在 2.5V，并且将过电压引发的过电流传递到 COMP 引脚，于是 LB6 处也会有电流流入 OVDET 模块，当过电流达到一定值（ $40\mu A$ ）时就会触发动态过压保护。

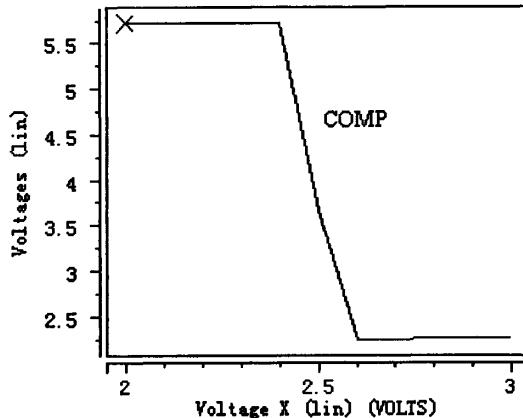

### 4.3.3 仿真验证结果

基于  $0.6\mu m$  30V BCD 工艺模型，对误差放大器电路采用 HSPICE 仿真软件进

行仿真。图 4.11 是误差放大器的 COMP 信号随 INV 引脚电压变化的直流特性曲线，由图中曲线可以看出，当  $V_{INV} > 2.6V$  时，COMP 引脚电压保持在 2.25V；当  $V_{INV} < 2.4V$  时，COMP 引脚电压保持在 5.7V；当  $2.4V < V_{INV} < 2.6V$  时，COMP 电压介于 2.25V 和 5.7V 之间。图 4.11 中的曲线显示了良好的直流特性。

图 4.11 EA 的直流特性曲线

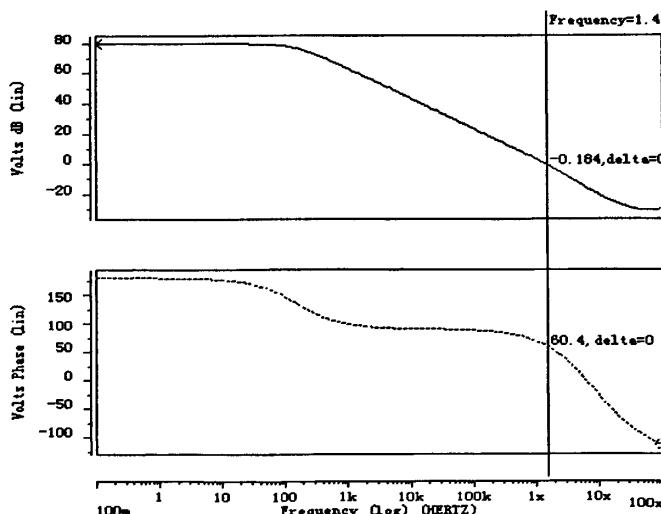

在 INV 信号端加入交流小信号进行环路增益的仿真<sup>[37]</sup>。图 4.12 是误差放大器在典型模型下的交流特性仿真图。由图中可以看出，EA 的增益高达 80dB，单位增益带宽为 1MHz，相位裕度为 60.4°。根据稳定性与频率补偿的要求：如果相位裕度太小，反馈系统的阶跃响应会出现小的减幅振荡现象，而且还会出现频率峰现象，对于更大的相位裕度，系统更加稳定，但时间响应减慢了，可以证明相位裕度等于 60° 通常被认为是最合适的数值。图 4.12 的仿真波形基本符合该理论，满足设计要求。

图 4.12 EA 的交流特性曲线

表 4.2 是 EA 模块在不同模型、不同温度下的增益和相位裕度仿真结果。

表 4.2 EA 模块的 CORNER 特性

| T(°C) | Model Index     | TT      | FF      | SS      | FNSP    | SNFP    |

|-------|-----------------|---------|---------|---------|---------|---------|

| 0     | Gain(dB)        | 74.2674 | 72.9121 | 74.7208 | 74.5345 | 73.9135 |

|       | Phase Margin(°) | 62.6666 | 62.8088 | 62.5115 | 62.7324 | 62.5957 |

| 25    | Gain(dB)        | 79.6593 | 79.6452 | 79.6967 | 79.7595 | 79.5890 |

|       | Phase Margin(°) | 60.9495 | 61.1174 | 60.7663 | 61.0320 | 60.8621 |

| 50    | Gain(dB)        | 82.4327 | 82.4285 | 82.4627 | 82.5614 | 82.3359 |

|       | Phase Margin(°) | 59.4391 | 59.6290 | 59.2309 | 59.5412 | 59.3325 |

| 80    | Gain(dB)        | 84.4157 | 84.3849 | 84.4655 | 84.5920 | 84.2721 |

|       | Phase Margin(°) | 57.9112 | 58.1384 | 57.6639 | 58.0365 | 57.7819 |

| 125   | Gain(dB)        | 72.1007 | 71.3688 | 71.6248 | 73.2910 | 70.9390 |

|       | Phase Margin(°) | 56.2574 | 56.6478 | 55.9692 | 56.4043 | 56.1122 |

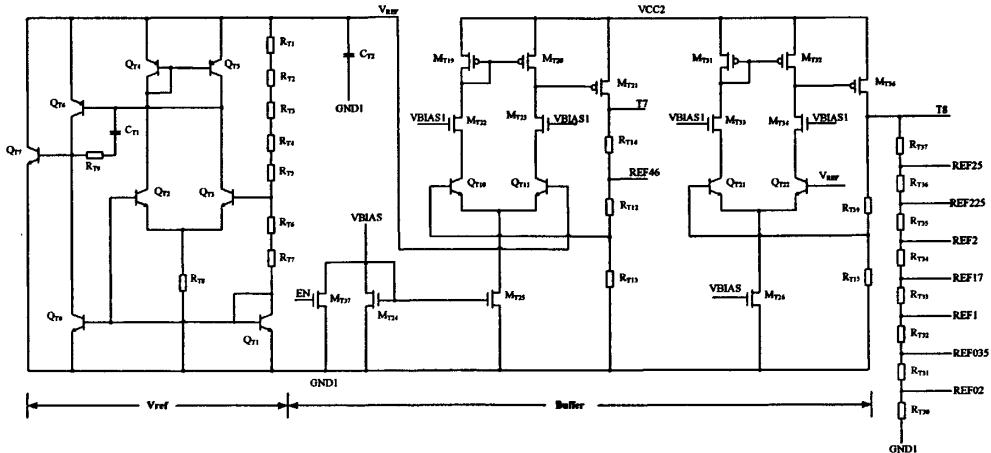

## 4.4 乘法器电路设计

乘法器是将误差放大器的输出信号  $V_{COMP}$  和交流电压经整流分压后的信号  $V_{MULT}$  相乘，得到正弦信号  $V_{PRODUCT} = K \cdot V_{MULT} \cdot (V_{COMP} - 2.5) + V_{OFFSET}$ ，作为峰值电流比较器 ICMP 的基准信号。其中  $V_{OFFSET}$  是由乘法器内嵌的 THD 优化电路产生的偏移量，可以在  $V_{MULT}$  为 0V 时抬高  $V_{PRODUCT}$  的电位，从而增大开关管在交流输入电压为零附近时的导通时间，减小 THD。

### 4.4.1 输入输出信号

输入信号：

T7：7V 基准电压信号；

GND1：地；

MULT：正弦交流输入电压整流分压后的信号；

COMP：误差放大器的输出信号；

REF25：2.5V 基准电压；

REF17：1.7V 基准电压；

SHUT：来自 LOGIC 模块的关断信号；

LB3：来自 OVDET 模块的动态过压保护“软制动”信号；

I\_MULT：来自基准模块的偏置电流信号；

EN：使能信号，来自 UVLO 模块，正常工作时为低电平。

输出信号：

PRODUCT：半波正弦信号，输出至 ICMP 模块的反相端。

#### 4.4.2 电路设计

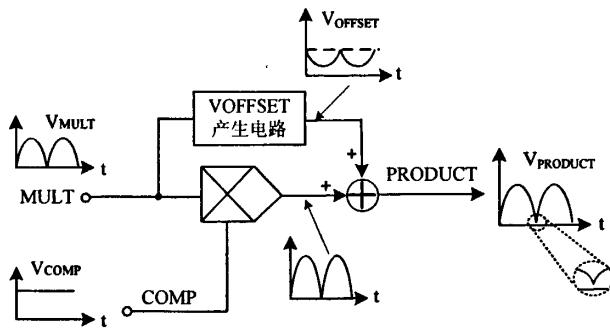

图 4.13 THD 优化设计原理

开关电源功率因数低的一个重要原因就是交流输入电流产生交越失真。所谓交越失真，是指在桥式整流器的交流输入电压过零时，交流输入电流的正弦曲线波形出现畸变，形成了一小段水平部分，也就产生了导通死角。为了减小交越失真，在电路中加入了用于 THD 优化的模拟乘法器，其原理如图 4.13 所示。其基本思想就是在乘法器的输出迭加一个微小的正向偏移电压  $V_{OFFSET}$ ，这个偏移电压是交流输入电压的函数，随着乘法器交流输入电压  $V_{MULT}$  瞬时值的增大而减小，所以当交流输入电压达到最大值时，这个偏移量已经足够小，以致可以忽略。这种设计思想主要是增大了乘法器输出电压  $V_{PRODUCT}$  在交流波形过零时的值，增大了峰值电感电流包络最低处的值，并使之更陡峭，从而减小了交越失真对输入电流的影响。因此，设计的乘法器实现了如下功能<sup>[38]</sup>：

$$V_{PRODUCT} = K \cdot V_{MULT} \cdot V_{COMP} + V_{OFFSET} \quad (4-15)$$

其中， $K$  是与输入无关的常量， $V_{OFFSET}$  随着  $V_{MULT}$  的增大而减小。

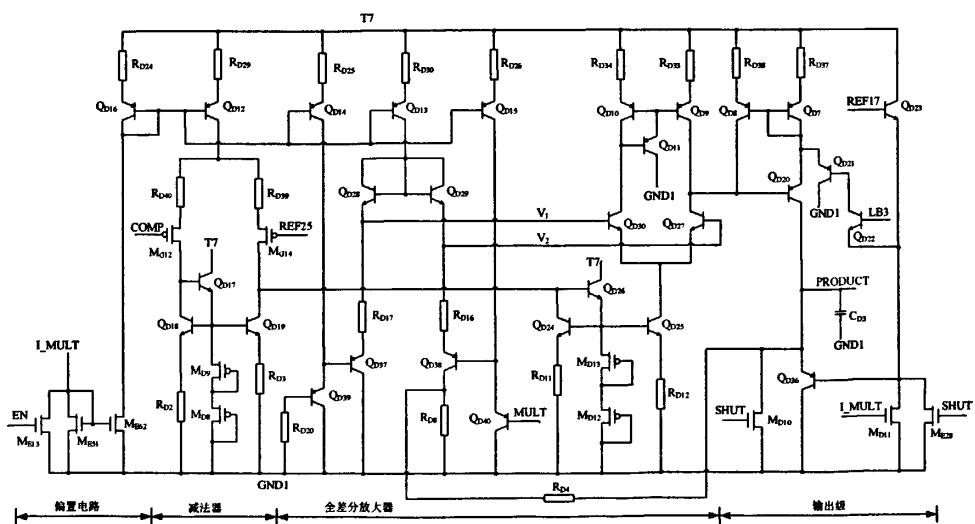

图 4.14 乘法器电路

图 4.14 所示为乘法器的实际电路，大致分为偏置、减法器、全差分放大器和输出级四部分。图中  $I_{MULT}$  为偏置电流。下面推导乘法器输出电压  $V_{PRODUCT}$ ，分析中均不考虑三极管的基极电流。

### (1) 偏置电路

偏置电流  $I_{MULT}$  来自基准偏置电路（见图 4.1）。 $M_{E51}$  和  $M_{E62}$  的宽长比相等，构成等比例电流镜，通过镜像作用为乘法器各支路提供工作电流。其大小为：

$$I_{MULT} = I_{MT1} = \frac{V_{BE9}}{R_{T10}} \quad (4-16)$$

### (2) 减法器

在图 4.14 中，相同电阻  $R_{D39}$  和  $R_{D40}$  增加了 OTA 的线性范围，同时也调整了增益。为了不影响基准电压 REF25 的稳定性，采用 PMOS 管作为差分对的输入对管。三极管  $Q_{D17}$  是为了提高电流镜的镜像精度。 $M_{G12}$  与  $M_{G14}$  的几何尺寸相等， $Q_{D18}$  与  $Q_{D19}$  发射极面积相等，且  $R_{D2} = R_{D3}$ ， $R_{D40} = R_{D39}$ ，则

$$I_{C_{QD24}} = \frac{V_{COMP} - V_{REF25}}{R_{D39}} \quad (4-17)$$

而  $Q_{D24}$  与  $Q_{D25}$  发射极面积之比为 1: 4，且  $R_{D11} = 4R_{D12}$ ，则

$$I_{C_{QD25}} \approx 4I_{C_{QD24}} \approx \frac{4 \cdot (V_{COMP} - V_{REF25})}{R_{D39}} \quad (4-18)$$

### (3) 两级差分放大器

设  $Q_{D30}$ 、 $Q_{D27}$  基极电压分别为  $V_1$ 、 $V_2$ ，因为  $Q_{D9}$  和  $Q_{D10}$  发射极面积相等，且  $R_{D33} = R_{D34}$ ，则

$$I_{C_{QD30}} = I_{C_{QD10}} = I_{C_{QD9}} \quad (4-19)$$

于是

$$I_{C_{QD8}} = I_{C_{QD27}} - I_{C_{QD9}} \quad (4-20)$$

又  $V_1 - V_{BE_{QD30}} = V_2 - V_{BE_{QD27}}$ ，且  $Q_{D30}$  和  $Q_{D27}$  发射极面积相等，有

$$\Delta V = V_2 - V_1 = V_{BE_{QD27}} - V_{BE_{QD30}} = V_T \ln \frac{I_{C_{QD27}}}{I_{C_{QD30}}} \quad (4-21)$$

又因为

$$I_{C_{QD27}} + I_{C_{QD30}} = I_{C_{QD25}} \quad (4-22)$$

由式 (4-21)、(4-22) 可得

$$\begin{cases} I_{C\_QD30} = \frac{1}{1 + e^{\frac{\Delta V}{V_T}}} \cdot I_{C\_QD25} \\ I_{C\_QD27} = \frac{e^{\frac{\Delta V}{V_T}}}{1 + e^{\frac{\Delta V}{V_T}}} \cdot I_{C\_QD25} \end{cases} \quad (4-23)$$

所以

$$I_{C\_QD8} = I_{C\_QD27} - I_{C\_QD9} = \frac{e^{\frac{\Delta V}{V_T}} - 1}{1 + e^{\frac{\Delta V}{V_T}}} \cdot I_{C\_QD25} = I_{C\_QD25} \cdot \tanh\left(\frac{\Delta V}{2V_T}\right) \quad (4-24)$$

同理对于第一级放大部分有

$$\begin{cases} V_1 + V_{BE\_QD28} = V_2 + V_{BE\_QD29} \\ I_{C\_QD28} + I_{C\_QD29} = I_{C\_QD13} \end{cases} \quad (4-25)$$

由于  $Q_{D28}$ 、 $Q_{D29}$  发射极面积相等，则

$$I_{C\_QD28} - I_{C\_QD29} = I_{C\_QD13} \cdot \tanh\left(\frac{\Delta V}{2V_T}\right) \quad (4-26)$$

又因为  $Q_{D37} \sim Q_{D40}$  发射极面积都相等，令  $V_{BE\_QD37} = \dots = V_{BE\_QD40} = V_{BE}$ ，

$R_{D17} = R_{D16}$ ，有

$$\begin{cases} I_{C\_QD28} = \frac{V_1 - 2V_{BE}}{R_{D17}} \\ I_{C\_QD29} = \frac{V_2 - V_{MULT} - 2V_{BE}}{R_{D16}} \end{cases} \quad (4-27)$$

所以

$$I_{C\_QD28} - I_{C\_QD29} = \frac{V_{MULT} - \Delta V}{R_{D17}} \approx \frac{V_{MULT}}{R_{D17}} \quad (4-28)$$

根据式 (4-26)、(4-28) 可得

$$\tanh\left(\frac{\Delta V}{2V_T}\right) = \frac{V_{MULT}}{R_{D17} \cdot I_{C\_QD13}} \quad (4-29)$$

将式 (4-18)、(4-29) 代入式 (4-24) 可得

$$I_{C\_QD8} = \frac{4(V_{COMP} - V_{REF25})}{R_{D39}} \cdot \frac{V_{MULT}}{R_{D17} \cdot I_{C\_QD13}} \quad (4-30)$$

又因为  $R_{D37} = R_{D38}$ ， $Q_{D7}$ 、 $Q_{D8}$  发射极面积相等，有

$$I_{C\_QD7} = I_{C\_QD8} \quad (4-31)$$

(4) 输出级

LB3 是来自 OVDET 模块的保护信号，用于两级动态过压保护的第一级，即当动态过压时，通过补偿网络流入误差放大器输出端 COMP 的电流达到  $37\mu A$  时， $V_{LB3} > 1.7V$ ，促使  $Q_{D21}$ 、 $Q_{D22}$  的导通，减小乘法器的输出电压，实现“软制动”。在正常工作状态下， $V_{LB3} < 1.7V$ ，不足以使  $Q_{D21}$ 、 $Q_{D22}$  导通。REF17 是  $1.7V$  电压基准信号，它与  $Q_{D23}$ 、 $Q_{D36}$  结合，实现对乘法器输出信号 PRODUCT 的箝位，使  $V_{PRODUCT} \leq 1.7V$ 。

当  $V_{PRODUCT} < 1.7V$  时， $Q_{D36}$  关断， $I_{C\_QD36} = 0$ ，此时

$$V_{PRODUCT} = I_{C\_QD7} \cdot R_{D4} + (I_{C\_QD38} + I_{C\_QD7}) \cdot R_{D8} \quad (4-32)$$

因为

$$\begin{cases} I_{C\_QD28} - I_{C\_QD29} = \frac{V_{MULT}}{R_{D17}} \\ I_{C\_QD28} + I_{C\_QD29} = I_{C\_QD13} \end{cases} \quad (4-33)$$

所以

$$I_{C\_QD38} = I_{C\_QD29} = \frac{1}{2} \cdot \left( I_{C\_QD13} - \frac{V_{MULT}}{R_{D17}} \right) \quad (4-34)$$

因为  $R_{D24} : R_{D30} = 2 : 1$ ， $Q_{D16}$ 、 $Q_{D13}$  发射极面积之比为  $1 : 2$ ，所以  $I_{QD13}$  可以精确地按比例镜像  $I_{QD16}$ ，即

$$I_{C\_QD13} = 2I_{C\_QD16} = 2I_{MULT} \quad (4-35)$$

将式 (4-30)、(4-31)、(4-34)、(4-35) 代入式 (4-32)，整理可得

$$\begin{aligned} V_{PRODUCT} &= \frac{2(R_{D4} + R_{D8}) \cdot (V_{COMP} - V_{REF25}) \cdot V_{MULT}}{R_{D39} \cdot R_{D17} \cdot I_{MULT}} + \frac{1}{2} \cdot (2I_{MULT} - \frac{V_{MULT}}{R_{D17}}) \cdot R_{D8} \\ &= K \cdot V_{MULT} \cdot (V_{COMP} - V_{REF25}) + V_{OFFSET} \end{aligned} \quad (4-36)$$

其中， $K = \frac{2(R_{D4} + R_{D8})}{R_{D39} \cdot R_{D17} \cdot I_{MULT}}$ ， $V_{OFFSET} = \frac{1}{2} \cdot (2I_{MULT} - \frac{V_{MULT}}{R_{D17}}) \cdot R_{D8}$

当  $V_{PRODUCT} > 1.7V$  时， $Q_{D36}$  导通， $V_{PRODUCT}$  被箝位于  $1.7V$ 。

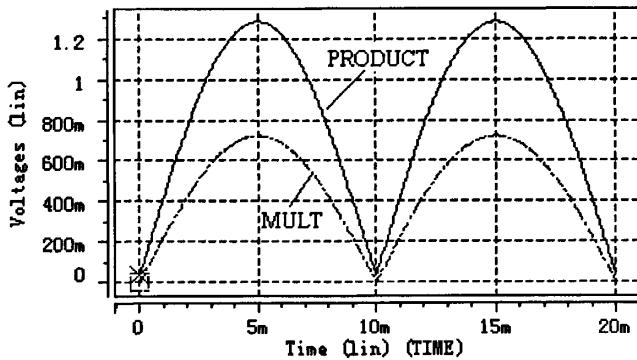

#### 4.4.3 仿真验证结果

图 4.15 是乘法器的瞬态特性曲线。 $V_{MULT}$  是交流电压（频率为  $50Hz$  的市电）经整流分压后的信号。可以看出，在  $V_{MULT}$  为  $0V$  时，乘法器的输出电压  $V_{PRODUCT}$  约为  $30mV$ ，实现了 THD 优化的功能。

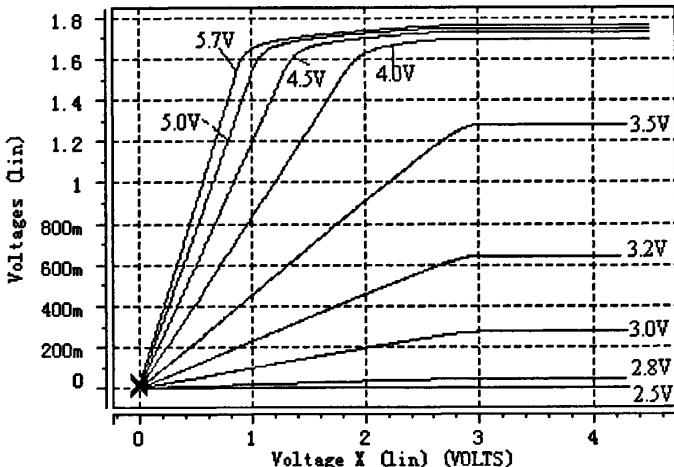

图 4.16 是乘法器的直流特性曲线，即当  $V_{COMP}$  分别为  $2.5V$ 、 $2.8V$ 、 $3.0V$ 、 $3.2V$ 、 $3.5V$ 、 $4.0V$ 、 $4.5V$ 、 $5.0V$ 、 $5.7V$ （高箝位）时，乘法器的输出电压  $V_{PRODUCT}$  随

$V_{MULT}$  的变化关系曲线。从图中曲线可以看出,  $V_{MULT}$  在 0V~3V 范围内变化时, 乘法器工作在线性范围内, 输出电压  $V_{PRODUCT}$  在 0V~1.7V 变化, 最大斜率为 1.53, 具有较大的线性范围和较高的线性度。

图 4.15 乘法器瞬态特性

图 4.16 乘法器直流特性

## 4.5 峰值电流比较器和零电流检测器的设计

零电流检测器 (ZCMP) 的主要功能是: 由迟滞比较器实现零电流检测。芯片引脚 ZCD 引入外电路电感电流信号, 然后与模块内部的参考电压进行比较, 当检测到外部电感电流为零时, ZCMP 输出置位信号到逻辑控制模块 LOGIC, 使开关管导通, 进而对电感充电。

峰值电流比较器 (ICMP) 的主要功能是: 对外部电感电流进行采样, 与乘法器的输出信号相比较, 当检测到外部电感电流达到峰值时, ICMP 输出置位信号到逻辑控制模块 LOGIC, 使开关管关断。

#### 4.5.1 输入输出信号

输入信号：

T8：5V 基准电压信号；

I\_ZCMP：来自基准的电流偏置信号，为 ZCMP 模块提供电流；

I\_ICMP：来自基准的电流偏置信号，为 ICMP 模块提供电流；

PRODUCT：半波正弦信号，来自乘法器的输出；

ZCD：芯片引脚 ZCD，检测电感电流；

CS：对外部电路的采样信号；

GND1：地。

输出信号：

ZCMP：零电流检测信号，输出至 LOGIC 模块来控制开关管；

ICMP：峰值电流关断信号，输出至 LOGIC 模块来控制开关管。

#### 4.5.2 电路设计

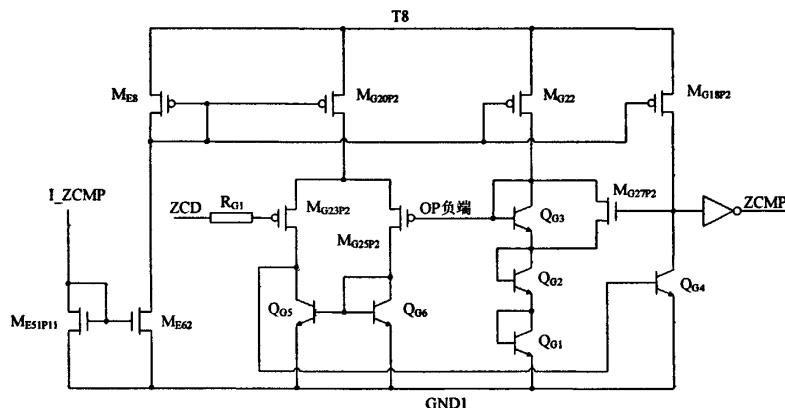

##### (1) 零电流检测器

图 4.17 零电流检测器电路

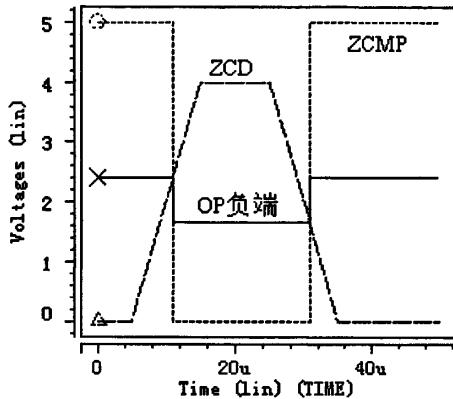

ZCMP 实际电路如图 4.17 所示，该电路采用基本的迟滞比较器实现，正相端 ZCD 为芯片引脚，负相端由三个三极管和一个 MOS 管组成。芯片引脚信号 ZCD 通过 DISABLE 模块进行箝制，使高低电平分别为 5.7V 和 0.65V。

当 ZCD 为高电平时，ZCMP 初始电平为低， $M_{G27P2}$  管导通，运放 OP 负端的参考电压为 1.6V。当 ZCD 上的信号由高电平逐渐降低到 1.6V 以下时，ZCMP 电平翻转为高， $M_{G27P2}$  管截止，OP 负端的参考电压变为  $1.6+0.8=2.4V$ ，由此得 ZCMP 的下门限电压约为 1.6V。

当 ZCD 上的信号为低电平时，ZCMP 初始电平为高， $M_{G27P2}$  管截止，运放

OP 负端的参考电压为  $1.6+0.8=2.4V$ 。当 ZCD 上的信号电压逐步上升到  $2.4V$  以上时, ZCMP 电平翻转为低,  $M_{G27P2}$  管导通, OP 负端的参考电压变为  $1.6V$ , 由此得 ZCMP 的上门限电压约为  $2.4V$ 。

结合整个芯片的功能进行分析, 当外电路电感电流降到零时, ZCD 引脚电压降到  $1.6V$ , ZCMP 由低电平翻转为高电平, 后级逻辑控制模块 (LOGIC) 检测到该上升沿信号后, 输出控制信号使外部开关管导通, 对电感再次充电。为了避免产生误动作, 引入了  $0.8V$  的迟滞电压。

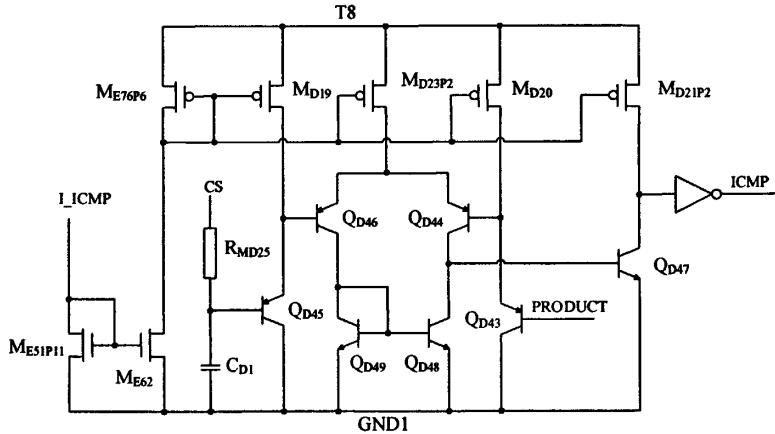

## (2) 峰值电流比较器

图 4.18 峰值电流比较器电路

ICMP 实际电路如图 4.18 所示, 引脚信号 CS 作为反相端, 同相端是乘法器输出的半波正弦信号 PRODUCT, 通过比较器两级放大, 获得的输出信号经逻辑模块去控制外部开关管的通断。 $M_{E76P6}$ 、 $M_{D19}$ 、 $M_{D23P2}$ 、 $M_{D20}$ 、 $M_{D21P2}$  为各支路提供工作电流。三极管  $Q_{D49}$  和  $Q_{D48}$  组成电流镜, 作为  $Q_{D46}$  和  $Q_{D44}$  的负载, 具有相同尺寸的  $Q_{D45}$  和  $Q_{D43}$  分别构成源跟随器, 来提高  $Q_{D46}$  和  $Q_{D44}$  的基极电位, 增大比较器的共模输入范围。第一级输出信号经过共射极放大器  $Q_{D47}$  进行第二级放大, 然后经过一个反相器得到峰值电流关断信号 ICMP, 输出至逻辑模块去控制外部开关管的通断, 高电平有效。 $R_{MD25}$  和  $C_{D1}$  用做峰值电流检测。芯片正常工作时, 同相端接乘法器的输出 PRODUCT, 用来控制升压电感峰值电流。

由图 4.18 可得各级增益。第一级的小信号增益为:

$$A_{v1} = -\beta_{QD44} \cdot (r_{o44} // r_{ce48} // r_{be47}) \quad (4-37)$$

第二级的小信号增益为:

$$A_{v2} = -\frac{\beta_{Q47} \cdot [(r_{oMD21P2}) // r_{ce47}]}{r_{be47}} \quad (4-38)$$

所以, 总的小信号增益为:

$$A_V = A_{V1} \cdot A_{V2} = \beta_{QD44} (r_{o44} // r_{ce48} // R_{be47}) \cdot \frac{\beta_{Q47} \cdot [(r_{0MD21P2}) // r_{ce47}]}{r_{be47}} \quad (4-39)$$

#### 4.5.3 仿真验证结果

图 4.19 ZCMP 瞬态特性曲线

图 4.20 ZCMP 直流特性曲线

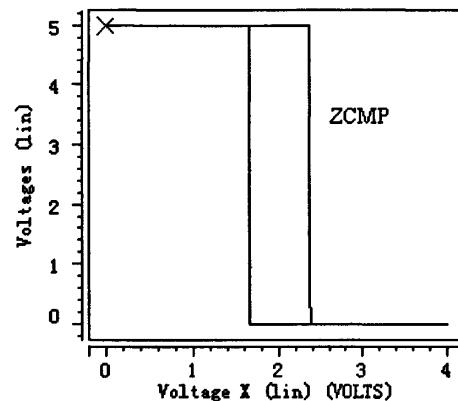

图 4.19 是 ZCMP 电路的瞬态特性仿真图, 图 4.20 是 ZCMP 电路的直流特性仿真图, 从这两幅图中可以看出, 当 ZCD 电压从零开始增大到 2.4V 时, ZCMP 从高电平变成低电平; 当 ZCD 电压从高开始下降到 1.6V 时, ZCMP 从低电平变成高电平。ZCMP 的下门限电压约为 1.6V, 上门限电压约为 2.4V, 引入了 0.8V 的迟滞电压。图中仿真结果存在一定的误差, 这是由于三极管的  $V_{BE}$  的大小受温度的影响, 且开关管  $M_{G27P2}$  对三极管的  $V_{BE}$  也存在一定的影响。

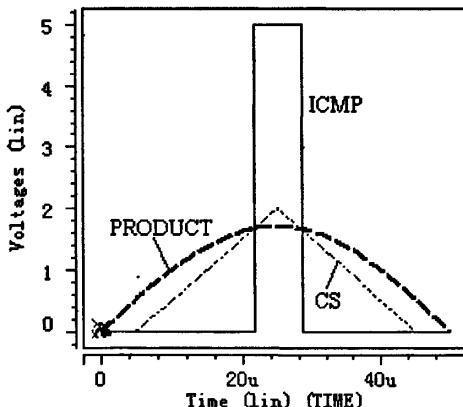

图 4.21 是 ICMP 电路的瞬态特性图, 当 CS 端的电位高于 PRODUCT 端的电位时, 输出 ICMP 变为高电平, 否则输出为低电平。在典型模型下, 温度为 25°C 时, 测得输出迟延  $T_d(H-L)$  为 131.19ns, 显示了良好的动态响应。满足指标要求。

图 4.21 ICMP 瞬态特性曲线

#### 4.6 驱动电路设计

对逻辑驱动模块输出的开关控制信号 DRIV 进行电平转换, 并通过图腾柱式结构输出驱动外部功率开关管的驱动信号 GD。

### 4.6.1 输入输出信号

输入信号：

VCC2：芯片电源电压；

GND1：地；

T7：内部 7V 电源；

T8：内部 5V 电源；

I\_DRIVER：来自 REF 模块的电流偏置信号；

XEN：使能信号，正常工作时为高电平；

DRIV：来自 LOGIC 模块的开关管控制信号。

输出信号：

GD：输出至外部开关管的驱动信号，高电平时开启外部开关管。

### 4.6.2 电路设计

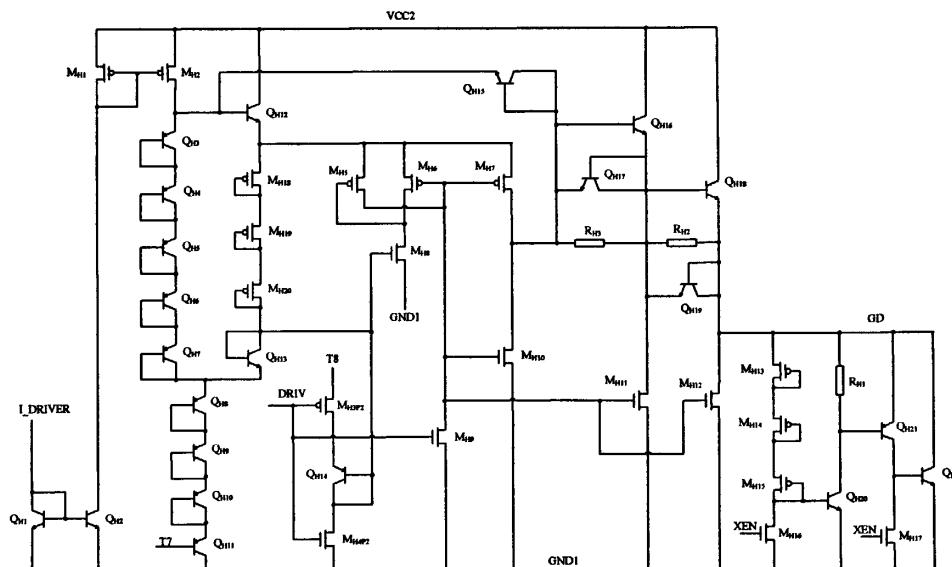

图 4.22 驱动模块电路

图 4.22 是驱动模块的实际电路图。当芯片电源电压 VCC2 在正常工作范围内时，XEN 为高电平。若 DRIV 为高电平，则  $M_{H4P2}$  和  $M_{H9}$  导通，它们的漏极电位都降低，于是  $M_{H10}$ 、 $M_{H11}$ 、 $M_{H12}$  关断， $M_{H8}$  关断， $M_{H6}$ 、 $M_{H7}$  导通，进而  $Q_{H16}$  和  $Q_{H18}$  导通，GD 输出高电位，打开外部开关管；若 DRIV 为低电平，则  $M_{H9}$  关断， $M_{H3P2}$  导通， $M_{H8}$  导通，使得  $M_{H5}$  导通，将  $M_{H10}$ 、 $M_{H11}$  和  $M_{H12}$  的栅极电位拉高使其导通，GD 输出低电位，关断外部开关管。

二极管连接的  $Q_{H3} \sim Q_{H10}$  用来实现对  $Q_{H12}$  的基极电压箝位，当电源电压 VCC2

过高时，通过三极管的 BE 结的电压  $V_{BE}$  可以使  $Q_{H12}$  的基极电压被箝位于 12V 左右，防止当电源电压过高时烧坏晶体管。接成二极管形式的  $M_{H18} \sim M_{H20}$  宽长比很小，工作在饱和状态，其作用相当于电阻，但是相对于电阻更加节省面积。

$Q_{H16}$  与  $Q_{H18}$  构成了达林顿复射极管。接成二极管形式的  $Q_{H17}$ 、 $Q_{H19}$  是为了加快晶体管的关断速度。以  $Q_{H17}$  为例，当 DRIV 信号为低电平时， $Q_{H16}$  基极电位降低， $Q_{H17}$  提供了一条反向  $I_{B\_QH17}$  的电流通路，加快了  $Q_{H16}$  的关断过程。同理， $Q_{H19}$  会加快外部功率开关管的关断过程。另外，当 DRIV 变为低电平时， $M_{H11}$  导通，将  $Q_{H18}$  的基极电位拉低，也提供了一条反向  $I_{B\_QH19}$  的电流通路，达到快速关断  $Q_{H18}$  的目的，这样能降低输出级的静态功耗。

$Q_{H18}$  和  $M_{H12}$  构成图腾柱式输出级，具有较低的静态功耗和较大的电流驱动能力。其中  $M_{H12}$  为 DMOS 器件，它具有较低的导通电阻，较小的阈值电压，而且能承受较高的源漏电压。当 DRIV 信号为高电平时， $M_{H9}$  导通， $Q_{H18}$  导通， $M_{H12}$  关断，输出驱动信号 GD 为高电平，打开外部开关管。当 DRIV 信号为低电平时， $Q_{H18}$  关断， $M_{H12}$  导通，输出驱动信号 GD 为低电平，关断外部开关管。

$R_{H1}$ 、 $M_{H13} \sim M_{H17}$  和  $Q_{H20} \sim Q_{H22}$  共同构成了驱动模块的下拉箝位电路。 $M_{H13} \sim M_{H15}$  宽长比很小，且接成二极管的形式，其作用相当于电阻。 $XEN$  是欠压锁定信号 UVLO 的同相信号，当欠压故障发生时， $XEN$  为低电平， $M_{H16}$  和  $M_{H17}$  截止， $Q_{H20} \sim Q_{H22}$  导通，从 GD 端拉下较大的电流到地，从而使 GD 电位迅速降低，避免在欠压状态时外部开关管产生误动作。在非欠压状态， $XEN$  为高电位， $Q_{H20}$  和  $Q_{H22}$  关断，虽然 GD 与地之间存在直流通路，但该通路的电流很小，基本不会影响图腾柱式输出级对外部开关管的控制作用。

#### 4.6.3 仿真验证结果

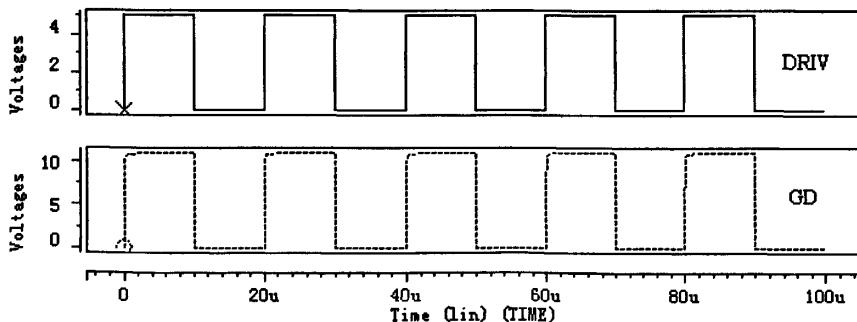

4.23 驱动模块的瞬态特性

图 4.23 是驱动模块的瞬态仿真波形图。 $XEN$  为高电平时，当 DRIV 信号为高电平时，输出驱动信号 GD 为高电平，打开外部开关管。当 DRIV 信号为低电平时，输出驱动信号 GD 为低电平，关断外部开关管。

## 第五章 芯片整体验证

本章首先介绍了 XD5622 的典型应用以及主要外围参数的确定，然后给出了基于  $0.6\mu\text{m}$  30V BCD 工艺模型下的芯片典型应用时的整体仿真结果。

### 5.1 典型应用

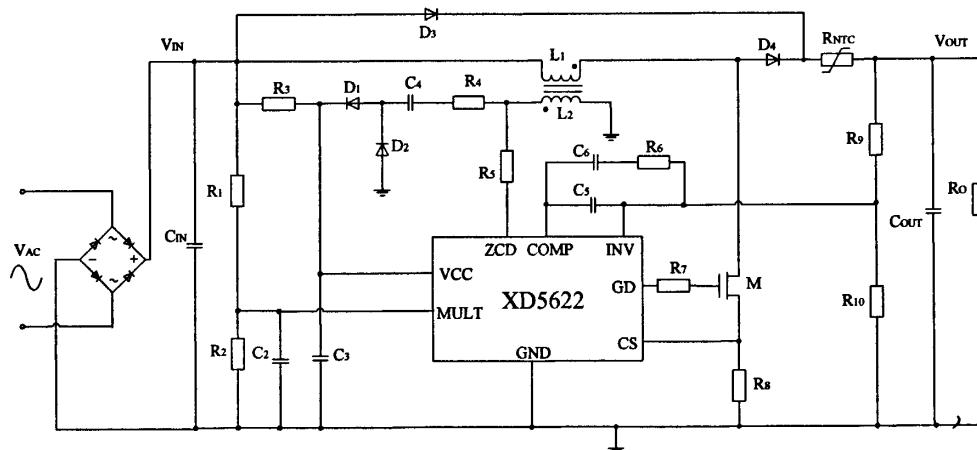

XD5622 是一款工作于临界导通模式下的升压型电流模 APFC 控制芯片，除了芯片自身的性能指标外，还必须与外围器件合理配合，才能达到更好的功率因数校正效果。其典型应用电路如图 5.1 所示。为了防止芯片中 ZCD 引脚的电流过大而使芯片烧坏，选择变压器初级线圈电感  $L_1$  的大小为  $560\mu\text{H}$ ，初、次级线圈匝数比为  $11: 1$ ，耦合系数为 0.98。设置交流输入电压峰值分别为  $220\text{V}$ ，频率  $50\text{Hz}$ ，输出功率  $250\text{W}$ 。

图 5.1 典型应用电路 (250W, 宽输入电压)

全桥整流将交流正弦市电  $V_{AC}$  转成半波正弦信号  $V_{IN}$ ，初级线圈  $L_1$  作为升压电感，次级线圈  $L_2$  用来检测  $L_1$  上的电流，通过电阻  $R_5$  输入到 ZCD 引脚。

采用负温度系数的热敏电阻  $R_{NTC}$  串联在输入端，用以增加线路的阻抗，把浪涌电流减小到安全值。当开关电源接通时，热敏电阻的阻值基本上是电阻的标称值。这样，由于阻值较大，它就限制了浪涌电流；当电容开始充电，充电电流流过热敏电阻，开始对其进行加热。由于热敏电阻具有负温度系数，随着电阻温度的升高，其电阻值开始下降，如果热敏电阻选择合适，在负载电流达到稳定状态时，其阻值应该是最小，这样就不会影响整个开关电源的效率。

$V_{CC}$  作为芯片的电源电压，范围为  $10\text{V} \sim 22\text{V}$ 。 $MULT$  引脚由电阻分压得到，大约是  $1.5\text{V}$  的半波正弦，作为乘法器的一个输入端。 $INV$  为输出端的反馈信号。

芯片上电时，为了确保升压功率开关管 M 在启动过程中正常导通，启动定时器模块强迫驱动电路向升压功率开关管的栅极提供驱动脉冲，以生成零电流检测器所需的电流检测信号，之后开关管的导通由 ZCMP 控制。当开关管刚关断时，次级电感感应电动势为正值，芯片将 ZCD 引脚的电位箝位在高电平，随着电感电流减小至零附近时，电感放电变得相对缓慢，ZCD 上的电压逐渐由高电位降低到零，使外部功率开关管导通，实现了零电流导通；当开关管刚导通时，CS 引脚的电位为低，随着电感电流增大至峰值附近时，电感充电变得相对缓慢，CS 端电位逐渐由低电位升高，当检测到峰值电压时，控制外部功率开关管关断，实现了峰值电流关断。

当输出电压上升时，误差放大器输出电压下降，使乘法器输出的基准电流值下降，开关管的导通时间缩短，流过电感的电流下降，从而使输出电压下降。反之，使输出电压上升，以达到稳定输出电压的目的。由于乘法器输入取样来自全桥整流的输出，所以乘法器的输出和全桥整流输出的电压波形相位相同，从而使电感电流的平均值和整流输出电压同相，达到功率因数校正的目的。

由于误差放大器需要窄带宽，外部补偿网络采用 II 类补偿<sup>[39]</sup>，如图 5.1 所示，其传输函数为：

$$H(s) = \frac{1}{R_1 C_3} \cdot \frac{s + \frac{1}{R_6 C_6}}{s \cdot \left( s + \frac{C_5 + C_6}{R_6 C_5 C_6} \right)} \quad (5-1)$$

根据传输函数可以得到 II 类补偿在零频率点产生一个极点，另外的零  $\omega_z$ 、极点  $\omega_p$  分别为：

$$\omega_z = -\frac{1}{R_6 C_6} \quad (5-2)$$

$$\omega_p = -\frac{C_5 + C_6}{R_6 C_5 C_6} \quad (5-3)$$

可见引入一个左半平面的零点，使相位有一个+90°的增加，可以补偿由外部 LC 电路产生的双极点，能有效地改善闭环系统的稳定性。

## 5.2 外围元件的选取

下面介绍典型应用电路图 5.1 中输入桥式整流电路、升压电感、输入电容、输出电容、续流二极管等外围器件的选择方法<sup>[5]</sup>。

### (1) 输入桥式整流电路

输入桥式整流电路没有特别的要求，只需整流二极管的输入电流、峰值电压以及温度特性满足设计要求即可。

### (2) 输入滤波电容

输入滤波电容  $C_{IN}$  是为了降低输入端的纹波和噪声，保证系统正常工作而引入的。假设所有的 AC 电流流经输入电容而不允许通过电路到输出端，输入电容器需要处理大的 AC 电流并保持小的输入纹波，所以选取一个满足 RMS 电流要求、低 ESR 的电容在电源滤波中至关重要。高频电压纹波的最大值通常是最小额定交流输入电压  $V_{irms(min)}$  的 1%~10%，这可以用一个系数  $\gamma$  来表示， $\gamma$  的典型取值范围是 0.01~0.1。于是，输入滤波电容  $C_{IN}$  的大小为：

$$C_{IN} = \frac{I_{rms(max)}}{2\pi f_{sw} \cdot \gamma \cdot V_{irms(min)}} \quad (5-4)$$

其中  $I_{rms(max)}=P_{IN}/V_{irms(min)}$  是最大输出电流， $f_{sw}$  是开关频率。输入滤波电容  $C_{IN}$  的取值要恰当。电容取值过大，虽然有助于减轻 EMI 滤波电路的负担，但是会造成功率因数和输入电流谐波质量的下降，在高输入电压、轻负载情况下更为明显；电容取值过小，虽然有助于减小输入电流的畸变，提高功率因数，但是将加重 EMI 滤波电路的负担，而且输入桥式整流电路的功耗也将增大。通常情况下，高频滤波电容不超过 1μF。

### (3) 升压电感

升压电感是 APFC 系统中重要的储能元件，增大电感值会降低输出电流纹波和输出电压纹波，增强输出信号的带载能力；而减小电感值则会获得较小的极板尺寸。电感的选择与工作频率有关，较高的工作频率允许采用较小的电感。对于升压型电流模 APFC 控制器而言，其开关频率  $f_{sw}$  为：

$$f_{sw}(\omega t) = \frac{\sqrt{2}V_{irms} \cdot (V_{OUT} - \sqrt{2} \cdot V_{irms} \cdot \sin \omega t)}{L \cdot P_{IN}} \quad (5-5)$$

其中  $V_{OUT}$  是升压变换器直流输出电压， $V_{irms}$  是交流输入电压， $P_{IN}$  是输入功率。因此开关频率在交流输入电压为零，即  $\sin(\omega t)=0$  时获得最大值；在交流输入电压达到其峰值，即  $\sin(\omega t)=1$  时获得最小值。为了确保功率开关管在电感电流为零时导通，开关频率的最小值  $f_{sw(min)}$  必须大于内部启动定时器的固有频率，在满足这一条件的基础上，得到升压电感值的估算公式为：

$$L_1 = \frac{V_{irms} \cdot (V_{OUT} - \sqrt{2}V_{irms})}{2 \cdot f_{sw(min)} \cdot P_{IN} \cdot V_{OUT}} \quad (5-6)$$

为了实现零电流检测，设计一个升压电感的次级绕组  $L_2$ ，其一端接地，另一端通过限流电阻与芯片的 ZCD 引脚相连。根据设计指标可知，当 ZCD 引脚电压

低于 1.6V 时，外部功率开关管导通。但是在这之前，即在外部功率开关管关断期间，ZCD 引脚电压必须高于 2.4V，零电流检测器的输出信号才能翻转为低电平，这样就可以在 ZCD 引脚电压低于 1.6V 时提供一个跳变信号，触发外部功率开关管导通。这样估算出升压电感与次级绕组的匝数比  $m$  为：

$$m \leq \frac{V_{OUT} - \sqrt{2}V_{rms(max)}}{2.1} \quad (5-7)$$

由于系统在刚启动时，会有数倍于稳态电流的浪涌电流流过功率开关管，使升压电感  $L_1$  饱和，因此加入了浪涌旁路二极管  $D_3$ 。

#### (4) 续流二极管

续流二极管  $D_1$  在满足系统工作电流、电压要求的前提下，重点考虑其正向导通压降和反向恢复时间指标。一般应选择具有低正向导通压降、快速恢复功能的二极管作为续流二极管。

续流二极管的功耗主要由导通损耗和反向恢复损耗两部分组成。由于采用肖特基二极管作为续流二极管，则 APFC 电路中续流二极管的平均功耗和其反向恢复功耗无关。对肖特基二极管而言，其导通损耗起主要作用。

#### (5) 功率开关管

功率开关管  $M$  的最终选择目标是在实现基本功能的同时，具有较小的功耗。其主要参数选取首先要确保其源-漏极电压、阈值电压、耐压、额定电流值等主要参数必须满足规定的指标要求，然后再折衷考虑栅电容、导通电阻等参数。

功率开关管的损耗可分为三部分：导通损耗、栅极充放电损耗和开关损耗。导通损耗是指功率开关管导通后消耗在其导通电阻  $R_{DS(on)}$  上的功率，可以表示为

$$P_{RDS(on)} = I_L^2 \times R_{DS(on)} \quad (5-8)$$

由于系统工作在临界导通模式，功率开关管的导通都是发生在电感电流  $I_L$  为零时，所以在选择功率开关管时需要着重考虑其导通电阻  $R_{DS(on)}$ 。栅极充放电损耗是由每个开关周期栅极电容充放电而引起的，即

$$P_{GATE} = V_{IN}^2 f C_{GATE} \quad (5-9)$$

开关损耗是在开关动作中，功率开关管处于放大区的时段形成的，上升、下降时间越快，开关损耗就越低。

#### (6) 输出滤波电容

输出滤波电容  $C_{OUT}$  主要起储能和对输出电压纹波滤波的作用，它的选择主要是基于系统输出电压纹波的要求。其主要技术指标有：电容量、耐电压值和电流有效值的额定值。涉及输出电容  $C_{OUT}$  的选择因素有很多：输出电流纹波、二次谐波纹波电流、直流输出电压、可承受的过电压、输出功率、输出电压纹波和维持

时间等。

输出电压一般具有二倍于工频的纹波，即 100Hz 的纹波电压  $\Delta V_{OUT}$ :

$$\Delta V_{OUT} = I_{OUT} \cdot \sqrt{\frac{1}{(2\pi \cdot 2f \cdot C_{OUT})^2} + R_{ESR}^2} \quad (5-10)$$

其中， $I_{OUT}$  表示升压变换器直流输出电流， $f$  表示交流输入电压频率，即工频， $R_{ESR}$  表示输出电容的等效串联电阻。通常，希望  $R_{ESR}$  尽可能低，以降低不必要的损耗，提高效率。这样输出电容  $C_{OUT}$  可估算如下：

$$C_{OUT} \geq \frac{P_{OUT}}{4\pi f \cdot V_{OUT} \cdot \Delta V_{OUT}} \quad (5-11)$$

其中， $P_{OUT}$  是输出功率， $\Delta V_{OUT}$  的取值通常为输出电压的 1%~5%。

输出电压纹波随着负载的增大而增大、随着工作频率的增大而减小。在输出电容的选取中，首先要根据系统输出电压纹波的要求确定需要的 ESR 指标。对于同样材料的电容，小的 ESR 需求总是意味着更大的电容值。一般来说，选取的输出电容若能满足电压纹波对 ESR 的要求、AC 电流对电容 RMS 电流指标的要求，则其容值通常已经足以满足系统滤波要求的。

### 5.3 整体仿真验证

子模块电路设计和外部器件选择完成之后，我们进行了整体电路的设计和仿真验证，各项指标基本满足设计要求。在本节中，我们给出了基于 0.6μm 30V BCD 工艺下，芯片整体电路的部分仿真结果。

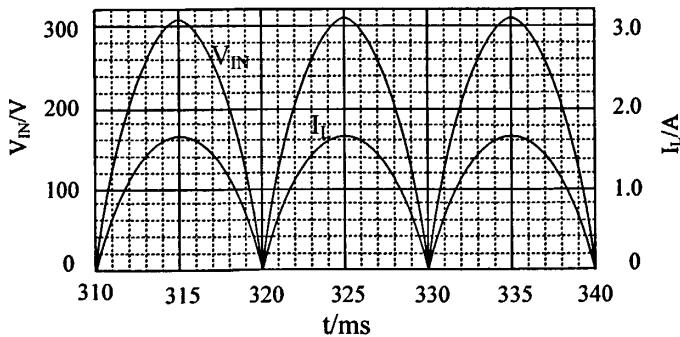

图 5.2 稳定时输入电压  $V_{IN}$  和输入电流  $I_L$  的波形图

由图 5.2 可见，升压电感的峰值电流  $I_L$  呈现出与整流后的输入电压  $V_{IN}$  同相的半波正弦包络。这说明 XD5622 的设计实现了预期的控制功能，使 APFC 升压变换器工作在临界导电模式，交流输入电流包络正弦化，且与输入电压同频同相，功率因数接近于 1。从图 5.2 我们还可以看到，在交流输入电压过零时基本看不到

电流的平直部分，改善了交越失真。这说明芯片内部的 THD 优化电路基本实现了设计要求。

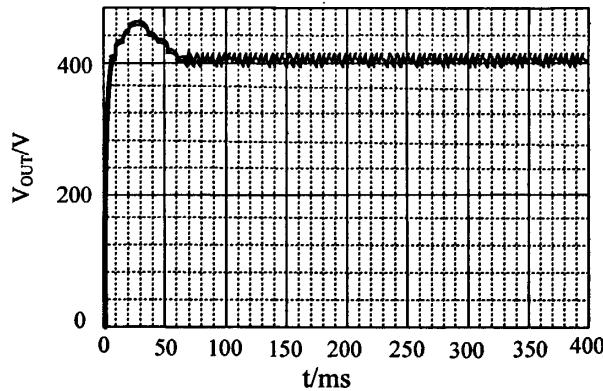

图 5.3 整体电路输出电压的瞬态特性

图 5.3 是整体的输出电压，可见经过一段时间后，输出电压稳定在 400V。设计值基本满足最初定义的指标要求。

芯片整体性能参数仿真结果如表 5.2 所示。从表 5.2 中给出的数据可以看出，设计值基本满足最初定义的指标要求。芯片的性能指标都已经基本实现，电路级的设计已经完成。

表 5.2 芯片整体部分性能参数

| 符号                                      | 测试条件                                                       | 最小值    | 典型值 | 最大值   | 单位  |

|-----------------------------------------|------------------------------------------------------------|--------|-----|-------|-----|

| <b>基准电源</b>                             |                                                            |        |     |       |     |

| VCC                                     | 芯片启动后                                                      | 10.5   |     | 22    | V   |

| V <sub>CC<sub>on</sub></sub>            |                                                            | 10.43  | 12  | 13.98 | V   |

| V <sub>CC<sub>off</sub></sub>           |                                                            | 8.42   | 9.5 | 10.89 | V   |

| Hys                                     |                                                            | 2.3    |     | 3.0   | V   |

| I <sub>start-up</sub>                   | VCC=11V                                                    |        | 42  | 70    | μA  |

| I <sub>q</sub>                          | 启动以后                                                       |        | 2.5 | 3.8   | mA  |

| I <sub>CC</sub>                         | @ 70kHz                                                    |        | 3.3 | 5     | mA  |

| I <sub>q</sub>                          | OVP(静态或动态)或<br>V <sub>ZCD</sub> =150mV                     |        |     | 2.1   | mA  |

| <b>乘法器</b>                              |                                                            |        |     |       |     |

| V <sub>MULT</sub>                       |                                                            | 0 to 3 |     |       | V   |

| $\frac{\Delta V_{CS}}{\Delta V_{MULT}}$ | V <sub>MULT</sub> =0 to 0.5 V<br>V <sub>COMP</sub> =箝位电压上限 | 1.65   |     | 1.53  | V/V |

| K                                       | V <sub>MULT</sub> =1 V, V <sub>COMP</sub> =4 V             | 0.55   | 0.6 | 0.625 | 1/V |

| <b>误差放大器</b>                            |                                                            |        |     |       |     |

| V <sub>INV</sub>                        | T <sub>j</sub> =25°C                                       | 2.455  | 2.5 | 2.53  | V   |

|                                         | 10.3V<VCC<22V                                              | 2.43   |     | 3.5   | V   |

|                      |                                               |       |        |       |     |

|----------------------|-----------------------------------------------|-------|--------|-------|-----|

| G <sub>V</sub>       | 开环                                            | 70.9  | 80     | 84.6  | dB  |

| GB                   |                                               |       | 1      |       | MHz |

| I <sub>SOURCE</sub>  | V <sub>COMP</sub> =4V, V <sub>INV</sub> =2.4V | -2.02 | -3.45  | -5.13 | mA  |

| I <sub>SINK</sub>    | V <sub>COMP</sub> =4V, V <sub>INV</sub> =2.6V | 2.5   | 4.53   |       | mA  |

| V <sub>COMP</sub>    | I <sub>SOURCE</sub> =0.5mA                    | 5.36  | 5.7    | 6.05  | V   |

|                      | I <sub>SINK</sub> =0.5mA                      | 2.13  | 2.25   | 2.45  | V   |

| <b>峰值电流比较器</b>       |                                               |       |        |       |     |

| t <sub>d(H-L)</sub>  |                                               |       | 131.19 |       | ns  |

| V <sub>Coffset</sub> | V <sub>MULT</sub> =0                          |       | 30     |       | mV  |

|                      | V <sub>MULT</sub> =2.5V                       |       | 4.83   |       |     |

| <b>零电流检测器</b>        |                                               |       |        |       |     |

| V <sub>ZCDH</sub>    | I <sub>ZCD</sub> =2.5mA                       | 5.03  | 5.72   | 6.43  | V   |

| V <sub>ZCDL</sub>    | I <sub>ZCD</sub> =-2.5mA                      | 0.3   | 0.65   | 1     | V   |

| I <sub>ZCDb</sub>    | V <sub>ZCD</sub> =1 to 4.5 V                  |       | 2      |       | μA  |

| V <sub>ZCDdis</sub>  |                                               | 150   | 198    | 250   | mV  |

| V <sub>ZCDen</sub>   |                                               |       |        | 350   | mV  |

| <b>输出过压</b>          |                                               |       |        |       |     |

| I <sub>ovp</sub>     |                                               | 34    | 41     | 47    | μA  |

| Hys                  |                                               |       | 30     |       | μA  |

| <b>栅极驱动</b>          |                                               |       |        |       |     |

| V <sub>OH</sub>      | I <sub>GDsource</sub> =20mA                   |       | 2.1    | 2.62  | V   |

|                      | I <sub>GDsource</sub> =200mA                  |       | 2.53   | 3.1   | V   |

| V <sub>OL</sub>      | I <sub>GDsink</sub> =200mA                    |       | 1.02   | 2.1   | V   |

| t <sub>f</sub>       |                                               |       | 28     | 75    | ns  |

| t <sub>r</sub>       |                                               |       | 42     | 82    | ns  |

| V <sub>Oclamp</sub>  | I <sub>GDsource</sub> =5mA,<br>VCC=20V        | 10.3  | 11     | 15.4  | V   |

## 结束语

随着电力电子技术的高速发展，开关电源的功率因数越来越受到人们的重视。由于普通电源的输入为容性阻抗或者感性阻抗，输入电流与电压有一定的偏离，产生许多高次谐波电流。这些谐波电流很容易使设备间的通信产生错误，甚至烧毁变压器。有源功率因数校正技术是降低或清除电网产生的谐波污染，提高功率因数的一种有效途径。随着对用电设备性能指标要求的不断提高，这一技术得到了广泛的应用。

本论文的设计工作是以参加的科研项目“基于 BCD 工艺的功率因数校正器的理论研究与设计”为背景，设计了一款升压型 AC-DC 有源功率因数校正控制器 XD5622。论文首先介绍了谐波的危害和国内外的发展现状；接着介绍了功率因数的基本概念，功率因数校正的基本拓扑结构、控制理论和方法，并对升压型峰值电流模控制下的电路进行了稳定性分析；然后根据系统要求进行了系统级的设计；对 XD5622 中的关键模块进行了详细的分析，并给出了基于  $0.6\mu\text{m}$  30V BCD 工艺模型下 HSPICE 软件的仿真结果；最后给出了整体电路的仿真结果。目前所设计的芯片已经通过 HSPICE 软件的前仿真验证，电路功能和性能指标均达到设计要求。

本论文的主要工作和成果有：

1. 详细阐述了 PFC 控制器的拓扑结构、控制方法和工艺选择。总结出升压型峰值电流模 APFC 电路具有导通时间恒定、开关频率可变、零电流导通、峰值电流关断等特点。

2. 由于芯片电源电压输入范围较大 (10V~22V)，设计内部高压基准电路产生 5V 和 7V 两个电压作为芯片内大部分子模块的电源电压。不仅提高了电路性能，也降低了芯片的功耗。

3. 为了改善因交越失真而导致的 THD 恶化现象，乘法器的内部嵌入了 THD 优化电路，增大外部功率开关管在交流输入电压过零时的导通时间，减小总谐波失真。

4. 芯片内部集成欠压锁定电路和两级输出过压保护电路。欠压锁定电路通过检测电源电压来控制电路是否工作；两级过压保护电路能安全及时地处理出现在启动时或负载断开时所引起的动态、静态过压情况。

5. 驱动电路采用图腾柱式的输出，增大了芯片的驱动能力。

6. 由于系统采用峰值电流关断、零电流导通模式，可以使输入电流很好地跟随输入电压的波形。每个开关周期都在电感电流放电至零时结束，因此电流环

路在外部功率开关管的占空比大于 50% 时无需斜坡补偿就可以保持其稳定性。

7. 电压环路采用 II 类补偿网络来进行补偿，可以根据芯片的实际应用环境进行选择性设计，使系统具有高度的静态电压稳定性，而且展宽了 AC-DC 变换器输入电压的调节范围。

作者和本项目组的其他成员完成了子模块电路的分析、设计与仿真以及整体电路的分析、设计、功能仿真。基于  $0.6\mu\text{m}$  30V BCD 工艺模型，利用 HSPICE 仿真软件进行了前仿真，仿真结果验证了子模块电路设计和整体电路设计的正确性。但如果要进行芯片生产，则还需要做容差分析与后仿真等一系列后续工作。同时，由于本人的水平有限，对其中的某些问题未能进行深入地分析和研究，还需要在今后的工作中努力学习和探讨。

## 致谢

值此论文完成之际，谨向所有指导、关心和帮助我的老师和同学，向始终给予我理解和支持的家人、朋友表示最衷心的感谢！

首先深深地感谢我的导师王松林教授。从我入学以来，无论是学习还是生活，一直都得到恩师的悉心教导和严格要求，也正是他无微不至的关心和指导，才使我得以完成本论文的工作。王老师扎实的学术理论、严谨的治学态度、不懈的进取精神、和蔼可亲的待人态度给我留下了深刻的印象，同时也给我树立了一个光辉的榜样。

特别感谢来新泉教授。两年来，来老师为我们创造了宽松民主的学术氛围、团结和谐的工作环境，为我们提供了难得的集成电路学习和设计机会。本论文从选题、论证、研究到最后完成无不凝结着来老师的心血。在此，谨向来老师致以最衷心的感谢。

感谢曹玉老师、李先锐老师、代国定老师、白凤莲、王安老师对我生活和工作上的悉心关照和帮助。

感谢师兄李磊、洪益文、孙朝阳、李琳，师姐元薇、罗莉、徐静萍给予我学习和工作上的帮助。

感谢各位同级同学对我学习和生活上的帮助，特别感谢陶晓冰、张沛泓、井海霞、韩敏、韩艳丽、张芬、徐剑、赵涛、曲玲玲、路璐、曼茂立、付军辉、胡佳民、冯旭、金杰、李俊、武传欣、徐自有、秦忠洋、刘斌、孙剑等同学，在和他们的探讨与交流中，令我不断开拓视野，从中受益，和他们共同学习和生活的时光将是我永远的美好回忆，在此衷心祝愿他们在以后的工作和学习中取得更大的成绩。

感谢师妹杜敏佳、王慧，师弟罗鹏、王旭、周波等。在一起合作设计该芯片的过程中他们给予了我很大的帮助。

最后感谢我的父母和家人，他们的长期鼓励、支持和无私的爱是我求学的强大精神和物质支柱，在我人生的每一个重要关头都有他们深切的关注和指引，家人无私的爱和深切的期望使我不断向前，积极进取。

## 参考文献

- [1] 路秋生. 功率因数校正技术与应用. 北京: 机械工业出版社, 2006.

- [2] R.Redl, L.Balogh. RMS, DC, Peak, and Harmonic Currents in High Frequency Power Factor Correctors with Capacitive Energy Storage. Applied Power Electronics Conference and Exposition Conference Proceedings. 1992. 533-540.

- [3] 王兆安, 杨君等. 谐波抑制和无功补偿. 北京: 机械工业出版社, 1998.

- [4] 周志敏, 周纪海. 开关电源功率因数校正电路设计与应用. 北京: 人民邮电出版社, 2004.

- [5] 侯振义. 直流开关电源技术及应用. 北京: 电子工业出版社, 2006.

- [6] Charles Mullett, Alan Ball. 开关电源中的功率因数校正技术. 电子设计应用. 2003, 6.

- [7] Daniel John Tooth, Neville McNeill, and Stephen J. A New Soft-Switching Technique Using a Modified PWM Scheme Requiring No Extra Hardware. IEEE Transactions on Power Electronics. 2001, 9, 16(5).

- [8] Staffan Norrga. An Experimental Study of a Soft-switched Isolated AC/DC Converter Without auxiliary Circuit. 35th Annual IEEE Power Electronics Specialists Conference. 2004.

- [9] Shumin Li, Geny Moschopoulos. Soft-Switching in Single-Stage AC-DC PWM Full-Bridge Converters. 26th Annual International Telecommunications Energy Conference. 2004. 51-58.

- [10] G.N. Bathurst, J. Arrillaga, N.R. Watson and A. R. Wood. Advanced modeling of the harmonic impedances of AC-DC converters. IEEE Proceedings online no. 20020657. 2002.

- [11] 许化民, 阮新波, 严仰光. 单级功率因数校正 AC/DC 变换器的综述. 电力电子技术. 2001.

- [12] Hirofumi Matsuo, Hamo Watanabe and Fujio Kurokawa. Analysis of the Novel Soft-Switching Buck-Boost Type AC-DC Converter Using Magnetic Coupling. IEEE 31st Annual Power Electronics Specialists Conference. 2000.

- [13] Lai Xinquan, Jia Ligang, Hu Juncai etc. The Design of A low Voltage and High Speed Driver Circuit for Boost DC-DC Converter. The 5th International Conference on ASIC Proceedings. 2003.

- [14] Luo Shiguo, Qiu Weihong and Issa Batarseh. Flyboost Power Factor Correction Cell and a New Family of Single-Stage AC-DC Converters. IEEE Transaction on

- Power Electronics. 2005, 1, 20(1).

- [15] Zhang J, Shao J and Xu P. Evaluation of Input Current in the Critical Mode Boost PFC Converter for distributed Power Systems. IEEE 16th APEC. 2001. 130-136.

- [16] R.Redl, B.P.Erisman. Reducing distortion in Peak-Current-Controlled Boost Power Factor Correctors. APEC Conference Proceedings. 1994. 576-583.

- [17] Z Lu, T C Green. A Study of Soft-Switched CCM Boost AC/DC Converter. Power Electronics and Variable Speed Drives. Seventh International Conference on power Electronics and Variable Speed Drives. 1998. 662-667.

- [18] 华伟. 通信开关电源的五种 PWM 反馈控制模式研究. 通信电源技术. 第二期. 2001.

- [19] 高强, 聂枝玉. 基于 ML4841 的具有 APFC 功能的 AC/DC 变换器设计. 自动化技术. 2002, 21(3).

- [20] 张占松, 蔡宣三. 开关电源的原理与设计(修订版). 北京: 电子工业出版社, 2004.

- [21] (美)毕查德·拉扎维著. 陈贵灿等译. 模拟 CMOS 集成电路设计. 西安: 西安交通大学出版社, 2002.

- [22] Bruno Murari. Smart Power Technology and the Evolution from Protective Umbrella to Complete System. Internationl Electron Devices Meeting. 1995. 9-15.

- [23] 陈志勇, 黄其煜, 龚大卫. BCD 工艺概述. 研究趋势与展望. 2006, 9.

- [24] Cedric Bassin, Hussein Ballan and Michel Declercq. High-Voltage Devices for 0.5- $\mu$ m Standard CMOS Technology. IEEE Electron Device Letters. January 2000, 21(1). 40-42.

- [25] 韩雁. 高压 BCD 集成电路中高压功率器件的设计研究. 固体电子学研究与进展. 2002, 22(3).

- [26] Appels J A ,Vaes H.M.J. High voltage thin layer devices (RESURF devices). International Electron Devices Meeting. 1979. 238-241.

- [27] 郝跃, 贾新章, 吴玉广. 微电子概论. 北京: 高等教育出版社, 2003.

- [28] 李玉山, 来新泉. 电子系统集成设计技术. 北京: 电子工业出版社, 2002.

- [29] 唐本奇, 罗晋生, 耿斌等. LVDMOS 晶体管新型器件结构的耐压分析. 半导体学报. 1999, 9.

- [30] 陈龙. 功率 VDMOS 物理结构与特性的研究与建模. 东南大学硕士学位论文. 2006.

- [31] M.Stoisiek, K.-G.Oppermann and U.Schwalke. A Dielectric Isolated High-Voltage IC-Technology for Off-Line Applications. Proceedings of the 7th International

- Symposium on Power Semiconductor Devices and ICs. 1995. 325-329.

- [32]林昌全. 基于 BCD 工艺的优化 THD 有源功率因数校正控制器设计. 西安电子科技大学硕士论文. 2007.

- [33]孙肖子, 张企民. 模拟电子技术基础. 西安: 西安电子科技大学出版社, 2001.

- [34]王红义, 王松林, 来新泉. CMOS 电压基准的设计原理. 微电子学. 2003, 10.

- [35]朱章华. 一款基于 BCD 工艺的高精度带隙基准电压电路. 电子器件. 2006.

- [36]Guo Xiaofeng, Lai Xinquan, Li Yushan. Design and application of the novel low-threshold comparator using hysteresis. The 6th International Conference on ASICON. 2005. 549-553.

- [37]P.E.艾伦, D.R.霍尔伯格. CMOS 模拟电路设计. 科学出版社, 1995.

- [38]PAUL R. GRAY, PAUL J. HURST, STEPHEN H. LEWIS and ROBERT G MEYER, Analysis and design of analog integrated circuits. Fourth Edition, JOHN WILEY & SONS. INC. New York.

- [39]Doug Mattingly. Designing Stable Compensation Networks for Single Phase Voltage Mode Buck Regulators. Intersil Technical Brief. 2003, 12.

## 在读期间研究成果

### 一、参加科研情况

1、参加西安电子科技大学电路 CAD 所科研项目“基于 BCD 工艺的功率因数校正器的理论研究与设计”，参与完成升压型有源功率因数校正（APFC）控制器 XD5622 的设计与仿真验证，该芯片采用  $0.6\mu\text{m}$  30V BCD 工艺。

2、参加西安电子科技大学电路 CAD 所科研项目“深亚微米电源管理类集成电路及各种数模混合集成电路的关键技术理论研究与设计”，参与一款升压型 DC-DC 转换器的设计与实现。

### 二、学术论文发表情况

1、刘超, 王松林, 徐剑, 陶晓冰. 高精度、低功耗的基准电压源设计. 电源技术学报. 2008.6 Vol.6 No.2.