## 摘要

随着设计水平和应用要求的不断提高,无线通信系统向着小型化和集成化方向发展。片上系统(System on Chip,SoC)成为业界焦点。近年来, SiGe BiCMOS 片上系统的全集成设计已成为国内外学术界和工业界研究的热点。

基于 Ku 波段的数字电视卫星广播 (DVB-S) 地面接收机,本文研究了工作频率在 12.25GHz—12.75GHz 的射频前端单元电路低噪声放大器(LNA)和有源双平衡混频器(active double-balance Mixer),并在此基础上采用 JAZZ 0.35  $\mu m$  SiGe BiCMOS 工艺实现了流片,为以后实现 Ku 波段 DVB-S 接收系统的单片化集成做好技术储备。

本文先介绍了 SiGe BiCMOS 射频集成电路的发展背景及其国内外动态,然后简单介绍了 JAZZ 0.35 $\mu m$  SiGe BiCMOS 工艺元件以及元件模型与电路设计的关系,再分别详细论述了低噪声放大器和有源双平衡混频器的基本设计原理和具体设计过程,其中包括指标的确定、电路的仿真和版图的优化设计。最后对所做的设计工作做一个总结。

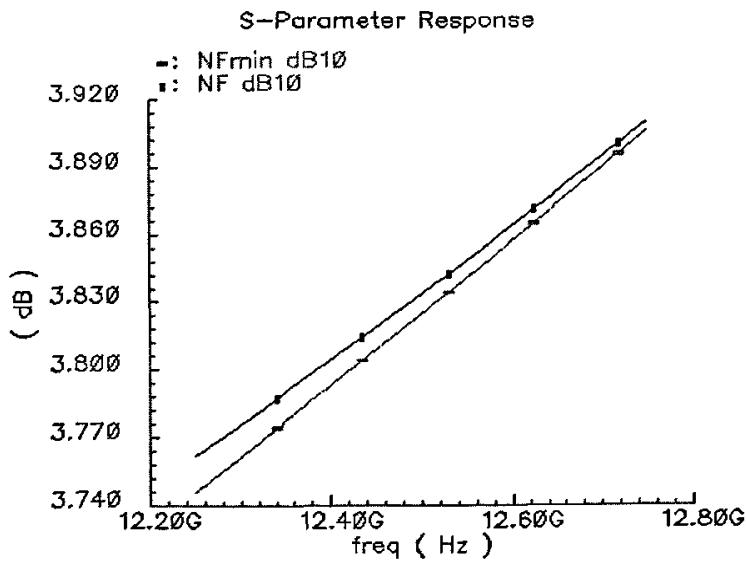

所设计的低噪声放大器在 12.25GHz—12.75GHz 宽频带内实现了 3.75dB~3.9dB 的噪声系数和 15dB 的平坦增益,输入输出匹配  $S_{11}$ 、 $S_{22}$  优于 -10dB,而功耗仅为 19.2mW, 面积为  $0.7 \times 0.7 m^2$ 。

所设计的混频器在 12.25GHz—12.75GHz 宽频带内仅以 36mW 功耗和  $0.9 \times 0.9 m^2$  的芯片面积实现了低于 6.5dB 的超低双边带噪声系数,大于 8dB 的增益, IIP3 为 -5.1dBm。

关键词: SiGe BiCMOS 射频集成电路 低噪声放大器 有源双平衡混频器

## Abstract

With the rapid development of technology, the size of wireless communication system is becoming more and more small and it's function is becoming more and more integrated. System on Chip (SoC) has become the main focus of the area of wireless communication.

In this thesis, a 12.25GHz-12.75GHz low noise amplifier (LNA), and an active double-balance mixer ,which are used in the RF front-end of the Ku-band DVB-S receiver ,are analyzed and implemented using JAZZ 0.35  $\mu m$  SiGe BiCMOS process, which are prepared for the full integration of Ku-band DVB-S receiver.

In the first, the development and trend of SiGe BiCMOS RFIC home and abroad are introduced, then, JAZZ 0.35  $\mu m$  SiGe BiCMOS process component and the relationship between component model and circuits design are introduced. After that separately the basic design theories and detail design processes of LNA and active double-balance mixer, including the schematic circuit simulation and the design and optimization of the layout were dissertated. The above design work was summarized at last.

The LNA which designed in this paper achieved 3.75dB~3.9dB noise figure (NF) and 15dB power gain in the pass band 12.25GHz-12.75GHz , and the input and output match  $S_{11}$ 、 $S_{22}$ are less than -10dB. The power dissipation of the LNA was merely 19.2mW.

The active mixer designed in this paper achieves a 6.5dB double side band noise figure, a 8dB power gain,an IIP3 of -5.1dBm, with only 36mW power dissipation and  $0.9 \times 0.9 m^2$  chip size.

**Key words:** SiGe BiCMOS    RFIC    LNA    Active Double-balance Mixer

## 独 创 性 声 明

本人声明所呈交的学位论文是本人在导师指导下进行的研究工作及取得的研究成果。据我所知，除了文中特别加以标注和致谢的地方外，论文中不包含其他人已经发表或撰写过的研究成果，也不包含为获得电子科技大学或其它教育机构的学位或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示谢意。

签名: 江金铭 日期: 2007年4月18日

## 关于论文使用授权的说明

本学位论文作者完全了解电子科技大学有关保留、使用学位论文的规定，有权保留并向国家有关部门或机构递交论文的复印件和磁盘，允许论文被查阅和借阅。本人授权电子科技大学可以将学位论文的全部或部分内容编入有关数据库进行检索，可以采用影印、缩印或扫描等复制手段保存、汇编学位论文。

(保密的学位论文在解密后应遵守此规定)

签名: 江金铭 导师签名: 李晓光

日期: 2007年4月18日

## 第一章 绪论

### 1.1 微波/射频集成电路的发展及应用前景

单片微波/射频集成电路(MMIC/RFIC)是利用半导体生产技术，将电路中所有的有源元件(如双极型晶体管、场效应晶体管等)和无源元件(如电阻、电容、电感等)都制作在同一块半导体衬底上的微波/射频电路。MMIC/RFIC 器件有使用简单、电性能指标好、可靠性高、寿命长、体积小、重量轻、一致性好、成本低等诸多优点，在当今的射频、微波电路设计中应用越来越多。如今，MMIC/RFIC 广泛应用于移动通信系统、无线视频分配系统、导航定位系统、智能化交通管理系统、卫星应用和航天领域等等。它们不仅在军事应用中具有相当的重要性，在民品应用中也同样具有较好的市场和经济效益，能显著地提高整机的性能和降低价格<sup>[1]</sup>。特别是在过去一二十年中，移动通信技术、全球定位系统(GPS)、无线局域网(WLAN)的迅猛发展，大大促进了射频集成电路的发展和应用。

近十年来通信技术以惊人的速度发展，而射频无线移动通信技术的发展显得尤为迅猛。例如以手机为代表的个人通信市场迅速增长，根据 IDC 的调查<sup>[2]</sup>，手机的交货量将从 2002 年的 3.91 亿部增加到 2006 年的 6.02 亿部，年增长率达 9.5%，预计到 2010 年，无线通信用户将达到 10 亿人，并将超过有线通信用户。便携式通信设备在提供方便、可靠的通信服务方面扮演了重要的角色。在便携式通信设备中，无线接收机前端用来接收和解调无线信号，是便携式通信设备中最关键的一部分。为了获得更方便、可靠的通信设备，无线接收机前端必须尺寸小、功耗低、工作频率高和生产成本低。

GPS 以全天候、高精度、自动化、高效率等显著特点及其所独具的定位导航、授时校频、精密测量等多方面的强大功能，已涉足众多的应用领域，如民用领域的汽车、船舶、飞机等运动物体的定位导航。在我国，拥有自主权的第一代卫星导航定位系统“北斗一号”已研发成功。导航定位系统地面接收机的射频前端电路通常的设计方法是采用分立元件或部分单片电路进行混合集成，存在体积大，成本高，不利于大批量生产，产品之间的参数离散性也较大等问题。

无线局域网以其灵活性、便捷性和高效性，在各行业逐步得到广泛应用，展示了极为广阔的市场前景。目前，全球无线局域网市场处在各种不同标准(IEEE

802.11a, IEEE 802.11b, IEEE 802.11g 和欧洲的 HiperLAN)相互竞争中走向统一的蓬勃发发展时代。目前市场上基于 802.11a 标准的商用芯片已经出现, 但这些芯片大多采用砷化镓和双极型硅工艺实现, 与后端基带采用的 CMOS 工艺不一致, 不利于集成。

以上各个应用领域的射频前端接收机系统, 都对低成本、低功耗和高容量提出了要求。但是长期以来, 射频前端芯片主要由分离元件或集成度低的射频芯片构成的, 不能满足目前射频集成电路的需求, 并且这些芯片一般都采用砷化镓(GaAs)、双极型硅(silicon bipolar)等工艺实现。GaAs 器件的电子迁移率高, 漂移速度快, 适于制作高速和微波器件, 但是 GaAs 晶圆片制备工艺比复杂, 因而成本较高。而数字基带处理部分通常采用低成本的标准 CMOS 工艺, 由于射频部分的 GaAs 工艺和基带部份的标准 CMOS 工艺不兼容, 所以不可能实现 SoC (System on Chip)。要想实现单片集成的收发器并最终实现单片全集成的 SoC 产品(即将射频, 中频, 基带全集成在同一块芯片上), 所以基带部分和射频部分必须选择一个相兼容的工艺。由于基带部分通常占到芯片面积的 75 %以上, 集成度及功耗等指标的要求使得不可能以 CMOS 以外的其他工艺实现, 所以改变基带部分工艺的可能性和可行性不大。虽然近年来随着深亚微米 CMOS 工艺的不断进步和成熟, 其沟道长度不断减小, 截止频率  $f_T$  不断增加, 噪声性能也在不断的改善, 但是由于 Si 材料自身的特点, 目前用 CMOS 工艺制作的射频集成电路仍然无法满足通信中愈来愈苛刻的射频前端指标的要求。在这种情况下, 基于 SiGe 的 BiCMOS 工艺应运而生。这种工艺是双极型硅(silicon bipolar)工艺和标准 CMOS 工艺的一种综合, 既可以提供射频性能可与 GaAs 器件相媲美的 SiGe HBT 器件, 又可提供标准的 CMOS 晶体管, 且制作工艺上与目前成熟的硅平面工艺相兼容, 而且其成本相对较低, 是实现全集成 SoC 的理想工艺选择。

由于基于 SiGe 的 BiCMOS 工艺具有工艺成熟、应用广泛、性能优越、价格低、集成度高、功耗小, 易于全集成等特点, 所以基于 SiGe 的 BiCMOS 工艺已成为近几年世界性范围内研究的热点, 世界各国的研究人员在基于 SiGe 的 BiCMOS 射频集成电路的设计和制作方面进行了大量的研究。美国许多成功的新兴集成电路无晶圆厂芯片设计公司(Fabless)都比较集中在这一领域。在 5GHz 以下, 基于 SiGe 工艺制造的射频集成电路, 在性能各方面已经能与 GaAs RFIC 一较长, 且在成本上具有明显的竞争优势, 在无线通讯、卫星定位导航、卫星广播电视等领域得到了广泛应用。

## 1.2 国内外动态

### 1.2.1 国外动态

在 SiGe 射频集成电路方面，国外已经取得了很大的突破。国外很多知名公司、大学和研究所已经用 SiGe 工艺实现了低噪声放大器(LNA)、压控振荡器(VCO)和混频器(Mixer)甚至是整个接收器(receiver)。

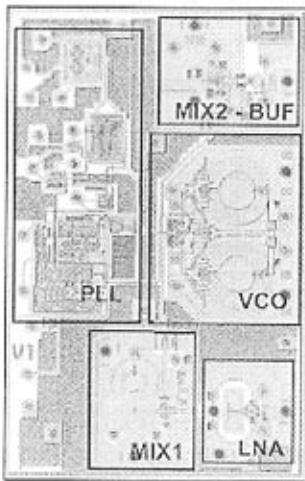

文献<sup>[3]</sup>报导的使用 SiGe HBT 在 12GHz 频带设计整个射频接收前端达到良好性能指标的 RFIC。该 RFIC 内含一个 LNA，两个混频器，一个 buffer，一个 VCO，一个 PLL，主要性能指标如下，工作频率 10.7GHz—12.75 GHz，增益 33.6dB，SSB 噪声系数 5.9dB，输出 IP3=16dBm，输出 1 dB 压缩点 5.5dBm，带内增益平坦度 5.5 dB，其中的 VCO 相位噪声在中心频率 5.3GHz 时为  $-102\text{dBc/Hz@100KHz}$ ，调制带宽为 1.1GHz。在 3.3V 的供电电压下功耗为 160mA，芯片如图 1-1 所示。

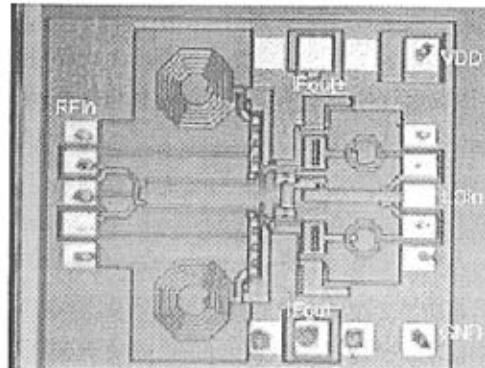

文献<sup>[4]</sup>报导的使用 SiGe HBT 工作在 18GHz 的有源双平衡混频器，工作频率在 18GHz，工作电压 3.3V，功率增益为 4.5dB，双边带噪声系数 7.1dB，输入三阶截断点 IIP3 为  $-1.0\text{dB}$ ，输出 1dB 压缩点为  $-12.2\text{dB}$ ，功耗为 16.5mW。芯片如图 1-2 所示。

图 1-1 12GHz DVB-S 接收前端

图 1-2 18GHz 有源双平衡混频器

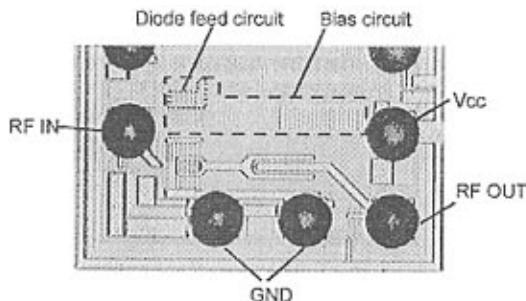

文献<sup>[5]</sup>报导的工作在 2.1GHz 的 SiGe HBT LNA 功率增益为 14.8dB，噪声系数 2.0dB，输入、输出反射系数分别为  $-8.2\text{dB}$ ， $-15.1\text{dB}$ ，输入 IP3 为  $0.2\text{dBm}$ ，输

出 1dB 压缩点为 4.5dBm。芯片如图 1-3 所示。

图 1-3 2.1GHz 低噪声放大器

另外文献<sup>[6]</sup>报导的 SiGe HBT 应用于设计混频器可以使其 3dB 带宽达到 20GHz；文献<sup>[7]</sup>报导的采用 SiGe HBT 设计的 VCO 可以工作在 40GHz 以上；文献<sup>[8]</sup>报导的采用 SiGe HBT 设计的功率放大器工作在 5GHz 以下时可以使输出功率达到 30dBm。

## 1.2.2 国内动态

国内的射频集成电路研究工作开展的比较晚，水平也比较低，但发展势头却很迅猛。近几年来采用 CMOS 工艺实现射频集成的研究工作在一些高校、研究所和公司中开展起来，主要研究单位有东南大学射频与光电集成电路研究所(射光所)、清华大学微电子系、复旦大学微电子学系、重庆西南集成电路设计中心、上海清华晶芯微电子、上海鼎芯半导体、华为海思半导体和广州广晟微电子等。

上海清华晶芯微电子有限公司首次在国内研制成功 2.4GHz 射频前端芯片组 CMOS 集成电路。此项目突破了 RFIC 产品设计的高难度障碍，填补国内空白，并为进入 3G 等众多的需要 RFIC 的无线通信领域奠定基础。它采用台积电 0.18  $\mu\text{m}$  RF CMOS 工艺，研制开发了可用于无线局域网的无线收发器完整射频集成电路芯片组。

清华大学微电子学研究所于 2002 年设计的低噪声放大器采用的差分结构<sup>[9]</sup>，测试结果表明工作在 2GHz 的时候噪声系数为 3.3dB，增益为 22dB。

东南大学射频与光电集成电路研究所利用 0.35  $\mu\text{m}$  CMOS 工艺，设计出了低噪声放大器等电路，是国内首次利用 CMOS 工艺设计的射频集成电路芯片<sup>[10]</sup>。在信息产业部电子十四所进行的芯片功能测试表明在 2.9GHz 的频率上功率增益大于 10dB，输入反射小于 -12dB，在 3V 电源下偏置电流为 8mA。这块工作频率高于 2GHz

的 CMOS 射频芯片其性能达到了当前世界上射频芯片的研究水平。

但目前国内基于 SiGe HBT 射频集成电路的发展却很缓慢。高校和研究所的研究方向主要集中于 SiGe 应变层的生长技术和微波 SiGe HBT 器件的制备，主要研究机构有清华大学、复旦大学、中国科学院半导体研究所、中科院微电子所和北京工业大学等十余家单位。对于 SiGe HBT 射频集成电路的研究主要有上海鼎芯半导体、华为海思半导体、广州广晟微电子这三家单位。

上海鼎芯半导体于 2004 年 12 月首次集成了用于 PHS（俗称小灵通）的全集成完整射频收发器 CL3110 和功率放大器芯片 CL3503，CL3110 采用低中频(10.8MHz)的架构，它内置 VCO 和小数分频 PLL，而且无须外置 SAW 滤波器，可以节约射频解决方案的整体成本。功放 CL3503 与 CL3110 配合，可以进一步降低成本，优化射频性能。CL3110 和 CL3503 分别采用 48 脚的 LGA 封装和 16 脚的 QFN 封装。

到目前为止高校中未见有基于 SiGe HBT 射频集成电路研究的报导。

### 1.3 本论文的主要工作

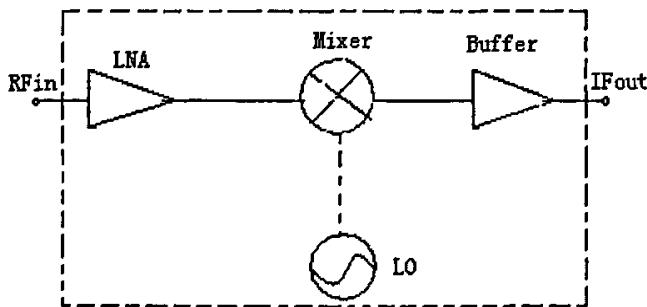

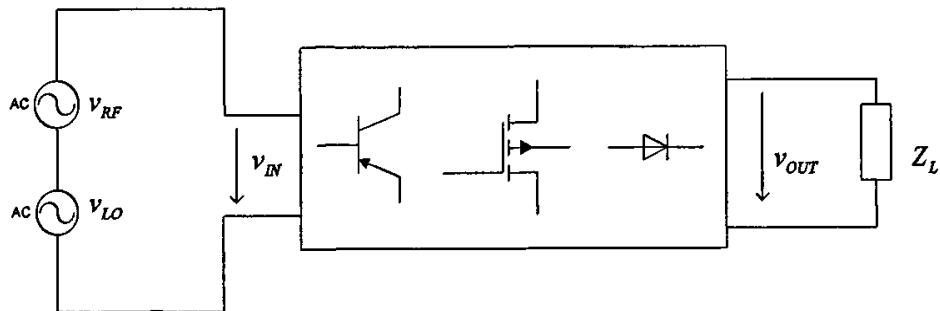

针对 Ku 波段数字卫星广播电视（DVB-S）系统的应用，本项目组设计了该系统的地面接收机的射频前端单片集成。该接收系统的设计采用采用外差结构，一次变频，工作频率为 12.25GHz-12.75GHz，其系统结构如图 1-4 所示。

图 1-4 射频接收前端单片集成结构图

本文在阅读大量相关文献的基础上，对低噪声放大器和混频器的原理进行了深入的分析和研究。并设计并实现其中的二个通用射频单元电路：

1. 低噪声放大器

2. 有源双平衡混频器

本文所设计的低噪放和混频器是目前国内首次采用基于 SiGe 的 BiCMOS 工艺

设计频率高于 10GHz 的射频集成电路，具有极大的设计挑战性，并取得了不错的仿真结果。本人主要完成了以下工作：

(1) 根据 Ku 波段 DVB-S 标准及射频前端电路的性能指标，明确了对低噪声放大器和混频器的设计要求，并据此收集相关文献资料。在对采用不同电路结构实现的低噪声放大器和混频器有了比较充分的了解之后，确定了所要设计的电路结构。

(2) 对低噪声放大器和有源双平衡混频器的性能指标，诸如噪声系数、线性度、增益、输入输出匹配进行了详细的分析，并得出了一些有指导意义的结论。

(3) 运用 Cadence SpectreRF 仿真工具对低噪声放大器和混频器进行电路仿真，设计电路。

(4) 运用 Virtuoso layout 版图工具设计和优化了低噪声放大器和混频器的版图，并用 Assura 和 Calibre 对版图进行了 drc (设计规则)、ant (天线效应)、density (金属密度)、softerc (电气规则)、stress (应力效应) 检查。

(5) 运用 Assura 和 Calibre 对版图进行了 LVS 检查(版图—原理图对照检查)，并运用 Assura 和 Calibre 中的参数提取工具提取了寄生参数，进行版图后仿真。

(6) 将版图数据生成为 GDS 文件，送往代工厂流片。

设计先从理论上分析射频集成电路低噪声放大器和混频器这两个单元电路开始，选择合适的工艺线，然后熟悉晶圆厂(Foundry)所提供的工艺文件以实现以上两个单元电路。考虑到第一次流片的风险性，决定选用以射频集成电路见长的国际著名代工厂 JAZZ 的  $0.35\mu m$  SiGe BiCMOS 工艺线。

## 第二章 JAZZ 0.35 $\mu$ m SiGe BiCMOS 工艺元件简介

### 2.1 元件模型与电路设计的关系

对于一个模拟射频集成电路设计者而言，首先必须要了解的是元件的特性、元件的制作过程，以及模型的建立，接下来才是在有限的元件中设计出符合指标要求的电路。由于工作频率的逐渐提高，过去可以忽略不计的杂散寄生效应在射频集成电路的设计中均会产生举足轻重的影响，因此在设计射频集成电路之初必须取得准确且完整的元件模型，才能设计出性能良好的射频集成电路。本论文电路设计采用美国 JAZZ 公司所提供的  $0.35\mu\text{m}1\text{P}4\text{M}$  SiGe BiCMOS 工艺设计与制作。该工艺有一层多晶层和四层金属层，第四层金属的厚度为  $3\mu\text{m}$ ，Via3 过孔的高度为  $2\mu\text{m}$ 。该工艺除了能提供 HBT,NMOS,PMOS,可变电容，无源巴仑，多晶电阻和 MIM 电容外还能提供高 Q 值的单端电感及差分电感。对应于最优化的偏置电流该工艺的 HBT 截止频率  $f_T$  可达到  $60\text{GHz}$ <sup>[11]</sup>。该工艺的应用目标为射频，模拟和数模混合集成电路，尤其长于射频集成电路的制造。

### 2.2 SiGe HBT

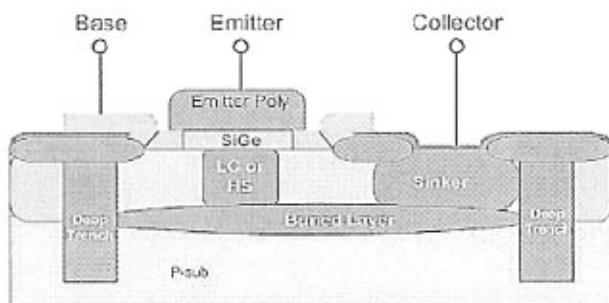

工艺提供了三种类型的 NPN HBT，分别是 digital/high speed,low voltage/standard,high voltage。三种类型晶体管的结构相差不大，如 0 所示：整个 NPN 管采用垂直结构制作，基区用 SiGe 参杂以获得优异的射频性能。

图 2.1 SiGe HBT 的结构

这三种 NPN HBT 的集电极反向击穿电压  $BVCEO$  和截止频率  $f_T$  如表 2-1 所示

表 2-1 NPN Specification by  $BVCEO$  and  $f_T$

|                      | $BVCEO(V)$ | $f_T(\text{GHz})$ |

|----------------------|------------|-------------------|

| digital/high speed   | 2.5        | 61                |

| low voltage/standard | 3.8        | 46                |

| high voltage         | 6          | 23                |

本设计采用的是截止频率最高的 digital/high speed NPN。NPN 晶体管元件在布局上采用多指交叉 (multi-finger) 的架构形式，目的在于减小基极电阻，降低噪声，提高晶体管面积的使用效率。

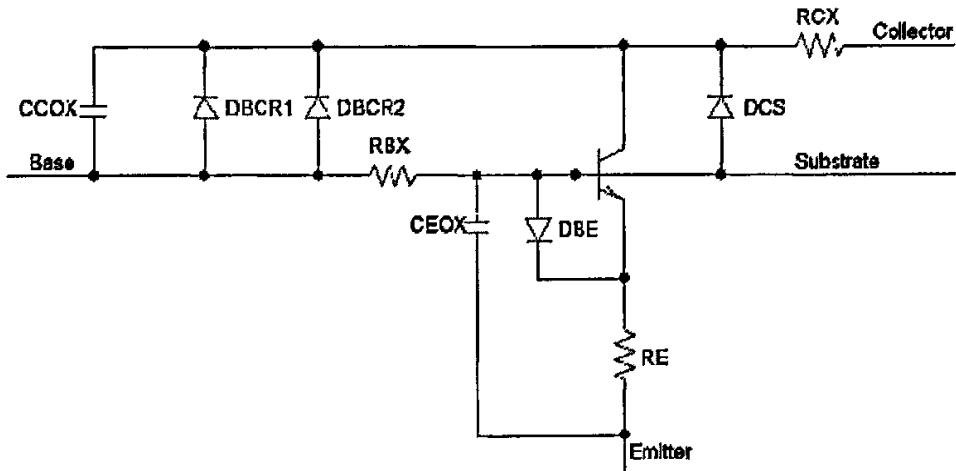

JAZZ 工艺库为 NPN 晶体管提供了 SGPM (Spice Gummel Poon Model) 和 HICUM(High Current Model)两种仿真模型。SGPM 是迄今为止最经典，稳定性和鲁棒性最好的双极型晶体管仿真模型，在小电流和高  $V_{be}$  的情况下有很高的仿真准确度。HICUM 模型在大电流下具有较好的适用性，但该模型目前还不够完善。考虑到所设计的低噪放和混频器均工作在小信号状态下，所以决定采用 SGPM 模型。

SGPM 模型电路如图 2-2 所示：

图 2-2 SGPM 模型等效电路

## 2.3 RF CMOS

JAZZ 提供了两种类型的 CMOS 晶体管，一种是应用于数字和模拟电路的普通晶体管，一种是应用于射频电路设计的晶体管。应用于数字和模拟电路的普通

MOSFET 采用经典的 BISM3v3 模型，这种模型在频率低于 200MHz 的频段内具有很高的准确性。如果工作频率高  $V_{ds}$  于 200MHz 就必须使用专门针对射频电路应用设计的 3.3V RF CMOS FET。3.3V RF CMOS FET 管子参数设置如表 2-2 所示：

表 2-2 3.3V RF CMOS FET 管子参数

| 模型名(Model name)                      | nfet_rf,pfet_rf                                    |

|--------------------------------------|----------------------------------------------------|

| 温度范围(Temperature range)              | -45°C -125°C                                       |

| 沟道长度(Channel Length)                 | 0.35μm <= L <= 0.8μm                               |

| 单指沟道宽度 (Single finger channel width) | 2μm <= W <= 15μm                                   |

| 指数(Number of fingers)                | 1 <= NF <= 25                                      |

| 偏置电压范围(Bias range)                   | $V_{gs}$ :0-3.3V, $V_{ds}$ :0-3.3V, $V_{bs}$ :0-3V |

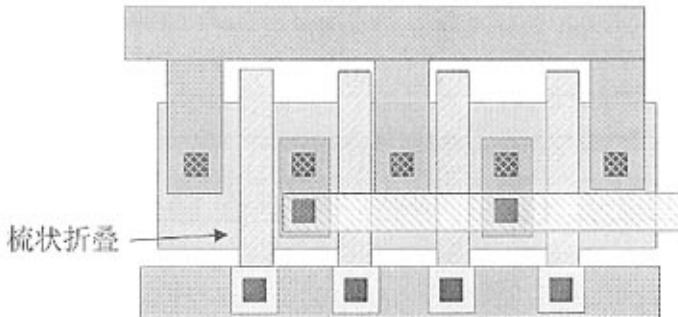

MOS 管的沟道宽度采用梳状结构，如图 2-3 所示。因此，沟道的总宽度为：W×N。梳状结构可以避免沟道宽度过大而造成沟道断裂；减小有源区的面积，从而减小芯片的总面积；并且可以使结构更加紧凑。

图 2-3 MOS 管有源区沟道的梳状结构

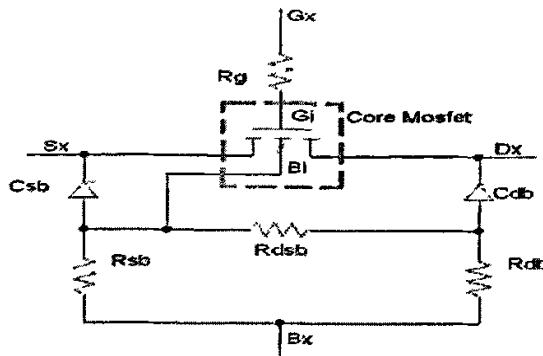

3.3V RF CMOS FET 的仿真模型采用增加了子电路的 BSIM3v3 模型。所谓增加了子电路的 BISM3v3 模型指的是用 BISM3v3 模型来模拟场效应晶体管的直流特性，并用加上了外接无源元件的 BSIM3v3 模型来模拟场效应晶体管高频时的交流效应，整体高频小信号模型在模拟的应用中可以被视为一个子电路的架构。如图 2-4 所示：

图 2-4 RF NMOS 等效电路模型

### 2.3 电阻

JAZZ 工艺提供了四种类型的电阻，分别是 rps,rnp3t,rph3t,rw3t,由于制作工艺的不同，这四种电阻的单位方块电阻及线性度均不相同，其中 rps,rnp3t,rph3t 是多晶电阻，rw3t 是阱电阻。这四种电阻的总结如表 2-3 所示

表 2-3 SBC35 电阻

| 电阻    | 描述         | 方块电阻值 (Ω) |

|-------|------------|-----------|

| rps   | 硅化多晶电阻     | 4.5       |

| rnp3t | 低阻值非硅化多晶电阻 | 100       |

| rph3t | 高阻值非硅化多晶电阻 | 1095      |

| rw3t  | 阱电阻        | 960       |

半导体基板掺杂区形成的阱电阻(N-Well resistance)，阻值较大，其不足之处是阻值不够精确，且温度系数大。另外，由于和衬底直接连接，与衬底的耦合电容较大，如果用于射频信号通路，会有很大的信号损耗。因此只能用于对电阻精度要求不高，且没有射频信号通过的直流电路中；多晶硅形成的多晶电阻(poly resistance)的阻值准确度高，线性度好，误差低，一般用于对电阻阻值要求精度高的偏置电路中。本设计中所用到的电阻均用于偏置电路，且阻值高，所以采用方块电阻值最高的 rph3t 电阻。电阻阻值的大小不仅与材料的电阻率有关，还与电阻的宽长比 (W/L) 有关，所以可以通过调整电阻的 L 与 W 以及串连或并联电阻指数 (fingers) 的不同来得到所需阻值的电阻。

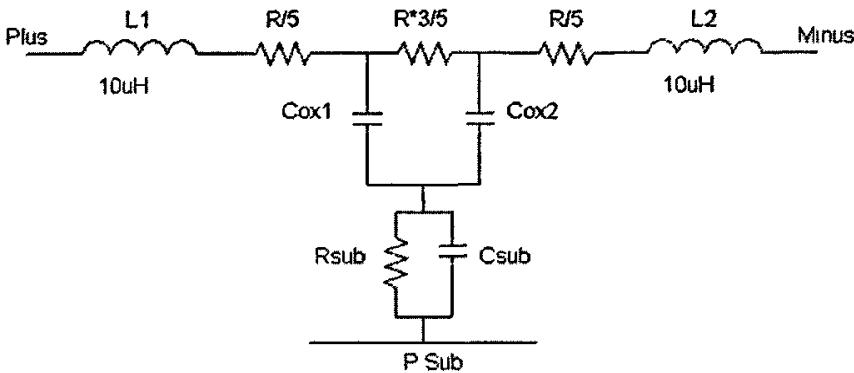

根据 JAZZ 的射频工艺库，可以把 rph3t 电阻等效为图 2-5：

图 2-5 rph3t 电阻等效电路模型

上图中,  $R$  为等效电阻,  $C_{ox1}$ 、 $C_{ox2}$  是氧化层电容,  $C_{sub}$  是衬底电容,  $R_{sub}$  是衬底电阻,  $L1$ 、 $L2$  是寄生电感。

$R$  的计算公式为:

$$R = \rho \frac{L + R_{end}}{W + \Delta W} \quad (2-1)$$

其中,  $\rho$  是方块电阻值,  $R_{end}$  和  $\Delta W$  是常数, 它们是由不同的电阻材料决定的。

## 2.4 MIM 电容

电容是另一类常见的无源元件, 在 CMOS 和 BiCMOS 工艺中, 常见的电容类型包括 pn 结电容、MOS 电容、MIM 电容、多晶硅电容和互连线电容等。

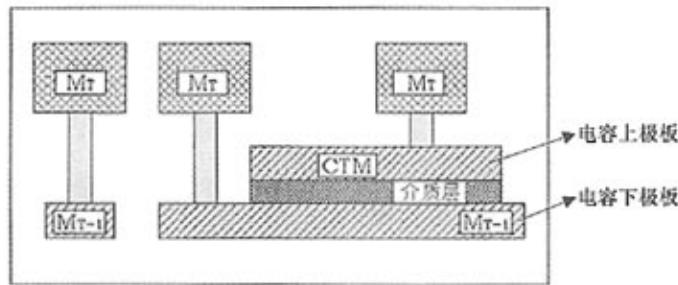

在射频集成电路中, 应用最广的电容是平板电容。其实, 所有的互连层都可以用来作为通常的平板电容, 然而, 普通的层间电介质比较厚(大约为 0.5-1  $\mu$ m), 大大减小了层间电容, 因此单位面积的电容很小。为了实现大容量的电容, 需要减小两个电容极板之间的距离, 通过在两层互连金属层之间插入特殊的金属层可以实现高密度的 MIM(Metal-Insulator-Metal) 电容, 其结构如图 2-6 所示。图中  $M_T$  和  $M_{T-1}$  是相邻的两层金属, 其中  $M_{T-1}$  作为电容的下极板; CTM(Capacitor Top Metal) 层是为制作 MIM 电容而插入的特殊金属层, 它作为平板电容的上极板。CTM 层和  $M_{T-1}$  层之间填充一层非常薄的介质层, 因此上下极板间的距离变的非常小, 大大增加了电容的密度, 同时寄生效应也很小。

MIM 电容的品质因数非常高, 温度系数值很低, 通常大约在 30-50 ppm/ $^{\circ}$ C 的范围内, 并且它主要取决于氧化物电介质本身的温度系数值。单位面积的总电容值还可以通过 MIM 电容的堆叠来加大。

图 2-6 MIM 电容图

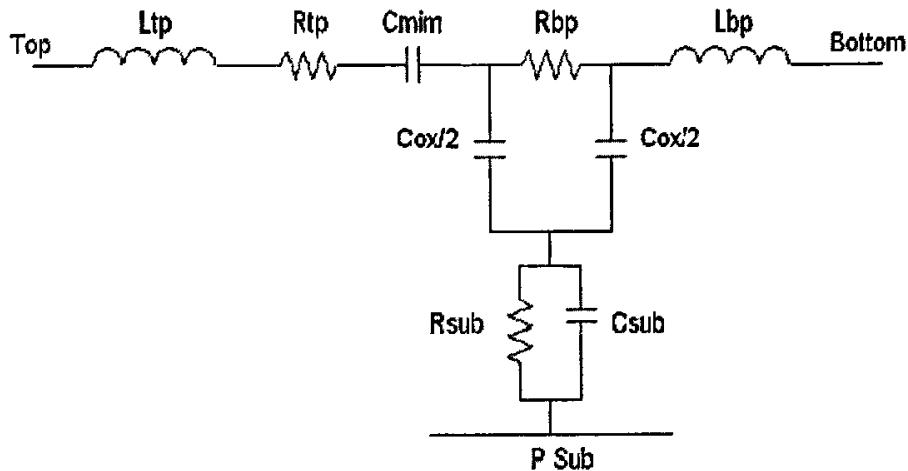

在JAZZ射频工艺库中提供了3种类型的MIM电容,分别是c3t\_mim, c3t\_mim2, c3t\_smim4。c3t\_mim,c3t\_mim2这两种电容介质位于金属2和金属3之间,金属2和金属3之间的单位电容值分别为 $1\text{fF}/\mu\text{m}^2$ , $2\text{fF}/\mu\text{m}^2$ 。c3t\_smim4这种类型的电容是堆叠MIM电容(stacked MIM capacitor),在金属2和金属3之间,金属3和金属4之间都有介质,金属2和金属4之间总的单位电容值为 $4\text{fF}/\mu\text{m}^2$ 。本设计采用频率特性和温度特性最好的c3t\_mim电容。我们也可以用一个等效电路来代替c3t\_mim MIM电容,等效电路如图2-7所示。

图 2-7 c3t\_mim MIM 电容模型

上图中,  $C_{mim}$  为 MIM 有效电容,  $C_{ox}$  是氧化层电容,  $C_{sub}$  是衬底电容,  $R_{sub}$  是衬底电阻,  $L_{tp}$ 、 $L_{bp}$  分别是顶层寄生电感和底层寄生电感,  $R_{tp}$  是顶层金属及过孔电阻,  $R_{bp}$  是底层电阻。

$C_{mim}$  的计算公式是:

$$C_{mim}=1\times 10^3 \cdot A_{ear} \times 10^{12} \text{ (pF)} \quad (2-2)$$

## 2.5 电感

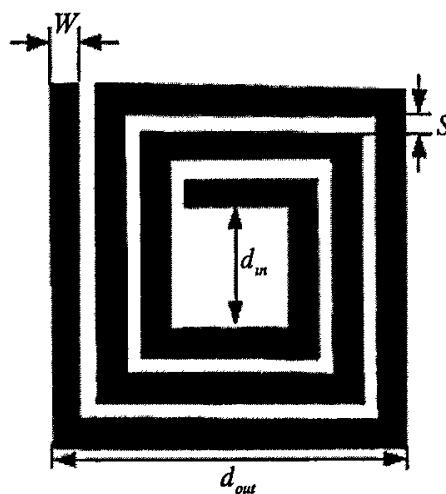

电感是射频集成电路中必不可少的元件，从射频集成电路的观点来看，不能制造出质量好的电感是至今标准IC工艺最明显的缺陷。尽管采用有源电路常常可以综合得到等效的电感，但它们比起“真正”的用几匝导线制成的电感，总是具有较高的噪声、失真以及功耗。在射频集成电路中，电感的实现方式有两种，即引线电感和片上螺旋电感。所谓引线电感，就是在芯片的两个压焊点之间或者压焊点与封装间焊接的金属线所形成的电感。引线电感的电感值和品质因数受引线长度、电阻率、直径的偏值影响波动较大，在工艺中很难控制，而且压焊点产生的寄生电容对射频电路影响很大。片上螺旋电感是利用CMOS工艺中的布线金属，在同一层绕圈形成磁通。片上螺旋电感面积较大，而布线金属下面的二氧化硅绝缘层厚度比较薄，因此，电感对地的寄生电容较大，导致自谐振频率较低。片上螺旋电感的电感值和Q值都是频率的函数。造成螺旋电感损耗的因素有金属的趋肤效应、衬底的位移电流损耗以及涡流损耗等。标准CMOS工艺硅衬底的高掺杂性，使线圈与衬底在高频时耦合强烈，衬底损耗大，同时与衬底间的寄生电容也很大。因此CMOS片上螺旋电感的Q值较低，通常在10以下。目前关于硅集成电感的研究主要在如何提高电感Q值上，而减小金属线串连电阻和硅衬底的损耗是主要的研究方向。常用的方法有用多层金属实现多层电感并联，用高电导率金属（例如，铜等）实现，以及用地屏蔽层隔离电感和衬底，以降低寄生电容等等。JAZZ射频工艺库中采用厚度最厚的第四层金属制作片上螺旋电感，不仅提供了单端金属螺旋电感，还提供了匹配性更好的差分金属螺旋电感。对于单端金属螺旋电感通过在有源区图案化的接地屏蔽（Patterned Ground Shields on Silicided Active）极大地减小了电感与衬底之间的信号泄漏和噪声耦合，提高了电感的品质因数。

图 2-8 给出了单端方形片上平面螺旋电感的结构。螺旋电感的电感值及品质因数由螺旋电感的内外线圈尺寸  $d_{in}$ ， $d_{out}$ ，螺旋线之间的间距 S，线宽 W，线圈匝数 N 决定。片上电感的电感量可以用以下公式计算

$$L = K_1 \mu_0 \frac{N^2 d_{avg}}{1 + K_2 \rho} \quad (2-3)$$

其中， $\rho = (d_{out} - d_{in}) / (d_{out} + d_{in})$ ， $d_{avg} = 0.5(d_{out} + d_{in})$ ， $K_1$ 、 $K_2$  与片上电感的版图有关，对于方形片上电感， $K_1$ 、 $K_2$  分别取 2.34 和 2.75。该表达式给出的结果与用电磁场分析方法得到的结果的典型误差在 (1~2) % 之间，一般不超过 3%。

图 2-8 单端方形金属螺旋电感

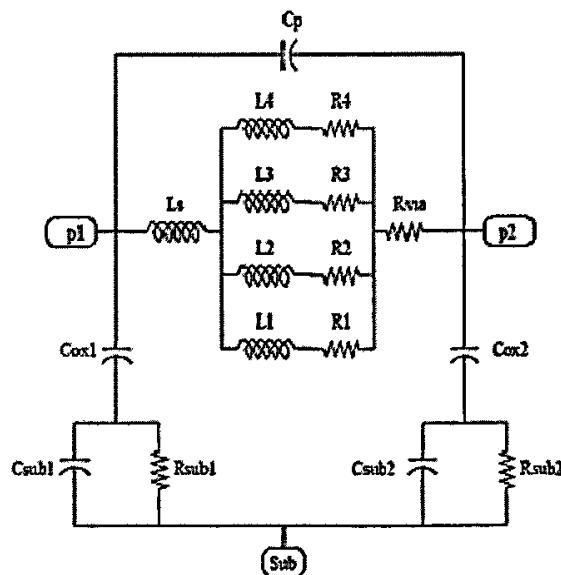

单端片上金属螺旋电感等效电路模型如图 2-9 所示。

图 2-9 单端片上金属螺旋电感等效电路模型

模型中的各个参数的含义如表 2-4 所示。

表 2-4 单端/差分电感模型参数含义

| 模型参数     | 参数含义                                          |

|----------|-----------------------------------------------|

| Csub     | 衬底电容                                          |

| Rsub     | 衬底电阻                                          |

| Cox      | 氧化层电容                                         |

| Cp/C1,C2 | 交叠电容(interwinding and cross-over capacitance) |

|       |                                       |

|-------|---------------------------------------|

| Rvia  | 过孔电阻                                  |

| Ls    | 串连电感                                  |

| R1-R4 | 梯形电阻元件 (Ladder resistance components) |

| L1-L4 | 梯形电感元件 (Ladder inductance components) |

| KK    | 互感                                    |

在 JAZZ 射频工艺库中, 线圈 N 为 1.5—8, 内半径 R 为  $25 \mu\text{m}$ — $200 \mu\text{m}$ ; 线间距 S 为  $2 \mu\text{m}$ ,  $2.5 \mu\text{m}$ ,  $3 \mu\text{m}$ ; 线宽 W 为  $2.6 \mu\text{m}$ — $28 \mu\text{m}$ ; 单端电感的取值可连续从  $0.138\text{nH}$  取至  $79.5\text{nH}$ 。JAZZ 射频工艺库中丰富的连续变化的电感取值给电路设计带来了极大的便利。

### 第三章 射频低噪声放大器设计

#### 3.1 射频的概念

众所周知，由于工作频率的日益提高，模拟和数字电路设计工程师们正在不断地开发和改进电路。用于无线通信的模拟电路工作在 GHz 波段。高性能的计算机、工作站，还有个人计算机，它们所用电路的时钟频率不断地增加。全球定位系统载波频率在 1227.60MHz 和 1575.42MHz 范围。个人通信系统中用的低噪声放大器工作 1.9GHz，在 C 波段的卫星广播包括 4 GHz 上行和 6 GHz 下行系统。一般说来，由于无线通信的快速发展，更紧凑的放大器、滤波器、振荡器和混频器电路正被设计出来并交付使用，通常这些电路的工作频率高于 1 GHz。

由于众多领域的应用，工程师们必须研究在宽频率范围工作的电路。这些年来，对频谱的分段已经进行了几次。第一次是由美国国防部在第二次世界大战期间和战后初期针对工业部门和政府机构提出的；而当今最通用的频谱分段法是由电气和电子工程师学会建立的，如表 3-1 所示<sup>[12]</sup>。射频频率范围通常是指从下表中的 VHF 波段到 S 波段。

表 3-1 IEEE 频谱图

| 频段       | 频率          | 波长           |

|----------|-------------|--------------|

| ELF(极低频) | 30—300Hz    | 10000—1000Km |

| VF(音频)   | 300—3000 Hz | 1000—100 Km  |

| VLF(甚低频) | 3—30KHz     | 100—10Km     |

| LF(低频)   | 30-300KHz   | 10—1Km       |

| MF(中频)   | 300-3000KHz | 1—0.1Km      |

| HF(高频)   | 3-30MHz     | 100—10m      |

| VHF(甚高频) | 30-300MHz   | 10—1 m       |

| UHF(特高频) | 300-3000MHz | 100—10cm     |

| SHF(超高频) | 3-30GHz     | 10-1cm       |

| EHF(极高频) | 30-300GHz   | 1-0.1cm      |

| 亚毫米波     | 300-3000GHz | 1-0.1mm      |

| P 波段     | 0.23-1GHz   | 130-30cm     |

| L 波段     | 1—2GHz      | 30-15cm      |

|       |             |             |

|-------|-------------|-------------|

| S 波段  | 2—4GHz      | 15-7.5cm    |

| C 波段  | 4—8GHz      | 7.5—3.75cm  |

| X 波段  | 8—12.5GHz   | 3.75—2.4cm  |

| Ku 波段 | 12.5—18GHz  | 2.4—1.67cm  |

| K 波段  | 18—26.5 GHz | 1.67—1.13cm |

| Ka 波段 | 26.5—40 GHz | 1.13—0.75cm |

| 毫米波   | 40—300 GHz  | 7.5—1mm     |

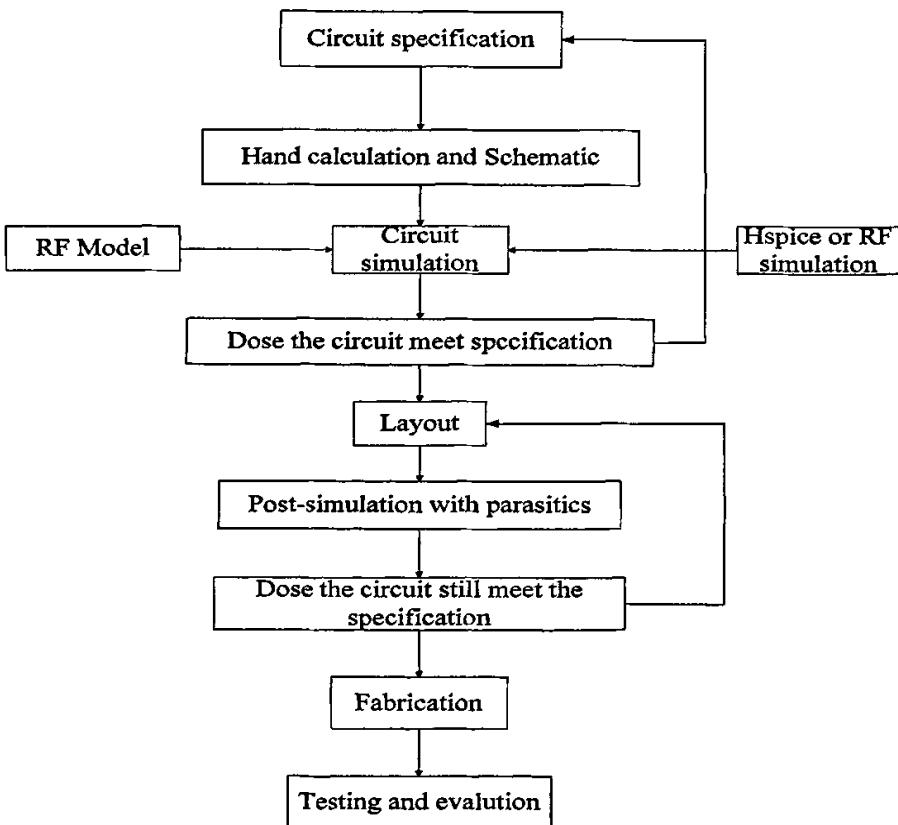

### 3.2 射频集成电路设计流程

射频集成电路由于低功耗、低成本和容易集成的优势而受到广泛的关注。目前对射频集成电路的设计主要局限在射频接收和发射系统子模块的研究，此方面的研究国外也刚刚起步，这对国内的 RFIC 行业是一个很好的发展契机。熟悉射频集成电路的设计流程可以正确地、高效地进行 RFIC 设计。图 3-1 是 RFIC 设计的流程图。

图 3-1 RFIC 设计流程图

### 3.3 集成低噪声放大器当前研究水平

射频接收机接收的信号是一个动态范围很大的信号。例如，对于GSM类型的接收机来说，其最小信号功率能小到-102dBm，而最大信号功率可以达到-15dBm。故接收机本身必须引入很小的噪声，同时接收机必须具有足够高的线性度。为了达到这样的要求，接收机的第一级通常为低噪声放大器，它的功能是在产生尽可能低噪声的前提下对射频信号进行放大以降低后面各级模块产生的噪声对信号的影响。低噪声放大器除了应该引入很少的噪声和提供足够高的增益外，还应该具有较高的线性度以避免非线性对信号质量的影响，另外，低噪声放大器的前级通常为分立的天线或者射频带通滤波器，由于天线和滤波器的传输特性与终端所接负载有很大关系，低噪声放大器的输入阻抗必须与天线或者滤波器实现阻抗匹配。在射频领域，该阻抗通常设定为一个统一的纯电阻值：50Ω。

随着现代无线通信应用的越来越广泛，使用的射频频率越来越高，带宽也越来越宽，要求芯片的功耗和成本越来越低，对RFIC的需求越来越多。基于GaAs的HEMT和HBT在过去占据了主要的应用领域，近年来由于BiCMOS技术和CMOS工艺的进步，更由于其低功耗、低成本的特性，使得COMS器件已经用于10GHz以上频率的RFIC设计。很多论文中的设计都使用了BiCMOS的SiGe HBT工艺，而且报道的此类LNA的噪声和增益特性都较好，噪声系数一般在4dB以下，增益在10dB以上。下表是对12GHz左右的LNA设计的一个归纳：

表 3-2 当前 LNA 研究水平

| 工艺             | 工作频率    | $S_{21}$ (dB) | NF(dB)  | $P_{1dB}$<br>(dBm) | $V_{dc}$<br>(V) | $I_{dc}$<br>(mA) | ref  |

|----------------|---------|---------------|---------|--------------------|-----------------|------------------|------|

| 0.18μm CMOS    | 3-6GHz  | 13-16         | 4.7-4.6 | -14                | 1.8             | 33               | [13] |

| 0.18μm CMOS    | 13 GHz  | 4.9           | 4.67    | -3                 | 1.8             | 5.4              | [14] |

| 0.18μm CMOS    | 24 GHz  | 13.1          | 3.9     | -12.2              | 1               | 14               | [15] |

| 0.13μm CMOS    | 20GHz   | 20            | 5.5     | -11                | 1.2             | 20               | [16] |

| 0.5μm SiGe HBT | 10.5GHz | 26            | 2       | na                 | 3.6             | 7.4              | [17] |

| 0.5μm SiGe HBT | 12 GHz  | 12            | 3       | na                 | 3.3             | 7.2              | [18] |

| SiGeHBT/50GHZ  | 16 GHz  | 8             | 4       | na                 | 1.5             | 5.3              | [19] |

|               |           |      |     |       |     |      |      |

|---------------|-----------|------|-----|-------|-----|------|------|

| 0.25μm BiCMOS | 4.5GHz    | 12.8 | 2.2 | -6.2  | 2   | 11.9 | [20] |

| 0.35μm BiCMOS | 3-10.6GHz | 10   | 5   | -15.8 | 1.5 | 3.6  | [21] |

| 0.35μm BiCMOS | 5-6GHz    | 17   | 2.3 | -18   | 3.3 | 4    | [22] |

| 0.25μm BiCMOS | 16GHz     | 14.5 | 3.8 | -10.5 | 1.5 | 1.5  | [23] |

### 3.4 低噪声放大器设计基本理论

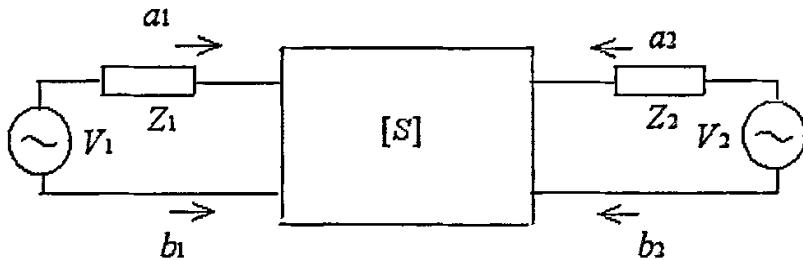

#### 3.4.1 散射参数

在绝大多数涉及射频系统的技术资料和数据手册中，经常用到散射参数(S参数)。其原因在于实际射频系统不能再采用终端开路、导线形成短路的测量方法。采用导线形成短路的时候，导线本身存在电感，而且其电感量在高频下非常之大，此外，开路情况也会在终端形成负载电容。另外，当涉及到电磁波传播时也不希望反射系数的模等于1，在这种情况下，终端的不连续性将导致有害的电压、电流反射，并产生可能造成器件损坏的振荡。S参数描述了两端口入射功率和反射功率之间的关系，而不是电压和电流的关系。应用S参数测量和校准都变得容易。

图 3-2 二端口网络 S 参数

图 3-2 描述了一系统被  $V_1$  和  $V_2$  激励， $a_1$ ， $a_2$  和  $b_1$ ， $b_2$  分别表示输入和输出口的入射波、反射波功率。假定系统是线性的，S 参数定义<sup>[24]</sup>：

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix} \quad (3-1)$$

式中  $[S] = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix}$  称为双端口网络的散射矩阵，简称为  $[S]$  矩阵，它的各参数的意义如下：

$$S_{11} = \left. \frac{b_1}{a_1} \right|_{a_2=0} \quad \text{表示端口 2 匹配时, 端口 1 的发射系数} \quad (3-2a)$$

$$S_{22} = \left. \frac{b_2}{a_2} \right|_{a_1=0} \quad \text{表示端口 1 匹配时, 端口 2 的发射系数} \quad (3-2b)$$

$$S_{12} = \left. \frac{b_1}{a_2} \right|_{a_1=0} \quad \text{表示端口 1 匹配时, 端口 2 到端口 1 的反向传输函数} \quad (3-2c)$$

$$S_{21} = \left. \frac{b_2}{a_1} \right|_{a_2=0} \quad \text{表示端口 2 匹配时, 端口 1 到端口 2 的正向传输函数} \quad (3-2d)$$

在射频/微波频段上, 与端口的开路、短路条件相比, 端口的匹配比较容易实现, 在端口匹配条件下进行测试也比较安全。

### 3.4.2 噪声

噪声因子描述了一个电路引入噪声的大小, 它的值是输入信噪比与输出信噪比的比值。通常可以表示为:

$$F = \frac{Ns + N_i}{Ns} = 1 + \frac{N_i}{Ns} \quad (3-3)$$

其中,  $N_s$  是信号源在输出端引入的噪声,  $N_i$  是电路本身产生的噪声。

在工程中, 通常习惯上使用噪声系数 (NF) 来作为一个系统噪声性能的衡量指标, 噪声系数是用分贝表示的噪声因子。一般二端口网络的噪声系数定义为输入端信号噪声比 (SNR) 除以在输出端信号的信号噪声比。

$$NF(dB) = \frac{(SNR)_m}{(SNR)_{out}} \quad (3-4)$$

其中,  $(SNR)_m = S_m / N_m$  表示输入端的信号功率和噪声功率之比,  $(SNR)_{out} = S_{out} / N_{out}$  表示输出端的信号功率和噪声功率之比。

其物理含义是: 信号通过放大器后, 由于放大器本身产生的噪声, 使信噪比恶化, 信噪比下降的倍数就是噪声系数。

理论证明, 对于一个二端口网络, 其噪声因子可表示成式(3-5)

$$F = F_{min} + \frac{R_s}{G_s} [(G_s - G_{opt})^2 + (B_s - B_{opt})^2] \quad (3-5)$$

其中

$$F_{\min} = 1 + 2R_n [G_{opt} + G_c] = 1 + 2R_n \left[ \sqrt{\frac{G_u}{R_n}} + G_c^2 + G_c \right] \quad (3-6)$$

$$B_{opt} = -B_c \quad (3-7)$$

$$G_{opt} = \sqrt{\frac{G_u}{R_n} + G_c^2} \quad (3-8)$$

式中, ( $G_c$ ,  $B_c$ ,  $R_n$  和  $G_u$ ) 是二端口网络的四个噪声参数, 取决于晶体管的材料、结构和工艺。 $F_{\min}$  是晶体管的最小噪声系数, 是由管子本身决定的;  $R_n$  代表网络噪声电压大小的等效电阻;  $G_s$  和  $B_s$  是信号源的电导和电纳;  $G_{opt}$  和  $B_{opt}$  是最佳源电导和电纳。

在原理上, 我们可以通过采用由四个噪声参数  $G_c$ ,  $B_c$ ,  $R_n$  和  $G_u$  定义的最优信号源阻抗来得到一个给定器件的最小噪声系数。在分立元件电路设计中, 由于晶体管的特性是固定的, 所以使噪声系数最小的信号源阻抗一般不同于使功率增益最大的信号源阻抗值。因此有可能在增益较低、输入匹配较差的情况下却能得到一个好的噪声系数。此外, 功耗在许多应用中是一个重要的考虑因素, 但经典的用于分立电路设计的噪声优化方法恰恰完全忽略功耗。但是在集成电路设计中, 设计者却可以充分地利用他们设计器件几何尺寸的自由度, 根据需要调整晶体管的几何尺寸, 从而实现增益、输入阻抗、噪声系数以及功耗之间的均衡, 在功耗允许的范围之内实现最小噪声和最大功率增益的同时匹配。

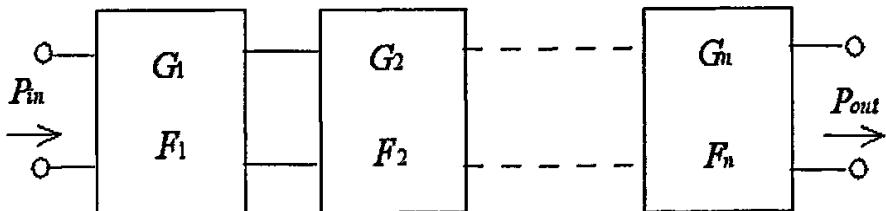

图 3-3 多级放大器级联

当系统中有多级放大器级连时(图 3-3), 其噪声系数表达式为:

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots \quad (3-9)$$

式中  $F$  表示多级放大器总的噪声系数;  $F_1$ 、 $F_2$  和  $F_3$  分别表第一、第二和第三级的噪声系数;  $G_1$  和  $G_2$  分别表示第一和第二级放大器的功率增益。从式(3-9)可知, 要

使整机的噪声低，必须使  $F_1$  尽量低，前级增益  $G_1$  和  $G_2$  足够大。

### 3.4.3 增益

放大器功率增益有多种定义，如实用功率增益、共轭增益等。对于实际的低噪声放大器，功率增益通常是指信源和负载都是  $50\Omega$  情况下实测的增益。其表达式为放大器输出功率与输入功率的比值：

$$G = \frac{P_{out}}{P_{in}} \quad (3-10)$$

提高低噪声放大器的增益对降低整机的噪声系数非常有利，但低噪声放大器的增益过高会影响整个接收机的动态范围。所以，一般来说低噪声放大器的增益确定应与系统的整机噪声系数、接收机动态范围等结合起来考虑。根据经验，一般取值在  $15\text{dB}$  至  $20\text{dB}$  较为合适。

### 3.4.4 稳定性

放大器电路必须满足的首要条件之一是其在工作频段内的稳定性。这一点对于射频电路是非常重要的，因为射频电路在某些工作频段和终端条件下有产生振荡的趋势。这是由于晶体管内部都存在反馈，S 参数的  $S_{12}$  就表示内部反馈量，它是电压波的反向传输系数。 $S_{12}$  越大，内部反馈越强，当反馈达到一定强度时，就会变为正反馈，引起放大器的稳定性变化，甚至产生自激。一个晶体管的射频绝对稳定条件是<sup>[25]</sup>：

$$\left\{ \begin{array}{l} k = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}||S_{21}|} > 1 \\ 1 - |S_{11}|^2 > |S_{12}||S_{21}| \\ 1 - |S_{22}|^2 > |S_{12}||S_{21}| \end{array} \right. \quad (3-11)$$

其中  $|\Delta| = |S_{11}S_{22} - S_{12}S_{21}|$

K 为稳定性判别系数，只有当式(3-11)中的 3 个条件都满足时，才能保证放大器是绝对稳定的。

### 3.4.5 线性度与大信号性能

除了噪声系数、增益以及输入匹配而外，线性度是一个重要的考虑，因为一个LNA不只是必须不附加太多的噪声来放大信号，它还必须甚至在接收强信号时也能保持线性。特别是在存在很强干扰信号情况下接收一个弱信号时，LNA必须保持线性工作；否则就会出现各种问题。这些交调失真的后果包括灵敏度降低（也称为阻塞）和交叉调制，阻塞发生在当强干扰引起的交调乘积项“淹没”了所要接收的弱信号，而交叉调制则发生在当非线性的相互作用把一个信号的调制传给另一个信号的载波时。显然这两种影响都不是所希望的，所以LNA设计者的另一个责任是把交调失真减小到可接受的程度。

## 3.5 低噪声放大器电路设计

低噪声放大器通常是接收机的第一级，其设计要综合考虑到很多指标，如：增益、噪声、功耗、阻抗匹配、稳定性和线性度等。它必须在一定的功耗条件下，提供足够的增益、优异的噪声性能、良好的线性度和输入输出匹配。足够的增益可以抑制后续级模块的噪声；优异的噪声性能几乎决定了整个接收机的噪声性能的优越程度；良好的线性度可以使它在较大的信号动态范围内正常工作。由于LNA的最主要的作用是降低整个接收机的噪声，那么噪声优化是低噪声放大器设计中最关键的步骤。传统射频微波分立电路有源器件的尺寸都是固定的，其输入匹配电路是按噪声最佳而设计，其结果必然偏离最佳共轭匹配状态，导致输入失配和过多的功率消耗。而现今的RFIC设计者，在一定的功耗和增益条件下可以调节有源器件的几何尺寸（发射极长度，基极指数等）、选择不同的匹配模式和调整偏置状态，以使最佳噪声匹配点尽可能地和 $S_{11}$ 的共轭接近，即可以同时达到最佳噪声匹配和最大功率传输匹配。

### 3.5.1 电路拓扑结构的选择

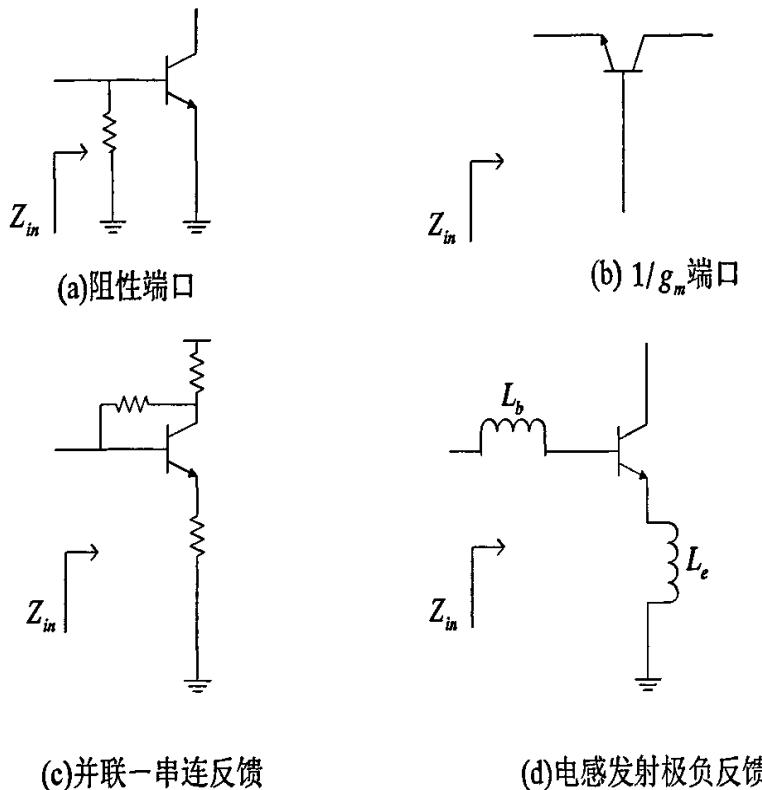

低噪声放大器通常有以下几种结构<sup>[26]</sup>：阻性端口、 $1/g_m$ 端口、并联一串联反馈、电感发射极负反馈，如图3-4所示。阻性端口使用电阻来实现阻抗匹配，这个电阻不但会产生热噪声，而且会削弱输入信号（衰减因子为2），这两种效应合在一起一般都会产生不可接受的高噪声系数。 $1/g_m$ 端口这种结构使用共基放大级的源端作为输入端口，由于从信号源终端看进去的放大器的输入阻抗为 $1/g_m$ （这也

是这种结构名称的来历），因此合适地选择器件的尺寸和偏置电流可以在很宽的频带范围内提供所希望的 $50\Omega$ 的电阻。但是在高频下，各种寄生效应和晶体管发射极所接偏置阻抗引入的噪声都会降低放大器的噪声性能。在某些性能要求不高的应用中，这种结构的放大器可以作为低噪声放大器来使用。并联一串联反馈结构则使用电阻并联和串联反馈来设置LNA的输入阻抗和输出阻抗，这种结构相对于阻性端口结构来讲，由于在放大之前没有含噪声的衰减器使信号减小，所以它的噪声系数会比阻性端口结构明显要好，但电阻反馈网络仍然会产生它自己的热噪声，并且也不能在所有的频率下对晶体管表现为等于 $Z_{opt}$ 的阻抗。结果，这种结构的放大器的噪声系数虽然一般要比阻性端口结构的放大器好得多，但一般仍超出器件 $F_{min}$ 几个分贝。然而这一电路结构能够提供宽带实数输入阻抗，所以在本质上是宽带放大的，所以在某些对噪声性能要求不是很高的宽带应用（如UWB系统）中，这类放大器得到广泛应用。电感发射极负反馈这种结构是目前应用最广的低噪声放大器结构，它是一种窄带放大器，利用发射极负反馈电感来得到具有正实部的输入阻抗，并可在功耗受限的情况下得到较优的噪声性能。如图3-4(d)所示， $L_e$ 为发射极反馈电感，它在晶体管基极引入一个实部阻抗，提供输入阻抗的实部， $L_b$ 与 $L_e$ 之和与 $C_{be}$ 谐振，使得输入阻抗的虚部为0，从而实现阻抗匹配。由于LC谐振只发生在有限的频带宽度内，因此这种结构的放大器是窄带放大器。由于理想电感并不引入额外的热噪声，同时通过合理的设计，可以在功耗受限的情况下做到近似的噪声匹配（ $Y_s = G_{opt} + jB_{opt}$ ），取得接近 $F_{min}$ 的噪声性能。另外，对于每种结构，还有单端输入和差分输入的区别。差分输入的电路结构复杂、功耗较大，但可以抑制共模噪声。

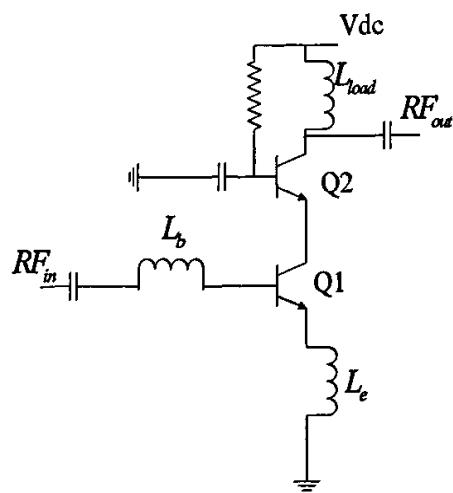

为了简化电路设计、降低流片风险，并考虑到测试设备不能提供射频差分信号的实际限制，本设计采用单端电感发射极负反馈的共射共基电路结构（Cascode结构），这种电路结构如图3-5所示，在电感发射极负反馈共射级之上层叠了一个共基级放大器。为了减小晶体管的Miller效应和有限输出阻抗对放大器性能的影响，并提供良好的反向隔离性能，低噪声放大器通常都采用这种共射共基结构。在图中，Q1是共射级放大管， $L_b$ 、 $L_e$ 与Q1提供匹配的输入阻抗，并将输入功率信号转化为电流信号；Q2是共基级晶体管，它可以提高放大器的输出阻抗，使得放大器的负载阻抗完全由负载网络来决定；共基级晶体管给共射级放大管提供了一个低阻抗负载，使得放大管的增益比较低，降低了放大管Miller效应对放大器性能的影响；共基级晶体管还提高了反向隔离性能，减弱了本地振荡信号的泄漏，同时使放大器成为一个单向化放大器，使得设计方程大大简化，极大地提高了放大

器的稳定性。

图3-4 低噪声放大器四种结构

图3-5 共射共基低噪声放大器

### 3.5.2 设计指标

具体的设计指标如下：

|                    |                   |

|--------------------|-------------------|

| 频率范围               | 12.25GHz—12.75GHz |

| 电源电压               | 3V                |

| 噪声系数               | <4dB              |

| 输入 1dB 压缩点         | >-22dBm           |

| 输入 IP3             | >-12dBm           |

| 增益 ( $S_{21}$ )    | >15dB@12.5GHz     |

| 输入匹配 ( $S_{11}$ )  | <-10dB@12.5GHz    |

| 输出匹配 ( $S_{22}$ )  | <-10dB@12.5GHz    |

| 反向隔离度 ( $S_{12}$ ) | <-30dB@12.5GHz    |

### 3.5.3 完整 LNA 电路结构图

图 3-6 实际电路仿真拓扑结构

实际仿真时单端低噪声放大器的电路拓扑结构如图3-6所示。理想电感本身不会产生噪声，采用这种结构进行输入阻抗匹配可以取得良好的噪声性能。晶体管Q1和Q2级联在一起可以改善输入级和输出级的隔离度。 $L_b$ 、 $L_e$ 与Q1提供匹配的输入阻抗；Q3和Q1组成电流镜用于偏置输入端口；电阻 $R_4$ 要取足够大的阻值以减小偏置电路的噪声电流；电阻 $R_1$ 用来调节输入级晶体管Q1的发射结电压和发射

极电流以决定静态功耗；为了增加电压余度，负载采用电感；负载  $L_{load}$  与  $V_{dc}$  间接旁路电容C，起保护电源，稳定电源电压的作用。

### 3.5.4 输入级晶体管的设计

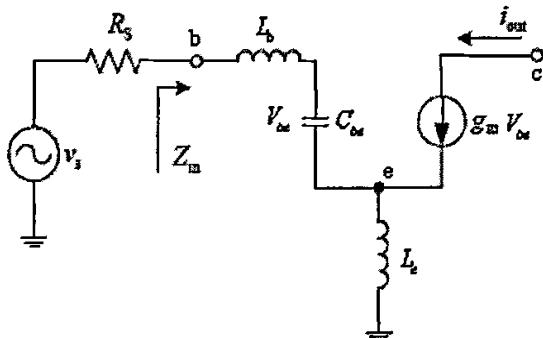

在经典的分立元件低噪声放大器设计中，晶体管达到最小噪声匹配时的最佳信号源反射系数和  $S_{11}^*$  ( $S_{11}$  的共轭) 在圆图上有一定的距离，而一般低噪声放大器的输入匹配电路是按照噪声最小来设计的，这必然导致输入端口的失配，反射增大而损耗过多的射频功率。在射频集成电路设计中，可以调节器件的几何尺寸使最佳噪声匹配点和  $S_{11}^*$  尽可能的接近，即尽可能地同时实现共轭匹配和最小噪声匹配。本文先分析了加发射级负反馈电感晶体管的输入阻抗。图 3-7 是输入级晶体管的等效电路， $L_e$  是发射极反馈电感， $L_b$  是基极电感， $C_{be}$  是基极一发射极电容。

图 3-7 发射极电感负反馈共射放大器小信号模型

输入阻抗

$$Z_{in} = s(L_e + L_b) + \frac{1}{sC_{be}} + \frac{g_m}{C_{be}} L_e \quad (3-12)$$

调节发射极反馈电感值和基极输入匹配电感值，使得

$$s(L_e + L_b) + \frac{1}{sC_{be}} = 0 \quad (3-13)$$

即当  $L_b$  与  $L_e$  之和与  $C_{be}$  谐振时

$$Z_{in} = \frac{g_m}{C_{be}} L_e = \omega_T L_e \quad (\omega_T = \frac{g_m}{C_{be}}) \quad (3-14)$$

谐振频率

$$\omega_o = \frac{1}{\sqrt{(L_e + L_b)C_{be}}} \quad (3-15)$$

选择合适的  $L_e$  和  $L_b$  的大小，就可以在谐振频率  $\omega_o$  处  $Z_m = \omega_o L_e = 50\Omega$ ，其中  $\omega_o$  为晶体管截止频率。

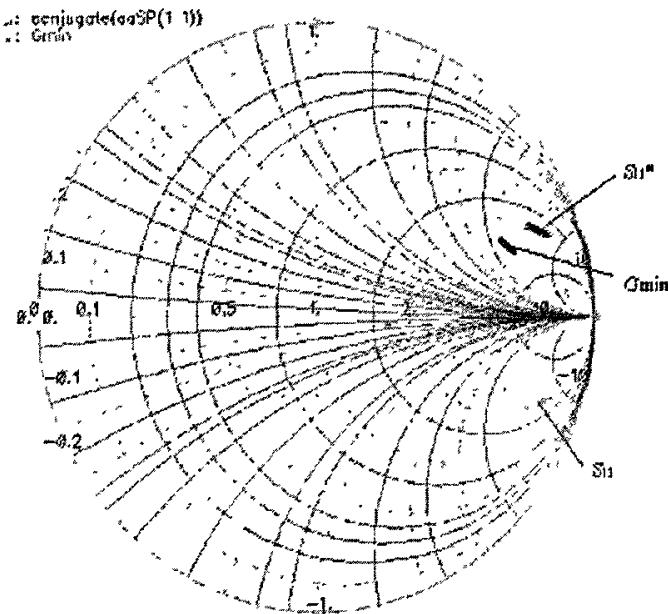

依据公式(3-14)，选定发射极反馈电感  $L_e$ ，使得  $Z_m = \omega_o L_e = 50\Omega$ ，然后再调节 Q1 发射极长度和并联的基极指数，使得最佳噪声匹配点  $G_{min}$  和  $S_{11}^*$  尽可能地接近。当发射极长度增加时，最佳发射极电导和电纳都增加，反映在圆图上为  $G_{min}$  向左移，同时  $S_{11}^*$  也随之变化。电流随着器件发射极长度的增加而增加；对于固定的发射级电流来说，降低基极偏置电压可以选用更大尺寸的晶体管。调节过程中由于  $L_e$  的值受到限制（JAZZ 工艺库中单端电感最小值为 0.138nH），最佳噪声匹配和  $S_{11}^*$  总相隔有一定的距离，如果过多的考虑最佳噪声匹配点和  $S_{11}^*$  接近，将导致增益的降低，所以说必须在两者之间作折衷。图 3-8 是最后得到的最佳噪声反射系数曲线、 $S_{11}$  和  $S_{11}^*$  的 smith 圆图。可以看出， $G_{min}$  和  $S_{11}^*$  相距较近，这样折衷可以实现匹配为最佳噪声匹配的时候，与共轭匹配也相距不远，端口驻波比和噪声系数同时满足设计要求。

图 3-8 噪声匹配和共轭匹配圆图

### 3.5.6 偏置电路的设计

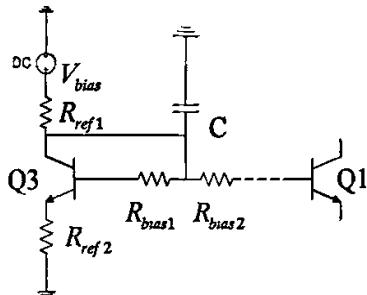

输入级偏置电路结构如图 3-9 所示：

图 3-9 输入级偏置电路

$R_{ref1}$ 、 $R_{ref2}$  和  $Q3$  共同确定偏置电路的直流电压，其主要工作原理与电流镜电路相同。目的是提供准确的直流电压，其电压值直接对应放大管  $Q1$  的直流偏置电压，对电路的噪声、增益及功耗都有较大影响。偏置电路采用的镜像恒流源电路与普通的恒流源电路不同的是，镜像的共基极之间有一个大电阻  $R_{bias}$ 。 $R_{bias}$  的阻值在 10K 以上，目的是减小偏置电路的噪声电流，而且采用对噪声影响较小的多晶（Poly）电阻。 $R_{ref1}$ 、 $R_{ref2}$  的选择要经过优化， $R_{ref1}$  电阻阻值相对较大，选择电阻宽度较大（经验值  $W \sim 1\mu m$  较佳）的电阻，且通过多个大电阻并联或小电阻串连来实现所需的电阻值，以尽量减少工艺偏差及温度变化引起的电阻阻值的变化。为尽量减小偏置电路的功耗， $Q3$  的发射极长度一般选为  $Q1$  的几分之一，本设计中为四分之一。

### 3.5.7 共栅级及负载设计

共基级相对于共射级来说，虽然对整体噪声系数影响较小<sup>[27]</sup>，但也必须认真设计。两个相互冲突的考虑限制了共基级晶体管尺寸的选择。基极—发射极的重叠电容可能会显著地减小从  $Q1$  的基极和集电极看进去的阻抗，使  $Q1$  的噪声性能和输入匹配都变差。另外，为了抑制密勒效应的影响，通常希望有一个较大的共基级器件以减小共射级晶体管的增益，但是大尺寸的共基级晶体管的发射极寄生电容会较大，这个大寄生电容在高频时可以显著地增加共基级本身内部噪声的放大作用。所以共基级的设计要折衷考虑<sup>[28]</sup>。负载采用电感，该电感与  $Q2$  集电极对地的寄生电容，输出负载电容和负载电阻并联谐振在工作频率上，提供一个极大的输出阻抗以得到较大的增益。

### 3.5.8 稳定性的考虑

放大器的设计都要考虑到稳定性，为了保证放大器在工作频带12.25GHz-12.75GHz 稳定工作，必须在一个很宽的频率范围内进行扫描，使稳定性因子K在一个很宽的频带范围内都大于1。

最终，图3-6中各元件的参数值如表3-3所示：

表 3-3 LNA 电路中元件参数

|               |                    |

|---------------|--------------------|

| Q1            | dn452 L=8 $\mu m$  |

| Q2            | dn452 L=13 $\mu m$ |

| Q3            | dn121 L=2 $\mu m$  |

| $R_1$         | 2.2K $\Omega$      |

| $R_2$         | 18.75 $\Omega$     |

| $R_3$         | 55.5K $\Omega$     |

| $R_4$         | 9.1K $\Omega$      |

| $R_5$         | 1K $\Omega$        |

| $L_e$         | 0.168nH            |

| $L_b$         | 0.7nH              |

| $L_{load}$    | 0.7nH              |

| $C_1$ 、 $C_2$ | 5pF                |

| $C_3$         | 1pF                |

| $C_{load}$    | 70fF               |

| $V_{dc}$      | 3V                 |

| $V_{bias}$    | 3V                 |

## 3.6 低噪声放大器版图设计

集成电路的版图定义为制造集成电路时所用掩模上的几何图形。这些几何图形包括如下几层：n阱、有源区、多晶硅、 $n^+$ 和 $p^+$ 注入、接触孔以及金属层。虽然每个晶体管的宽度和长度是由电路设计决定的，但版图中其它大多数尺寸都要受“设计规则”的限制。设计规则就是不管制造工艺的每一步出现什么样的偏差都能保证正确制造晶体管和各种连接的一套规则。大部分规则都可以纳入以下四种规则之一<sup>[29]</sup>。

1. 最小宽度。掩模上定义的几何图形的宽度(和长度)必须大于一个最小值，该值由光刻和工艺的水平决定。

2. 最小间距。在同一层掩模上，各图形之间的间距必须大于最小间距，在某些情况下，不同的掩模图行的间距也必须大于最小间距。

3. 最小包围。 $n$  阵和  $p^+$  注入区在环绕晶体管时均应有足够的余量，以确保即使在出现制造偏差时器件部分始终在  $n$  阵和  $p^+$  注入区里面。

4. 最小延伸。有些图形在其它图形的边缘外还应至少延长一个最小长度。

版图设计及优化是射频集成电路设计的一个重要步骤。设计拙劣的版图可能导致测试结果与电路仿真结果的较大差异，甚至是芯片不工作。在版图布局设计中，必须考虑电磁兼容(EMC)原则，主要体现在以下一些方面<sup>[30]</sup>：

1. 版图设计中将输入、输出信号分别安排在芯片两侧对称分布，形成单方向信号通路，可增加输入输出隔离度，避免信号回路产生的耦合。

2. 射频输入输出焊盘(PAD)采用标准的地-信号-地(G-S-G)或地-信号-地-信号-地(G-S-G-S-G)的共面波导的结构。

3. 尽量采用顶层金属走射频信号，底层金属(M1)和衬底大面积接地，这样可以屏蔽来自衬底的噪声干扰，同时减少由寄生电容引起的耦合损耗。对于直流信号，焊盘采用多层金属，可以保证一定的电流量。

4. 射频信号线线宽要适中。太宽，对地的寄生电容很大，射频信号泄漏严重；太窄，信号线寄生电阻大而且电流承载能力会很低。在线宽要适中的前提下，信号走线要尽量短，可以减小串联寄生电阻、电感和对地寄生电容。

5. 对有两个或多个电感的电路，各电感之间要用接地的顶层金属作隔离墙，以减小各电感之间的互感。

6. 元器件的四周最好采用接地的金属一层包围起来，这样可以将器件屏蔽以减小外界对它的干扰，但是需要在接地圈上凿出开口以防止其形成闭合回路，因为闭合回路会产生电流涡流而对电路造成影响。

7. 版图中需要放置尽量多的衬底接触孔，以使衬底近似于干净的地。

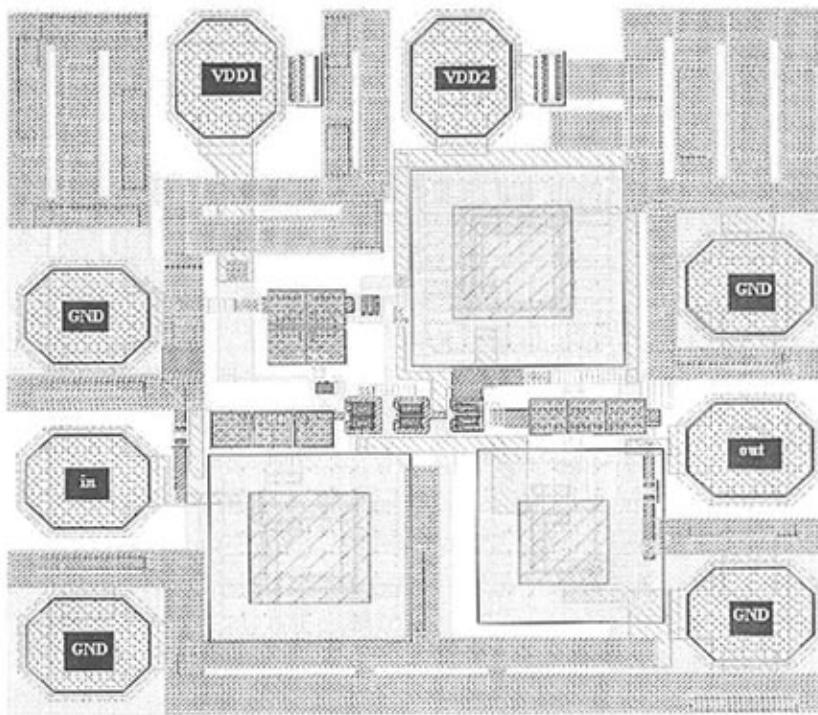

另外，要按照对称的原则进行版图布局，以抑制共模分量，并尽可能让版图看上去美观。根据电路设计相对应的版图，如图 3-10 所示，面积为 0.7mm×0.7mm。

图 3-10 低噪放版图

### 3.7 版图寄生参数提取及后仿真

版图设计完后需要提取其中的各种寄生参数进行后仿真，只有后仿真的结果满足要求之后才能提交给半导体代工厂进行芯片的加工制造。版图必须通过 DRC 设计规则检查和 LVS(版图与原理图对比)检查以后才可以提取其中的寄生参数。版图中的寄生参数包括金属互连线的寄生电阻，寄生电感及对衬底的寄生电容，元器件间的互耦电感，PAD (焊盘) 所引入的寄生电阻、寄生电容等等。Cadence 公司的寄生参数提取软件 Assura 和 Calibre 可以将各种寄生的电阻、电感、电容提取并显示出来以用于电路的后仿真。将版图中提取出来的所有寄生参数带入原理图中进行后仿真，此时放大器的各项性能指标会有所变化，必须调整某些元器件的参数重新优化电路设计，然后重新修改和优化版图，再提取寄生参数进行后仿真，经过多次迭代直到后仿真结果满足要求。

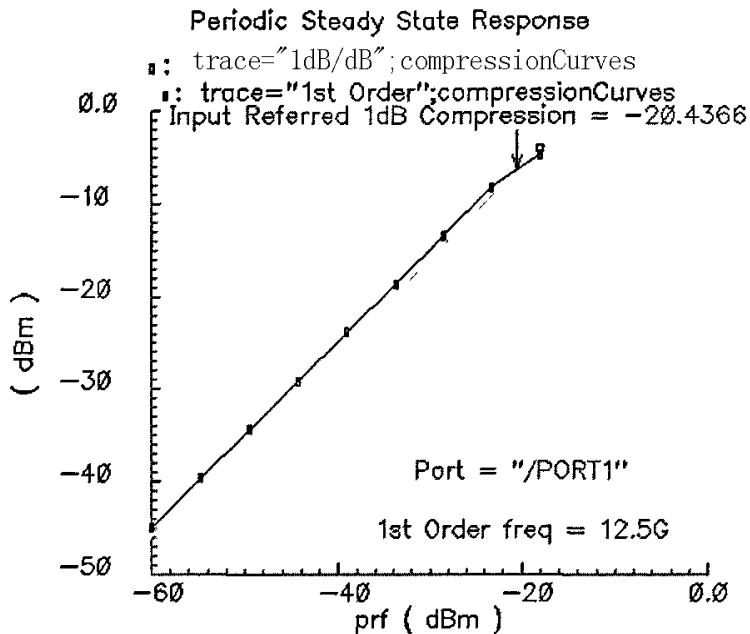

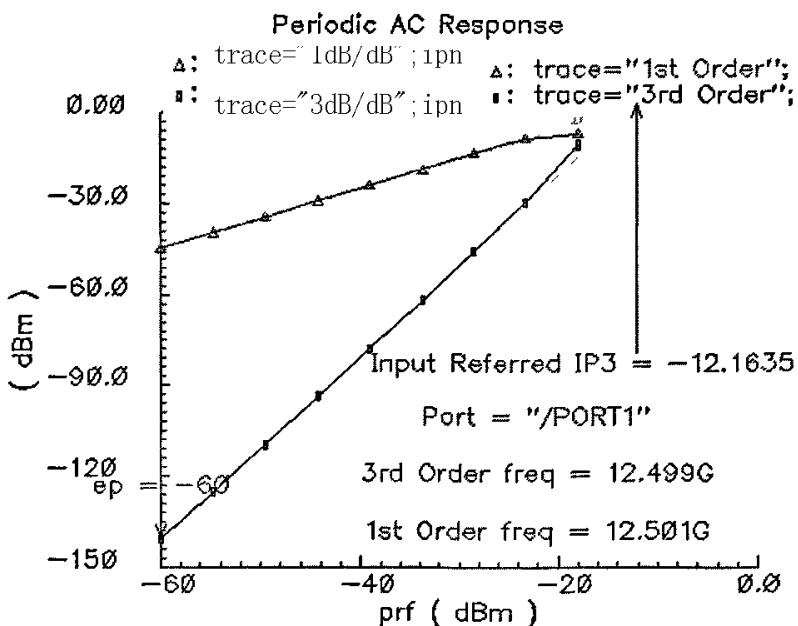

根据以上设计思路，通过对电路原理图和版图的多次迭代优化以后对主要指标在 Cadence 中由 SpectreRF 进行仿真，得到的前后仿真结果总结如表 3-4 所示：

表 3-4 LNA 仿真结果

| 指标                 | 版图前仿真结果          | 版图后仿真结果          |

|--------------------|------------------|------------------|

| NF                 | 3.56dB@12.5GHz   | 3.83dB@12.5GHz   |

| 增益( $S_{12}$ )     | 15.6dB@12.5GHz   | 15.1dB@12.5GHz   |

| $P_{1dB}$          | -19.5dBm@12.5GHz | -20.4dBm@12.5GHz |

| IIP3               | -10dBm@12.5GHz   | -12.1dBm@12.5GHz |

| 输入反射系数( $S_{11}$ ) | -12.5dB@12.5GHz  | -9.3dB@12.5GHz   |

| 输出反射系数( $S_{22}$ ) | -27.3dB@12.5GHz  | -25.3dB@12.5GHz  |

| 反向隔离度( $S_{21}$ )  | -35dB@12.5GHz    | -30dB@12.5GHz    |

| 功耗                 | 6.4mA@3V         | 6.4mA@3V         |

对比前仿真结果可知：由于寄生参数的影响，低噪声放大器的噪声系数恶化了约 0.3dB，变为 3.83dB； $S_{11}$ 有所恶化，但带内仍然优于-9dB；电路的输入 1dB 压缩点恶化为-20.4dBm，反向隔离度  $S_{21}$  恶化为-30dB。

图 3-11 低噪声放大器噪声系数

图 3-12  $P_{1dB}$  压缩点

图 3-13 输入三阶截断点 IIP3

图 3-14 S 参数仿真结果

由上面的各个参数的仿真结果可以得知，在 12.5GHz，该设计同时取得了良好的输入、输出匹配、很好的隔离度、合适的增益和较好的线性度，除输入反射系数  $S_{11}$  略差于指标外，其余各项指标都达到预期的设计目标。

## 第四章 双平衡有源混频器设计

### 4.1 射频混频技术

#### 4.1.1 混频器概述

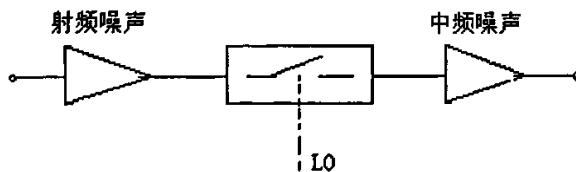

通常混频器在射频系统中起着调制和解调的作用。在发射机中，混频器将中频信号搬移到射频频段；而在接收机中，混频器将接收到的射频信号搬移到中频上。本文设计的混频器为接收机中的混频器，即下变频器，它位于 LNA 之后。

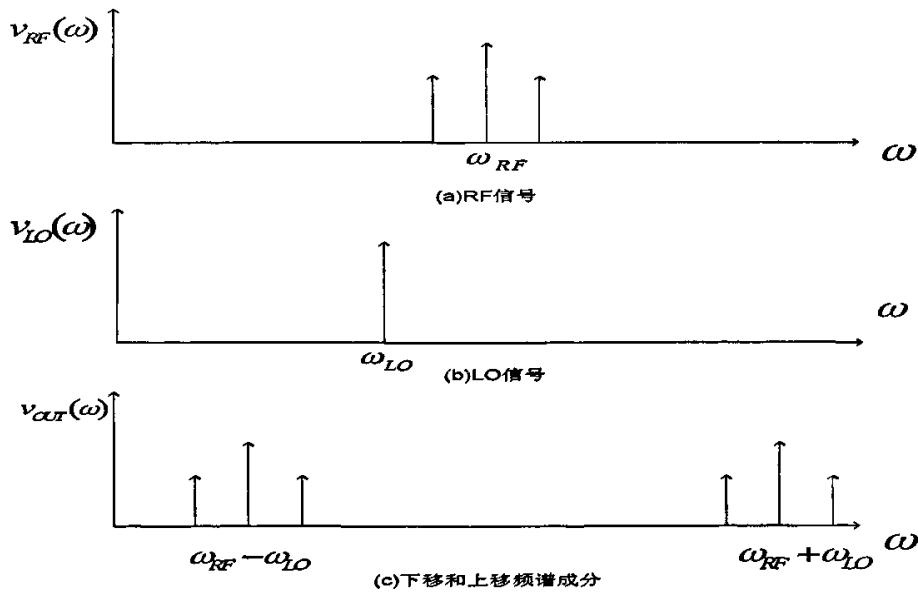

混频是一种频谱的线性搬移过程，它使信号自某一频率变成另一个频率。混频器是将不同频率的信号相乘，它实现频率的转换。混频器有三个端口，一个是射频端口，输入/输出的是射频信号；一个是本振端口，输入的是本振信号；第三个是中频端口，输出/输入中频信号。从频域的角度看混频是一种频谱的线性搬移，输出中频信号与输入射频信号的频谱结构相同，唯一不同的是本振信号。从时域波形看，输出中频信号的波形与输入射频信号的波形相同，不同的也是本振信号。

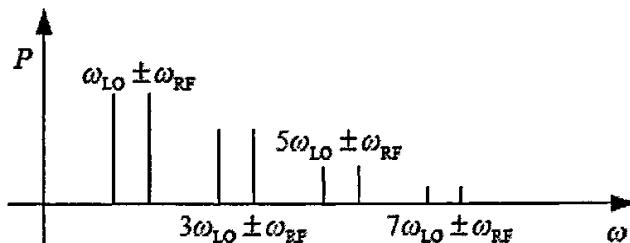

混频的频谱图像如图 4-1 所示：

图 4-1 混频过程中的频谱图像

混频是频谱的线性搬移过程，完成频谱线性搬移功能的关键是获得两个输入信号的乘积，如果能过滤出这个乘积相，就可以完成所需的线性搬移功能。混频器电路的核心部分是将两个信号在时域相乘。乘法的基本作用可以通过考察以下三角恒等式来理解：

$$(A \cos w_1 t)(B \cos w_2 t) = \frac{AB}{2} [\cos(w_1 - w_2)t + \cos(w_1 + w_2)t] \quad (4-1)$$

因此乘法产生了输入信号频率之和与频率之差的输出信号，他们的幅值正比于射频信号和本振信号幅值的乘积。因此，如果本振信号的幅值不变，那么射频信号中任何幅值调制都传递给了中频信号。

可以用工作在线性时变状态的非线性器件实现信号相乘。常用的非线性器件有二极管、场效应管（FET）和双极型晶体管（BJT）。混频器在线性时变工作时，要求射频输入是小信号，本振输入是大信号。混频器对射频信号而言应该是线性系统，其参数随本振信号做周期性变化，这样才能保证在频谱搬移时，射频的频谱结构不变。与 FET、BJT 相比，二极管不需要偏置，功耗低，开关速度快，常被用于混频电路。FET 是平方率特性器件，用它构成混频器产生的无用频率成份要比用 BJT 构成的混频器少得多，BJT 跨导较大，由 BJT 构成的混频器相对增益较高，噪声低。

#### 4.1.2 混频器的基本原理

图 4-2 是混频器的基本原理框图<sup>[12]</sup>，其中混频器的输入信号为：射频信号  $V_{RF}(t)$  和本振信号  $V_{LO}(t)$ 。

图 4-2 是混频器的基本原理框图

由图可见，输入射频信号与本振信号混合后施加在具有非线性传输特性的半导体器件上，该器件则以电流驱动负载。我们假定非线性是理想的，那么就可以用以下的级数展开式来描述输入和输出的关系<sup>[28]</sup>：

$$V_{out} = \sum_{n=0}^N C_n (V_{in})^n \quad (4-2)$$

采用 N 次非线性度作为混频器要求信号  $V_{in}$  是射频输入信号与本振器信号的和。一般来说，输出将包括三类乘积：DC 项、输入的谐波以及这些谐波相互调制的积。并不是所有这些频谱分量都是所希望的，所以在混频器设计中的部分挑战是设计拓扑连接使其从根本上几乎不产生不希望的项。

公式 (4-2) 中的偶次非线性因子构成了 DC 项，他们可以通过 AC 耦合很容易地被滤掉。在  $mw_{LO}$  和  $mw_{RF}$  处的谐波项从基波 ( $m=1$ ) 一直延展到 N 次谐波。与 DC 项一样，它们常常也比较容易被滤掉，因为他们的频率通常离开所希望的中频信号频率很远。

相互调制积是各种频率之和与频率之差的项。它们的频率可以表示成  $p w_{RF} \pm q w_{LO}$ ，这里的 p 和 q 是大于零的整数且它们的和最大为 N。只有二阶相互调制 ( $q=p=1$ ) 是通常所希望的。遗憾的是，当其它的相互调制积的频率很接近所希望的中频频率时，它们就很难被消除。

我们来理论推导混频器中所希望的乘法而实现混频，注意到在级数展开式中唯一的非零系数是  $c_1$  和  $c_2$  项。然后，如果我们假定输入信号  $v_{in}$  是两个余弦的和：

$$v_{in} = v_{RF} \cos(w_{RF}t) + v_{LO} \cos(w_{LO}t) \quad (4-3)$$

那么这个混频器的输出可以表示成三个不同分量的和：

$$v_{out} = v_{fund} + v_{square} + v_{cross} \quad (4-4)$$

其中：

$$v_{fund} = c_1 [v_{RF} \cos(w_{RF}t) + v_{LO} \cos(w_{LO}t)] \quad (4-5)$$

$$v_{square} = c_2 \{[v_{RF} \cos(w_{RF}t)]^2 + [v_{LO} \cos(w_{LO}t)]^2\} \quad (4-6)$$

$$v_{cross} = 2c_2 v_{RF} v_{LO} [\cos(w_{RF}t)][\cos(w_{LO}t)] \quad (4-7)$$

基波项就是与原始输入成比例的部份，因此代表着没有任何有用信号的混频器输出，它们必须通过滤波去除。同样， $v_{square}$  分量也代表着没有任何有用信号的混频器输出，因为这可以从公式 (4-1) 的以下特殊情况中明显的看出：

$$[\cos wt]^2 = \frac{1}{2}[1 + \cos 2wt] \quad (4-8)$$

于是我们看到  $v_{square}$  分量产生了 DC 偏置以及输入信号的二次谐波。这些一般也必

须通过滤波去除。

有用的输出来自 $v_{cross}$ 分量，利用公式(4-1)我们可以把 $v_{cross}$ 重写成能更清楚显示混频作用的形式：

$$v_{out} = C_2 v_{RF} v_{LO} [\cos(w_{RF} - w_{LO})t + \cos(w_{RF} + w_{LO})t] \quad (4-9)$$

我们从公式(4-9)看到了射频信号与本振信号频率相加与相减，这正是我们设计时所期望出现的信号频率，即实现混频。

### 4.1.3 混频器的技术指标

衡量一个混频器电路的好坏主要由该电路的转换增益、噪声系数、线性度、端口间隔离度、输入输出阻抗、功耗等来决定。

#### 4.1.3.1 转换增益

转换增益是衡量混频器的一个重要指标，它定义为输出差频信号或者和频信号与输入信号的比值。转换增益可以用功率增益、电压增益或者电流增益来描述，它们之间的联系为：

$$G_p = G_v^2 \frac{R_s}{R_L} = G_i^2 \frac{R_L}{R_s} \quad (4-10)$$

其中， $G_p$ 是功率增益， $G_v$ 是电压增益， $G_i$ 是电流增益， $R_L$ 是负载阻抗， $R_s$ 是源阻抗。因此将负载阻抗提高一倍，电压增益可以提高6dB，而功率增益仅增加3dB。

根据功率增益，混频器可以分为有源混频器和无源混频器两种。它们的区别就在于是否有功率增益，无源混频器的功率增益小于1，称为混频损耗。无源混频器常用于二极管和工作在可变电阻区的场效应管构成。有源混频器的增益大于1，它由场效应管和双极型晶体管构成。通常希望混频器具有一定的转换增益。这是由于在接收机中，下变频器具有一定的转换增益可以降低混频器后面各级模块对系统噪声性能的影响。而在发射机中，上变频器具有一定的转换增益可以减轻对后级功率放大模块增益的压力。但混频器的转换增益也不能太大，否则可能使得混频器后面的各级模块出现饱和而无法工作。

#### 4.1.3.2 噪声因子（噪声系数）

在接收机里，混频器作为下变频器来使用，它通常位于低噪声放大器后面。由于低噪声放大器提供了一定的增益，因此对下变频器的噪声要求不像对低噪声

放大器那么苛刻，但考虑到射频低噪声放大器的增益有限，而混频过程通常会引入很大的噪声，因此为了降低对低噪声放大器增益的要求，下变频器也需要具有较低的噪声系数。

在发射机里，混频器作为上变频器来使用。由于发射机中有用信号是最强的信号，因此对上变频器噪声系数的要求不像下变频器那么严格。

对于下变频器来说，存在两种类型的噪声系数：单边带噪声系数（SSB）和双边带噪声系数（DSB）。这是由于下变频后产生的中频信号的频率仅与射频信号、本振信号频率之差的幅度有关，因此射频信号和它的镜像信号都会被变换到相同的中频频带上。如果镜像信号频带位置不存在有用信号，这时测量出的噪声系数称为单边带噪声系数；如果有用信号同时出现在射频信号频带和镜像信号频带上，这时测量出的噪声系数称为双边带噪声系数。在大多数接收机系统中（如超外差、低中频接收机等），镜像信号频带位置是不存在有用信号的，因此单边带噪声系数反应了混频器真实的噪声性能；而在零中频接收机中，有用信号同时出现在射频信号频带和镜像信号频带上，因此双边带噪声系数反应了混频器真实的噪声性能。

由于在双边带噪声系数测量中，射频信号频带和镜像信号频带都存在有用信号，而在单边带噪声系数测量中，仅射频信号频带存在有用信号，因此前者的信号功率是后者信号功率的两倍。对同一个混频器来说，前者的输入信噪比比后者高3dB，因此通常来说，单边带噪声系数比双边带噪声系数大3dB。

#### 4.1.3.3 线性度

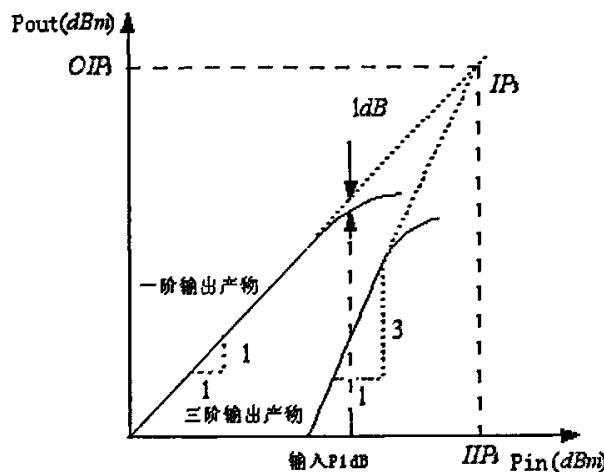

在现代高性能的通信系统中动态范围要求是非常严格的。混频器对输入RF小信号而言是线性网络，理论上我们希望IF输出幅值正比于RF输入信号的幅值，但是现实的混频器存在某一限制，超出了这一限制，输出与输入之间就会有非线性关系，即当输入信号功率逐渐增大到某一程度的时候，存在着非线性失真的问题。线性度决定了混频器能处理的最大信号强度。无论是应用于接收机系统还是应用于发射机系统中的混频器，其输入信号能量都较高，因此混频器必须具有较高的线性度。线性度通常用1dB压缩点( $P_{dB}$ )和三阶交调点(IP3)来描述。

当混频器的射频输入功率较低时，输出功率于输入功率成比例关系。然而，当输入功率超过一定的量值之后，晶体管的增益开始下降，最终结果是输出功率达到饱和。当放大器的增益比其小信号增益低1dB时，此点就被称为1dB压缩点。如图4-3所示。

两个正弦信号的三阶失调也用来表示混频器的线性度特性。一个两正弦信号

的相互调制是估计混频器线性度性能的合适方法，一个所希望的信号与一个可能的干扰同时加入到了混频器的输入端。理想情况下，两个相迭加的射频输入中的每一个都进行频率变换而不会相互干扰，然而实际的混频器总是显示出某种相互调制的效应，因此混频器的输出将包含三阶交调分量经过频率变换后的部分，三阶交调分量的频率为 $2w_{RF1} \pm w_{RF2}$ 及 $2w_{RF2} \pm w_{RF1}$ 。和频项经过频率变换后的部分通常可以被过滤掉，而差频项经过频率变换后的部分通常会落在中频通带内，会对有用中频产生干扰。

三阶交调分量产生的中频信号输出功率与有用中频信号输出功率外推的交点称为三阶交调截断点，此时的输入信号功率记为 IIP3，如图 4-4 所示。

图 4-4 1dB 压缩点及三阶交调截断点示意图

#### 4.1.3.4 输入输出阻抗

对混频器的三个端口要求阻抗匹配，具体来讲就是射频及中频口的匹配可以保证与各滤波器相接时能实现功率的最大传输，本振口的匹配可以有效地向本地振荡器汲取功率。

#### 4.1.3.5 端口间隔离度

混频器各端口间的隔离不理想会产生以下几个方面的影响。本振（LO）口向射频（RF）口的泄漏会使本振大信号影响 LNA 的工作。RF 口向 LO 口的串通会使 RF 中包含的强干扰信号影响本地振荡器的工作，如产生频率牵引等现象，从而影响本振输出频率。LO 口向中频口的串通，本振大信号会使后接的中频放大器过载。RF 信号如果隔离度不好也会直接送到中频输出口，但是一般来说，由于 RF

频率很高，射频泄漏信号都会被中频滤波器滤出，不会影响输出中频。

## 4.2 当前集成混频器研究水平

由于混频器本质上是实现频率变换，所以从信号与系统的观点来看，它不是一个时不变系统，而是一个时变系统。另一方面，由于混频器的本振端是一个周期的本振信号激励，所以混频器是一个线性周期时变系统。

当前射频集成电路设计中混频器的研究水平总结于表 4-1 中。从表 4-1 可看出，当前射频集成混频器设计基本上都是采用有源双平衡混频器（具体解释见下文）的结构，这种结构也称为基于 Gilbert 单元的混频器结构（Gilbert Cell Mixer），其名字来源于发明此结构的 B. Gilbert<sup>[31]</sup>

表 4-1 当前射频集成混频器研究水平

| RF 频率<br>(GHz) | 工艺                | Gain(dB) | NF(dB)    | IIP3<br>(dB) | 输出<br>$P_{1dB}$ | 功耗<br>(mW) | Ref |

|----------------|-------------------|----------|-----------|--------------|-----------------|------------|-----|

| 5.5            | 47GHz $f_T$ SiGe  | 24       | 9.3(DSB)  | -4           | 13              | 12         | 32  |

| 8              | 0.18 $\mu m$ CMOS | 6.6      | 11(SSB)   | 3.5          | 1.1             | 6.9        | 33  |

| 17.35          | 47GHz $f_T$ SiGe  | 12.0     | 11.5(DSB) | -10.0        | -25             | 17.8       | 34  |

| 20.0           | 80GHz $f_T$ SiGe  | 10.0     | 6.0(DSB)  | -11.3        | -21             | 10.0       | 35  |

| 17.0           | 52GHz $f_T$ SiGe  | 5.4      | 8.8(DSB)  | -9.9         | -19             | 7.0        | 35  |

| 20.0           | 50GHz $f_T$ SiGe  | 10.0     | 17.0(DSB) | -1.0         | -9              | 32.0       | 36  |

| 18.0           | 45GHz $f_T$ SiGe  | 4.5      | 7.1(DSB)  | -1.0         | -12.2           | 16.5       | 4   |

## 4.3 双平衡有源混频器性能分析

### 4.3.1 电路拓扑结构选择

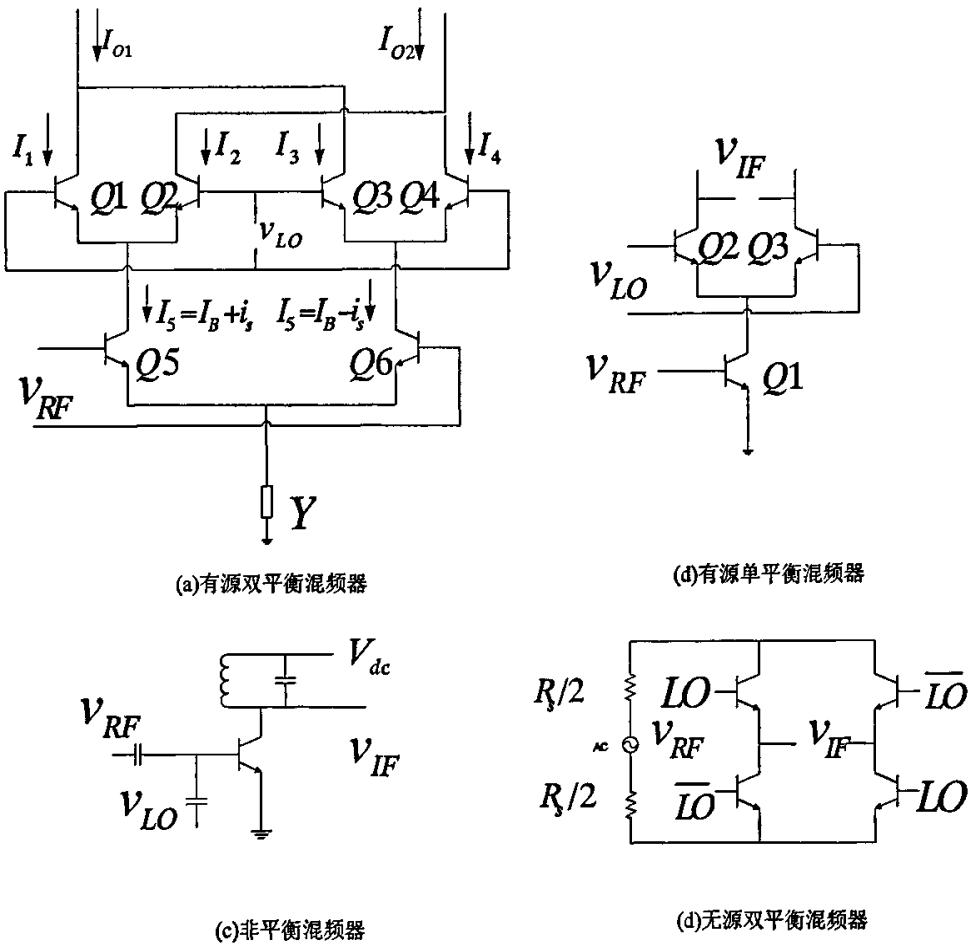

按照混频器中所使用的非线性元件的不同，混频器可以分为二极管混频器和晶体管混频器。由于在分立元件电路中经典的常用的双平衡二极管混频器需要性能优越的变压器，而集成电路工艺不能提供性能优越的变压器元件，所以在集成

电路设计中一般都采用晶体管混频器。对于晶体管混频器，按照混频器是否提供转换增益，可以将其分为有源混频器和无源混频器，无源混频器不提供转换增益，但工作电压低，适用于低功耗电路；有源混频器提供一定的转换增益，可以减小后级模块对噪声系数的贡献。在有源混频器中，又可以根据输入信号和本振信号是否采取差分形式来分为三类：如果输入信号和本振信号都采取差分形式，这类混频器称为双平衡混频器；如果输入信号采取单端形式而本振信号采取差分形式，这类混频器称为单平衡混频器；如果输入信号和本振信号都采取单端形式，这类混频器称为非平衡有源混频器或单端有源混频器。典型的双平衡有源混频器、单平衡有源混频器、非平衡有源混频器和双平衡无源混频器的电路拓扑结构如图 4-5 所示<sup>[12][28]</sup>。

图 4-5 混频器拓扑结构图

单平衡有源混频器结构的主要缺点是无法抑制本振口到射频口的泄漏，采用全差分结构的双平衡结构则有效地阻隔了本振口到射频口的通路。典型的 Gilbert 混频器就是在电流域内实现的一种双平衡有源混频器，如图 4-5 (a) 所示。Gilbert 混频器由两级电路构成，即偏置在固定工作点的差分对管 Q5 和 Q6 构成的跨导级和由大的本振信号驱动的开关级 Q1,Q2 和 Q3,Q4。跨导级将输入的射频电压信号转换为电流信号。大的本振信号在第一个半周期内使 Q1 和 Q3 导通，Q2 和 Q4 截止，则输出电流  $I_{o1} - I_{o2} = I_5 - I_6 = 2i_s$ ；在第二个半周期内，使 Q2 和 Q4 导通，Q1 和 Q3 截止，则输出电流为  $I_{o1} - I_{o2} = I_6 - I_5 = -2i_s$ 。这种输出信号符号的变化提供了需要的混频效应。采用 Gilbert 型双平衡混频器可以获得较高的变频增益，并且因为中频输出不包含本振信号及其谐波，因此存在很高的输入端口，输出端口及本振端口之间的隔离，极大地减轻了本振泄漏及中频滤波的压力。因此本设计中的混频器将采用这种结构实现下变频。

### 4.3.2 双平衡有源混频器转换增益分析

如图4-5 (a) 所示。双平衡有源混频器也被称为Gilbert单元，当射频(RF)和本振(LO)两个输入信号都较弱时，它可以完成模拟信号相乘的功能，这也是该结构提出时的初衷。但在图4-5 (a) 中，本振信号一般都足够强，使得上面的晶体管（图4-5 (a) 中的Q1、Q2、Q3、Q4）都近似为理想开关对。这些开关对在本振信号控制下，将跨导级产生的电流周期性地由一边转换到另一边。差分对Q5、Q6和元件Y构成混频器的跨导级，将输入射频电压信号转换为电流，送入开关对的共源节点。对于双平衡混频器来说，Y可以为一个电流源、直接接地或者为LC谐振电路，该跨导级分别被称为全差分跨导级、伪差分跨导级和LC简并跨导级。伪差分跨导级可以增加混频器的输出摆幅，但跨导级没有共模抑制能力，全差分跨导级可以提供很好的共模抑制能力，但混频器的输出摆幅受到一定的限制；而LC简并跨导级中的LC谐振电路在输入射频信号频率处谐振，对差分射频信号提供低阻抗，而对共模信号，LC谐振电路却提供一个很高的阻抗，因此它也具有一定的共模抑制能力，而且电感本身不消耗电压摆幅，因此混频器的输出摆幅也不会受到影响。本设计将采用LC简并跨导级双平衡结构。

如果本振信号足够强，晶体管Q1~Q4可以近似为理想开关，则双平衡混频器的输出电流为：

$$I_o = I_{o1} - I_{o2} = (I_1 - I_2) - (I_4 - I_3) \quad (4-13)$$

$$= \text{sgn}[\cos(w_{LO}t)](I_B + i_s) - \text{sgn}[\cos(w_{LO}t)](I_B - i_s) \quad (4-14)$$

$$= \text{sgn}[\cos(w_{LO}t)]i_s \quad (4-15)$$

其中  $\text{sgn}[\cos(w_{LO}t)]$  是一个幅度为 1, 频率为  $w_{LO}$  的方波信号:

$$\text{sgn}[\cos(w_{LO}t)] = \begin{cases} +1 & \cos(w_{LO}t) > 0 \\ -1 & \cos(w_{LO}t) < 0 \end{cases} \quad (4-16)$$

将方波信号  $\text{sgn}[\cos w_{LO}t]$  进行傅立叶变换, 可以得到:

$$\text{sgn}[\cos w_{LO}t] = \sum_{n=1}^{\infty} A_n \cos n\pi/2 \quad A_n = \frac{\sin(n\pi/2)}{n\pi/4} \quad (4-17)$$

方波信号是由本振信号的各奇次谐波组成的。

对于跨导器来说, 它的输出为:

$$2i_s = g_m v_{RF} \cos w_{RF} t \quad (4-18)$$

$g_m$  为差分对 M5、M6 的跨导,  $g_m = g_{m5} = g_{m6}$

因此双平衡混频器的输出电流为:

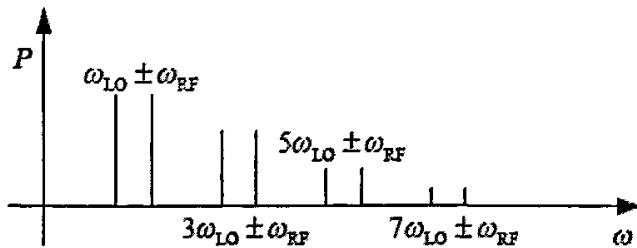

$$I_O = g_m v_{RF} \sum_{n=1}^{\infty} \frac{\sin(n\pi/2)}{n\pi/2} [\cos(nw_{LO} + w_{RF})t + \cos(nw_{LO} - w_{RF})t] \quad (4-19)$$

该输出电流经负载转换为电压信号或者功率信号, 由于负载一般采用线性负载, 因此双平衡混频器的输出仅由  $w_{LO}$  的各奇次谐波与输入射频信号的和频和差频成分组成, 如图4-6所示, 与其它混频器相比, 双平衡混频器的输出频谱中包含有较少的毛刺成分。通常 LO 的基频与输入射频信号的和频 (上变频器) 或者差频成分 (下变频器) 是需要的中频信号, 其它频谱成分都是毛刺干扰信号。双平衡混频器的输出中不包含本振信号成分, 也不包含有射频信号成分, 而且由于开关对采用差分对形式, 本振输入端与射频输入端之间也有很好的隔离, 因此双平衡混频器提供了很高的 LO、RF、IF 之间的隔离度, 这是双平衡混频器的主要优点。实际的双平衡混频器由于受到开关对不匹配的影响, 存在一定的 LO-IF 泄漏, 不匹配程度与版图设计存在很大的关系, 可以通过合理的版图设计 (如共心型版图结构) 来减小。

图4-6 双平衡混频器的输出频谱成份

由式(4-18)可知, 当本振信号足够强时, 双平衡混频器的转换电压增益为:

$$G_v = g_m \frac{2}{\pi} R_L \quad (4-20)$$

其中,  $R_L$  为负载的阻抗值。

对于单平衡混频器, 如图4-5(B)所示, 同样, 如果本振信号足够强, 晶体管M1、M2可以近似为理想开关, 则单平衡混频器的输出电流为:

$$I_{o1} = I_1 - I_2 \quad (4-21)$$

$$= \text{sgn}[\cos(\omega_{LO}t)](I_B + i_s) \quad (4-22)$$

考虑晶体管M3, 电流  $i_s$  为:

$$i_s = g_m v_{RF} \cos(\omega_{RF}t) \quad (4-23)$$

$g_m$  为晶体管M3的跨导。

将方波信号  $\text{sgn}[\cos \omega_{LO}t]$  的傅立叶变换代入, 可以得到单平衡混频器的输出电流为:

$$I_{o1} = g_m v_{RF} \sum_{n=1}^{\infty} \frac{\sin(n\pi/2)}{n\pi/2} [2I_B \cos(n\omega_{LO}t) + \cos(n\omega_{LO}t + \omega_{RF})t + \cos(n\omega_{LO} - \omega_{RF})t] \quad (4-24)$$

该输出电流经负载转换为电压信号或者功率信号, 由于负载一般采用线性负载, 因此单平衡混频器的输出不仅包含有LO的各奇次谐波与输入射频信号的和频差频成分, 而且还包含有本振信号成分, 如图4-7所示。通常LO的基频与输入射频信号的和频(上变频器)或者差频成分(下变频器)是需要的中频信号, 其它频谱成分都是毛刺干扰信号。由于单平衡混频器的输出中包含本振信号成分, 因此存在很严重的LO-IF泄漏。极强的本振馈通信号会增加混频器输出电压的摆幅, 使得混频器输出端出现饱和, 降低了混频器的1dB压缩点, 而在双平衡结构中却不会出现这种情况, 这也是为什么在实际工程应用中一般采用双平衡结构的原因。

由式(4-23)可知, 当本振信号足够强时, 单平衡混频器的转换电压增益仍为:

$$G_v = g_m \frac{2}{\pi} R_L \quad (4-25)$$

其中,  $R_L$  为负载的阻抗值。

图4-7 双平衡混频器的输出频谱成份

### 4.3.3 双平衡有源混频器噪声分析

混频器的时变性和频率的变换使得很难计算它的的噪声因子。如图4-8的概念性图示说明，在经过下变频器前噪声成份位于RF范围内，而经过下变频后噪声成份位于IF范围内。通过转换级的RF噪声成份的转换是不能在SPICE中直接使用小信号交流和噪声分析的，因为SPICE要求模拟必须在时域中进行。但是，现在大多数SPICE版本都不支持时域噪声分析<sup>[37]</sup>。另一个困难是开关级贡献的噪声呈现出时变统计特性。在此我们仅对BJT型单平衡混频器的噪声特性做定性的分析，虽然定性的分析无法得出精确的噪声因子的计算公式，但是通过定性分析却可以指出几种重要的噪声源并且可以提供有关如何使噪声系数最小的一般建议。

图4-8 混频器噪声转换概念图

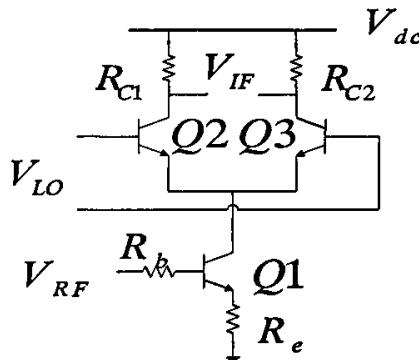

混频器输出端的噪声主要是由跨导级产生的热噪声、开关对产生的热噪声和散粒噪声、负载热噪声引起的。跨导级是一个共源放大器，因此可以采用与低噪声放大器相同的噪声优化方法来优化跨导级中晶体管的尺寸和偏置，使得跨导级产生的热噪声尽可能低。

图4-9是一个典型的BJT型单平衡混频器拓扑结构图。在这个电路中有这样几个噪声源：首先，在RF路径中，由Q1基极电阻和发射极电阻 $R_e$ 产生的热噪声，以

及集电极Q1产生的散粒噪声（shot noise）构成了主要的成份。其次，在IF路径中，电阻 $R_{c1}$ 和 $R_{c2}$ 引入热噪声。需要更加关注的是由Q2和Q3贡献的噪声。首先，假定晶体管的转换都是在瞬间进行的。则如图4-10所示，在LO周期内每个器件都有一半的时间是导通的，将噪声注入到输出端。这是因为节点P处存在的寄生电容 $C_p$ 提供了到地的阻抗。这个电容起源于Q2和Q3的基极—发射极结和Q1的集电极—基极和集电极—衬底结。如果为了减小晶体管的基极电阻而采用大尺寸的晶体管，这个电容会变得很大。因而，由基极电阻和Q2的集电极电流产生的RF噪声被该晶体管的开关操作转移到IF信号里。

图4-9 典型的BJT型单平衡混频器拓扑结构图

图4-10 Q3截止时Q2的噪声贡献示意图

实际上，LO信号一般并不是方波，而是正弦波，在一个周期内有一部份时间Q2和Q3会同时导通。在同时导通的时间内，两个晶体管放大了它们基极电阻产生的热噪声，并将它们集电极的散粒噪声注入到输出端。从另外一个角度来讲，在这种情况下Q2的操作与图4-10描述的情况相似。不同的是在此中情况下从Q2的发射极看到的是一个低的对地阻抗（ $\sim 1/g_m$ ）。

当Q2和Q3同时导通，都向IF输出端注入噪声，这时 $I_{c1}$ 中的噪声影响就会很小，

这是因为它主要以共模信号的形式出现。换句话说，当Q2和Q3的噪声变得很大时， $I_{c1}$ 的噪声就变得不重要了，反之亦然。

通过以上分析，可以采用以下的四种方式来减小Q2和Q3贡献的热噪声和散粒噪声<sup>[37]</sup>：（1）利用大的LO信号摆幅（但要避免Q2和Q3饱和）；（2）降低 $C_p$ ，也就是减小Q1、Q2、Q3的尺寸，但是却会产生更高的基极电阻噪声；（3）降低Q2和Q3的基极电阻，但是会导致 $C_p$ 的增大；（4）减小Q2和Q3的集电极电流。对方式（4）需要做进一步的解释。因为Q2和Q3出现在信号电流路径上，它们的散粒噪声电流 $\overline{I_n^2} = 2qI_c \overline{I_n^2} = 2qI_c$ 直接破坏了信号，因此当 $I_c$ 减小的时候这个噪声电流也减小。与此不同，Q1的散粒噪声的影响可以等效为噪声电压 $\overline{V_n^2}, \overline{V_n}$ 可看作是以输入端做参考的电压 $\overline{V_n^2} = 2kT/g_m = 2kTV_T/I_c$ ，如果基极散粒噪声的效应可以忽略，那么 $I_c$ 增加它会减小。换言之，当Q1的集电极电流减小的时候，它会贡献更多的噪声，而Q2和Q3的贡献就会减少。

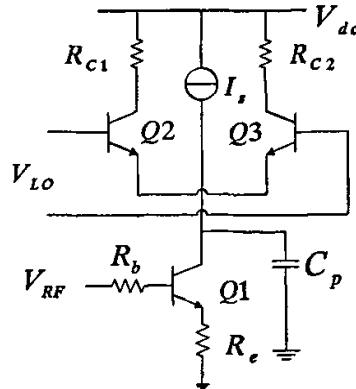

上述的折衷选择要求仔细选择器件的尺寸和偏置电流以使得整体得噪声因子达到最小。为了让Q1和Q2,Q3的集电极电流值相互独立，可以增加一个电流源，如图4-11所示。流经Q2和Q3的集电极电流减小，可以减小Q2和Q3贡献的散粒噪声。同时，对于给定的，可以允许的 $R_{c1}$ 和 $R_{c2}$ 两端的电压降，它们的电阻值可以增加，因而也就提高了电压转换增益。但是，这种方法还面临两个问题。第一，当Q2和Q3的集电极电流减少时，从它们的发射极看进去的阻抗增加，导致Q1提供更多的RF电流通过 $C_p$ 分流到地。第二，由 $I_s$ 产生的噪声电流直接加到了RF信号上。由于这些原因，这种结构只能降低一小部分噪声因子。

图4-11 通过减小流过开关对的电流来减小混频器的噪声系数

#### 4.3.4 双平衡有源混频器线性度分析

当混频器的负载是线性负载时，混频器的线性度与跨导级和开关对有关。由于开关对的状态是一个周期性稳态过程，因此分析它的线性度是非常复杂的。本小节将仅针对三阶交调截断点进行定性说明。由于双平衡混频器是由两个单平衡混频器以差分结构构成的，双平衡混频器的输入功率在两个单平衡混频器之间平分，因此双平衡混频器的线性度性能比单平衡混频器高3dB。下面仅针对单平衡混频器进行说明。对于单平衡混频器来说，跨导级是一个共源放大器，因此跨导级的线性度限制了混频器最高能达到的线性度性能，也就是说，如果由LO驱动的晶体管的作用如性能良好的开关，那么整个混频器的IP3一般不会与跨导电路的IP3有什么差别。当跨导级是一个理想的电压-电流线性变换器时，混频器的线性度也会受到开关对引入的交调的限制。研究发现，当本振信号频率较低，可以忽略电路中的节点寄生电容时，开关对引入的三阶交调积与本振信号过零处的斜率成反比，随本振信号幅度的增加而减小，因此当开关对可近似作为理想开关时，可以忽略开关对引入的三阶交调积的贡献；而当本振信号频率较高时，开关对共射节点的寄生电容会严重恶化混频器的三阶交调性能，共射节点的寄生电容越大，三阶交调积越高，而且与低频情况下不同，高频下开关对引入的三阶交调积与本振信号幅度之间不是单调关系。本振信号幅度较小时，本振信号幅度增加，开关对引入的三阶交调积会减小；而当本振信号幅度增加到一定程度后，开关对引入的三阶交调积反而会随着本振信号幅度的增加而增加，因此存在一个优化的本振信号幅度，可以最大程度地减小开关对引入的三阶交调积。无论是高频下还是低频下，混频器的三阶交调积近似是跨导级的三阶交调积和开关对引入的三阶交调积之和。

由于混频器的线性度主要与跨导级和开关对有关，因此改善混频器的线性度应从提高跨导级的线性度和提高开关对的线性度两方面着手进行考虑。跨导级实际上是一个高频V-I变换电路，可以通过以下技术来提高跨导级的线性度：发射级负反馈技术、AB类工作的跨导级技术、分段线性近似技术等<sup>[38]</sup>。为了减小开关对引入的三阶交调积，应对本振信号幅度和开关对尺寸进行优化，选择使三阶交调积最小的本振信号幅度和开关对尺寸，另外还可以采用在开关对共射节点并联一个电感的方法来降低共射节点寄生电容充放电所引入的非线性（本设计中的混频器即采用了这种技术）。

下面分别对发射级负反馈技术、AB类工作的跨导级技术、分段线性近似技术

做简要介绍。

### 1. 发射级负反馈技术

这种技术通过在跨导级晶体管的发射极串联一个无源元件形成串联负反馈来提高跨导级的线性度，负反馈无源元件可以是电感、电容或者电阻。电阻作负反馈元件会引入热噪声，而且电阻本身会产生DC压降，使电源有效净电压的范围减小；电容和电感作负反馈元件并不会引入额外的噪声，特别是电感负反馈，提高频率使一个电感的电抗增加有助于衰减高频谐波和交调分量，另外考虑到电容作负反馈元件还需要在跨导级中插入额外的直流通路，而且会在晶体管的基极产生一个负阻，使得跨导级不稳定，因此通常用电感作负反馈元件。

### 2. AB类工作的跨导级技术

AB类工作的跨导级偏置于AB类工作模式，跨导级的偏置电流小于平均输出电流，因此在一个周期的一部分时间内，跨导级的晶体管处于截止状态。在高输入功率时使晶体管工作于AB类模式，可以减小偏置电流，减小负载上的直流压降，避免混频器过早因电压受限而使增益受到压缩，因此可以提高混频器的1dB压缩点。但该技术不能改善混频器的三阶交调性能（三阶交调性能是由电路的弱非线性决定的），而且跨导级中的晶体管截止会产生大量的谐波，使得混频器输出信号中含有大量的毛刺成份，因此该类混频器输出端必须有滤波网络来滤除毛刺成分。

### 3. 分段线性近似技术

分段线性近似利用了以下原理来提高线性度：任何一个系统在一个足够小的范围内都是线性的，因此可以用几个子系统来组成一个完整的系统，每一个子系统在一段范围内是线性的，而且在每一段范围内，整个系统中仅有一个子系统在工作，其它的子系统都不工作，这样的子系统组合起来后就具有较大的线性范围。

本设计采用的是第一种方法即发射极电感负反馈来提高混频器的线性度。

## 4.4 双平衡有源混频器电路设计

### 4.4.1 设计指标

具体的设计指标如下：

射频(RF) 频率范围 12.25GHz—12.75GHz

本振(LO) 频率 11.3 GHz

|                  |                                  |

|------------------|----------------------------------|

| 电源电压             | 3V                               |

| 噪声系数(DSB)        | <8dB                             |

| 输入 1dB 压缩点       | >-15dBm @fif=1.2GHz              |

| 输入 IP3           | >-5dBm @fif=1.2GHz               |

| 增益               | >8dB@12.5GHz                     |

| 输入匹配( $S_{11}$ ) | <-10dB@12.5GHz                   |

| 输出匹配( $S_{22}$ ) | <-10dB@ $f_{IF} = 1.2\text{GHz}$ |

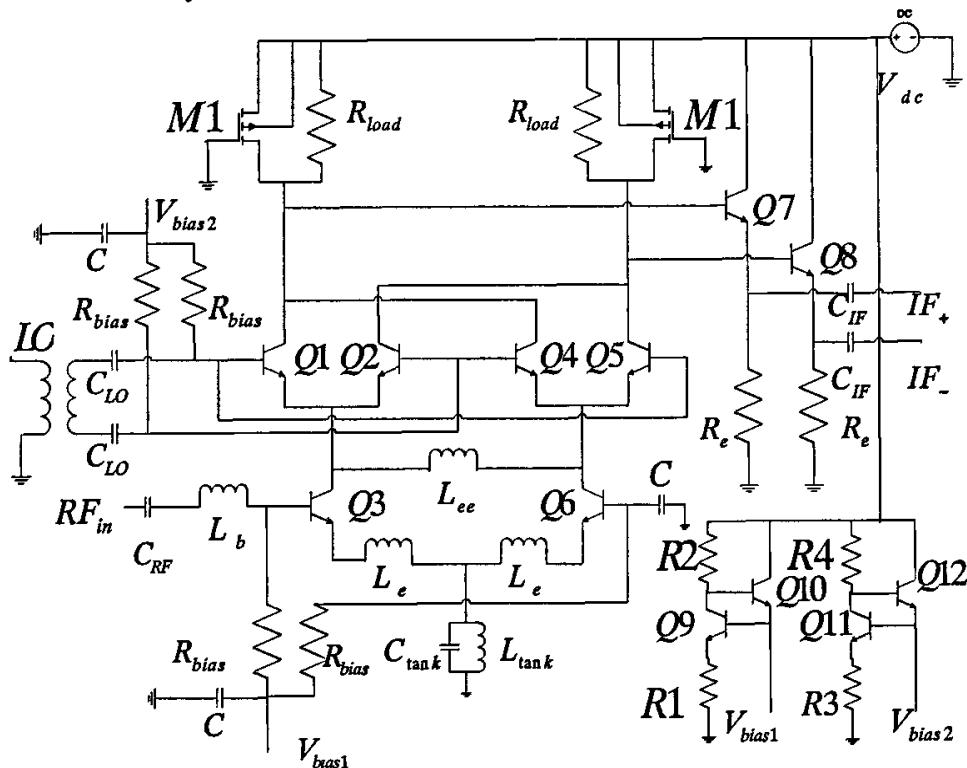

#### 4.4.2 完整混频器电路结构图

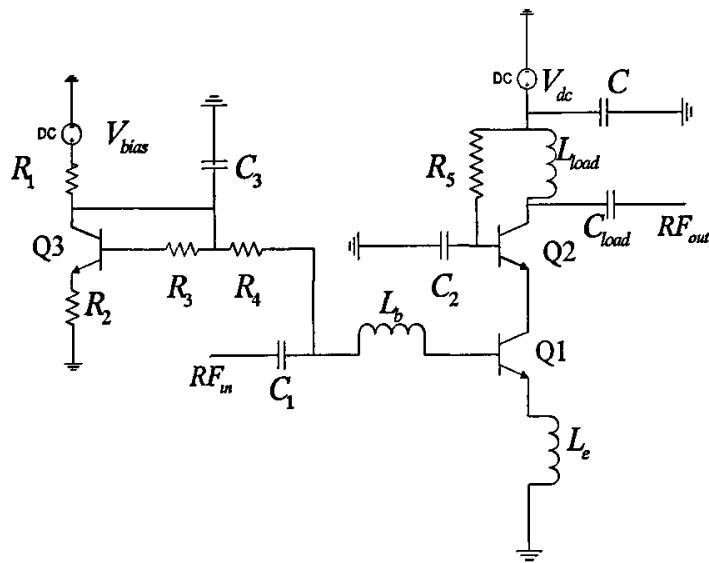

本文设计的基于 Gilbert 单元为核心的有源双平衡混频器完整拓扑结构图如图 4-12 所示。由于前级的低噪声放大器是单端结构，出于系统级联方面的考虑，所以紧接在低噪声放大器后的混频器的射频输入端必须是单端输入的。另外考虑到在测试时是在片测试 (on-wafer test)，测试系统不能够提供频率高达 11.3GHz 的差分信号，所以本振 (LO) 输入端也必须是单端输入，单端输入的 LO 信号再通过 JAAZ 工艺库提供的片上巴伦转变为差分信号做为差分本振输入信号。所以本设计中的混频器结构是射频、本振都是单端输入的基于 Gilbert 单元为核心的有源双平衡结构。整个电路包含跨导管对 Q5、Q6，噪声和功率匹配电感  $L_b$ 、 $L_e$ ，开关管 Q1、Q2、Q3、Q4，去噪声电感  $L_{ee}$ ；抑制共模分量的并联 LC 谐振槽 (parallel LC tank)；含有分流单元的中频负载电路、偏置电路和输出缓冲电路。

#### 4.4.3 跨导级的设计

射频差分信号通过跨导级晶体管的基极进入电路。为了尽可能减小跨导级电路部分的噪声和实现射频信号功率的最大传输，跨导管对和匹配网络被设计成能同时实现噪声和功率的 50 欧姆匹配。为了同时实现最小噪声匹配和最大功率传输匹配，我们要求

$$Z_{in}^* = Z_s = Z_{opt} \quad (4-25)$$

其中  $Z_{in}^*$ ， $Z_s$ ， $Z_{opt}$  分别表示电路输入阻抗，信号源阻抗和最小噪声源阻抗。对于一个给定的晶体管可以通过设定偏置电流，晶体管尺寸和发射极负反馈电感值来实现

$$\begin{cases} \Re(Z_{in}) = \Re(Z_s) = \Re(Z_{opt}) \\ \Im(Z_{in}) = -\Im(Z_{opt}) \end{cases} \quad (4-26)$$

对于一个实信号源阻抗，我们可以通过设置一个合适的基极电感来实现上述匹配<sup>[39]</sup>。对于任何一种工艺来讲，最小集电极电流密度对应于最小噪声（我们往往用  $NF_{min}$  来表征最小噪声）但是实际上  $NF_{min}$  随集电极电流密度的变化而变化的很缓慢，正是这一点使得我们在设置偏置电流和晶体管尺寸时有更为宽松的选择<sup>[40]</sup>。通过反复优化，最终跨导管对每个晶体管的集电极电流被设置为 4.6 mA，晶体管采用双基极的晶体管，发射极尺寸为  $0.35 \mu m \times 12 \mu m$ 。之所以采用双基极的晶体管而不采用单基极的晶体管是为了减小串接在基极的寄生电阻产生的热噪声。发射极负反馈电感  $L_e$  和串接在晶体管基极的基极电感  $L_b$  分别为 0.89nH 和 0.13nH。

图 4.12 有源双平衡混频器完整拓扑结构图

#### 4.4.4 并联 LC 谐振槽的设计

一个典型的有源双平衡混频器结构如图4-5(a)所示，通常Y为一个DC电流源，这种结构可以提供很好的共模抑制能力，但混频器的输出摆幅受到一定的限制；在低电压应用中，可以用一个并联的LC谐振槽来代替DC电流源以构成一个“零净空”（zero-headroom）的AC（交流）电流源。这一振荡回路的谐振频率应当选择

成能排除任何最不希望有的共模分量<sup>[28]</sup>。通常这一振荡频率被设置为射频信号的频率。由于本设计的工作电压仅为3V，所以也采用这种最小电源净空（minimum supply-headroom）的结构。谐振槽路由并联的 $L_{\text{tank}}$  和  $C_{\text{tank}}$  构成，谐振频率为射频信号频率12.5GHz。考虑到工艺库中电感值越小的电感自谐振频率越高，品质因数相对于电感值较大的电感也较高，而且，电感值越小，电感尺寸也越小。但是电容的品质因数一般很高，而且随电容值的变化不大。所以决定采用较小的电感和一个电容谐振在12.5GHz。根据公式

$$f = \frac{1}{2\pi\sqrt{L_{\text{tank}}C_{\text{tank}}}} \quad (4-27)$$

$f = 12.5\text{GHz}$ , 当  $L_{\text{tank}}$  取值为0.2nH时，通过计算可得  $C_{\text{tank}} = 810\text{fF}$ 。但实际上考虑到电感  $L_e$  对地的并联寄生电容的存在和版图设计中所带来的不可避免的寄生电容的影响， $C_{\text{tank}}$  值要比810fF小才能使其与  $L_{\text{tank}}$  谐振在12.5 GHz。具体  $L_{\text{tank}}$  和  $C_{\text{tank}}$  的值要通过版图后仿真优化才能得到。最终  $L_{\text{tank}}$  和  $C_{\text{tank}}$  的值分别为0.198nH和795fF。

#### 4.4.5 开关级的设计

混频器的开关级也在好几个方面使混频器的噪声性能下降。一个对噪声系数的影响来源于非理想的开关特性，它会引起信号电流的衰减。开关晶体管的另一个NF影响表现在两个晶体管都导通电流并且因此产生噪声的时候。此外在本振中的任何噪声也在这个有效的放大期间被放大。使这一同时导通时间最短可以减少性能的下降，所以必须要提供足够的本振驱动使这一差分对在最大的实用范围内接近理想的无穷快的开关<sup>[28]</sup>。典型的开关晶体管的尺寸要小于跨导管的尺寸，这是因为更大的集电极电流密度会提高晶体管的截止频率  $f_T$ ，截止频率越高开关特性会越好。从另一方面来讲，选择偏置电流许可的最小尺寸也不是一个最优的选择。这是因为跨导管的集电极寄生电容提供了一个对地的有限阻抗，所以开关级的每一个晶体管的表现就相当于一个共射放大器，它的基极电阻热噪声会被放大至中频口输出。在跨导管集电极之间跨接一个电感，并使其与集电极寄生电容谐振在射频信号中心频率上，可以极大地降低基极电阻热噪声的影响。此跨接电感电感值为1.1nH。过度地减小开关管的尺寸会导致很大的基极电阻和产生很大的噪声，所以在此电路中开关管尺寸被设置为跨导管的3/4。

#### 4.4.6 负载电路的设计

为提高混频器的变频增益以抑制噪声, 对传统的Gilbert型双平衡混频器结构进行了改进, 即增加了分流源单元。大的负载电阻可以提高增益, 但是大的负载电阻会消耗很大的电压降, 给开关级和跨导级造成很大的电压余度压力, 在峰值电流下可能会使开关管和跨导管脱离放大区进入饱和区或者截止区造成严重的非线性失真。因此在开关管的集电极引入两个电流源, 用来分流流入负载电阻  $R_{load}$  的电流。分流源是通过连接在电源和跨导管之间的PMOS晶体管M1,M2来实现的。经计算和仿真优化, 负载电阻值设置为1000欧姆, 流经PMOS和负载电阻的电流分别为总电流的4/5和1/5时噪声性能最好。

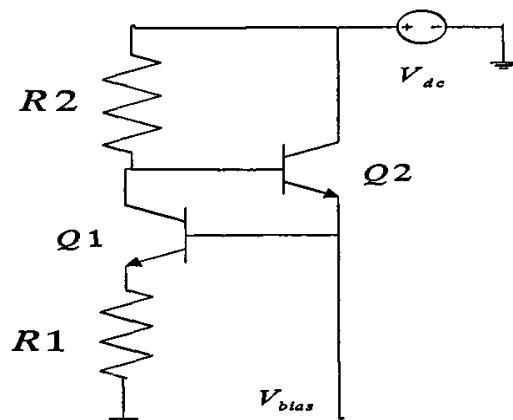

#### 4.4.7 偏置电路的设计

BiCMOS电路对于偏置电压的稳定性要求很高, 所以需要专门的模块来提供参考电压, 使其在电源和温度变化的情况下保持相对的稳定。本设计中采用一种双基极反馈电路(如图4-13所示)来提供本芯片中跨导级1.18V和开关级2.1V的偏置电压, 这种双基极反馈电路对工艺偏差, 电源电压变化和温度变化均不敏感<sup>[5]</sup>。另外将阻值为10K的电阻  $R_{bias}$  分别置于RF和LO信号的输入端与直流偏置电路之间, 阻止RF信号以及LO信号泄漏到偏置电路中。

图4-13 混频器偏置电路

#### 4.4.8 输出缓冲器的设计

为了实现在0.95GHz—1.45GHz的宽频带范围内的良好匹配, 中频信号经由射随器构成的输出缓冲器输出。另一方面, 用射随器做输出缓冲器可以避免在中频

口使用LC匹配网络，降低电感的使用数量，减小芯片的面积。输出缓冲器消耗的功耗为3mA。

最终，图4-12中各元件的参数值如表4-1所示：

表4-1 混频器电路中元件参数

|                     |                                     |

|---------------------|-------------------------------------|

| Q1、Q2、Q3、Q4         | dn452, EL(emitter length)=9 $\mu m$ |

| Q5、Q6               | dn452, EL=12 $\mu m$                |

| Q7、Q8               | dn452, EL=3 $\mu m$                 |

| Q9                  | dn111, EL=3 $\mu m$                 |

| Q10                 | dn111, EL=9.1 $\mu m$               |

| Q11                 | dn111, EL=5.5 $\mu m$               |

| Q12                 | dn111, EL=12 $\mu m$                |

| M1、M2               | L=0.35 $\mu m$ , W=50 $\mu m$       |

| $L_b$               | 0.89nH                              |

| $L_e$               | 0.13nH                              |

| $L_{ee}$            | 1.1nH                               |

| $L_{tank}$          | 0.198nH                             |

| $C_{tank}$          | 795fF                               |

| $C_{LO}$ 、 $C_{RF}$ | 1.3pF                               |

| $C_{IF}$            | 26pF                                |

| $C$                 | 5pF                                 |

| $R_1$               | 3.27K $\Omega$                      |

| $R_2$               | 1000 $\Omega$                       |

| $R_3$               | 1000 $\Omega$                       |

| $R_4$               | 837 $\Omega$                        |

| $R_{load}$          | 1000 $\Omega$                       |

| $R_e$               | 800 $\Omega$                        |

| $V_{bias1}$         | 1.18V                               |

| $V_{bias2}$         | 2.1V                                |

## 4.5 双平衡有源混频器版图的设计

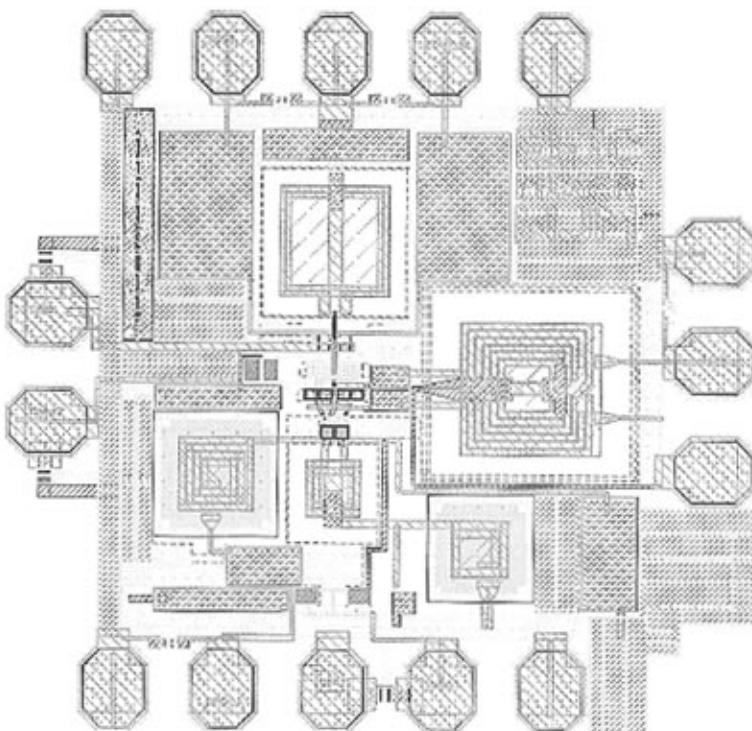

本设计中的混频器采用JAZZ半导体公司商用0.35um SiGe BiCMOS工艺进行MPW(多项目流片)。该工艺能够提供一层多晶层和四层金属层。对于最优化的偏置电流该工艺的HBT截止频率 $f_T$ 可达到60GHz, 在12.5GHz的频率下单管的最小噪声系数 $NF_{min}$ 为2.7dB。该工艺的应用目标为射频, 模拟和数模混合电路, 尤其适用于射频集成电路制造。厚度达3 $\mu m$ 的顶层金属减小了信号的互连损耗。利用该工艺提供的深沟道绝缘和多晶硅防护, 片上电感的品质因素在12.5GHz时可达到13。以下是在设计本设计中双平衡混频器版图时的几点经验总结。

- (1) 版图布局是版图设计的第一步, 也是最重要最关键的一步, 在具体画版图之前应当多花时间综合全面的考虑版图布局, 好的开始是成功的一半。

- (2) 双平衡混频器是全差分结构, 在版图布局时要使版图尽可能的对称以抑制共模噪声。

- (3) 在版图布局时要尽量紧凑, 以减小信号走线长度, 尽可能降低信号金属走线的寄生电阻, 寄生电感和对地寄生电容, 金属走线之间相互耦合电容所带来的影响。另一方面也可以减小芯片面积。

- (4) 要注意元件的匹配, 特别是有源晶体管对的匹配, 如Q5与Q6, Q1与Q2, Q3与Q4, Q1、Q2整体与Q3、Q4整体, Q7与Q8, M1与M2匹配, 具体做法是让Q5与Q6, Q1与Q2, Q3与Q4, Q1、Q2整体与Q3、Q4整体, Q7与Q8, M1与M2分别沿某根轴线尽可能近地对称分布, 如有可能可以采用共心结构或者dummy元件以尽可能减小元件的不匹配性。

- (5) 电感 $L_e$ 、 $L_{ee}$ 均采用差分电感, 一方面可以提高匹配另一方面也极大地减小了芯片面积。

- (6) 为了尽可能减小本振、射频、中频信号之间的相互串扰, 特别是减小本振信号在射频口的泄漏, 本振口、射频口和中频口要相互远离, 本设计中将本振口输入、射频口输入、中频口输出分别置于三个不同的边上。

- (7) 为了防止电磁耦合, 电感之间的间距根据该工艺提供的推荐值设置为25 $\mu m$ 。如果面积允许, 电感之间的间距应该尽可能的远。

- (8) 为了防止衬底噪声之间的相互耦合, 同时也是为了保证衬底电位的一致性, 对衬底进行了大面积接地处理。具体做法是对最低层的金属1层

尽可能的铺金属，使金属1层的金属接地，然后再通过打过孔使衬底与金属1层相连，这样一来可以保证衬底的大面积接地。

- (9) 对于射频集成电路，寄生参数会严重地影响电路的性能，为了减小寄生电容和寄生电阻对电路性能的影响，射频信号走线尽可能采用最厚的顶层金属走线，信号线要尽量短，并且信号线按照 $1\mu\text{m}/1\text{mA}$ 的经验值进行布线。在偏置电路和连接电源的走直流信号的金属走线要尽可能的宽，以尽可能减小金属线寄生电阻所带来的电压降。

- (10) 根据EMC原则，射频信号走线在拐角处不要走直角，应进行45度的倒角处理或弧形倒角处理，以减小射频信号的反射。

- (11) 起到连接层与层金属线的过孔数目要尽可能的多，如果是连接射频信号走线的过孔，数目最好保证在50个以上，以尽可能减小过孔电阻对信号的损耗，同时也可以避免闭锁(Latch-up)效应。

该芯片的版图如图4-14所示，面积为 $0.9\text{mm}\times 0.9\text{mm}$ (包含pads)。

图4-14 双平衡有源混频器芯片版图

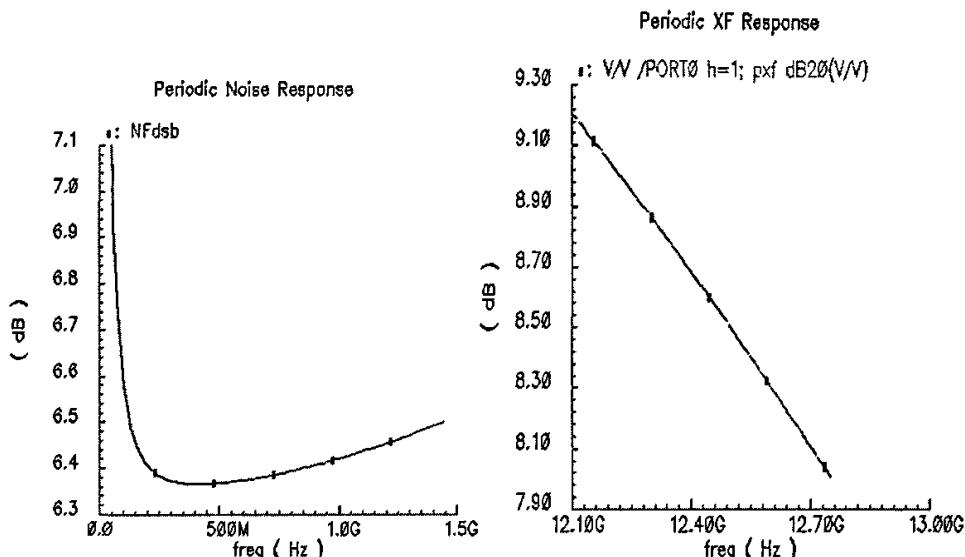

## 4.6 版图寄生参数提取及后仿真

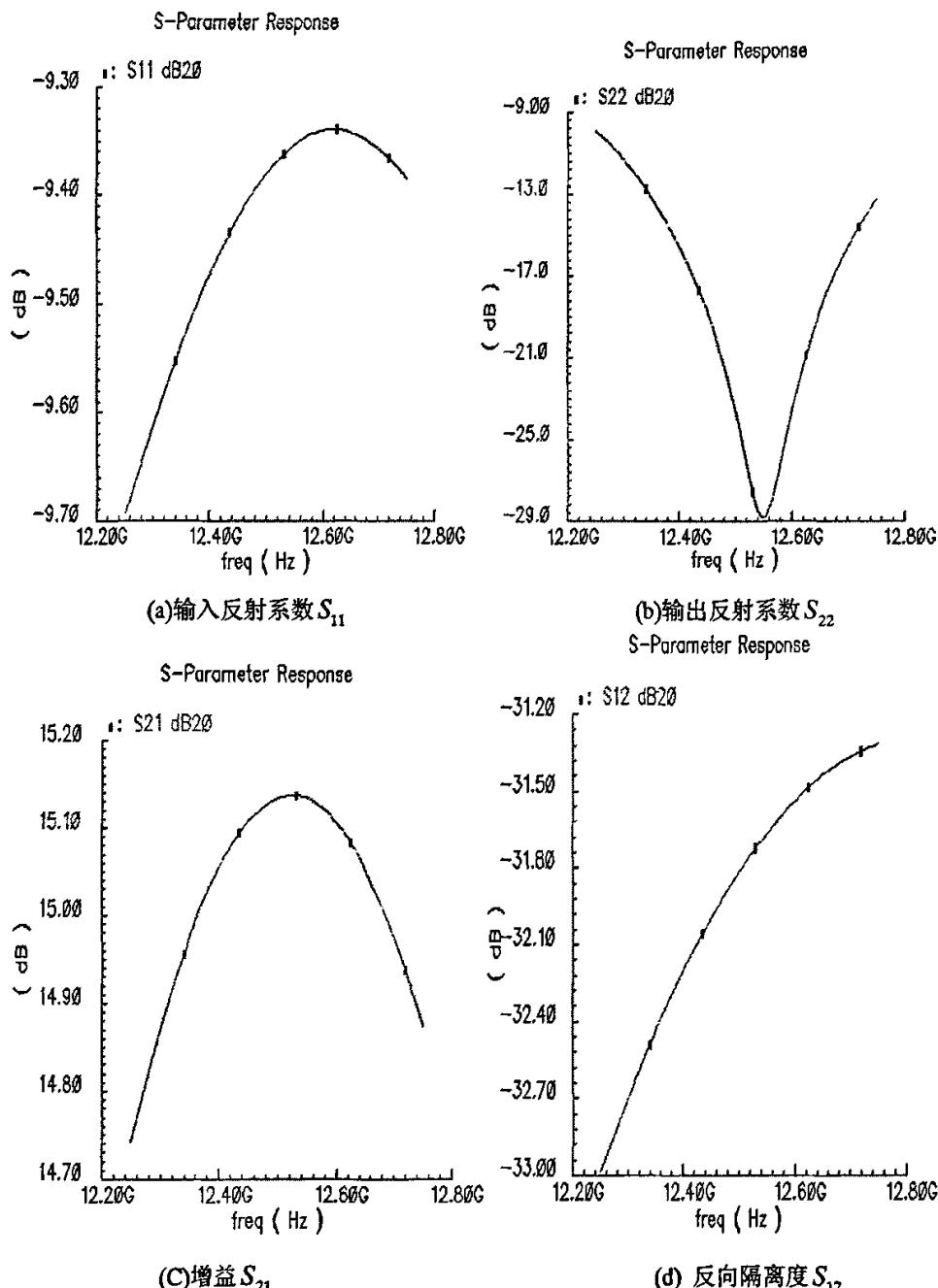

与第三章低噪声放大器设计中的后仿真相类似，用 Cadence 公司的寄生参数提取软件 Assura 和 Calibre 将各种寄生的电阻、电感、电容提取并显示出来以用于电路的后仿真。将版图中提取出来的所有寄生参数带入原理图中进行后仿真，通过对电路原理图和版图的多次迭代优化以后，对主要指标在 Cadence 中由 SpectreRF 进行仿真，得到的仿真结果总结如表 4-3 所示：

表 4-3 混频器仿真结果

|                         | 版图前仿真               | 版图后仿真               |

|-------------------------|---------------------|---------------------|

| 射频信号 (RF) 频率            | 12.25GHz-12.75GHz   | 12.25GHz-12.75GHz   |

| 本振 (LO) 频率              | 11.3GHz             | 11.3GHz             |

| 电源电压 Vdc                | 3V                  | 3V                  |

| Vbias1                  | 1.18V               | 1.18V               |

| Vbias2                  | 2.1V                | 2.1V                |

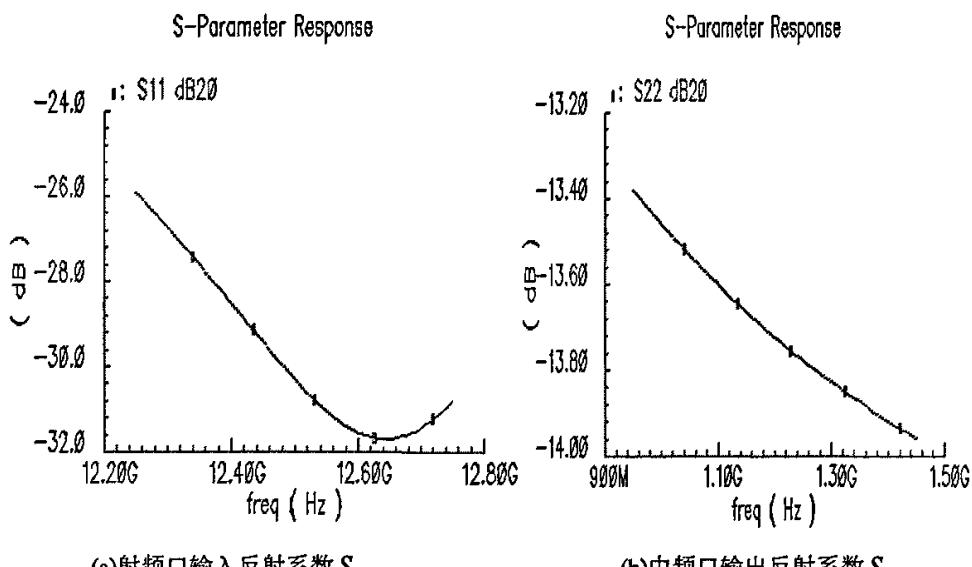

| 射频口输入反射系数 $S_{11}$      | -20dB@frf=12.5GHz   | -31dB@frf=12.5GHz   |

| 中频口输出反射系数 $S_{22}$      | -20dB@fif=1.2GHz    | -13.8dB@fif=1.2GHz  |

| NF(DSB)                 | 6dB@fif=1.2GHz      | 6.43dB@fif=1.2GHz   |

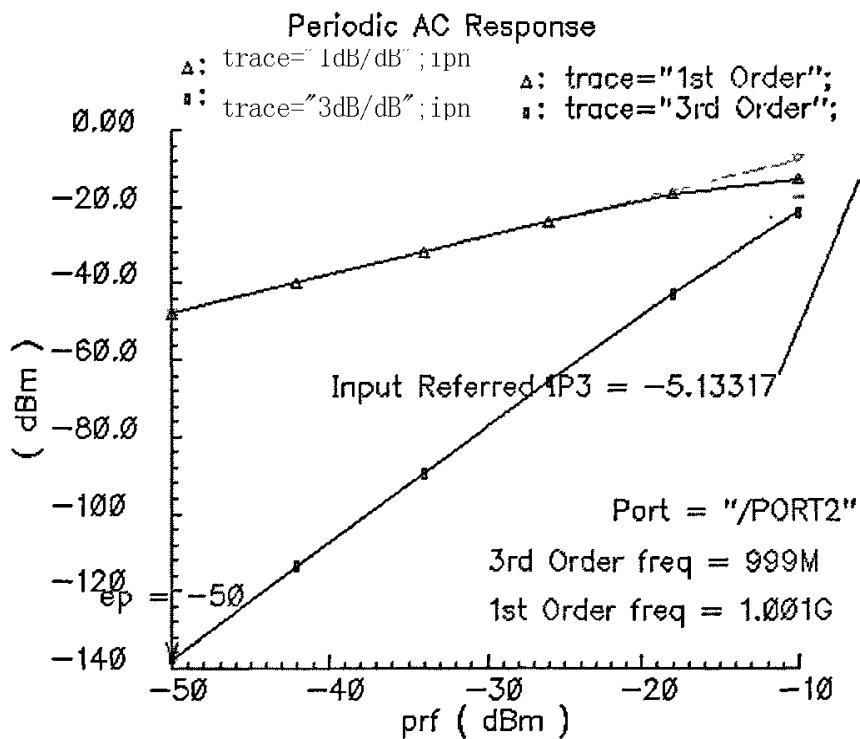

| IIP3                    | -4.5dBm @fif=1.2GHz | -5.1dBm @fif=1.2GHz |

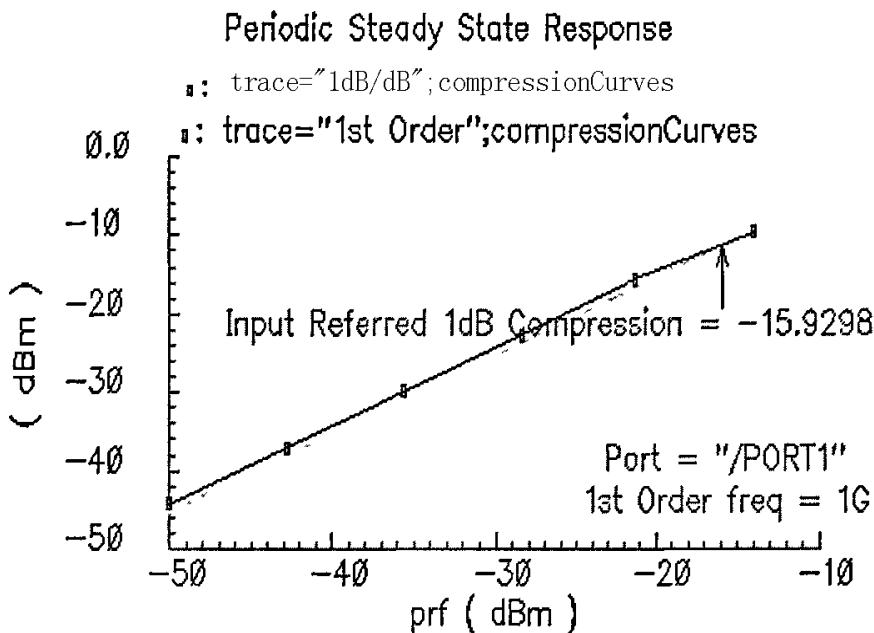

| $P_{1dB}$ (frf=12.5GHz) | -14.3dBm@fif=1.2GHz | -15.9dBm@fif=1.2GHz |

| 转换增益                    | 9.5 dB@fif=1.2GHz   | 8.5dB@fif=1.2GHz    |

| 功耗                      | 12.3mA@3V           | 12.3mA@3V           |

对比前仿真结果可知：由于寄生参数的影响，有源双平衡混频器的噪声系数恶化了约 0.43dB，变为 6.43dB； $S_{22}$ 有所恶化，但带内仍然优于 -10dB；电路的输入 1dB 压缩点恶化为 -15.9dBm，转换增益下降为 8.5dB。

图4-16 混频器DSB噪声系数NF

图4-17 混频器转换增益

(a)射频口输入反射系数\$S\_{11}\$

(b)中频口输出反射系数\$S\_{22}\$

图4-18 输入输出反射系数

图4-19 输入1dB压缩点  $P_{1dB}$

图4-20 输入三阶截断点IIP3

由上面的各个参数的仿真结果可以得知，在工作频段内，该设计同时取得了良好的输入、输出匹配、极低的噪声系数、较高的增益和较好的线性度，除输出反射系数  $S_{11}$  和线性度略差于指标外，其余各项指标都达到或超过预期的设计目标。特别是取得了 6.43dB 的超低的双边带噪声系数，这个指标是笔者目前所见到的类似 SiGe 工艺相关频段内有源混频器设计中最低的。但是，由于目前高频晶体管噪声模型还不完善，有一定的不准确性，以及目前所用的仿真工具还不能对频率在 5GHz 以上的电路进行金属线寄生电感参数的提取，再加上在芯片实际制造过程中所带来的难以预测的各种寄生参数的影响，实测出来的噪声系数肯定会比仿真结果要高。由于实验室的测试设备还未配置好，具体结果如何要等到对芯片进行测试以后才能进行比较。

## 第五章 结论

SiGe 工艺相对于 Si 工艺性能优越许多，价格上又没有 GaAs 工艺昂贵，是 Si 工艺和 GaAs 工艺很好的折衷，并且由于其成本相对低，成品率高，工艺完善、稳定，性能优越，可以广泛应用于移动通信、卫星定位和 RFID 等市场，而且在工艺上可以与常规的数字模拟电路集成，制造功能完整的 SoC 芯片，目前采用 SiGe 材料制作射频集成电路已成为国际上研究的热点。我国作为全世界第一大手机市场，第二大计算机市场，第一大无绳电话生产制造基地，第一大玩具生产大国，急需本土的射频集成电路(RFIC)设计和制作能力。由于无线通信传统上一直是国家和信息安全的重要领域，掌握具有中国自主知识产权的 RFIC 技术，就成为刻不容缓的战略性需要。

本文在阅读大量相关文献的基础上，对低噪声放大器和混频器的原理进行了深入的分析和研究，针对 Ku 波段 DVB-S 下行链路标准设计了一个工作在 12.25GHz—12.75GHz 的低噪声放大器和混频器。本文所设计的低噪放和混频器是目前国内首次采用基于 SiGe 的 BiCMOS 工艺设计频率高于 10GHz 的射频集成电路，具有极大的设计挑战性，并取得了不错的仿真结果。本论文主要完成了以下工作：

- (1) 根据 Ku 波段 DVB-S 标准及射频前端电路的性能指标，明确了对低噪放和混频器的设计要求，并据此收集相关文献资料。在对采用不同电路结构实现的低噪声放大器和混频器有了比较充分的了解之后，确定了所要设计的电路结构。

- (2) 对低噪声放大器和有源双平衡混频器的性能指标，诸如噪声系数、线性度、增益、输入输出匹配进行了详细的分析，并得出了一些有指导意义的结论。

- (3) 运用 Cadence SpectreRF 仿真工具对低噪声放大器和混频器进行电路仿真，设计电路。

- (4) 运用 Virtuoso layout 版图工具设计和优化了低噪声放大器和混频器的版图，并用 Assura 和 Calibre 对版图进行了 drc (设计规则)、ant (天线效应)、density (金属密度)、softerc (电气规则)、stress (应力效应) 检查。

- (5) 运用 Assura 和 Calibre 对版图进行了 LVS 检查(版图一原理图对照检查)，并运用 Assura 和 Calibre 中的参数提取工具提取了寄生参数，进行版图后仿真。

- (6) 将版图数据生成为 GDS 文件，送往代工厂流片。

从前后仿真的对比结果可以知道，RFIC 后端版图设计十分重要，衬底之间的耦合和各个单元之间的隔离应该充分考虑到。进一步研究不仅仅包括后续单元电路如开关、功放、锁相环、VCO 等设计，重点应该从系统级考虑适用于射频集成电路的射频前端系统架构和适用于这种系统架构的各个单元模块的设计。

## 致谢

首先我要衷心感谢我的导师刘光祜教授和马建国教授。本论文的选题、理论研究和论文的撰写都是在两位老师的悉心指导和鼓励下完成的。三年来，刘老师严谨的科研作风，诚挚的待人态度，以及对学生无微不至的关心，都将使我一生受益。马老师深厚的理论功底，专业的技术知识、积极的工作热情和谦逊的待人态度都给我留下了深深的印象。

本论文的具体研究工作是在韩磊博士的直接领导和鼓励下完成的，谨向他致以深深的谢意。

感谢教研室熊飞工程师、唐贻莲工程师和 Wingfoon.Lee 博士的帮助和指导，在与他们的讨论过程中我受益良多。

感谢李萍，喻浩然、卫颜锋等射频组同学，以及教研室所有师兄弟给予的支持和鼓励。特别感谢范正锋同学在论文写作过程中所给予的帮助。

感谢我的父母和亲人在我漫长的求学过程中给予的理解和支持！

感谢为评阅本文付出辛勤劳动的专家和学者们！

## 参考文献

- [1] 姚飞, 成步文, 王启明 “SiGe HBT 及高速电路的发展” 微纳电子技术 2003 年第 10 期

- [2] 李建平, 2003 信息产业展望, [www.ccw.com.cn](http://www.ccw.com.cn)

- [3] Copani T,Santo A S,Girlando G,et al.A 12-GHz silicon bipolar dual-conversation receiver for digital satellite application.IEEE Journal of Solid-State Circuit,2005,40(6):1278-1287

- [4] Yanxin Wang,Jon S.Duster,and Kevin T.Kornegay,et al. An 18 GHz Low Noise High Linearity Active Mixer in SiGe.IEEE Circuit and Systems,2005.ISCAS.2005,Vol.4:3243-3246

- [5] Takayuki Ikushima,Kenji Itoh, et al.A Dual Bias-Feed Circuit Design for SiGe HBT Low-Noise Linear Amplifier. IEEE Transactions on Microwave and Techniques, Vol.51, No.2, Feb 2003.

- [6] Hachl S, Meister T F. Low-noise low-power monolithically integrated active 20 GHz mixer in SiGe technology, Electron. Lett. 2001, 37(1): 36-37

- [7] Gruhle A, Shuppen A, Konig U, et al “ Monolithic 26 GHz and 40 GHz VCO’s with SiGe heterojunction bipolar transistors” IEDM Tech. Dig. 1995, 725-728

- [8] Tseng Pei-Der, Zhang Liyang, Gao Guangbo, et al “ A 3-V monolithic SiGe HBT power amplifier for dual-mode (CDMA/AMPS) cellular handset applications”IEEE J. Solid-State Circuits, 2000, 35(9): 1338-1344

- [9] 林敏, 王海永, 李永明, 等. 2GHz CMOS 射频低噪声放大器的设计与测试. 电子学报, 2002, Vol. 30, NO. 9, pp.1278-1281.

- [10] 陶蕤, 王志功, 谢婷婷, 等. 2.9GHz 0.35 $\mu$ m CMOS 低噪声放大器. 电子学报, 2001, Vol. 29, NO. 11, pp.1530-1532.

- [11] JAZZ SBC35 (SiGe60) Design Manual

- [12] 美.Reinhold Ludwig,Pavel Bretschko 著. 王子宇等译.射频电路设计—理论与应用.北京: 电子工业出版社, 2002

- [13] C.-P. Chang and H.-R. Chuang: “0.18 um 3-6 GHz CMOS broadband LNA for UWB radio” ELECTRONICS LETTERS 9th June 2005 Vol. 41 No. 12 pp.3056-3058

- [14] Joonho Gil, Kwangscok Han and Hyungcheol Shin: “13 GHz 4.67 dB NF CMOS low-noise amplifier” ELECTRONICS LETTERS 10th July 2003 Vol. 39 No. 14 pp.1056-1058

- [15] Shih-Chieh Shin, Ming-Da Tsai, Ren-Chieh Liu, Kun-You Lin, and Huei Wang: “A 24-GHz 3.9dB NF Low-Noise Amplifier Using 0.18 um CMOS Technology” IEEE MICROWAVE

- AND WIRELESS COMPONENTS LETTERS, VOL. 15, NO. 7, JULY 2005 pp.448-450

- [16] Xiaoling Guo, Kenneth K. O:“A Power Efficient Differential 20-GHz Low Noise Amplifier With 5.3-GHz 3-dB Bandwidth” IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, VOL. 15, NO. 9, SEPTEMBER 2005 pp.4056-4058

- [17] D. Zoschg, W. Wilhelm, T.F. Meister, H. Knapp, H.-D. Wohlmuth, K. Aufinger, M. Wurzer, J. Bock, H. Schafer and A. Scholtz: “2dB noise figure, 10.5GHz LNA using SiGe bipolar technology” ELECTRONICS LETTERS 9th December 1999 Vol. 35 No. 25 pp.2195-2196

- [18] H. Knapp, D. Zöschg, T. Meister, K. Aufinger, S. Boguth, and L. Treitinger, “15 GHz wideband amplifier with 2.8 dB noise figure in bipolar technology” IEEE Radio Frequency Integrated Circuits Symp., June 2001, pp. 287-290

- [19] K.-B. Schad, U. Erben, E. Sömnez, P. Abele, and H. Schumacher, “A Ku band SiGe low noise amplifier” in Silicon Monolithic Integrated Circuits in RF Systems Topical Meeting, 2000, pp. 159-162

- [20] Paolo Crippa, Simone Orcioni, Francesco Ricciardi, Claudio Turchetti “DESIGN OF A 4.4 TO 5 GHz LNA IN 0.25-/spl mu/m SiGe BiCMOS TECHNOLOGY” IEEE Circuit and Systems,2003.ISCAS.2003,Vol1:1333-1336

- [21] Bo Shi and Michael, Yan Wah Chia “A 3.1-10.6 GHz RF Front-End for MultiBand UWB Wireless Receivers” IEEE Radio Frequency Integrated Circuits Symposium.12-14June 2005 page(s).343-346

- [22] J.Sadowy, J.Graffeuil, E.Tournier, L.Escotte and R.Plana: “Advanced Design of high linearity, low noise amplifier for WLAN using a SiGe BiCMOS Technology” Silicon Monolithic Integrated Circuits in RF Systems, 2001. Digest of Papers. 2001 Topical Meeting on 12-14 Sept. 2001 pp.6-11

- [23] Frank Ellinger, and Heinz Jäckel: “Low-Cost BiCMOS Variable Gain LNA at Ku-Band With Ultra-Low Power Consumption” IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 52, NO. 2, FEBRUARY 2004 pp.702-708

- [24] 刘学观, 郭辉萍.微波技术与天线.西安: 西安电子科技大学出版社, 2001, 81-82

- [25] 顾其铮, 项家桢, 袁孝康.微波集成电路设计.北京: 国防工业出版社, 1985, 325-327

- [26] 陈邦媛. 射频通信电路.北京: 科学技术出版社, 2002

- [27] Jung-Suk Goo, Hee-Tae Ahn, and Donald J. Ladwig, et al, “A NoiseOptimization Technique for Integrated Low-Noise Amplifiers”, IEEE Journalof Solid-State Circuits, Vol. 37, NO. 8, August 2002 pp.702-708

- [28] Thomas H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits .Cambridge university Press 1998

- [29] Behzad Razavi. Design of Analog CMOS Integrated Circuits. McGraw-Hill 2001.

- [30] Tommy K. K. Tsang, Mourad N. El-Gamal, Gain Controllable Very Low Voltage 8-9GHz Integrated CMOS LNA. IEEE Radio Frequency Integrated Circuits Symposium.2-4June 2002 page(s).205-208

- [31] B.Gilbert.A Precise Four Quadrant Multiplier with Subnanosecond Response.IEEE J.Solid-State Circuits,Vol.SC-3,pp.365-373,Dec.1968

- [32] Corrado Carta, Rolf Vogt, Werner Bachtold. A Low-Power SiGe-HBT Activ Double-Balanced Mixer for Compact Integrated C-Band Wireless-LAN Receivers. IEEE Microwave and Optoelectronics Conference,2003,IMOC 2003,Volume3,sept,page(s)20-23.

- [33] Farsheed Mahomoudi,C.Andre T.Salama.8GHz,1V,High Linearity,Low Power CMOS Active Mixer. IEEE Radio Frequency Integrated Circuits Symposium. 2-4June 2004 page(s).605-608.

- [34] Lynch, M. W., Holdenried, et al. A 17-GHz Direct Down-Conversion Mixer in a 47-GHz SiGe Process. IEEE Radio Frequency Integrated Circuits Symposium, pp. 461-464, Jun. 2003.

- [35] Hackl, S., et al. Benefits of SiGe over Silicon Bipolar Technology for Broadband Mixer with Bandwith above 10 GHz. 2001 IEEE MTT-S International Microwave Symposium Digest, Vol. 3, pp. 1693-1696, May 2001.

- [36] Schad, K.B., Schumacher, H., Schuppen, A.. Low-Power Active Mixer for Ku-band Application Using SiGe HBT MMIC Technology. 2000 IEEE MTT-S International Microwave Symposium Digest, Vol. 1, pp. 397-400, Jun 2000.

- [37] 美 Behzad Razavi 著,余志平, 周润德译.射频微电子.北京: 清华大学出版社, 2006

- [38] 池保勇, 余志平, 石秉学. CMOS 射频集成电路分析与设计. 北京: 清华大学出版社, 2006

- [39] D.Shaeffer and T.Lee,A 1.5V,1.5GHz CMOS low noise amplifier.[J].IEEE Journal of Solid-State Circuits, Vol32, No.5, pp.745-59,1997

- [40] B.Razavi. RF Microelectronics,ser[M]. Pretience Hall Communications Engineering and Emerging Technologies Series. Hall PTR,1997

## 个人简历

姓名：汪金铭

出生年月：1981 年 11 月

2000 年—2004 年      电子科技大学       电子工程专业

2004 年—2007 年      电子科技大学       电路与系统专业

## 研究成果

- [1] 汪金铭, 韩磊. 12.5GHz 基于 SiGe 工艺的超低噪声有源混频器芯片设计. 成都: 四川省电子学会半导体与集成技术专委会 2006 年度学术年会论文集, 2006 年 12 月, pp. 223-226.

- [2] 马建国, 韩磊, 谢李萍, 汪金铭等. 基于硅工艺的 12GHz 单片接收 RF Front-End 设计. 成都: 电子科技大学学报, 2006 年 8 月, Vol.35 No.4, pp.638-641.